Матричный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

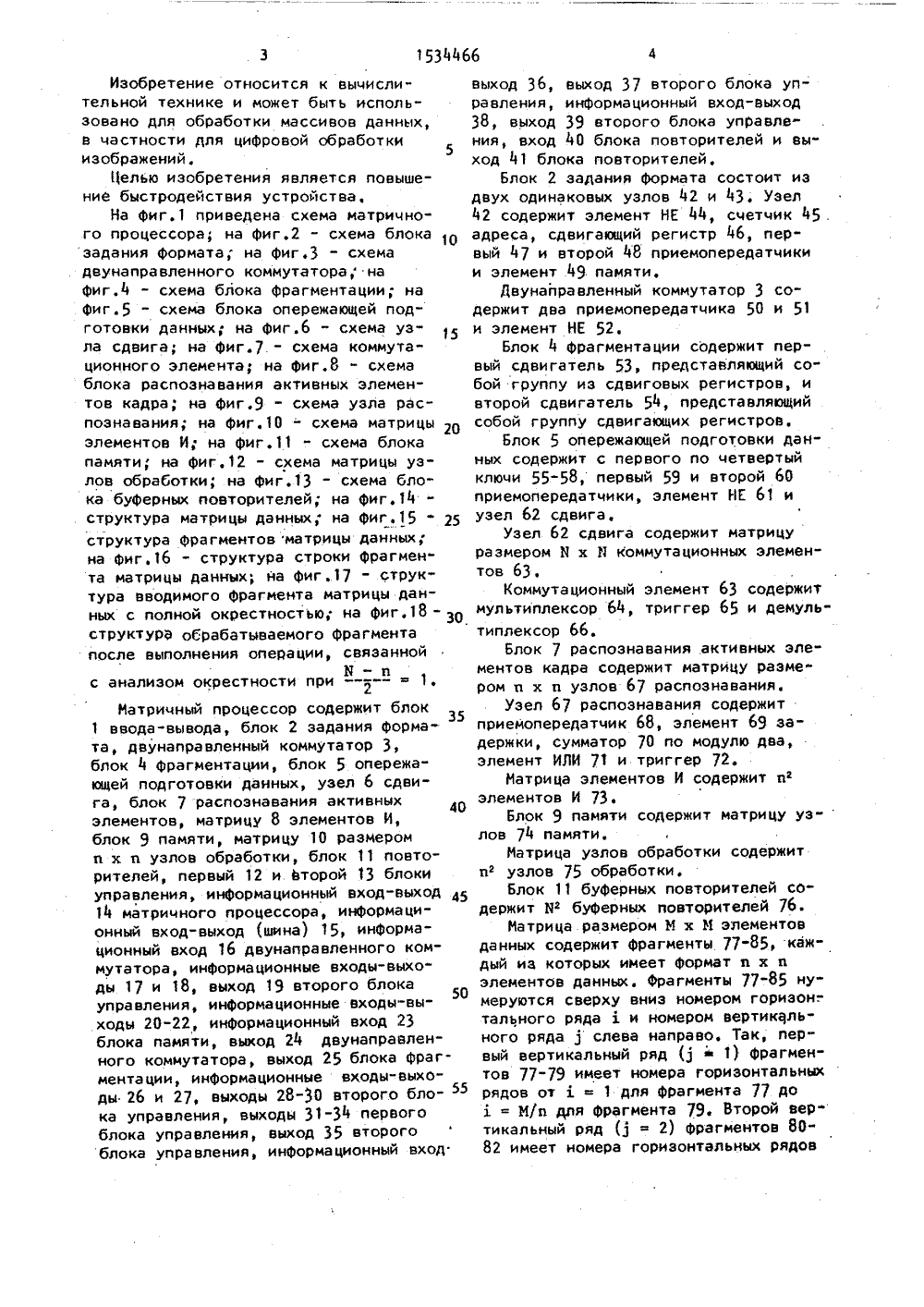

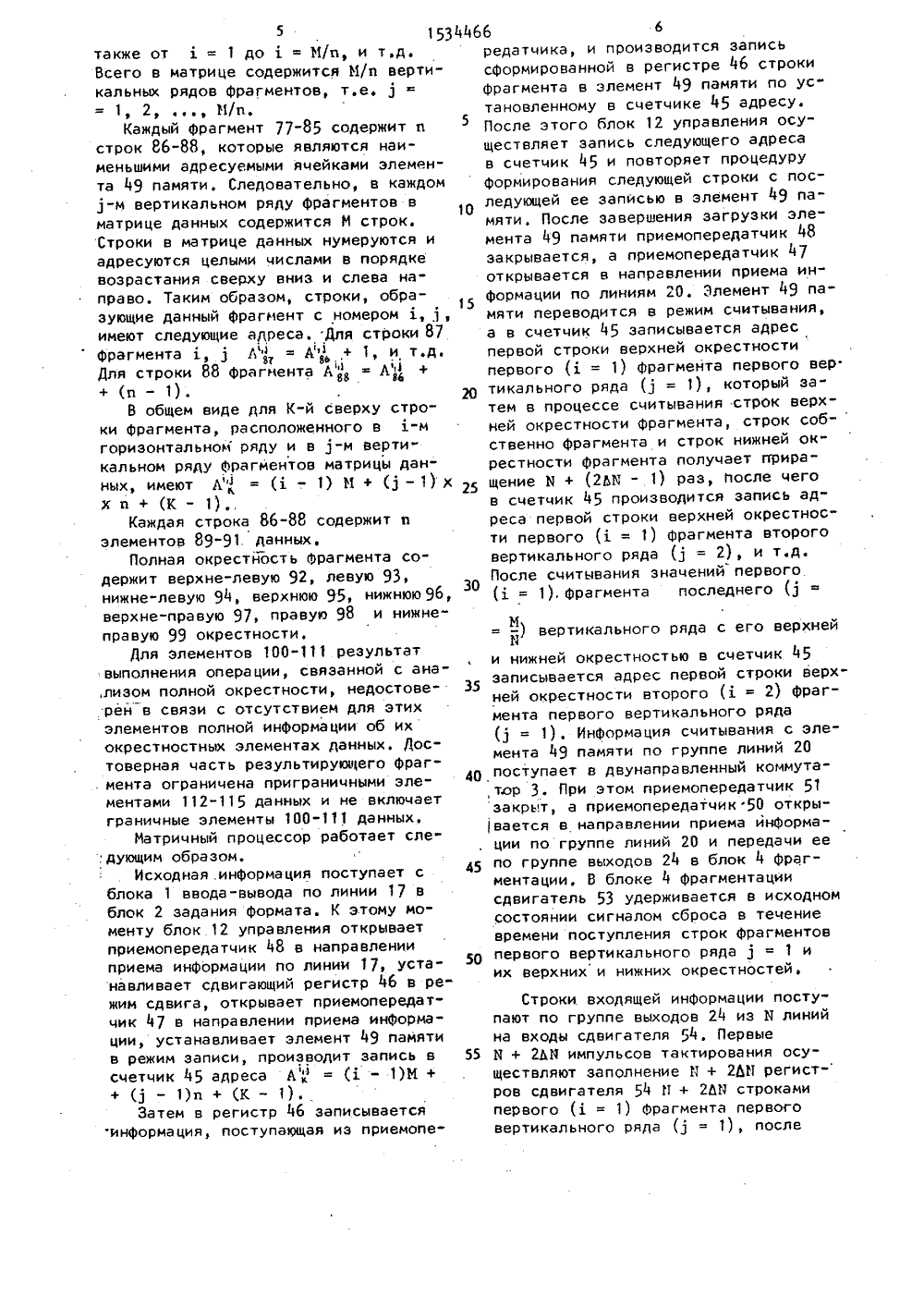

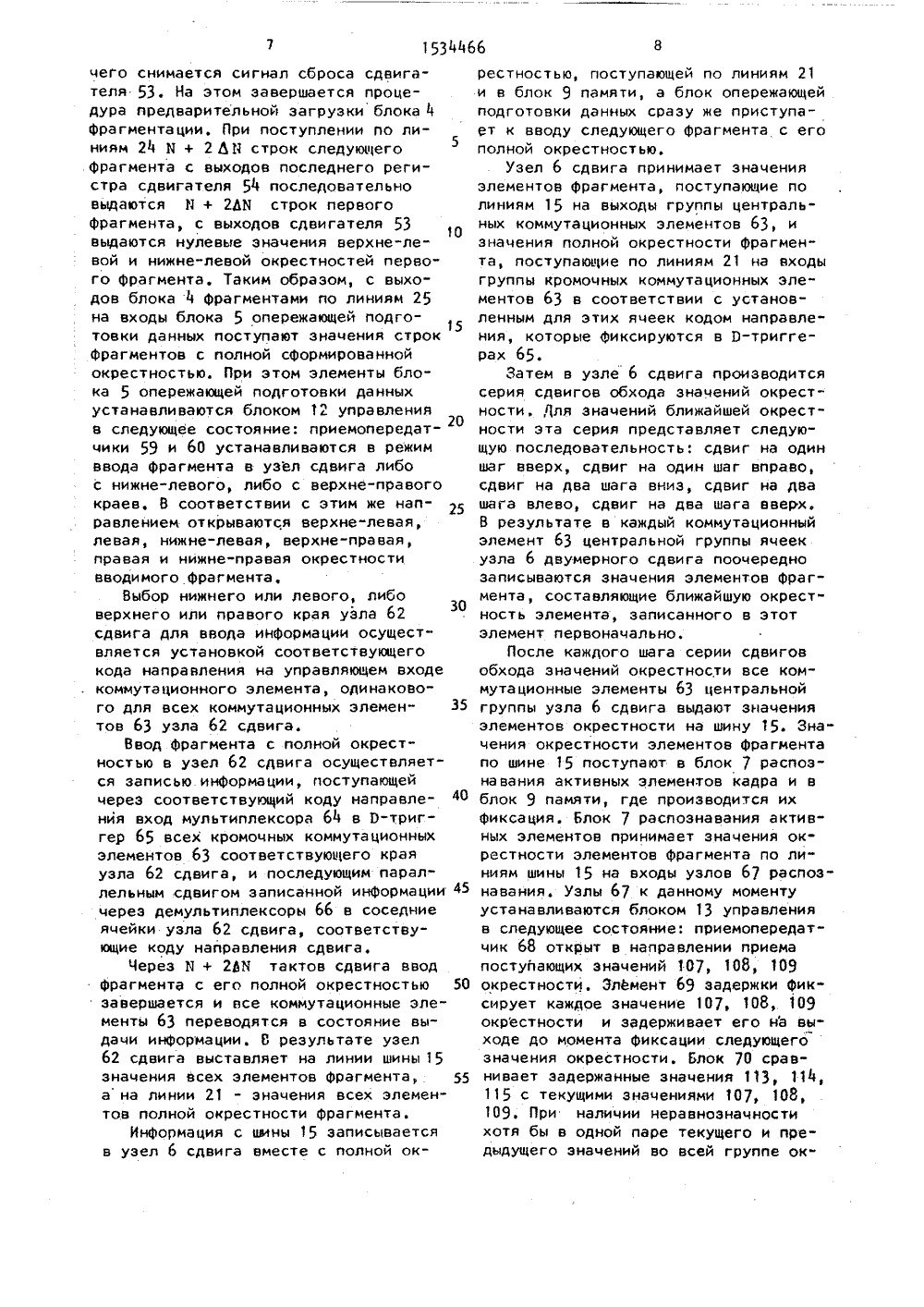

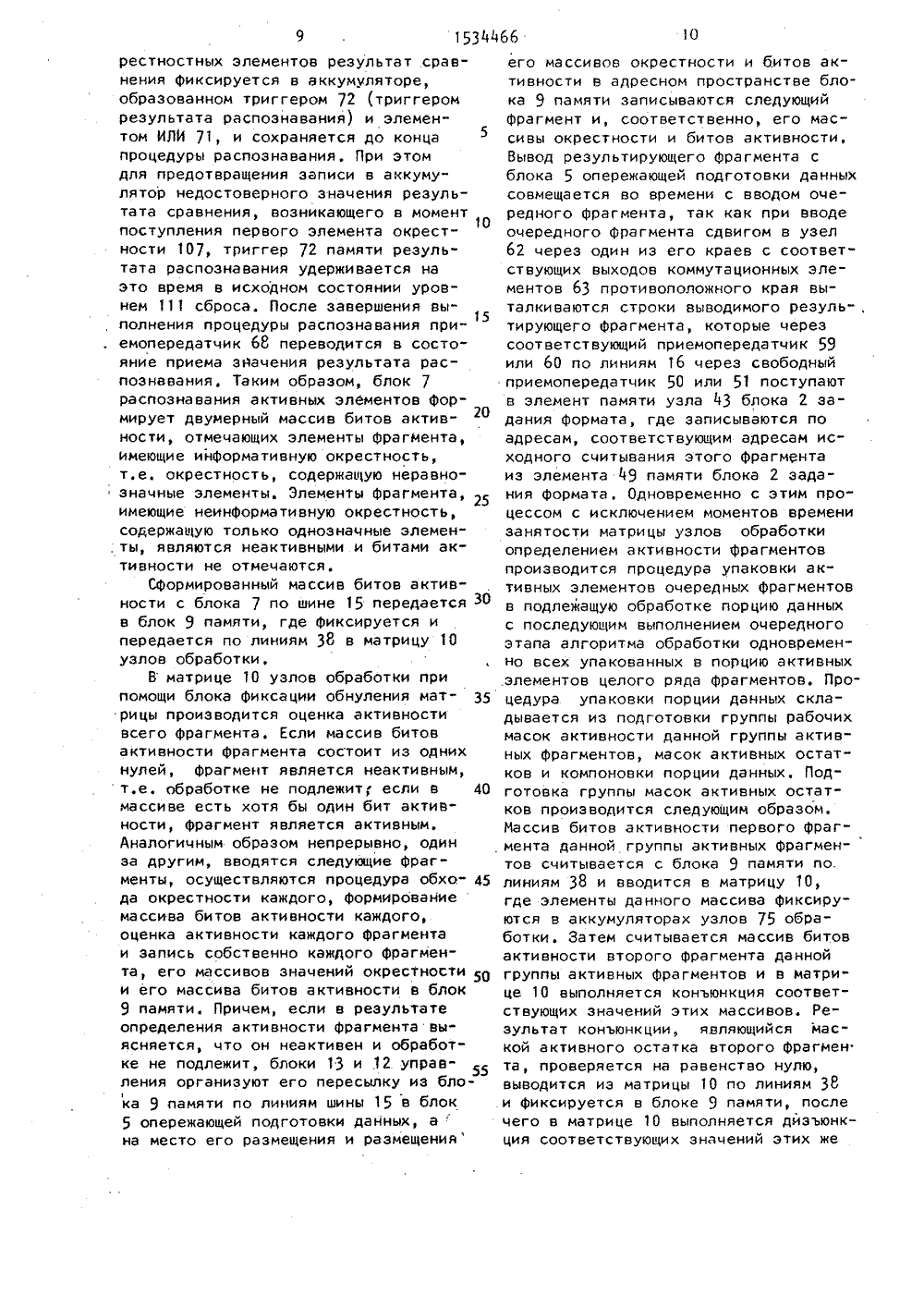

ОЮЗ СОВЕТСКИХОЦИАЛИСТИЧЕСНИСПУБЛИК 1) 5 С 06 Г 15/16 О НИЕ ИЗ ТЕНИЯ ЛЬСТВУ(57) Изобретени вычислительной к устройствам д массивов данных изобретения - и ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ П 1 НТ СССР К АВТОРСКОМУ СВИД(71) Специализированное проектно-кструкторское бюро автоматизированнсистем управления "Кибернетика"(56) Патент СИЯ В" 4115401)кл. с о 6 г 7/00, 198 о.Явторское свидетельство СССРЮ 1354204, кл. С 06 Г 15/16) 1986. РОЦЕССОРотносится к областехники, в частностия обработки большихизображений. Цельвышение быстродейст вия за счет предварительной активности элементов массива ции и исключения из процесса ки неактивных элементов одно с обработкой предыдущей порци ных элементов. Цель достигае что матричный процессор содер блок 1 ввода-вывода, блок 2 3 формата, двунаправленный ком блок 4 фрагментации, блок 5 о ющей подготовки данных, узел га, блок, 7 распознавания акти элементов кадра, матрицу 8 ра И х И, где Л - линейный разм батываемого кадра, элементов9 памяти, матрицу размером И лов обработки, блок 11 буферн торителей, первый 12 и второй ки управления. 5 з,п. ф-лы, 1 оценки информа- обработвременно и активтся тем, жит адания мутатор 3 пережаб сдвивных амером ер обра- И, блок х И узых пов 13 бло ил.дое матрицы, первые информационные входы-выходы коммутационных элементов первого столбца с первой поВ-и-ю подключены соответственно2Б - ик восьмой группе изинформа 2ционных входов-выходов матрицы, третьи информационные входы-выходы коммутационных элементов первой строки 1 И-истолбцов с первого по -й под 2ключены соответственно к девятой 1 О Б-и 15 группе изинформационных вхо.2дое-выходов матрицы, первые информационные входы-выходы коммутационных элементов первого столбца строк с20В-и( + и + 1)-й по И-ю подключены2соответственно к десятой группе иэИ - иинформационных входов-выходов 252матрицы, четвертые информационныевходы-выходы коммутационных элементовИ - иН-й строки с ( + и + 1)-го по И-й30столбцов подключены соответственно кИ - иодиннадцатой группе изинфор 2мационных входов-выходов матрицы,вторые и нформа ционные входы-выходыкоммутационных элементов И-го столбцаИ-и.строк с первой по -ю подключе 2ны соответственно к двенадцатой груп 40Н-ипе иэ ("-) информационных входов 2выходов матрицы, четвертые информационные входы-выходы коммутационныхэлементов И-й строки столбцов с перБ - ивого по -й подключены соответ 2ственно к тринадцатой группе иэК-иинформа ционных входов-выходов 502матрицы, вторые информационные входы- выходы коммутационных элементов матрицы, вторые информационные входы- выходы коммутационных элементов И-го55М - истолбца с ( + и + 1)-й по И-ю2строк подключены соответственно к чеГ 1 - итырнадцатой группе иэинформационных входов-выходов матрицы, пятые информационные входы-выходы коммутационных элементов т.-й строки -гостолбца матрицы подключены соответственно к первой группе иэ и информационных входов-выходов матрицы, апятые информационные входы-выходы остальных коммутационных элементов матрицы подключены соответственно к второй группе из (11 - и) информационных входов-выходов матрицы, при этомкаждый коммутационный элемент матрицысодержит мультиплексор, демультиплек"сор и триггер, причем е каждом коммутационном элементе матрицы первыйинформационный вход-выход коммутационного элемента подклюцен к первомувыходу демультиплексора и к первомуинформационному входу мультиплексора,второй информационный вход-выход коммутационного элемента подключен квторому выходу демультиплексора и второму информационному входу мультиплексора, третий информационный входвыход коммутационного элемента подключен к третьему выходу демультиплексора и третьему информационномувходу мультиплексора, четвертый информационный вход-выход коммутационного элемента подключен к четвертомувыходу демультиплексора и четвертомуинформационному входу мультиплексора,пятый информационный вход-выход коммутационного элемента подключен к пятому выходу демультиплексора и пятому информационному входу мультиплексора, управляющий вход коммутационного элемента подключен к входу синхронизации триггера, к управляющемувходу демультиплексора и управляющемувходу мультиплексора, выход которогоподключен к информационному входудемультиплексора,Процессор по п,1, о т л и ц аю щ и й с я тем, что блок распознавания элементов кадра содержит матрицу размером и х и узлов распознавания, причем и информационных входов"выходов матрицы подключены соответственно к информационным входам-выходам и узлов распознавания матрицы,первый, второй и третий управляющиевходы блока подключены соответственнок первым, вторым и третьим управляющим входам и узлов распознаванияматрицы, при этом каждый узел распоэ навания матрицы содержит приемопередатчик, элемент задержки, элемент ИЛ 11,сумматор по модулю два и триггер,причем в каждом узле распознаванияинформационный вход-выход узла распознавания подключен к инФормационному входу-выходу приемопередатчика,выход которого подключен к первомувходу сумматора по модулю два и входуОэлемента задержки, выход которогоподключен к второму входу сумматорапо модулю два, выход которого подключен к первому входу элемента ИЛИ, выход которого подключен к информацион 15ному входу триггера, выход которогоподключен к информационному входу приемопередатчика и второму входу эле"мента ИЛИ, первый и второй управляю"щие входы узла распознавания подключены соответственно к управляющемувходу приемопередатчика и входу установки в "0" триггера, третий управляющий вход узла распознавания подключен к синхровходам элемента задержкии триггера,5, Процессор по п.1, о т л и ч аю щ и й с я тем, что блок памяти содержит матрицу размером п к п узловпамяти, причем первые и вторые информационные входы-выходы узлов памятиматрицы подключены соответственно кпервой группе из и информационныхвходов-выходов и к второй группе изи информационных входов-выходов блока памяти, с первого по и информационные входы которого подключены соответственно к управляющим входам и узлов памяти матрицы, первый, второйи третий управляющие входы первойгруппы и первый, второй и третий управляющие входы второй группы блокапамяти подключены соответственно кпервым адресным входам, к первым входам чтения, к первым входам записи,к вторым адресным входам, к вторымвходам чтения и вторым входам записивсех узлов памяти матрицы, при этомматрица элементов И содержит и элементов И первые входы и выходы которых подключены соответственно к ивходам и к и выходам матрицы элементов И, управляющий вход матрицы элементов И подклюцен к вторым входамвсех элементов И матрицы. б. Процессор по п.1, о т л и ч аю щ и й с я тем, что матрица размером и х п узлов обработки содержит и узлов обработки, причем и информационных входов-выходов матрицы подключены соответственно к информационным входам-выходам и узлов обработки, выходы которых подключены соответственно к и выходам матрицы узлов обработки, управляющий вход которой подключен к входам кода операции всех узлов обработки матрицы, при этом блок буферных повторителей содержит и буферных повторителей, входы которых подключены соответственно к входам с первого по и блока буферных повторителей, выходы и буферных повторителей обьединены и подключены к выходу блока буФерных повторителей.153 М 66 Составитель В,Смирноведактор О,Юрковецкая Техред М.Дидык Корректор Т,Пали Тираж 554 Подписное оиэводственно-издательский комбинат "Патент", г. Уж арина,101 ул. Заказ Й 2ВИИИПИ Госу твенного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Я, .Раушская наб., д. Й/5Изобретение относится к вычислительной технике и может быть использовано для обработки массивов данных, в частности для цифровой обработки изображений.Целью изобретения является повышение быстродействия устройства.На фиг.1 приведена схема матричного процессора; на Фиг.2 - схема блока 10 задания формата; на фиг.3 - схема . двунаправленного коммутатора; на фиг.4 - схема блока Фрагментации; на фиг.5 - схема блока опережающей подготовки данных; на Фиг.б - схема узла сдвига; на фиг.7. - схема коммута"ционного элемента; на Фиг.8 - схема блока распознавания активных элементов кадра; на Фиг.9 - схема узла распознавания; на фиг.10 - схема матрицы 20элементов И; на фиг.11 - схема блокапамяти; на фиг,12 - схема матрицы узлов обработки; на Фиг.13 - схема блока буФерных повторителей; на Фиг.14структура матрицы данных; на Фиг,15 - 25структура фрагментов матрицы данных; на фиг, 16 - структура строки фрагмента матрицы данных; на фиг.17 - структура вводимого Фрагмента матрицы данных с полной окрестностью; на Фиг,18 - З 0 структура обрабатываемого фрагмента после выполнения операции, связаннойК - ис анализом окрестности при1,Иатричный процессоР соДержит блок1 ввода-вывода, блок 2 задания формата, двунаправленный коммутатор 3,блок 4 фрагментации, блок 5 опережающей подготовки данных, узел 6 сдвига, блок 7 распознавания активных 40элементов, матрицу 8 элементов И,блок 9 памяти, матрицу 10 размероми х и узлов обработки, блок 11 повторителей, первый 12 и второй 13 блокиуправления, информационный вход-выход 4514 матричного процессора, информационный вход-выход (шина) 15, информационный вход 16 двунаправленного коммутатора, информационные входы-выходы 17 и 18, выход 19 второго блокауправления, информационные входы-выходы 20-22, информационный вход 23блока памяти, выкод 24 двунаправленного коммутатора, выход 25 блока Фрагментации, инФормационные входы-выхо" ды 26 и 27, выходы 28-30 второго бло 55ка управления, выходы 31-34 первого блока управления, выход 35 второго блока управления, информационный вход выход 36, выход 37 второго блока упРавления, информационный вход-выход38 выход 39 второго блока управления, вход 40 блока повторителей и выход 41 блока повторителей.Блок 2 задания Формата состоит издвух одинаковых узлов 42 и 43. Узел42 содержит элемент НЕ 44, счетчик 45 .адреса, сдвигающий регистр 46, первый 47 и второй 48 приемопередатчикии элемент 49 памяти,двунаправленный коммутатор 3 содержит два приемопередатчика 50 и 51и элемент НЕ 52.Блок 4 фрагментации содержит первый сдвигатель 53, представляющий собой группу из сдвиговых регистров, ивторой сдвигатель 54, представляющийсобой группу сдвигающих регистров.Блок 5 опережающей подготовки данных содержит с первого по четвертыйключи 55-58, первый 59 и второй 60приемопередатчики, элемент НЕ 61 иузел 62 сдвига.Узел 62 сдвига содержит матрицуразмером Н х Л коммутационных элементов 63.Коммутационный элемент 63 содержитмультиплексор 64, триггер 65 и демуль"типлексор 66.Блок 7 распознавания .активных элементов кадра содержит матрицу разме"ром и х и узлов 67 распознавания.Узел 67 распознавания содержитприемопередатчик 68, элемент 69 задержки, сумматор 70 по модулю два,элемент ИЛИ 71 и триггер 72.Иатрица элементов И содержит иэлементов И 73.Блок 9 памяти содержит матрицу уз-лов 74 памяти,Матрица узлов обработки содержити узлов 75 обработки.Блок 11 буферных повторителей содержит Н буФерных повторителей 76.Иатрица размером И х И элементовданных содержит фрагменты 77-85, каж"дый из которых имеет формат и х иэлементов данных. Фрагменты 77-85 нумеруются сверху вниз номером горизон-.тального рядаи номером вертикального ряда 1 слева направо, Так, первый вертикальный ряд (д 1) фрагментов 77-79 имеет номера горизонтальныхрядов от1 для Фрагмента 77 дохМ/и Для Фрагмента 79, Второй вертикальный ряд (12) Фрагментов 80"82 имеет номера горизонтальных рядов344666 5 1 О 15 20 25 30 35 45 50 55 5 15также от 1 = 1 до 1 = И/а, и т,д.Всего в матрице содержится И/и вертикальных рядов Фрагментов, т.е.1, 2, , И/п.Каждый Фрагмент 77-85 содержит истрок 86-88, которые являются наименьшими адресуемыми ячейками элемента 49 памяти, Следовательно, в каждом1-м вертикальном ряду фрагментов вматрице данных содержится М строк.Строки в матрице данных нумеруются иадресуются целыми числами в порядкевозрастания сверху вниз и слева направо. Таким образом, строки, образующие данный Фрагмент с номеромимеют следующие адреса, Для строки 87Для строки 88 Фрагйента Л" А ++ (и - )В общем виде для К-й сверху строки Фрагмента, расположенного в -мгоризонтальном ряду и в 1-м верти"кальном ряду Фрагментов матрицы данных, имеют А" = (1. - 1) И + (3 - 1) Хха+ (К)Каждая строка 86-88 содержит аэлементов 89-91 данныхПолная окрестность Фрагмента содержит верхне-левую 92, левую 93,нижне-левую 94, верхнюю 95, нижнюю 96,верхне-правую 97, правую 98 и нижнеправую 99 окрестности.Для элементов 100-111 результатвыполнения операции, связанной с ана,лизом полной окрестности, недостоверен в связи с отсутствием для этихэлементов полной информации об ихокрестностных элементах данных. Достоверная часть результирующего фраг. мента ограничена приграничными элементами 112-115 данных и не включаетграничные элементы 100-111 данных,Матричный процессор работает следующим образом,Исходная .информация поступает сблока 1 ввода-вывода по линии 17 вблок 2 задания формата. К этому моменту блок.12 управления открываетприемопередатчик 48 в направленииприема информации по линии 17, устанавливает сдвигающий регистр 46 в ре"жим сдвига, открывает приемопередатчик 47 в направлении приема информации, устанавливает элемент 49 памятив режим записи, производит запись всчетчик 45 адреса А" = (х - 1)М ++ (1-1)и+ (К),Затеи в регистр 46 записываетсяинформация, поступающая из приемопе" редатцика, и производится записьсформированной в регистре 46 строкифрагмента в элемент 49 памяти по установленному в счетчике 45 адресу.После этого блок 12 управления осуществляет запись следующего адресав счетчик 45 и повторяет процедуруформирования следующей строки с последующей ее записью в элемент 49 памяти, После завершения загрузки элемента 49 памяти приемопередатчик 48закрывается, а приемопередатчик 47открывается в направлении приема инФормации по линиям 20. Элемент 49 памяти переводится в режим считывания,а в счетчик 45 записывается адреспервой строки верхней окрестностипервого ( = 1) фрагмента первого вер.тикального ряда ( = 1), который затем в процессе считывания строк верхней окрестности фрагмента, строк соб-ственно Фрагмента и строк нижней окрестности Фрагмента получает приращение В + (2 ЬИ - 1) раз, после чегов сцетцик 45 производится запись адреса первой строки верхней окрестности первого ( = 1) Фрагмента второговертикального ряда ( = 2), и т.дПосле считывания значений первого= -) вертикального ряда с его верхнеиВ и нижней окрестностью в счетчик 45 записывается адрес первой строки верхней окрестности второго (1 = 2) Фрагмента первого вертикального ряда(3 = 1). ИнФормация считывания с элемента 49 памяти по группе линий 20 40 поступает в двунаправленный коммута,тор 3. При этом приемопередатцик 51 закрыт, а приемопередатчик 50 открывается в направлении приема информа" ции по группе линий 20 и передачи еепо группе выходов 24 в блок 4 фрагментации, В блоке 4 фрагментациисдвигатель 53 удерживается в исходномсостоянии сигналом сброса в течениевремени поступления строк фрагментовпервого вертикального ряда= 1 иих верхних и нижних окрестностей,Строки. входящей информации поступают по группе выходов 24 из Б линий на входы сдвигателя 54, Первые Б + АМ импульсов тактирования осуществляют заполнение И + 2 ДИ регист- ров сдвигателя 54 И + 2 Ь 11 строками первого (1 = 1) Фрагмента первого вертикального ряда ( = 1), послечего снимается сигнал сброса сдвигателя 53. На этом завершается процедура предварительной загрузки блока 4фрагментации, При поступлении по линиям 24 И + 2 ЛИ строк следующего.Фрагмента с выходов последнего регистра сдвигателя 54 последовательновыдаются 11 + 2 ДИ строк первогоФрагмента, с выходов сдвигателя 53выдаются нулевые значения верхне-левой и нижне-левой окрестностей первого Фрагмента, Такии образом, с выходов блока 4 Фрагментами по линиям 25на входы блока 5 опережающей подготовки данных поступают значения строкФрагментов с полной сформированнойокрестностью. При этом элементы блока 5 опережающей подготовки данныхустанавливаются блоком 12 управленияв следующее состояние: приемопередат"чики 59 и 60 устанавливаются в режимввода фрагмента в узел сдвига либос нижне-левого, либо с верхне-правогокраев. В соответствии с этим же направлением открываются верхне-левая,левая, нижне-левая, верхне-правая,правая и нижне-правая окрестностивводимого фрагмента,Выбор нижнего или левого, либоверхнего или правого края узла 62сдвига для ввода информации осущест"вляется установкой соответствующегокода направления на управляющем входекоммутационного элемента, одинакового для всех коммутационных элемен- З 5тов 63 узла 62 сдвига,Ввод фрагмента с полной окрестностью в узел 62 сдвига осуществляется записью информации, поступающейчерез соответствуюи 1 ий коду направления вход мультиплексора 64 в 0-триггер 65 всех кромочных коммутационныхэлементов 63 соответствующего краяузла 62 сдвига, и последующим параллельным сдвигом записанной инФормации 45через демультиплексоры 66 в соседниеячейки узла 62 сдвига, соответствующие коду направления сдвига.Через И + 2 ЬМ тактов сдвига вводфрагмента с его полной окрестностью 50завершается и все коммутационные элементы 63 переводятся в состояние выдачи информации. В результате узел62 сдвига выставляет на линии шины 15значения всех элементов фрагмента, 55а на линии 21 - значения всех элементов полной окрестности Фрагмента.ИнФормация с шины 15 записываетсяв узел 6 сдвига вместе с полной окрестностью, поступающей по линиям 21 и в блок 9 памяти, а блок опережающей подготовки данных сразу же приступает к вводу следующего фрагмента с его полной окрестностью.Узел 6 сдвига принимает значения элементов Фрагмента, поступающие по линиям 15 на выходы группы центральных коммутационных элементов 63, и значения полной окрестности Фрагмента, поступающие по линиям 21 на входыгруппы кромочных коммутационных элементов 63 в соответствии с установленным для этих ячеек кодом направления, которые фиксируются в П-триггерах 65.Затем в узле сдвига производится серия сдвигов обхода значений окрестности. Для значений ближайшей окрестности эта серия представляет следующую последовательность: сдвиг на одиншаг вверх, сдвиг на один шаг вправо,сдвиг на два шага вниз, сдвиг на двашага влево, сдвиг на два шага вверх.В результате в каждый коммутационныйэлемент б 3 центральной группы ячеекузла 6 двумерного сдвига поочереднозаписываются значения элементов Фрагмента, составляющие ближайшую окрестность элемента, записанного в этотэлемент первоначально,После каждого шага серии сдвиговобхода значений окрестности все коммутационные элементы 63 центральнойгруппы узла 6 сдвига выдают значенияэлементов окрестности на шину 15. Зна"чения окрестности элементов фрагментапо шине 15 поступают в блок 7 распознавания активных элементов кадра и в блок 9 памяти, где производится их Фиксация. Блок 7 распознавания активных элементов принимает значения окрестности элементов Фрагмента по линиям шины 15 на входы узлов 67 распоз"навания, Узлы 67 к данному моменту устанавливаются блоком 13 управления в следующее состояние: приемопередат" чик 68 открыт в направлении приема поступающих значений 107, 108, 109 окрестности, Элемент 69 задержки фиксирует каждое значение 107, 108, 109 окрестности и задерживает его на выходе до момента фиксации следующего значения окрестностиБлок 70 сравнивает задержанные значения 113, 114, 115 с текущими значениями 107, 108, 109. При наличии неравнозначности хотя бы в одной паре текущего и предыдущего значений во всей группе ок 153 ййббрестностных элементов результат сравнения фиксируется в аккумуляторе,образованном триггером 72 (триггеромрезультата распознавания) и элементом ИЛИ 71, и сохраняется до концапроцедуры распознавания. При этомдля предотвращения записи в аккумулятор недостоверного значения результата сравнения, возникающего в момент1 Опоступления первого элемента окрестности 107, триггер 72 памяти результата распознавания удерживается наэто время в исходном состоянии уровнем 111 сброса. После завершения вы 15полнения процедуры распознавания приемопередатчик 68 переводится в состояние приема зйачения результата распознавания, Таким образом, блок 7распознавания активных элементов Формирует двумерный массив битов активности, отмечающих элементы Фрагмента,имеющие информативную окрестность,т.е. окрестность, содержащую неравнозначные элементы. Элементы фрагмента, 2имеющие неинформативную окрестность,содержащую только однозначные элементы, являются неактивными и битами активности не отмечаются,Сформированный массив битов активности с блока 7 по шине 15 передается Ов блок 9 памяти, где Фиксируется ипередается по линиям 38 в матрицу 1 Оузлов обработки,В матрице 1 О узлов обработки припомощи блока Фиксации обнуления матрицы производится оценка активностивсего Фрагмента, Если массив битовактивности Фрагмента состоит из однихнулей, фрагмент является неактивным,т,е. обработке не подлежит; если в 40массиве есть хотя бы один бит активности, фрагмент является активным,Аналогичным образом непрерывно, одинза другим, вводятся следующие фрагменты, осуществляются процедура обхода окрестности каждого, Формированиемассива битов активности каждого,оценка активности каждого Фрагментаи запись собственно каждого Фрагмента, его массивов значений окрестности Ои его массива битов активности в блок9 памяти. Причем, если в результатеопределения активности фрагмента выясняется, что он неактивен и обработке не подлежит, блоки 13 и 12 управления организуют его пересылку из блока 9 памяти по линиям шины 15 в блок5 опережающей подготовки данных, ана место его размещения и размещения его массивов окрестности и битов активности в адресном пространстве блока 9 памяти записываются следующийФрагмент и, соответственно, его массивы окрестности и битов активности.Вывод результирующего Фрагмента сблока 5 опережающей подготовки данныхсовмещается во времени с вводом очередного фрагмента, так как при вводеочередного фрагмента сдвигом в узел62 через один из его краев с соответ"ствующих выходов коммутационных элементов 63 противоположного края выталкиваются строки выводимого резуль-,тирующего Фрагмента, которые черезсоответствующий приемопередатчик 59или 60 по линиям 16 через свободныйприемопередатчик 50 или 5 поступаютв элемент памяти узла 13 блока 2 задания Формата, где записываются поадресам, соответствующим адресам исходного считывания этого Фрагментаиз элемента ч 9 памяти блока 2 задания Формата, Одновременно с этим процессом с исключением моментов временизанятости матрицы узлов обработкиопределением активности фрагментовпроизводится процедура упаковки активных элементов очередных Фрагментовв подлежащую обработке порцию данныхс последующим выполнением очередногоэтапа алгоритма обработки одновременно всех упакованных в порцию активныхэлементов целого ряда Фрагментов. Процедура упаковки порции данных складывается из подготовки группы рабочихмасок активности данной группы активных Фрагментов, масок активных остатков и компоновки порции данных. Подготовка группы масок активных остатков производится следующим образом.Массив битов активности первого Фрагмента данной группы активных фрагментов считывается с блока 9 памяти по.линиям 38 и вводится в матрицу 10,где элементы данного массива фиксируются в аккумуляторах узлов 75 обработки. Затем считывается массив битовактивности второго фрагмента даннойгруппы активных фрагментов и в матрице 1 О выполняется конъюнкция соответствующих значений этих массивов. Результат конъюнкции, являющийся маской активного остатка второго фрагмента, проверяется на равенство нулювыводится из матрицы 10 по линиям 38и фиксируется в блоке 9 памяти, послечего в матрице 10 выполняется дизъюнкция соответствующих значений этих жемассивов битов активности первого и второго фрагментов с фиксацией резуль тата в аккумуляторах узлов 75 обработки, После этого с блока 9 памяти считывается массив битов активности5 третьего активного Фрагмента и выполняется конъюнкция его соответствующих значений и значений содержимого аккумуляторов матрицы 10, Результат конъюнкции, являющийся маской активного остатка третьего фрагмента, проверяется на равенство нулю и Фиксируется в блоке 9 памяти, после чего в матрице 10 выполняется дизъюнкция соответствующих значений массива битов активности третьего Фрагмента и содержимого аккумуляторов, результат которой заносится в аккумуляторы узлов 75. Эта процедура продолжается с четвертым, пятым и т.д.фрагментами аналогичным образом до момента появления критерия достаточности которым может служить в простейшем случае установленное максимальное число неравных нулю активных остатков, подсчитываемых блоком 13После достижения критерия достаточности блок 13 приступает к подготовке рабочих масок активности данной группы активных Фрагментов, для чего поочередно выполняет функцию неравнозначности элементов массивов битов активности с элементами соответствующих масок остатков данной группы активных Фрагментов в матрице 10 с фик- З 5 сацией полученных рабочих масок активности в блоке памяти, Далее массив битов активности первого Фрагмента поступает из матрицы элементов и по линиям 23 в блок 9 памяти, Одновремен 40 но блок 13 осуществляет считывание первого Фрагмента с блока 9 памяти по линиям 38 в матрицу 10, где значения его элементов Фиксируются в аккумуляторах узлов 75 обработки. При этом элементы считываемого фрагмента, не отмеченные битом активности, не считываются, и вместо них в матрицу 10 поступают нулевые значения, После этого блок 13 осуществляет аналогичное 50 маскирование соответствующей рабочей маской активности считывания с блоков 9 памяти следующего Фрагмента данной группы, ввод результата маскирования в матрицу 10, дизъюнкцию его у значений с соответствующими значениями, содержащимися в аккумуляторах узлов обработки, и Фиксацию полученного результата в те же аккумуляторы. Таким образом, производится логическоесложение неперекрывающихся активныхзон фрагментов данной группы. Областиперекрытия активных зон вместе с неактивными зонами отсекаются соответствующими масками активности всехфрагментов данной группы эа исключечением первого Фрагмента, для которого массив битов активности одновременно является рабочей маскойактивности, т.е. он не имеет активного остатка. После выполнения процедуры компоновки порции данных блок13 при помощи матрицы 1 О и блока 9памяти выполняет процедуры данногоэтапа обработки, Затем, аналогичноиспользуя те же рабочие маски активности и матрицу 8, блок 13 поочереднораспределяет обработанные зоны Фрагментов данной группы записью по соответствующим адресам ячеек блока 9памяти, Непосредственно после этогоблоки 12.и 13 обеспечивают пересылкуФрагментов, проведших обработку и неимеющих необработанных активных остатков, что характеризуется равенством нуле их масок активных остатков,с блока 9 памяти. по линиям шины 15в блок 5 опережающей подготовки данных, откуда они выводятся в элементпамяти узла Й 3, Одновременно оставшиеся необработанные активные остатки недообработанных фрагментов подвергаются повторной процедуре упаковки, При этом маски этих активных остатков используются как массивы битовактивности для оставшихся недоработанных Фрагментов первой группы. Кроме того, в процессе повторной упаков"ки оставшиеся фрагменты первой группыдополняются следующими не проходившими обработку Фрагментами до выполнения критерия достаточности,Полученная совокупность Фрагментовявляется второй группой фрагментов,образующих вторую порцию данных, подлежащих обработке. Аналогичным образом процедуры обработки данного этапавыполняются над всеми Фрагментами матрицы данных. Упаковка и обработка оставшихся активных остатков последнейгруппы Фрагментов матрицы данныхповторяется до момента их полной обработки, после чего блоки 12 и 13 переходят к следующему этапу обработки Фрагментов матрицы данных, При этом исходная,информация считывается черезсоответствующий приемопередатчик 50или 51 с элемента памяти того узла ч 21534 или 43, в котором зафиксирован результат предыдущего этапа обработки,После выполнения всех этих этапов обработки результирующая информация, находящаяся, например, в элементе 49 памяти, выводится на блок 1 ввода-вывода. 4 бб 14 ответственно к первому, второму итретьему управляющим входам блока опережающей подготовки данных, перваягруппа из и информационных входоввыходов которого подключена соответственно к первой группе из и информационных входов-выходов узла сдвига,соответственно к и информационнымвходам-выходам распознавания активныхэлементов кадра, соответственно к ивходам матрицы элементов И и соответственно к первой группе иэ а информационных входов - выходов блока памяти, вторая группа из и информационных входов - выходов которого подключена соответственно к и информационным входам-выходам матрицы узлов обработки, выходы с первого по и -йкоторой подключены к входам блока буФерных повторителей, выход которого подклюцен к входам режима первого и второго блоков управления, вторые инФормационные входы-выходы .которыхобъединены и подключены к управляющему входу-выходу матричного процессора, вторая группа из (Б - и), где И - линейный размер фрагмента обрабатываемого кадра с окрестностью, информационных входов-выходов блока опережающей подготовки данных подключена соответственно к второй группе из (И - и) информационных входов- выходов узла сдвига, третья группа из И информационных входов-выходов узла сдвига объединена с четвертой и пятой группами по И информационных входов-выходов в каждой узла сдвига и подключена соответственно к шестой группе из И информационных входов-выходов узла сдвига, выходы с первого по и-й матрицы элементов И подключены соответственно к информационным, входам с первого по и -й блока памяти, второй и третий выходы второго блока управления подключены соответственно к первому и второму управляющим входам узла сдвига, с четвертого по шестой выходы второго блока управ" ления подключены соответственно к первому, второму и третьему управляющим входам блока распознавания активных элементов кадра, седьмой выход второго блока управления подключен к управляющему входу матрицы элементов И, с восьмого по тринадцатый выходы второго блока управления подключены соответственно к первому, второму, третьему управляющим входам первой группы и к первому, второму и третьеФормула изобретения1 О Матричный процессор, содержащийблок ввода-вывода, двунаправленный коммутатор, блок фрагментации, первый и второй блоки управления и матрицу размером и х и узлов обработки, где , п - линейный размер фрагмента обрабатываемого кадра, прицем с первого по третий выходы первого блока управления подключены соответственно к уп 20 равляющим входам с первого по третий двунаправленного коммутатора, четвертый и пятый выходы первого блока управления подключены соответственно к первому и второму управляющим входам блока Фрагментации, информационный вход которого подключен к выходу двунаправленного коммутатора, первый выход второго блока управления под" ключен к управляющему входу матрицы узлов обработки, первый информацион" ный вход-выход первого блока управления подключен к первому информацион. ному входу-выходу второго блока уп" равления, о т л и ц а ю щ и й с я тем, что, с целью повышения быстро действия устройства, в него введены блок задания Формата, блок опережающей подготовки данных, узел сдвига, блок распознавания активных элементов кадра, матрица размером о х и элемен" 40 тов И, блок памяти и блок буферных повторителей, при этом выходы с шестого по двенадцатый первого блока управления подключены к управляющим вхо" дам с первого по пятнадцатый блока 45 задания Формата, с первого по третий информационные входы-выходы которого подключены соответственно к первому и второму информационным входам-выходам двунаправленного коммутатора, ин формационный вход которого подключен к выходу блока опережающей подготовки данных, с первого по третий информационные входы которого подключены соответственно к первому, второму и 55 третьему выходам блока фрагментации данных, двадцать первый, двадцать второй и двадцать третий выходы пер вого блока управления подклюцены сому управлядщим ях дам вт рой группыблока памяти,2, Процессор по п,1, о т л и л аю щ и й с я тем, что блок задания5формата содержит два счетчика, дваузла памяти, два сдвигающих регистра,два элемента НГ и две группы по дваприемопередатчика в каждой, причемпервый и второй информационные входывыходы блока подключены соответст венно к информационным входам-выходампервого и второго приемопередатчиковпервой группы, первый управляющий входблока подключен к входу сдвига перво"го сдвигающего регистра и к первомууправляющему входу первого приемопередатчика первой группы, второй управляющий вход блока подключен к входусдвига второго сдвигающего регистраИ к первому управляющему входу второго приемопередатчика первой группы,третий управляющий вход блока подключен к управляющему входу первого приемопередатчика второй группы и к входу первого элемента НЕ, выход которого подключен к второму управляющемувходу первого приемопередатчика первой группы, четвертый управляющийвход блока подключен к управляющемувходу второго приемопередатчика второй группы и к входу второго элемента НЕ, выход которого подключен квторому управляющему входу второго. приемопередатчика первой группы, пятый управляющий вход блока подключен 35к информационным входам первого ивторого счетчиков, выходы которыхподключены соответственно к адреснымвходам первого и второго узлов памяти, управляющие входы с шестого по40пятнадцатый блока подключены соответственно к входам записи-чтенияпервого и от рого узлов памяти, квходам синхронизации первого и второго узлов памяти, к входам синхронизации первого и второго счетчиков ксчетным входам первого и второгосчетчиков и к входам синхронизациипервого и второго сдвигающих регистров, выход переноса первого сдвигающего регистра подключен к информационному входу первого приемопередатчика первой группы и к первому информационному входу первого приемопередатчика второй группы, выход переноса 55второго сдвигающего регистра подключен к информационному входу второгоприемопередатчика первой группы и кпервому информационному входу вторс -г приемопередат ика второй группы, выходы первых приемопередатчиков первой и второй групп подключены соответственно к первому и второму информационным входам первого сдвигающето регистра, выход которого подключен к информационному входу первого приемопередатчика второй группы, выходы вторых приемопередатчиков первой и второй групп подключены соответственно к первому и второму информационным входам второго сдвигающего регистра, выход которого подключен к информационному входу второго приемопередатчика второй группы, информационный вход- выход первого приемопередатчика второй группы объединен с входом-выходом первого узла памяти и подключен к третьему информационному входу-выходу блока, информационный вход-выход второго приемопередатчика второй группы объединен с входом-выходом второго узла памяти и подключен к четвертому информационному входу-выходу блока,3. Процессор по п,1, о т л и ч а ю щ и й с я тем, что блок опережающей подготовки данных содержит узел сдвига, два приемопередатчика четыре ключа и элемент НЕ, при этом первый управляющий вход блока подключенвходу элемента НЕ и к управляющим входам первого ключа, второго ключа и первого приемопередатчика, второй и третий управляющие входы блока подключены соответственно к первому и второму управляющим входам узла сдвига, выход элемента НЕ подключен к управляющим входам третьего ключа, второго приемопередатчика и четвертого ключа, первый информационный вход блока подключен к информационным входам второго и четвертого ключей, второй информационный вход блока подключен к информационным входам первого и второго приемопередатчиков, выходы которых объединены и подключены к выходу блока, третий информационный вход блока подключен к информационным входам первого и тре" тьего ключей, первая группа из и информационных входов-выходов узла сдвига подключена соответственно к первой группе из п информационных входов-выходов блока, вторая группа из (Б - л) информационных входов- выходов узла сдвига подключена соответственно к второй группе из (И - и) информационных входов-выходов блока, третья Группа из п информационныхвходов-выходов узла сдвига объединена соответственно с четвертой группой из и информационных входов-выходов узла сдвига и подключена соответственно к и входам-выходам второго приемопередатчика, пятая группа из и информационных входов-выходов узла сдвига объединена соответственно с шестой группой из и информационных10 входов-выходов узла сдвига и подключена соответственно к и входам-выходам первого приемопередатчика, седьИ - имая группаинформационных2 15входов-выходов узла сдвига объединенасоответственно с восьмой группой изИ - иинформационных входов-выходов2узла сдвига и подключена соответственИ - . ино квыходам третьего ключа,11 - идевятая группа изинформацион 225 ных входов-выходов узла сдвига объединена соответственно с десятой группойИизинформационных входов-выходов узла сдвига и подключена соответст- З 0И. - ивенно квыходам четвертого2Ю-иключа, одиннадцатая группа из (2)информационных входов-выходов узласдвига объединена соответственно с З 5И-идвенадцатой группой из (-") инфор 2мационных входов-выходов узла сдвигаЦ-и 40и подключена соответственно кГ - и Б - и1 + и 32Ч - и-а второй управляющийвход узла подключен к управляющим входам остальных коммутационных элементов матрицы, первый информационный вход-выход коммутационного элемента К-й строки 1-го столбца матрицы (где К = 1.1,", 1 =, И) подключен к второму информационному входу- выходу коммутационного элемента К-й строки (1-1)-го столбца матрицы, третий информационный вход-выход коммутационного элемента р-й строки и-го столбца матрицы, (где р = 2,Ч = 1, , М) подключен к четвертому информационному входу-выходу коммутационного элемента (р) -й строки 1-го столбца матрицы, третьи информационные входы-выходы коммутационных элеИ - иментов первой строки с ( + 1) -го2И-ипо ( + и) -го столбца матрицы под 2ключены соответственно к и информационным входам-выходам третьей группы матрицы, первые информационные входы- выходы коммутационных элементов перИ - ивого столбца с ( + 1)-й по2И - и(+ и) -ю строк матрицы подключены2соответственно к и информационным входам-выходам четвертой группы матрицы, вторые информационные входы- выходы коммутационных элементов И-гоИ - истолбца с ( + 1)-й по ( + и)-ю 22И-игруппа изинформационных вхо 245дов-выходов узла сдвига объединенасоответственно с четырнадцатой групиз (ч) информационных входов-выхо - и 2 выходам первого ключа, тринадцатая К-ипой изинформационных входов 2. выходов узла сдвига и подключена со И-иответственно квыходам вто 2рого ключа, при этом узел сдвига со-держит матрицу размером И х И элементов коммутации, причем первый управляющий вход подключен к управляющим входам коммутационных элементов 1-й строки 1-го столбца матрицы (где строк матрицы подключены соответственно к И информационным входам-выходам пятой группы матрицы четвертые информационные входы-выходы коммутационных элементов И-й строки с И-и И - и(+1)-го по (+и)-й столбцов2 2 матрицы подключены соответственно к и информационным входам-выходам шестой группы матрицы, третьи информационные входы-выходы коммутационных элементов первой строки столбцовМ - ис ( + и + 1) -го по Л-й подключе 2ны соответственно к седьмой группе

СмотретьЗаявка

4342671, 14.12.1987

СПЕЦИАЛИЗИРОВАННОЕ ПРОЕКТНО-КОНСТРУКТОРСКОЕ БЮРО АВТОМАТИЗИРОВАННЫХ СИСТЕМ УПРАВЛЕНИЯ "КИБЕРНЕТИКА"

КОРОБКИН ВЯЧЕСЛАВ МИХАЙЛОВИЧ, СИТНИКОВ АЛЕКСЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 15/173

Опубликовано: 07.01.1990

Код ссылки

<a href="https://patents.su/18-1534466-matrichnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Матричный процессор</a>

Предыдущий патент: Селекторный канал

Следующий патент: Моделирующий элемент вероятностного графа

Случайный патент: Состав стекла для герметизации