Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1361572

Автор: Минутин

Текст

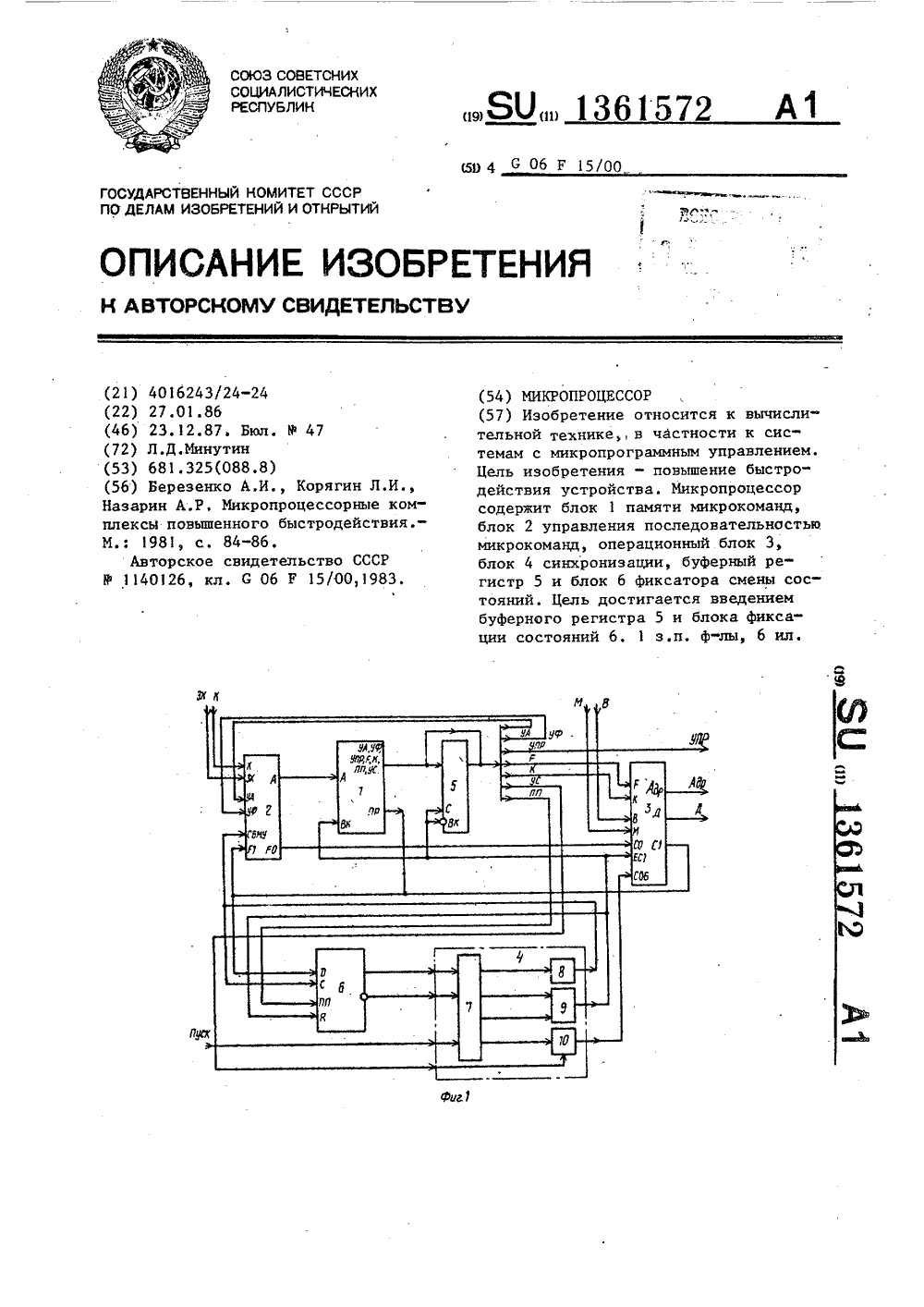

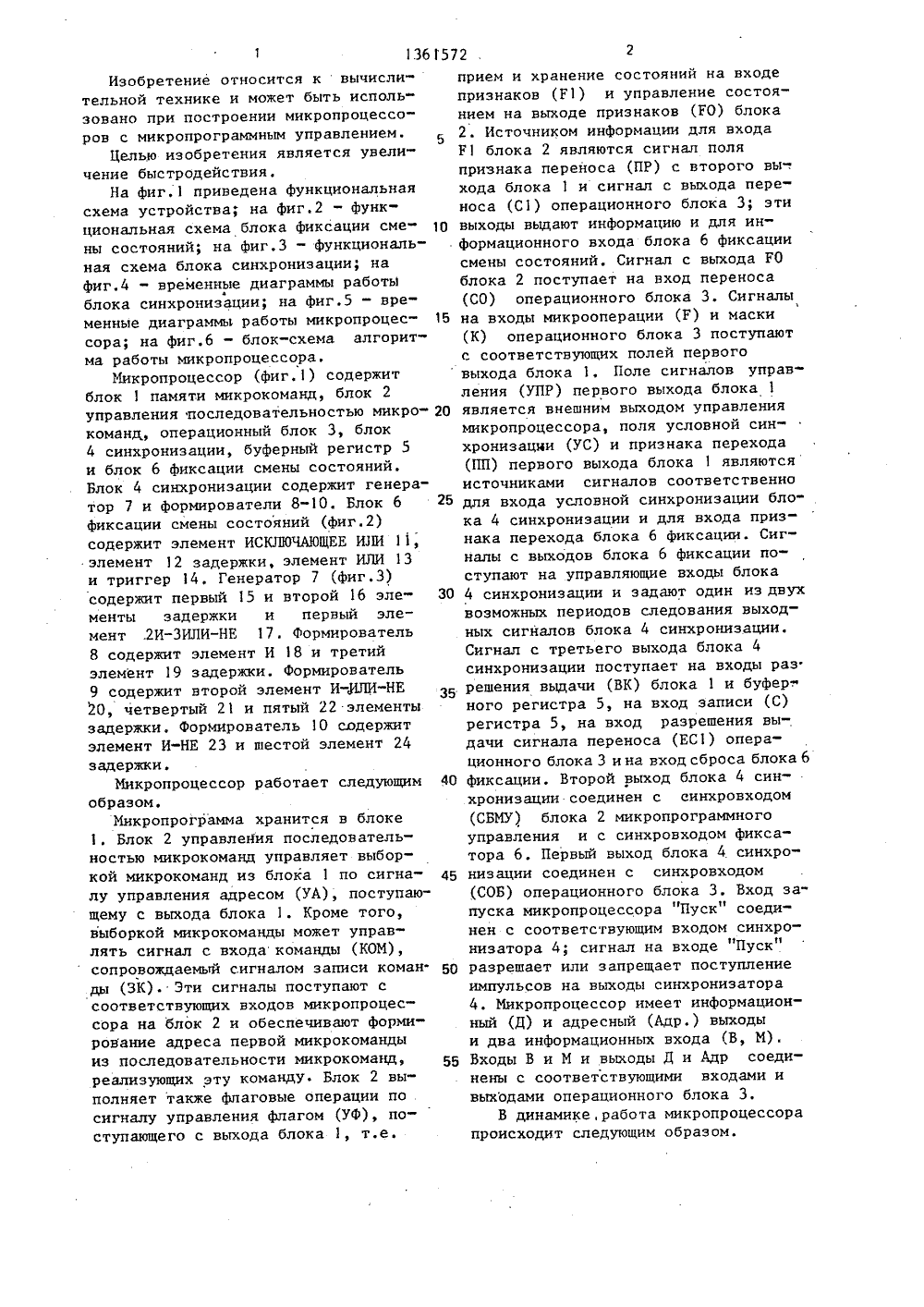

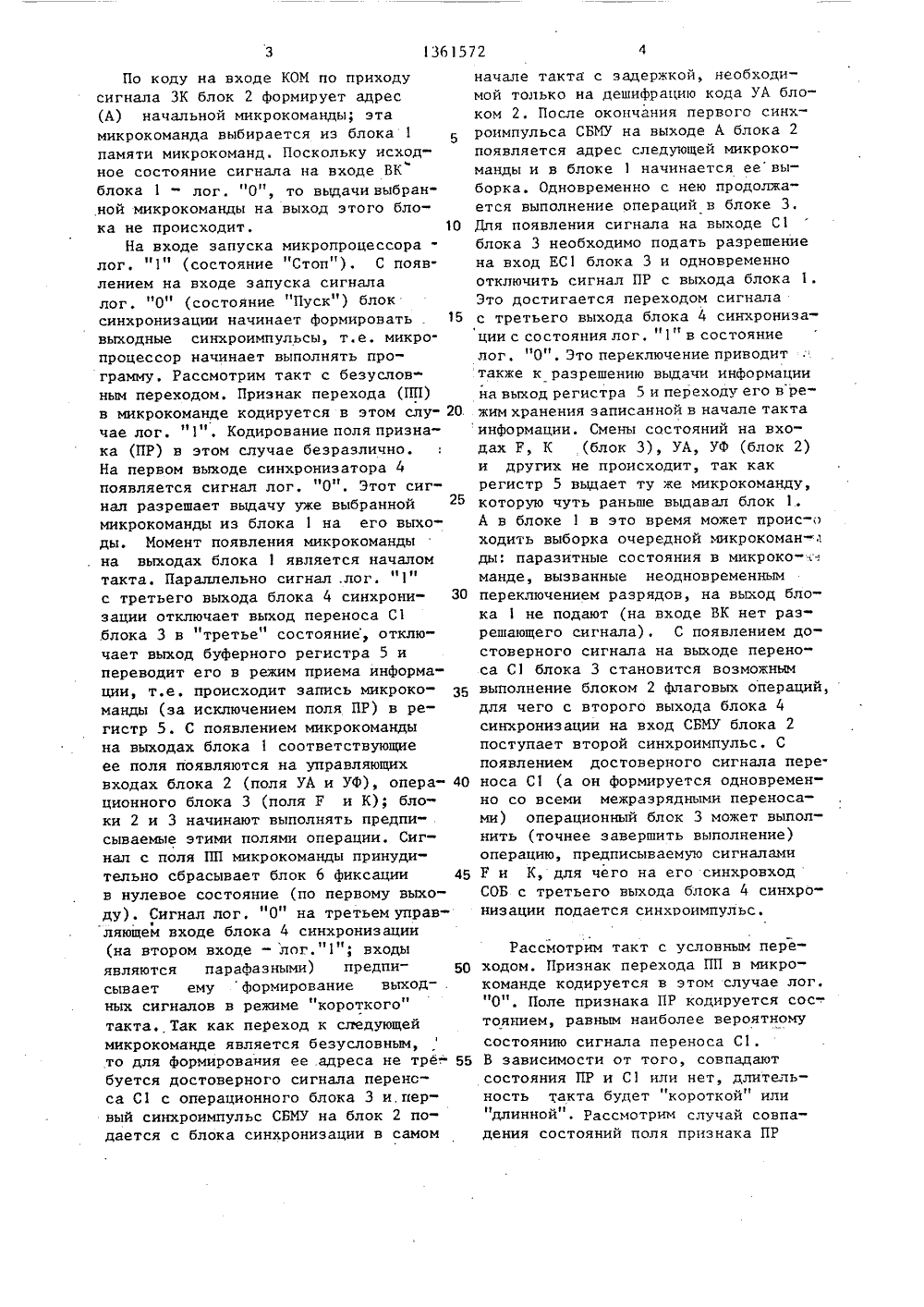

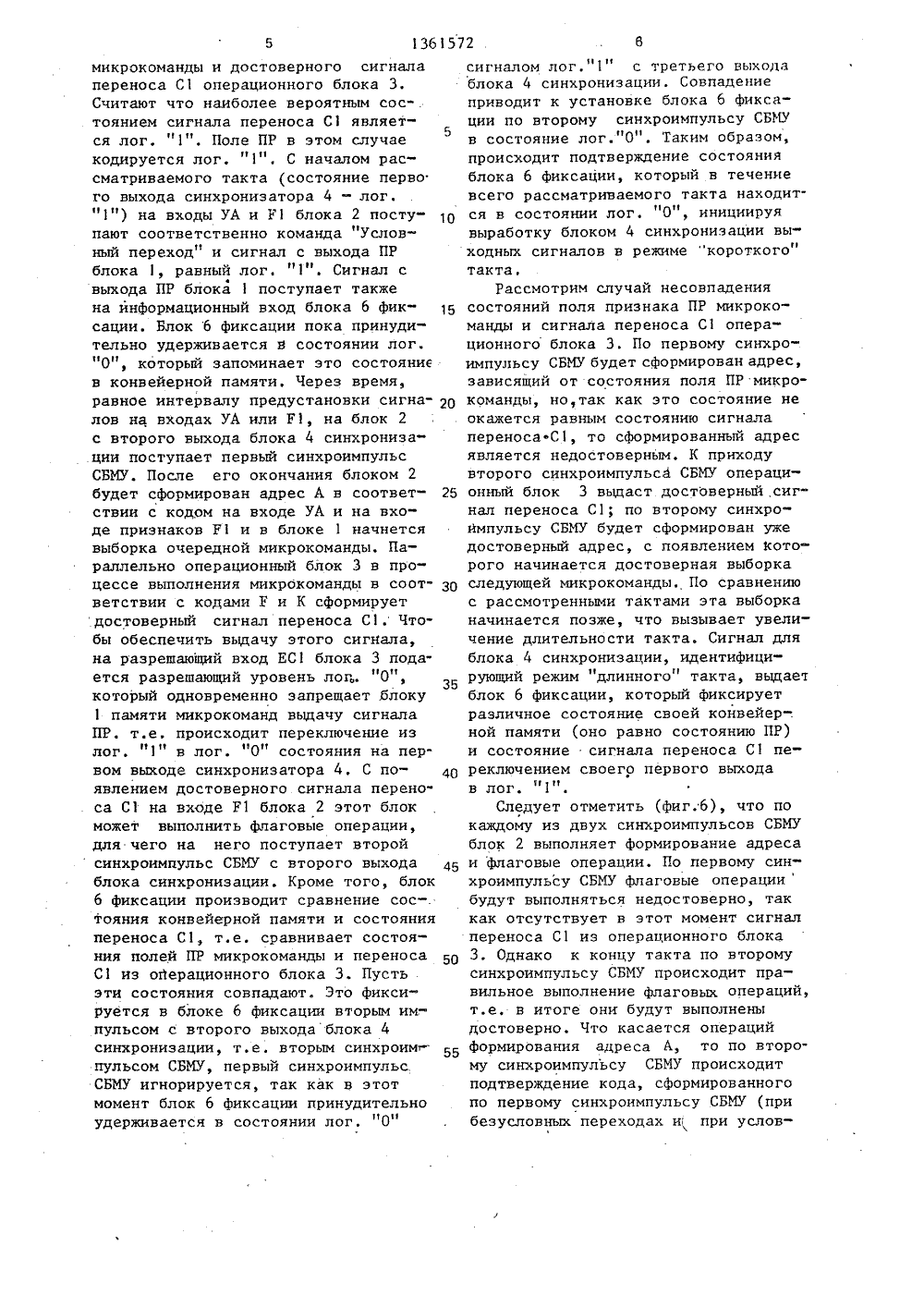

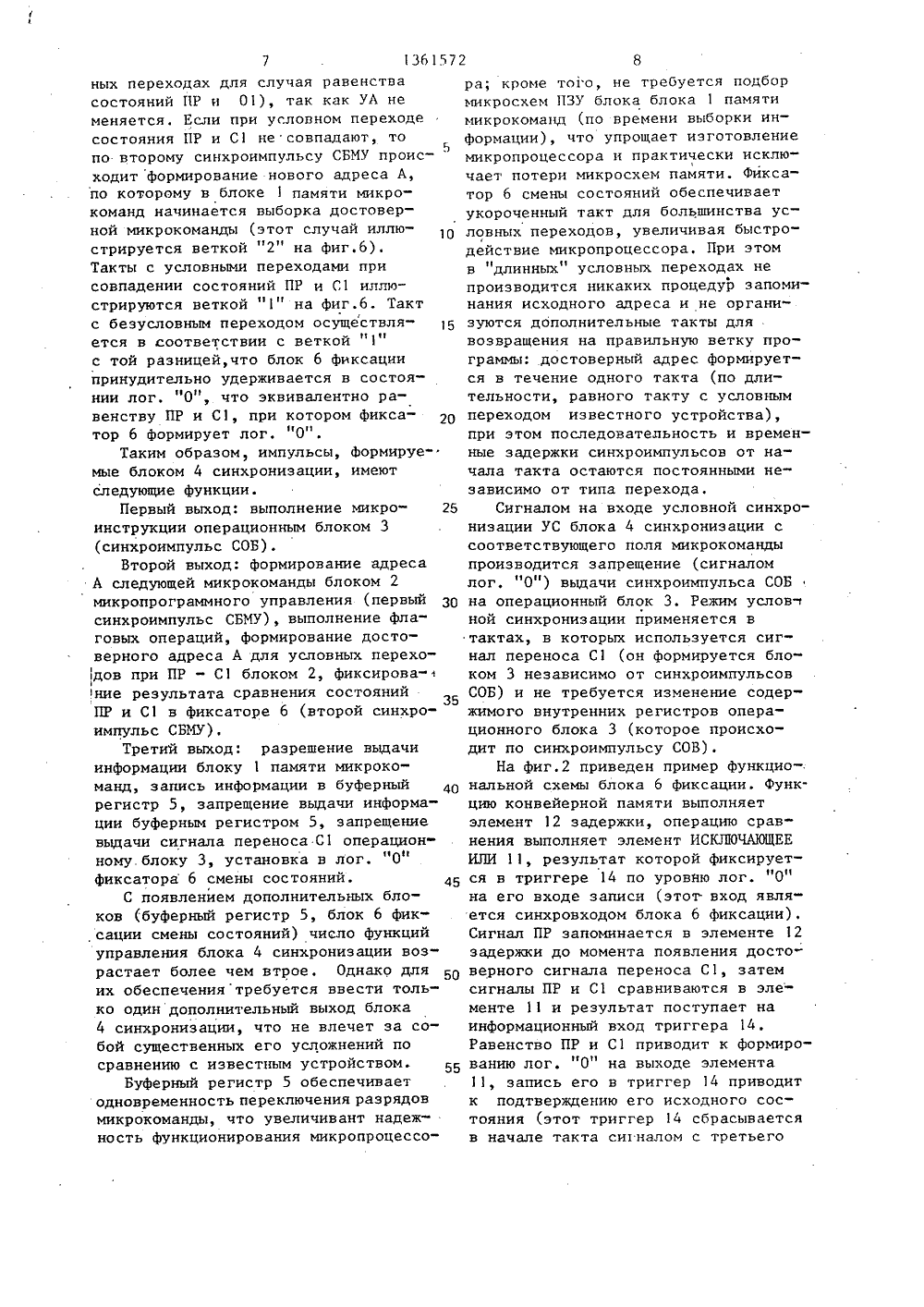

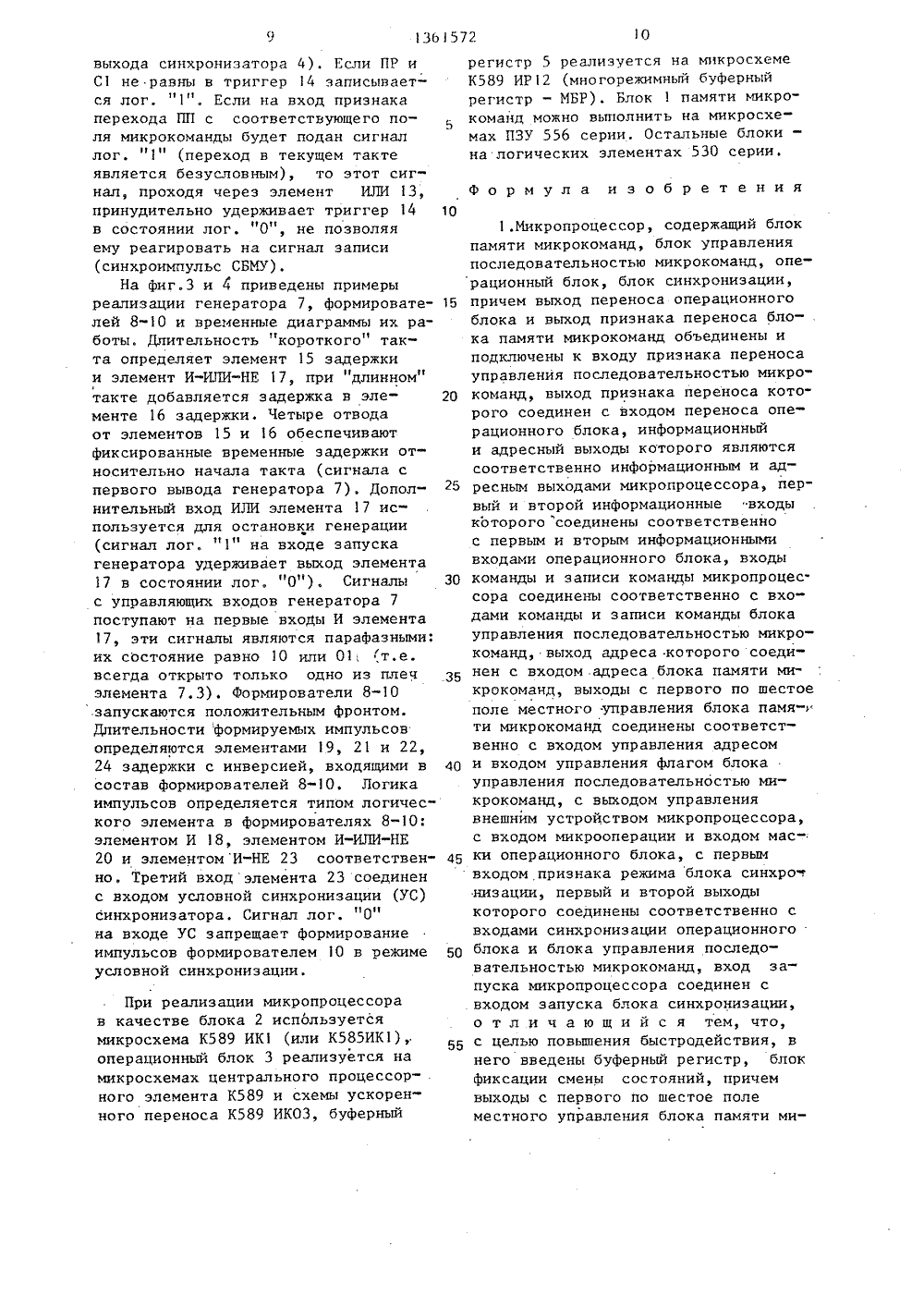

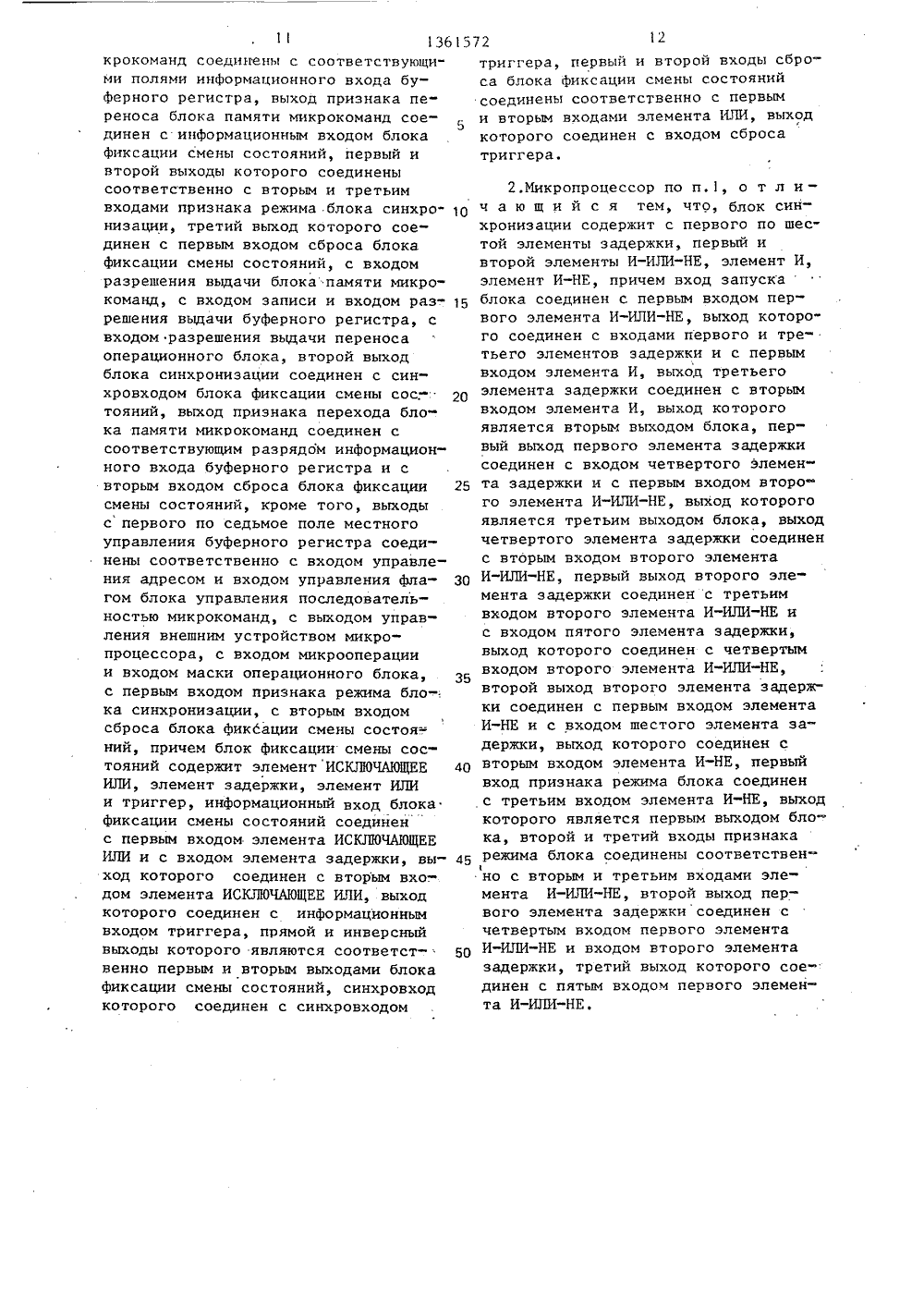

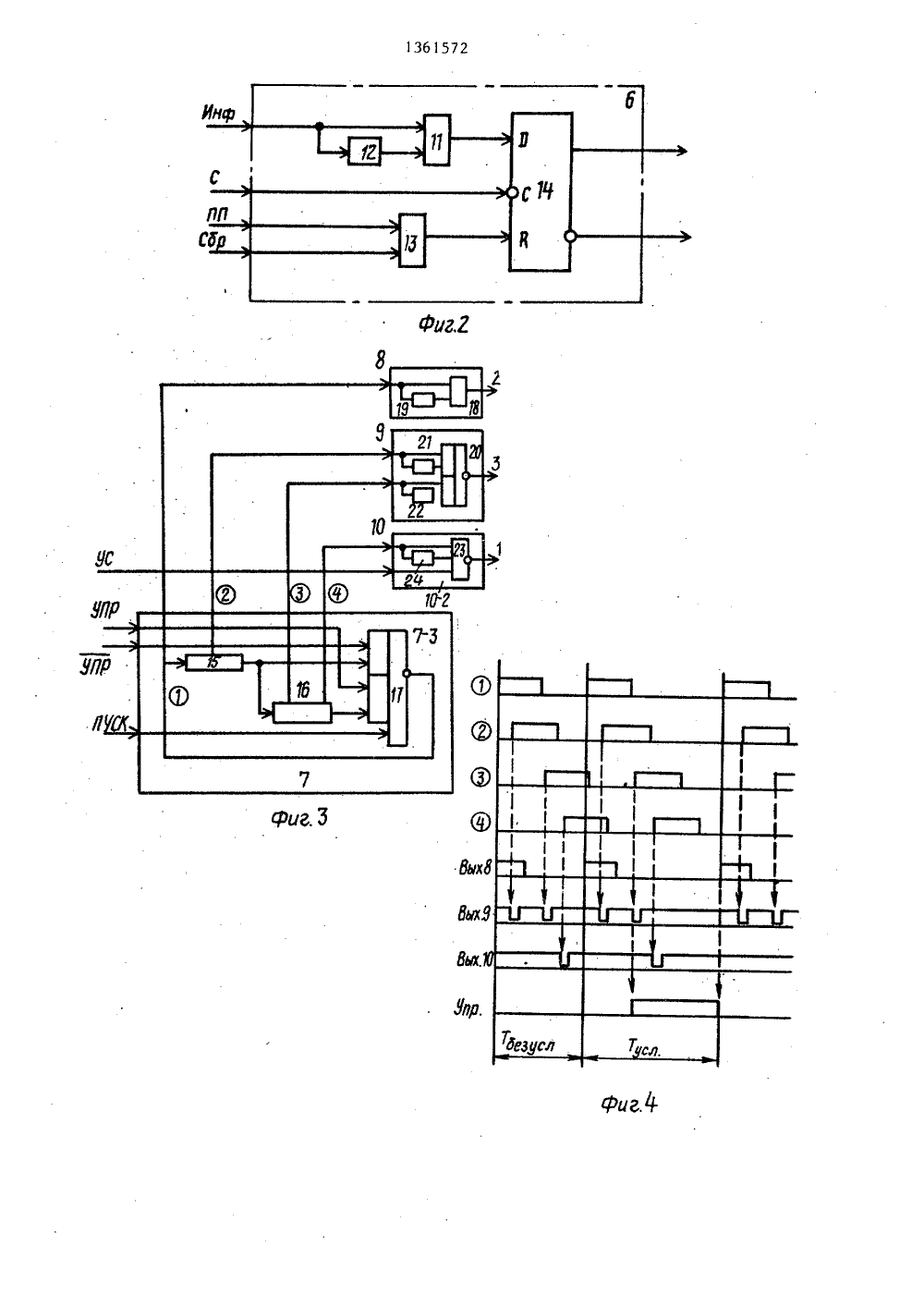

-2 Б)0 л. ство СССР 15/00,1983 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ(57) Изобретение относится к вычислительной технике в частности к системам с микропрограммным управлением.Цель изобретения - повышение быстродействия устройства. Микропроцессорсодержит блок 1 памяти микрокоманд,блок 2 управления последовательностьюмикрокоманд, операционный блок 3,блок 4 синхронизации, буферный регистр 5 и блок 6 фиксатора смены состояний. Цель достигается введениембуферного регистра 5 и блока фиксации состояний 6, 1 з.п. ф-лы, 6 ил.1361572 КОМ Выбрана начальная мцкрономан 0 а Ййсалзор Об намял Начло Ь 5 ормцкро- ки микрокомакоаад ды Фкса- Сраднение тор состояний синхро. При С 1 и ксцр, 3 е,Аьпи ПР и П ра 3 нь1 процзошло подтдерждеице од- едреса микроиои.Я =Ф Насахо ыборадостодерноймикаиаюанйгпе аоресуАЗа ершениеЖоркимикрококанЬ ЙР 1 ЯП 2 ь ЩЮ- омане Составитель А.СошкинТехред А,Кравчук Корректор И.Пожо Редактор В.Бугренкова Заказ 6292/49 Тираж 671 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий1.13035 Москва, Ж, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 бмУ 1.ый сцнх цип. бМУ Я- ц синх оп Рормроданцеадреса,4 Оедуюи 1 ец" мцккеманды Выполнениецыагооык оперФориира даниеадреса А микрокоманды йммь мцкро- оюэд ЗапоминаниесостоянияПР Память цК,ОО" коиондНачало девиграции милроинструкииРормиро аниесигнал пеНОСа С 1 Выполнениесиарз микроинсщр.цмп,Зодеошенцеоыборкииилрокоман 0 ыИзобретение относится квычислительной технике и может быть использовано при построении микропроцессоров с микропрограммным управлением.Целью изобретения является увеличение быстродействия.На фиг.1 приведена функциональнаясхема устройства; на фиг,2 - функциональная схема блока фиксации смены состояний; на фиг.З - функциональная схема блока синхронизации; нафиг.4 - временные диаграммы работь 1блока синхронизации; на фиг.5 - временные диаграммы работы микропроцессора; на фиг.6 - блок-схема алгоритма работы микропроцессора.Микропроцессор (фиг.1) содержитблок 1 памяти микрокоманд, блок 2управления последовательностью микрокоманд, операционный блок 3, блок4 синхронизации, буферный регистр 5и блок 6 фиксации смены состояний.Блок 4 синхронизации содержит генера"тор 7 и формирователи 8-10. Блок 6фиксации смены состояний (фиг.2)содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11,элемент 12 задержки, элемент ИЛИ 13и триггер 14. Генератор 7 (фиг.З)содержит первый 15 и второй 16 элементы задержки и первый элемент .2 И-ЗИЛИ-НЕ 17. Формирователь8 содержит элемент И 18 и третийэлемент 19 задержки. Формирователь9 содержит второй элемент И-ИЛИ-НЕ20, четвертый 21 и пятый 22 элементызадержки. Формирователь 10 содержитэлемент И-НЕ 23 и шестой элемент 24задержки,Микропроцессор работает следующимобразом.Микропрограмма хранится в блоке1, Блок 2 управления последовательностью микрокоманд управляет выборкой микрокоманд из блока 1 по сигналу управления адресом (УА), поступающему с выхода блока 1. Кроме того,выборкой микрокоманды может управлять сигнал с входа команды (КОМ),сопровождаемый сигналом записи коман"ды (ЗК). Эти сигналы поступают ссоответствующих входов микропроцессора на блок 2 и обеспечивают формирование адреса первой микрокомандыиз последовательности микрокоманд,реализующих эту команду Блок 2 выполняет также флаговые операции посигналу управления флагом (УФ), поступающего с выхода блока 1, т.е.возможных периодов следования выходных сигналов блока 4 синхронизации.Сигнал с третьего выхода блока 4 синхронизации поступает на входы раз. З 5 решения выдачи (ВК) блока 1 и буфер,ного регистра 5, на вход записи (С) регистра 5, на вход разрешения выдачи сигнала переноса (ЕС 1) операционного блока 3 и на вход сброса блока 6 40 45 50 55 1015 2030 прием и хранение состояний на входе признаков (Р 1) и управление состоянием на выходе признаков (РО) блока 2. Источником информации для входа Р 1 блока 2 являются сигнал поля признака переноса (ПР) с второго вы-. хода блока 1 и сигнал с выхода переноса (С 1) операционного блока 3; этивыходы вьщают информацию и для информационного входа блока 6 фиксациисмены состояний. Сигнал с выхода РОблока 2 поступает на вход переноса(СО) операционного блока 3. Сигналына входы микрооперации (Р) н маски (К) операционного блока 3 поступают с соответствующих полей первого выхода блока 1. Поле сигналов управления (УПР) первого выхода блока 1 является внешним выходом управления микропроцессора, поля условной синхронизации (УС) и признака перехода (ПП) первого выхода блока 1 являются источниками сигналов соответственнодля входа условной синхронизации блока 4 синхронизации и для входа признака перехода блока 6 фиксации. Сигналы с выходов блока 6 фиксации поступают на управляющие входы блока4 синхронизации и задают один из двух фиксации. Второй выход блока 4 синхронизации соединен с аинхровходом (СБМУ) блока 2 микропрограммного управления и с синхровходом фиксатора 6. Первый выход блока 4 синхронизации соединен с синхровходом (СОБ) операционного блока 3. Вход запуска микропроцессора "Пуск" соединен с соответствующим входом синхронизатора 4; сигнал на входе "Пуск" разрешает или запрещает поступление импульсов на выходы синхронизатора 4. Микропроцессор имеет информационный (Д) и адресный (Адр.) выходы и два информационных входа (В, М). Входы В и М и выходы Д и Адр соединены с соответствующими входами и выходами операционного блока 3.В динамике, работа микропроцессора происходит следующим образом.По коду на входе КОМ по приходу сигнала ЗК блок 2 формирует адрес (А) начальной микрокоманды; эта микрокоманда выбирается из блока 1 памяти микрокоманд, Поскольку исходное состояние сигнала на входе ВК блока 1 - лог. "О", то выдачи выбранной микрокоманды на выход этого блока не происходит. 10На входе запуска микропроцессоралог. "1" (состояние "Стоп" ). С появлением на входе запуска сигнала лог. "О" (состояние "Пуск" ) блок синхронизации начинает формировать . 15 выходные синхроимпульсы, т.е, микропроцессор начинает выполнять программу. Рассмотрим такт с безусловным переходом. Признак перехода (ПП) в микрокоманде кодируется в этом слу чае лог. "1", Кодирование поля признака (ПР) в этом случае безразлично. На первом выходе синхронизатора 4 появляется сигнал лог. "О". Этот сигнал разрешает выдачу уже выбранной микрокоманды из блока 1 на его выходы. Момент появления микрокоманды на выходах блока 1 является началом такта. Параллельно сигнал .лог. "1" с третьего выхода блока 4 синхрони зации отключает выход переноса С 1 ,блока 3 в "третье" состояние, отключает выход буферного регистра 5 и переводит его в режим приема информации, т.е. происходит запись микрокоманды (за исключением поля ПР) в регистр 5. С появлением микрокоманды на выходах блока 1 соответствующие ее поля появляются на управляющих входах блока 2 (поля УА и Уф), опера ционного блока 3 (поля Р и К); блоки 2 и 3 начинают выполнять предписываемые этими полями операции. Сигнал с поля ПП микрокоманды принудительно сбрасывает блок 6 фиксации 45 в нулевое состояние (по первому выходу). Сигнал лог, "О" на третьем управляющем входе блока 4 синхронизации (на втором входе - лог."1"; входы являются парафазными) предпи сывает емуформирование выход- . ных сигналов в режиме "короткого" такта. Так как переход к следующей микрокоманде является безусловным, то для формирования ее .адреса не тре+ 55 буется достоверного сигнала переноса С 1 с операционного блока 3 и.первый синхроимпульс СБМУ на блок 2 подается с блока синхронизации в самом начале такта с задержкой, необходимой только на дешифрацию кода УА блоком 2, После окончания первого синхроимпульса СБМУ на выходе А блока 2появляется адрес следующей микрокоманды и в блоке 1 начинается еевыборка. Одновременно с нею продолжается выполнение операций в блоке 3,Для появления сигнала на выходе С 1блока 3 необходимо подать разрешениена вход ЕС 1 блока 3 и одновременноотключить сигнал ПР с выхода блока 1.Это достигается переходом сигналас третьего выхода блока 4 синхронизации с состояния лог. "1" в состояниелог, "О". Это переключение приводиттакже к разрешению выдачи информациина выход регистра 5 и переходу его врежим хранения записанной в начале тактаинформации. Смены состояний на входах Р, К (блок 3), УА, Уф (блок 2)и других не происходит, так какрегистр 5 выдает ту же микрокоманду,которую чуть раньше выдавал блок 1А в блоке 1 в это время может проис-оходить выборка очередной микрокоман-ды: паразитные состояния в микроко-".манде, вызванные неодновременнымпереключением разрядов, на выход блока 1 не подают (на входе ВК нет разрешающего сигнала). С появлением достоверного сигнала на выходе переноса С 1 блока 3 становится возможнымвыполнение блоком 2 флаговых операций,для чего с второго выхода блока 4синхронизации на вход СБМУ блока 2поступает второй синхроимпульс. Споявлением достоверного сигнала пере.носа С 1 (а он формируется одновременно со всеми межразрядными переносами) операционный блок 3 может выполнить (точнее завершить выполнение)операцию, предписываемую сигналамиР и К, для чего на его синхровходСОБ с третьего выхода блока 4 синхронизации подается синхроимпульс. Рассмотрим такт с условным переходом. Признак перехода ПП в микрокоманде кодируется в этом случае лог. "О". Поле признака ПР кодируется сос-. тоянием, равным наиболее вероятному состоянию сигнала переноса С 1.В зависимости от того, совпадают состояния ПР и С 1 или нет, длительность такта будет "короткой" илидлиннои . Рассмотрим случай совпадения состояний поля признака ПРмикрокоманды и достоверного сигнала переноса С 1 операционного блока 3. Считают что наиболее вероятным сос-. тоянием сигнала переноса С 1 является лог. "1". Поле ПР в этом случае кодируется лог, "1". С началом рассматриваемого такта (состояние перво го выхода синхронизатора 4 - лог. "1") на входы УА и Е блока 2 поступают соответственно команда "Условный переход" и сигнал с выхода ПР блока 1, равный лог, "1"Сигнал с выхода НР блока 1 поступает также на информационный вход блока 6 фиксации. Блок 6 фиксации пока принудительно удерживается в состоянии лог. "О", который запоминает это состояние в конвейерной памяти. Через время, равное интервалу предустановки сигналов на входах УА или Г 1, на блок 2 с второго выхода блока 4 синхронизации поступает первый синхроимпульс СБМУ. После его окончания блоком 2 будет сформирован адрес А в соответствии с кодом на входе УА и на входе признаков Р 1 и в блоке 1 начнется выборка очередной микрокоманды. Параллельно операционный блок 3 в процессе выполнения микрокоманды в соответствии с кодами Р и К сформирует достоверный сигнал переноса С 1. Чтобы обеспечить выдачу этого сигнала, на разрешающий вход ЕС 1 блока 3 пода" ется разрешающий уровень лог. "О", который одновременно запрещает блоку 1 памяти микрокоманд выдачу сигнала ПР, т.е, происходит переключение из лог. "1" в лог. "О" состояния на первом выходе синхронизатора 4, С появлением достоверного сигнала перено" са С 1 на входе Р блока 2 этот блок может выполнить флаговые операции, для чего на него поступает второйсинхроимнульс СБМУ с второго выхода блока синхронизации. Кроме того, блок 6 фиксации производит сравнение сос-. тояния конвейерной памяти и состояния переноса С 1 т.е. сравнивает состояния полей ПР микрокоманды и переноса С 1 из операционного блока 3. Пусть эти состояния совпадают. Это фиксируется в блоке 6 фиксации вторым импульсом с второго выхода блока 4 синхронизации, т.е. вторым синхроимтпульсом СБМУ, первый синхроимпульс СБМУ игнорируется, так как в этот момент блок 6 фиксации принудительно удерживается в состоянии лог, "О" 5 1 О 15 20 25 30 35 40 45 50 55 сигналом лог."1 с третьего выходаблока 4 синхронизации. Совпадениеприводит к установке блока 6 фиксации по второму синхронмпульсу СБИУв состояние лог."О". Таким образом,происходит подтверждение состоянияблока 6 фиксации, который в течениевсего рассматриваемого такта находится в состоянии лог. "О", инициируявыработку блоком 4 синхронизации выходных сигналов в режиме "короткого"такта,Рассмотрим случай несовпадениясостояний поля признака ПР микрокоманды и сигнала переноса С 1 операционного блока 3. По первому синхроимпульсу СБМУ будет сформирован адрес,зависящий от состояния поля ПР микро"команды, но,так как это состояние неокажется равным состоянию сигналапереносафС 1, то сформированный адресявляется недостоверным. К приходувторого синхроимпульсй СБМУ операционный блок 3 выдаст достоверный .сигнал переноса С 1; по второму синхроимпульсу СБМУ будет сформирован ужедостоверный адрес, с появлением которого начинается достоверная выборкаследующей микрокоманды, По сравнениюс рассмотренными тактами эта выборканачинается позже, что вызывает увеличение длительности такта. Сигнал дляблока 4 синхронизации, идентифицирующий режим "длинного" такта, выдаетблок 6 фиксации, который фиксируетразличное состояние своей конвейер-.ной памяти (оно равно состоянию ПР)и состояние сигнала переноса С 1 переключением своего первого выходав лог. "1".Следует отметить (фиг;6), что покаждому из двух синхроимпульсов СБМУблок 2 выполняет формирование адресаи флаговые операции. По первому синхроимпульсу СБМУ флаговые операциибудут выполняться недостоверно, таккак отсутствует в этот момент сигналпереноса С 1 из операционного блока3. Однако к концу такта по второмусинхроимпульсу СБМУ происходит правильное выполнение флаговых операций,т.е, в итоге они будут выполненыдостоверно. Что касается операцийформирования адреса А, то по второму синхроимпульсу СБМУ происходитподтверждение кода, сформированногопо первому синхроимпульсу СБМУ (прибезусловных переходах и при услов 7 1 Зб 1572 8ных переходах для случая равенства состояний ПР и 01), так как УА не меняется. Если при условном переходе состояния ПР и С 1 не совпадают, то5 по второму синхроимпульсу СБМУ проис-ходит формирование нового адреса А, по которому в блоке 1 памяти микро- команд начинается выборка достоверной микрокоманды (этот случай иллюстрируется веткой "2" на фиг.б). Такты с условными переходами при совпадении состояний ПР и С 1 иллюстрируются веткой "1" на фиг.б. Такт с безусловным переходом осуществляется в соответствии с веткой "1с той разницей,что блок 6 фиксации принудительно удерживается в состоянии лог. "О", что эквивалентно равенству ПР и С 1, при котором фиксатор 6 формирует лог. "О".Таким образом, импульсы, формируемые блоком 4 синхронизации, имеют следующие функции.Первый выход: выполнение микро инструкции операционным блоком 3 (синхроимпульс СОБ).Второй выход: формирование адреса А следующей микрокоманды блоком 2 микропрограммного управления (первый синхроимпульс СБМУ), выполнение флаговых операций, формирование достоверного адреса А для условных переходов при ПР - С 1 блоком 2, фиксирова- ние результата сравнения состояний ПР и С 1 в фиксаторе 6 (второй синхроимпульс СБМУ).Третий выход: разрешение выдачи информации блоку 1 памяти микрокоманд, запись информации в буферный 40 регистр 5, запрещение выдачи информации буферным регистром 5, запрещение выдачи сигнала переноса С 1 операционному блоку 3, установка в лог. "Он фиксатора 6 смены состояний. 45С появлением дополнительных блоков (буферный регистр 5, блок 6 фиксации смены состояний) число функций управления блока 4 синхронизации возрастает более чем втрое. Однако для их обеспечениятребуется ввести только один дополнительный выход блока 4 синхронизации, что не влечет за собой существенных его усложнений по сравнению с известным устройством.Буферный регистр 5 обеспечивает одновременность переключения разрядов микрокоманды, что увеличивант надежность функционирования микропроцессора; кроме того, не требуется подбор микросхем 113 У блока блока 1 памяти микрокоманд (по времени выборки информации), что упрощает изготовление микропроцессора и практически исключает потери микросхем памяти. Фиксатор 6 смены состояний обеспечивает укороченный такт для большинства условных переходов, увеличивая быстродействие микропроцессора. При этом в "длинных" условных переходах не производится никаких процедур запоминания исходного адреса и не организуются дополнительные такты для возвращения на правильную ветку программы; достоверный адрес формируется в течение одного такта (по длительности, равного такту с условным переходом известного устройства), при этом последовательность и временные задержки синхроимпульсов от начала такта остаются постоянными независимо от типа перехода,Сигналом на входе условной синхронизации УС блока 4 синхронизации ссоответствующего поля микрокомандыпроизводится запрещение (сигналомлог. "О") выдачи синхроимпульса СОБна операционный блок 3. Режим услов-ной синхронизации применяется втактах, в которых используется сигнал переноса С 1 (он формируется блоком 3 независимо от синхроимпульсовСОБ) и не требуется изменение содержимого внутренних регистров операционного блока 3 (которое происходит по синхроимпульсу СОВ).На фиг.2 приведен пример функциональной схемы блока 6 фиксации. Функцию конвейерной памяти выполняетэлемент 12 задержки, операцию сравнения выполняет элемент ИСКЛЮЧАЮЩЕЕИЛИ 11, результат которой фиксируется в триггере 14 по уровню лог. "О"на его входе записи (этот вход является синхровходом блока 6 фиксации),Сигнал ПР запоминается в элементе 12задержки до момента появления достоверного сигнала переноса С 1, затем сигналы ПР и С 1 сравниваются в элементе 11 и результат поступает на информационный вход триггера 14. Равенство ПР и С 1 приводит к формированию лог. "О" на выходе элемента 11, запись его в триггер 14 приводит к подтверждению его исходного состояния (этот триггер 14 сбрасывается в начале такта синалом с третьеговыхода синхронизатора 4). Если ПР и С не равны в триггер 14 записывается лог. "1". Если на вход признака перехода ПП с соответствующего по 6 ля микрокоманды будет подан сигнал лог. "1" (переход в текущем такте является безусловным), то этот сигнал, проходя через элемент ИЛИ 13, принудительно удерживает триггер 14 О в состоянии лог. "0", не позволяя ему реагировать на сигнал записи (синхроимпульс СБМУ).На фиг.З и 4 приведены примеры реализации генератора 7, формировате лей 8-10 и временные диаграммы их работы. Длительность "короткого" такта определяет элемент 15 задержки и элемент И-ИЛИ-НЕ 17, при "длинном" такте добавляется задержка в эле менте 16 задержки. Четыре отвода от элементов 15 и 16 обеспечивают фиксированные временные задержки относительно начала такта (сигнала с первого вывода генератора 7). Дополнительный вход ИЛИ элемента 17 используется для остановки генерации (сигнал лог. "1" на входе запуска генератора удерживает выход элемента 17 в состоянии лог, "0"), Сигналы 30 с управляющих входов генератора 7 поступают на первые входы И элемента 17, эти сигналы являются парафазными: их состояние равно 10 или 01 т.е. всегда открыто только одно из плеч элемента 7.3). Формирователи 8-10 запускаются положительным фронтом. Длительности формируемых импульсов определяются элементами 19, 21 и 22, 24 задержки с инверсией, входящими в 40 состав формирователей 8-10. Логика импульсов определяется типом логичес" кого элемента в формирователях 8-10: элементом И 18, элементом И-ИЛИ-НЕ 20 и элементом И-НЕ 23 соответствен но. Третий вход элемента 23 соединен с входом условной синхронизации (УС) синхронизатора, Сигнал лог. "0" на входе УС запрещает формирование импульсов формирователем 10 в режиме 50 условной синхронизации. При реализации микропроцессора в качестве блока 2 используется микросхема К 589 ИК 1 (или К 585 ИК 1), операционный блок 3 реализуется на микросхемах центрального процессор- . ного элемента К 589 и схемы ускоренного переноса К 589 ИКОЗ, буферный регистр 5 реализуется на микросхеме К 589 ИР 12 (многорежимньп буферный регистр - МБР). Блок 1 памяти микро" команд можно выполнить на микросхемах ПЗУ 556 серии. Остальные блоки - на логических элементах 530 серии.Формула изобретения1.Микропроцессор, содержащий блок памяти микрокоманд, блок управления последовательностью микрокоманд, операционный блок, блок синхронизации, причем выход переноса операционного блока и выход признака переноса блока памяти микрокоманд объединены и подключены к входу признака переноса управления последовательностью микро- команд, выход признака переноса которого соединен с входом переноса операционного блока, информационный и адресный выходы которого являются соответственно информационным и адресным выходами микропроцессора, первый и второй информационные входы которого "соединены соответственно с первым и вторым информационными входами операционного блока, входы команды и записи команды микропроцес" сора соединены соответственно с входами команды и записи команды блока управления последовательностью микро- команд, выход адреса которого соединен с входом адреса блока памяти микрокоманд, выходы с первого по шестое поле местного управления блока памя- ти микрокоманд соединены соответственно с входом управления адресом и входом управления флагом блока управления последовательностью микрокоманд, с выходом управления внешним устройством микропроцессора, с входом микрооперации и входом маски операционного блока, с первым входом признака режима блока синхро" низации, первый и второй выходы которого соединены соответственно с входами синхронизации операционного блока и блока управления последовательностью микрокоманд, вход запуска микропроцессора соединен с входом запуска блока синхронизации, о т л и ч а ю щ и й с я тем что, с целью повышения быстродействия, в него введены буферный регистр, блок фиксации смены состояний, причем выходы с первого по шестое поле местного управления блока памяти ми72 12триггера, первый и второй входы сброса блока фиксации смены состоянийсоединены соответственно с первыми вторым входами элемента ИЛИ, выходкоторого соединен с входом сбросатриггера. 2.Микропроцессор по п.1, о т л и - ч а ю щ и й с я тем, что, блок синхронизации содержит с первого по шестой элементы задержки, первый и второй элементы И-ИЛИ-НЕ, элемент И, элемент И-НЕ, причем вход запуска блока соединен с первым входом первого элемента И-ИЛИ-НЕ, выход которо" го соединен с входами первого и третьего элементов задержки и с первым входом элемента И, выход третьего элемента задержки соединен с вторым входом элемента И, выход которого является вторым выходом блока, первый выход первого элемента задержки соединен с входом четвертого элемента задержки и с первым входом второго элемента И-ИЛИ-НЕ, выход которого является третьим выходом блока, выход четвертого элемента задержки соединен с вторым входом второго элемента И-ИПИ-НЕ, первый выход второго элемента задержки соединен с третьим входом второго элемента И-ИЛИ-НЕ и с входом пятого элемента задержки, выход которого соединен с четвертым входом второго элемента И-ИЛИ-НЕ, второй выход второго элемента задержки соединен с первым входом элемента И-НЕ и с входом шестого элемента задержки, выход которого соединен с вторым входом элемента И-НЕ, первый вход признака режима блока соединен с третьим входом элемента И-НЕ, выход которого является первым выходом блока, второй и третий входы признака режима блока соединены соответственно с вторым и третьим входами элемента И-ИЛИ-НЕ, второй выход первого элемента задержки соединен с четвертым входом первого элемента И-ИЛИ-НЕ и входом второго элемента задержки, третий выход которого соединен с пятым входом первого элемента И-ИЛИ-НЕ. 11 13615 крокоманд соединены с соответствующими полями информационного входа буферного регистра, выход признака переноса блока памяти микрокоманд соединен с информационным входом блока фиксации смены состояний, первый и второй выходы которого соединены соответственно с вторым и третьим входами признака режима блока синхро" 10 низации, третий выход которого соединен с первым входом сброса блока фиксации смены состояний, с входом разрешения выдачи блокапамяти микро- команд, с входом записи и входом раз решения выдачи буферного регистра, с входом разрешения выдачи переноса операционного блока, второй выход блока синхронизации соединен с синхровходом блока фиксации смены сос.-: 20 тояний, выход признака перехода блока памяти микрокоманд соединен с соответствующим разрядом информационного входа буферного регистра и с вторым входом сброса блока фиксации 25 смены состояний, кроме того, выходы с первого по седьмое поле местного управления буферного регистра соединены соответственно с входом управления адресом и входом управления фла гом блока управления последовательностью микрокоманд, с выходом управления внешним устройством микропроцессора, с входом микрооперации и входом маски операционного блока, с первым входом признака режима блока синхронизации, с вторым входом сброса блока фиксации смены состоя.= ний, причем блок фиксации смены состояний содержит элемент ИСКЛОЧАЮЩЕЕ 40 ИЛИ, элемент задержки, элемент ИЛИ и триггер, информационный вход блока фиксации смены состояний соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с входом элемента задержки, вы ход которого соединен с вторым вхо-. дом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с информационным входом триггера, прямой и инверсный выходы которого являются соответст венно первым и вторым выходами блока фиксации смены состояний, синхровход которого соединен с синхровходом

СмотретьЗаявка

4016243, 27.01.1986

ОПЫТНО-КОНСТРУКТОРСКОЕ БЮРО НОВГОРОДСКОГО ПОЛИТЕХНИЧЕСКОГО ИНСТИТУТА

МИНУТИН ЛЕОНИД ДМИТРИЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 23.12.1987

Код ссылки

<a href="https://patents.su/10-1361572-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Устройство для подключения эвм к системной шине

Следующий патент: Блок обслуживания заявок

Случайный патент: Устройство для испытания авиационных колес на усталостную нрочность