Микропрограммный мультиплексный канал

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1305693

Авторы: Асцатуров, Извозчикова, Мазикин, Пронин, Яновская

Текст

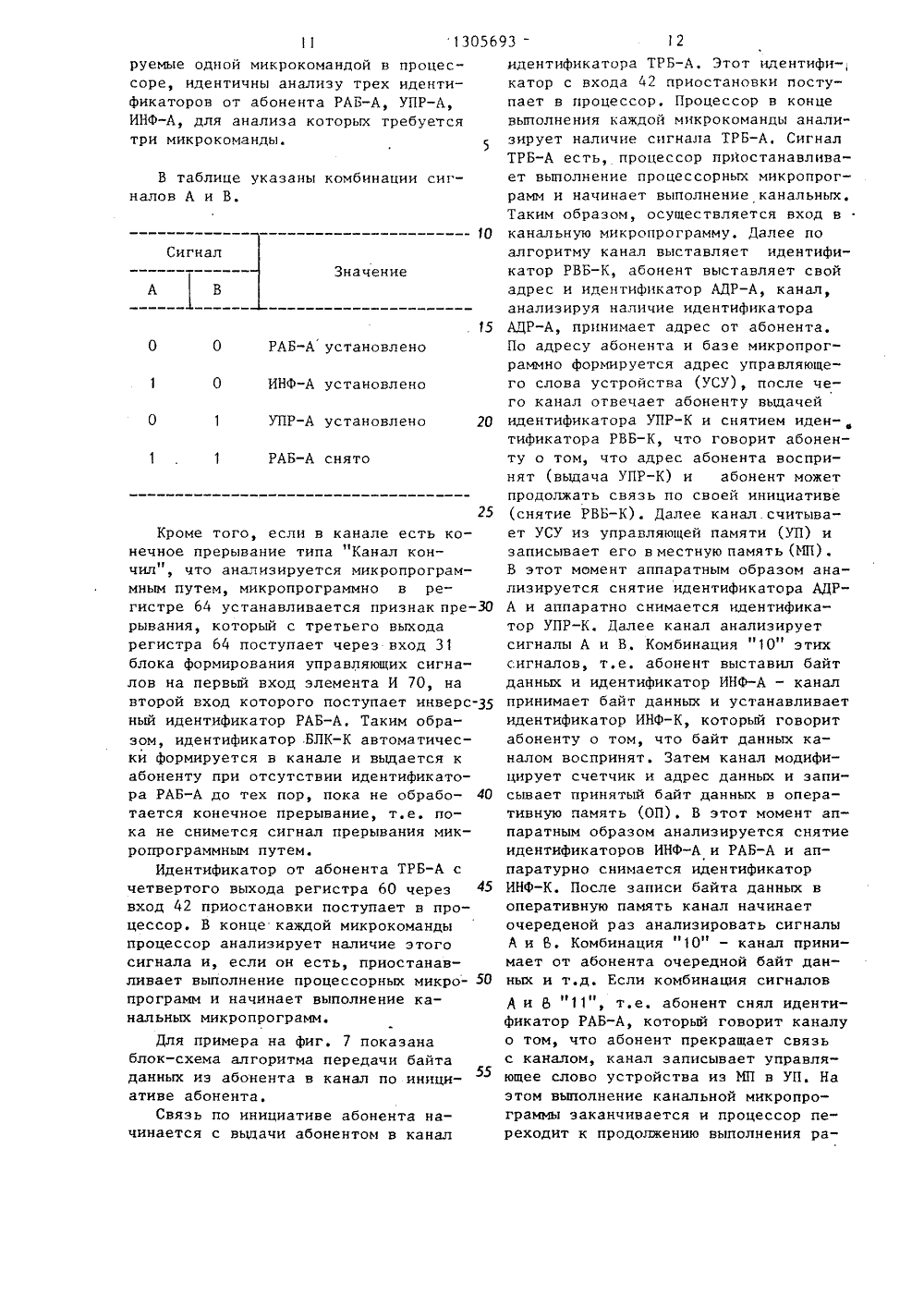

(19) (1 6 Р 13/О ПИСАНИЕ ИЗОБРЕТЕНИ Щги(61) (21) (22) (46) между периферийным процессором, Целью ется расширение фу и устр изобр нкцион граммн У 15 М. А новс можностеи микропр ату 1. ов лексного нала за сче ации пл ли налов и их произв льного ный му ния. лкропрограм содержит бл ирования упдешифрации и, блок,7 а модулю два, ел 15 регис в, узел 17 гистра 3 и тов И 10-13 13 ил 1 т канал6 формблок 1 ельство СССР 13/00, 1985.МУЛЬТНПЛЕКСНЫИ к 2 регистро авляющих сиг команд, блок ализа, узел 9 блок 14 шифр ров, узел 16 иксации подк,блок алов, 5 ком сверт мутацики по12, узраторо бретение касается числий те дешифналов,пы ки, в частности орга типлексных ии микропрограммных м четыр групНЕ. ных вычислител налов микропро элеменф-лы,элемебл,спользован формацией т быть обмена ых маши о ган ции ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ 12560363976083/24-2418.11.8523,04,87. Бюл.В,М. Пронин, РМазикин, А,Г,Извозчикова681325(088.8)Авторское свид6036; кл. С 06МИКРОПРОГРАММН1305617состояния регистра 98 определяется наличие свободных подканалов. Если свободные подканалы есть, пятиразрядный код, полученный с регистров 100 и 102, определяет адрес слова таблицы ."., в котором есть по крайней мере один свободный подканал, Указанныйанализ выполняется микропрограммно путем чтения информации с информационного выхода 49 узла регистров. Про читанный пятиразрядный код адреса слона второй таблицы запоминается в ячейке МПЗ. По этому адресу из второй таблицы читается слово, которое запоминается в ячейке МП 5. Затем слово 15 из ячейки МП 5 выдается в блок 14 шифраторов аналогично указателю слов второй таблицы и далее запоминается в узле 15 регистров. После этого микропрограммно происходит аналогичный 20 анализ информации с регистра 99 и регистров 101 и 103.Таким образом, после анализа двух слов: указателя слов второй таблицы и одного из слов второй таблицы полу чается полный адрес свободного подканала Этот адрес записывается в ячейку ИП 2, а затем по адресу таблицы 1, хранящегося в ячейке МП 4, переписывается вместе с признаком, что подканал назначен в первую таблицу 1После назначения подканала необходимо скорректировать слово второй таблицы и,если необходимо, указатель слов второй таблицы. Для этой цели35 код адреса бита в байте слова второй табгицы и код адреса бита в байте указателя слов второй таблицы с регистров 103 и 102 по линиями 106 и 105 соответственно через информационный вход 50 узла дешифраторов подаются на входы дешифраторов 108 и 107 Далее по коду адреса байта, полученного с регистра 101, корректируется соответствующий байт слова второй табли цы, которое хранится в ячейке МП 5, путем сложения этого байта с константой, полученной с выхода дешифратора .08. После этого скорректированное слово второй таблицы проверяется на предмет наличия в нем свободных подканалов. Для этой цели скорректированное слово второй таблицы из ячейки МП 5 подается на информационный вход 21 блока шифраторови на регистре 99 запсминается признак наличия свободных подканалов, Этот признак анализируется, Если свободные подканалы есть, слово второй таблицы из ячейки МП 5 9318переписывается во вторую таблицу по адресу, который хранится в ячейке МП 3; Назначение подканалов заканчивается, Если свободных подканалов нет, необходимо скорректировать соответствующий байт указателя слов второй таблицы, расположенного в ячейке МП 1.Для этой пели по коду адреса байта, полученного с выхода регистра 100;корректируется соответствующий байт указателя слов второй таблицы путем сложения этого байта с константой, полученной с дешифратора 107. Скорректированный байт записывается в ячейку МП 1, Слово второй таблицы из ячейки МП 5 записывается во вторую таблицу. Назначение подканалов заканчивается.Освобождение подканалов выполняется после конца связи с периферийным устройством, когда соответствующий подканал не нужен, Освобождение подканала осуществляется микропрограммным способом.Таким образом, аппаратно-микропрограммный способ распределения плавающего количества подканалов, который позволяет с минимальными аппаратными затратами производительно осуществлять назначение любого подканала любому периферийному устройству в процессе выполнения команды ввода-вывода, исключает жесткую зависимость количества подключаемых к микропрограммному мультиплексному каналу периферийных устройств от количества отведенных подканалов, вызванное соответствием адреса периферийного устройства адресу соответствующего подканала, что приводит к возможности гибкойадаптации в условиях пользователя в части подключения к каналу широкой номенклатуры периферийных устройствв количественном составе.Организация плавающего количестваподканалов, кроме того, позволяет гибко и простым способом адаптироваться к условиям пользователя путемпредоставления ему того количестваподканалов, которые необходимо только ему для создания определенных конфигураций периферийных устройств сорганизацией их параллеЛьной работы,используя при этом минимальный объемуправляющей памяти, предназначеннойдля хранения подканалов, 1305693920формулаизобретения 1. Микропрограммный мультиплексный канал по авт.св. Р 1256036, о т л и чающий с я тем, что, с целью 5 расширения функциональных возможностей за счет организации плавающего количества подканалов и их произвольного распределения, в него введены блок шифраторов, узел регистров, узел 10 дешифраторов, узел фиксации подканалов, причем информационный вход блока шифраторов является входом канала для подключения к информационному выходу процессора, информационные выходы уз ла регистров, узла дешифраторов и узла фиксации подканалов подключены к выходу микропрограммного мультиплексного канала для подключения к информационному входу процессора, при этом группа разрядных выходов блока дешифрации команд соединена с соответствующими разрядами разрешающих входов узла регистров и с разрешающими входами узла дешифраторов и узла фиксации подканалов, информационный выход блока шифраторов соединен с информационным входом узла регистров, выход которого соединен с информационным входом узла дешифраторов.2, Канал по и. 1, о т л и ч а ю - щ и й с я тем, что узел фиксации подканалов содержит регистр и группу элементов И, причем выходы регистра соединены с первыми входами элементов И группы, вторые входы и выходы которых образуют соответственно разрешающий вход и информационный выход узла.1305693Фиг 10 Алааратурно анаши зируется снягпие АЯРи аппарогпурно сиигфаелср УПР-Р 112Я(121305693 ЛПУ Составитель С Техред А. Кравч Редактор И. Шулл Заказ 1453 4 4/5 оизводственно-полиграфическое предприятие, г, Ужгород, ул, Проектная,/ Тираж б 73ВНИИПИ Государственнопо делам изобретений 113035, Москва, Ж, Ра тныл фЮрадиэирувльсм игю-Л,ва 1 отурио сицмаию-г естмал КорректорС, Черни Подписнокомитета СССРи открытийская наб д15 25 45 1 13056Изобретение относится к вычислительной технике, в частности к организации микропрограммных мультиплексных каналов микропрограммных вычислительных машин,. может быть использо ванс для органиэации обмена информациеймежду периферийными устройствами и процессором и является усовершенствованием изобретения по авт,св,Ф 1256036,Цель изобретения - расширение.функциональных возможностей микропрограммного мультиплексного каналаза счет организации плавающего количества подканалов с возможностью ихпроизвольного распределения, т,еназначения любого подканала любомупериферийному устройству с последующим освобождением его после конца связи канала с периферийным устройст вом,На фиг, 1 изображена схема микропрограммного мультиплексного канала; на Фиг. 2 - схема блока дешифрации команд на фиг. 3 - схема блока регистров; на фиг, 4 - схема блока коммутации; на фиг. 5 - схема блока формирования управляющих сигналов; нафиг 6 - схема блока анализа; нафиг 7 - схема блока шифраторов", наФиг 8 - схема узла регистров; на Фиг 9 - схема узла дешифраторов; на фиг 10 - схема узла фиксации подканалов; на Фиг. 11 и 12 - схема алгоритма передачи байта от абонента в канал по инициативе абонента; на фиг 13 - возможное количество используемых ячеек местной памяти процессора при распределении подканалов. Иикропрограммный мультиплексный 40 канал (Фиг, 1) содержит блок 1 дешифрации команд, блок 2 регистров, регистры: второй 3 и первый 4 блок 5коммутации, блок б Формирования управляющих сигналов, блок 7 анализа,93 2ции, первый информационный выход 27 блока коммутации, второй информационный выход 28 блока коммутации, первый улравляющий вход 29 блока коммутации, первый выход 30 группы информационных разрядов блока регистров, первый выход 31 группы управляющих разрядов блока регистров, первый выход 32 блока формирования. управляющих сигналов, второй выход 33 блока формирования управпяющих сигналов, второй выход 34 блока анализа, второй вход 35 блока анализа, третий выход 36 блока анализа, второй выход 37 группы управляющих разрядов блока регистров, выход 38 элемента НЕ, второй выход 39 группы информационных разрядов блока регистров, выход 40 узла свертки по модулю два, второй информационный выход 41 блока регистров, выход 42 приостановки процессора, третий выхоц 43 блока дешифрации команд, первый выход 44 блока дешифрации команд, первый выход 45 блока анализа, четвертый выход 46 блока дешифрации команд, информационный выход 47 узла фиксации, информационный выход 48 блока шифраторов, второй информационный выход 49 и первый информационный выход 50 узла регистров, информационный выход 51 узла дешифраторовБлок 1 дешифрации команд (Фиг, 2) содержит регистр 52 микрокоманд и дешифратор 53 микрокоманд, Дешифратор 53 микрокоманд имеет выходы 54-58,Блок 2 регистров (фиг, 3) содержит регистр 59 подсинхронизации, регистр 60 приема, группу элементов И 61, регистр 62 выдачи, 0-триггер 63, первый 64 и второй 65 регистры,Блок 5 коммутации (фиг. 4) содержит элемент НЕ 66, две группы элементов И 67 и 68, группу элементов ИЛИ 69.элемент НЕ 8, узел 9 свертки по модулю два, четыре группы элементов И:четвертую 10, третью 11, вторую 12 ипервую 13, блок 14 шифраторов, узел15 регистров, узел 16 дешифраторов, 5 О узел 17 фиксации подканалов, информационный выход 18 абонента, вход 19 включения питания, синхровыход 20 процессора, информационный выход 21 процессора, управляющий выход 22 або нента, управляющий вход 23 абонента, информационный вход 24 абонента, информационный вход 25 процессора, информационный . вход 26 блока коммутаБлок 6 формирования управляющихсигналов (фиг. 5) содержит элементИ 70, первый 71, второй 72 и третий73 элементы ИЛИ, второй 74 и первый75 элементы НЕ, узел 76 свертки помодулю два,Блок 7 анализа (фиг. 6) содержитпервый 77, второй 78, третий 79 ичетвертый 80 элементы НЕ; третий 81,первый 82, второй 83 и четвертый 84элементы И, первый 85 и второй 86элементы ИЛИ.3 13056Блок 14 шифраторов (фиг, 7) содержит первый 87, второй 88, третий 89 и четвертый шифраторы 90, первый 91, второй 92 и третий 93 мультиплексоры и пятый шифратор 94, Мультиплексоры и пятый шифратор имеют выходы 95-97 (фиг, 7).Узел 15 регистров (фиг. 8) содержит первый 98 и второй 99 одноразрядные регистры, первый 100 и второй 101 10 двухразрядные регистры, первый 102 и второй 103 трехразрядные регистры, группу элементов И 104, Регистры 102 и 103 имеют соответственно выходы 105 и 106 (фиг. 8). 15Узел 16 дешифраторов содержит первый 107 и второй 108 дешифраторы и элемент И 109.Узел 17 фиксации подканалов содержит регистр 110 и группу элементов 20 И 111.Блок 1 дешифрации команд служит для приема с информационного выхода 21 микрокоманд в регистр 52 микрокоманд и дешифрации микрокоманд при по 25 мощи дешифратора 53, первый, второй, третий и четвертый выходы которого являются результатом дешифрации микрокоманд записи информации в регистр 62 выдачи, записи информации в триг гер 63, первый регистр 64, второй регистр 65, диагностики, по которой разрешается запись информации из регистра 62 вьдачи через группу элементов И 67 в регистр 59 подсинхронизации, и чтения, по которой клапанируются групповые элементы И 10 - 13 и информация с них поступает на информационный выход 25 к процессору.40Блок 2 регистров предназначен для приема информации от абонента на группу элементов И 61 с информационного выхода 18 абонента и вьдачи информации на пеРВый ВхОд Группы элементОВ 45 И 10, приема информации с информационного выхода 27 в регистр 59 подсинхронизации с последующим приемом этой информации в регистр 60 приема и выдачи с первого, второго, третьего, четвертого и пятого выходов регистра 60 приема на информационный выход 39, а с первого, второго, шестого и седьмого выходов - на выход 37, приема информации в регистр 62 вьдачи с информационного выхода 21 процессора и вьдачи информации с выхода регистра 62 вьдачи через блок 5 коммутации в регистр 59 подсинхронизации в случае 93диагностирования или через группу элементов И 13 на информационный вход 25 процессора для организации контроля переданной из процессора информации в регистр 62 выдачи путем ее сравнения в процессоре и через второй регистр 3 на информационный вход 24 абонента в случае передачи .информации к абоненту, приема управляющих сигна-лов для абонента с информационного выхода 21 процессора на триггер 63, первый 64 и второй 65 регистры и выдачи управляющих сигналов с выхода триггера 63, первого и второго выходов первого регистра 64 и с первого и второго выходов второго регистра 65 на информационный выход 30 для выдачи через первый регистр 4 управля-, ющих сигналов к абоненту и в блок 6 формирования управляющих сигналов, вьдачи с третьего выхода регистра 60 приема управляющего сигнала на вход 42 приостановки процессора, для организации сброса второго регистра 65 сигналом с управляющего входа сброса, вьдачи управляющих сигналов с третьего и четвертого выходов регистра 64 на управляющий выход 31.Блок 5 коммутатора используется для коммутации информации с. Управляющего выхода 22 абонента через группу элементов И 68 и группу элементов ИЛИ 69 в регистр 59 подсинхронизации в рабочем режиме или информации с регистра 62 вьдачи через группу элементов И 67 и группу элементов ИЛИ 69 в регистр 59 подсинхронизации в диагностическом режиме.Блок 6 формирования управляющих сигналов служит для формирования некоторых управляющих сигналов, необходимых для управления работой аппаратуры канала, а именно сигналов с элементов НЕ 74 и 75, поступающих через, вход 35 в блок 7 анализа, необходимых для управления работой периферийных устройств, а именно сигналов с элементов ИЛИ 72 и 73, поступающих на выход 33 и далее через регистр 4 на управляющий вход 23 абонента, а также для возможности контроля сравнением в процессоре, информации, принятой с информационного выхода 21 процессора, во-первых, в регистр 62 выдачи, информация с которого поступает через второй регистр 3 на информационный вход 24 абонента в виде обменного байта данных с периферийными устрой5 13056ствами, а также для контроля сравнением в процессоре через группу элементов И 13 на информационный вход 25 процессора и, во-вторых, в триг, гер 63, регистры 64 и 65, с выходов которых информация поступает в блок б формирования управляющих сигналов, где эта информация поступает с выходов 30 и 31 на элемент 76 для формирования к этой информации контрольно 1 О го разряда и на выход 32 вместе с контрольным разрядом с выхода элемента 76 и через группу элементов И 12 на информационный вход 25 процессора,.Блок 7 анализа используется для выработки управляющих сигналов с выхода элемента И 81 и с элемента НЕ 80, которые через выходы 45 и 34 поступают на сбросовый вход регистра 65 и на второй вход элемента И 70 соответственно с целью исключения микропрограммного анализа наиболее частоучаствующих в управлении управляющих сигналов, что сокращает объем канальных микропрограмм и, следовательно, 25время их выполнения, а также формирования определенной комбинации управляющих сигналов, получаемых с выходов элементов ИЛИ 85 и 86, которые поступают в процессор через группу элементов И 11, после анализа которых микропрограммным путем канальнаямикропрограмма определяет состояниетрек управляющих сигналов, за счетчего сокращается объем канальных микропрограмм и, следовательно, время их выполнения,Элемент НЕ 8 используется для инверсии принятого с синхровхода 20 синхронизирующего сигнала о дальнейшем использовании прямого и инверсного синхронизирующих сигналов для управления приемом информации в регистре 59 и 60 блока 2 регистров и для выработки в определенное время управляющего сигнала с выхода элемента И 81 в блоке 7 анализа.Узел 9 свертки по модулю два служит для формирования контрольного разряда к информации, которая поступает на его вход из блока 7 анализа и блока 2 регистров соответственно, и выдачи этого контрольного разрядана первый вход группы элементов И 11.Группы элементов И 10-13 используются для коммутации при помощи управляющего сигнала, поступающего свыхода 44 дешифрации, информации,поступа 1 ощей из блока 2, регистров с вы 304050 93- 6хода группового элемента И 61 на первый вход четвертой группы элементовИ 10, блока 2 регистров с выхода регистра 60 приема через информационный выход 39, из блока 7 анализа сэлементов ИЛИ 85 и 86 и с выхода 40на первый вход третьей группы элементов И 11, из блока 6 формирования свыхода 32 на первый вход второй группы элементов И 12, из блока 2 регистров с выхода регистра 62 выдачинапервый вход первой группы элементовИ 13 с последующей одновременной выдачей с выходов групп элементов И 1013 информации на информационный вход25 процессора,Блок 14 шифраторов предназначендля формирования адреса свободногоподканала, который выполняется путеманализа на наличие нулевых бит в че -тырех байтах информационного слова,поступающего с информационного выхода 21 процессора побайтно на информационные входы шифраторов 87-90, иформирования первого нулевого бита винформационном слове, начиная, например, с нулевого бита, при помощи пятого шифратора 94, на первый - четвертый информационные входы которогопоступают управляющие выходы с шифраторов 87-90 соответственно, и припомощи трех мультиплексоров 91-93,на первый - четвертый информационныевходы которых поступают соответственно первые, вторыеи третьи адресныевыходы шифраторов 87-90, и выдачи свыходов мультиплексоров 91-93, с адресного и управляющего выходов шифратора 94 на информационный выход 48блока трех-, двух-и одноразрядногокодов соответственно,Узел 15 регистров используется дляхранения на регистрах 98-103 информации, полученной с информационноговхода 48, а также выдачи информациис регистров 98-103 через группу элементов И 104 под управлением управляющего сигнала с выходов 54, полученного с выхода дешифратора 53, напервый информационный. выход 49 и свыходов регистров 102 и 103 на второй информационный выход 50.Узел 16 дешифраторов предназначендля Формирования соответствующих констант путем дешифрации на дешифраторах 107 и 108 трехразрядной информации, поступающей на входы дешифраторов 107 и 108 с информационного входа 50 и выдачи этих констант через, 1305693групповой элемент И 109 под управлением управляющего сигнала с входа 57,полученного с выхода дешифратора 53,на информационный выход 51,Узел 17 фиксации предназначен длязадания при помощи регистра 110 коммутации конкретного количества подканалов путем набора при помощи переключателей определенного кода на регистре 110 коммутации и выдачи этого 10кода через групповой элемент И 111под управлением управляющего сигнала58, полученного с выхода дешифратора53, на информационный выход 47,Микропрограммный мультиплексный 15канал работает под управлением канальных микропрограмм, расположенных совместно с процессорными микропрограммами в памяти микропрограмм (управляющей памяти), Это позволяет в любой 20момент времени выполнять или микропрограммы процессора, или микропрограммы мультиплексного канала.Микропрограммы мультиплексного канала являются более приоритетными поотношению к процессорным микропрограммам. Как только возникает необходимость в выполнении канальных микропрограмм процессорные микропрограммы немедленно приостанавливаются и начи- З 0 нается выполнение канальных микропрограмм. После их выполнения выполнение процессорных микропрограмм продолжается.Операция ввода-вывода в микропро граммном мультиплексном канале начинается по специальной команде процессора, которая задает адреса канала и периферийного устройства и при помощи специальных управляющих слов ка нала, которые указываются или в проблемной программе, или формируются при помощи специальной управляющей программы (например, супервизор ввода-вывода), указывает код команды, началь ный адрес оперативной памяти для организации обмена данными, количество передаваемых байт данных и другиеуправляющие признаки, по которым под управлением специальной канальной 50 микропрограммы формируется управляющее слово устройства. Формирование управляющего слова устройства выполняется с использованием нескольких ячеек в местной памяти процессора, построенной на полупроводниковых запоминающих элементах, быстродействие которых соизмеримо с быстродействием регистровой памяти, что позволяет значительно сократить время работы канальных микропрограмм. С этой целью управляющее слово устройства, если его необходимо сохранить, переписывается из местной памя ти процессора не в оперативную память, а в управляющую, быстродействие которой гораздо выше оперативной памяти.Так как канал может работать снесколькими периферийными устройствами (абонентами) одновременно, то длякаждого абонента необходимо сохранятьего управляющее слово. Для этой целив управляющей памяти отводится специальная область для хранения управляющего слова для каждого абонента.Причем общая область в управляющей памяти для хранения всех управляющих словотводится таким образом, чтобы выборку управляющих слов из управляющейпамяти можно было организовать по адресу периферийного устройства, совмещенного с определенной базой, определяющей начало массива. Это позволяет простым способом быстро извлекатьиэ управляющей памяти управляющееслово для конкретного периферийногоустройства. Извлечение из управляющей памяти управляющее слово помещается в местную память процессора ипри необходимости обратно переписывается в управляющую память, Таким образом, возможность одновременной работы канала с несколькими периферийными устройствами определяется количеством управляющих слов, которые могут храниться в управляющей памяти,те, объемом управляющей памяти иликоличеством подканалов, отведеннойдля хранения управляющих слов. Вместной памяти используется столько ячеек, сколько необходимо для храненияодного управляющего слова,После формирования управляющего слова устройства канальная микропрограмма начинает организовывать связь с периферийным устройством (абонентом) по стандартному интерфейсу ввода-вывода. При этом информационный байт данных вместе с контрольным разрядом из процессора передается к абоненту через информационный вход 21 от процессора, регистр 62 выдачи во второй информационный выход 26 блока 2 регистров и регистр 3. Управляющие идентификаторы канала из процессорапередаЮтся к абоненту через информационный вход 21 ат процессора, триггер 63, регистры 62,64 и 65, информационные выходы 26 и 30 блока 2 регистров и с выходов элемента ИЛИ 73 и 72 через выход 33 блока 6 формирования управляющих сигналов и далее через регистр 4 на управляющий выход 23 к абоненту. Причем с выхода триггера 63 выдается индентификатар ра боты от канала РАБ-К, с первого по четвертый выходы регистра 64 вьдаются идентификаторы распространения выборки от канала РВК-К, адрес от канала АДР-К, прерывания ПРЕР, блакирав ка от канала БЛК-К, соответственно с первого и второго выходов регистра 65 выдаются индентификатары управления ат канала УПР-К и информация от канала ИНФ-К. 20Информационный байт данных вместе с контрольным разрядом от абонента к процессору поступает с информационного входа 18 ат абонента через группу25 элементов И 61 и группу элементов И 10 и информационный выход 25 к процессору. Управляющие сигналы от абонент к процессору поступают с группового управляющего входа 22 от абонент через группу элементов И 68, группу элементов ИЛИ 69 в блок 2 регистров по информационному входу 27 и далее через регистр 59 подсинхронизации, регистр 60 приема, через информационный выход 39 блока 2 регист 35 ров и с выходов элементов ИЛИ 85 и 86 через информационный выход 36 блока 7 анализа вместе со сформированным на узле 9 контрольным РазРядом чеРез 40 группу элементов И 11 и информационный выход 25 к процессору. Причем с первого, второго, третьего, четвертого, пятого, шестого и седьмого выходов регистра 60 приема выдаются иден тификаторы работы от абонента РАБ-А, адрес от абонента АДР-А, выборка от абонента ВБР-А, требование от абонента ТРБ-А,отключение от абонента ОТК-А, управление от абонента УПР-А и ин 50 формация от абонента ИНФ-А соответственно, Контроль переданной информации из процессора в канал по информационному входу 21 от процессора и правильность работы связанной с этой передачей оборудования какала выполняются, путем возврата этой информации в процессор через группы элементов И 12 и 13 и ее сравнения в процессоре с переданной. Этот контроль выполняется в процессе работы канала при передаче данных из процессора к абоненту.Контроль работы оборудования канала, связанного с передачей данных из абонента в процессор, осуществляется в диагностическом режиме путем занесения в регистр 60 приема фиктивных идентификаторов от абонента через регистр 62 выдачи и блок 5 коммутации с дальнейшим анализом снятых с группы элементов И 12 и информационного выхода 25 к процессору заранее известных идентификаторов.Установка всех идентификаторов от канала, кроме идентификатора выборки от кнала ВБР-К, выполняется микропрограммным путем. Установка идентификатора РАБ-К выполняется еще и управляющим сигналом при включении питания процессора по управляющему входу 19 включения питания. Установка сигнала ВБР-К выполняется автоматически при включении питания и выдается с элемента ИЛИ 73 на соответствующий разряд регистра - усилителя 4 постоянноСброс всех идентификаторов от канала также выполняется микропрограммным путем. Однако наиболее часто встречающиеся идентификаторы УПР-К и ИНФ-К могут сбрасываться аппаратным путем в процессе работы канала при связи с абонентом. Аппаратный сброс идентификаторов выполняется в регистре 65 путем выработки сигнала сброса. с элемента И 8, который появляется на выходе этого элемента при отсутствии идентификаторов от абонента АДР-А, УПР-А и ИНФ-А и отсутствии синхросигнала, поступающЕего из процессора в канал через синхровыход 38 на четвертый вход элемента И 81,Наличие или отсутствие идентификаторов ат абонента анализируется микропрограммным путем, Однако для более быстрого анализа часто используемых в управлении идентификаторов от абонента РАБ-А, АДР-А, ИНФ-А и УПР-А в комбинации с наличием или отсутствием идентификаторов от Канала АДР-К, УПР-К и ИНФ-К в канале аппаратно формируются два специальных управляющих сигнала - сигнал А с выхода элемента ИЛИ 85 и сигнал В с выхода элемента ИЛИ 86, комбинации которых, анализи 1305693 2руемые одной микрокомандой в процессоре, идентичны анализу трех идентификаторов от абонента РАБ-А, УПР-А,ИНФ-А, для анализа которых требуетсятри микрокоманды. В таблице указаны комбинации сигналов А и В.- 10 Сигнал Значение АВ 15 0 РАБ-А установлено 0 0 ИНФ-А установлено 1 УПР-А установлено 20 РАБ-А снято 25 Кроме того, если в канале есть конечное прерывание типа "Канал кончил", что анализируется микропрограммным путем, микропрограммно в регистре 64 устанавливается признак прерывания, который с третьего выхода регистра 64 поступает через вход 31 блока формирования управляющих сигналов на первый вход элемента И 70, на второй вход которого поступает инверсный идентификатор РАБ-А, Таким образом, идентификатор .БЛК-К автоматически формируется в канале и выдается к абоненту при отсутствии идентификатора РАБ-А до тех пор, пока не обрабо тается конечное прерывание, т,е, пока не снимется сигнал прерывания микропрограммным путем.Идентификатор от абонента ТРБ-А с четвертого выхода регистра 60 через 45 вход 42 приостановки поступает в процессор. В конце каждой микрокоманды процессор анализирует наличие этого сигнала и, если он есть, приостанавливает выполнение процессорных микро программ и начинает выполнение канальных микропрограмм.Для примера на фиг. 7 показана блок-схема алгоритма передачи байта данных из абонента в канал по инициативе абонента.Связь по инициативе абонента начинается с выдачи абонентом в канал идентификатора ТРБ-А, Этот идентифи-,катор с входа 42 приостановки поступает в процессор. Процессор в концевыполнения каждой микрокоманды анализирует наличие сигнала ТРБ-А, СигналТРБ-А есть, процессор прйостанавливает выполнение процессорных микропрограмм и начинает выполнение канальных,Таким образом, осуществляется вход вканальную микропрограмму. Далее поалгоритму канал выставляет идентификатор РВБ-К, абонент выставляет свойадрес и идентификатор АДР-А, канал,анализируя наличие идентификатораАДР-А, принимает адрес от абонента,По адресу абонента и базе микропрограммно формируется адрес управляющего слова устройства (УСУ), после чего канал отвечает абоненту выдачейидентификатора УПР-К и снятием иден-тификатора РВБ-К, что говорит абоненту о том, что адрес абонента воспринят (выдача УПР-К) и абонент можетпродолжать связь по своей инициативе(снятие РВБ-К). Далее канал.считывает УСУ из управляющей памяти (УП) изаписывает его в местную память (ИП).В этот момент аппаратным образом анализируется снятие идентификатора АДРА и аппаратно снимается идентификатор УПР-К. Далее канал анализируетсигналы А и В. Комбинация "10" этихсигналов, т,е. абонент выставил байтданных и идентификатор ИНФ-А - каналпринимает байт данных и устанавливаетидентификатор ИНФ-К, который говоритабоненту о том, что байт данных каналом воспринят. Затем канал модифицирует счетчик и адрес данных и записывает принятый байт данных в оперативную память (ОП), В этот момент аппаратным образом анализируется снятиеидентификаторов ИНФ-А и РАБ-А и аппаратурно снимается идентификаторИНФ-К. После записи байта данных воперативную память канал начинаеточереденой раз анализировать сигналыА и Б, Комбинация "10" - канал принимает от абонента очередной байт данных и т.д. Если комбинация сигналовА и 6 "11", т.е. абонент снял идентификатор РАБ-А, который говорит каналуо том, что абонент прекращает связьс каналом, канал записывает управляющее слово устройства из ИП в УП. Наэтом выполнение канальной микропрограммы заканчивается и процессор переходит к продолжению выполнения ра13 13056 нее прерванной процессорной микропрограммы,Задание в микропрограммном мультиплексном канале и плавающего объемаподканалов и возможности их произ 5вольного назначения выполняются следующим образом.При помощи регистра 110 коммутацииузла 17 фиксации набирается и-разрядный код, определяющий максимальноеколичество подканалов или максимальный объем УП, который отводится дляхранения управляющих слов устройства,При выполнении микропрограммы сбросасистемы этот код через групповой элемент И 111 считывается в процессорчерез информационный выход 25 к процессору и запоминается в УП как характеристика объема подканалов, отведенных в управляющий памяти для микропрограммного мультиплексного канала. В дальнейшем эта информация используется для назначения подканаловв г:роцессе выполнения очередной команды ввода-вывода, Если подканалы 25исг:ользуются не все, назначение подкав:ала выполняется, Если свободныхпор;каналов нет, выполнение командыввода-вывода прекращается, Причем вэтсм случае микропрограмма канала фор-З 0мирует такой признак результата, который формируется каналом в том случае, если при выполнении команды ввода-вывода оказывается, что нужногопериферийного устройства нет, Подобный алгоритм формирования признакарезультата выполнения команды ввода- вывода при отсутствии свободных подканалов выбирается из расчета указать пользователю, что при существующем 10 количестве подключенных периферийных устройств максимальное количество порканалов выбрано неправильно, Такой вывод должен сделать пользователь, когда операционная система (или какая-либо другая система) стандартносообщает, что конкретного периферийного устройства нет, а на самом деле оно подключается к каналу и нормально функционирует, Таким образом, предлагаемая организация плавающего количества подканалов позволяет пользователю выбирать для своих целей минимальное количество подканалов и при необходимости оперативно корректиро вать его.Произвольное назначение подканалов, т.е. возможность назначения любого подканала любому периферийному 934устройству с дальнейшим освобождением этого подкацала после конца связи с периферийным устройством, выполняется аппаратцо-микропрограммным путем, используя аппаратуру микропрограммного мультиплексцого канала, и, в частности, блока 14 шифраторов, узла 15 регистров, узла 16 дешифраторов, двух таблиц, расположенных в УП, и нескольких ячеек ИП, необходимых ,цля оперативной обработки управляющей инФормации.Первая таблица содержит 256 последовательно адресованных ячеек УП,каждая из которых предназначена для хранения адреса назначенного подканала для конкретного периферийного устройства. Адресация ячеек первой таблицы выполняется по адресу периферийного устройства, для которого выполняется команда ввода-вывода. Первая таблица, кроме того, предназначена для хранения признака, который говорит о том, назначен для данного периферийного устройства подканал или нет. При назначении подканала э.от признак устанавливается, После конца работы с периферийным устройством этот признак сбрасывается. Вторая таблица, содержащая и последовательно адресованных ячеек для хранения и-разрядных слов (в указанном случае восемь ячеек для хранения в каждой ячейке 32-разрядного слова) совместно с указателем слов второй таблицы, который состоит из одного носьмиразрядного слова и которое размещается в ячейке местной памяти (Фиг, 13), используется для формирования адреса свободного подканала, Вторая таблица определяет то максимальное количество подканалов, которое может быть отведено для микропрограммного мультиплексного канала. В указанном случае восемь 32-разрядных слова второй таблицы определяют максимальное количество подканалов в размере 256.Восьмиразрядный позиционный код указателя слов второй таблицы используется для оперативного нахождения свободного подканала из общего количества подканалов.Адрес свободного подканала Формируется из адреса слова второй таблицы и адреса бита в этом словеВ рассматриваемом случае адрес слова второй таблицы определяется адресом бита указателя слов второй таблицы,расположенного в ячейке Г 1 П 1 (Фиг. 13), 15 1305693поэтому адрес свободного подканала формируется из адреса бита в указателе слов второй таблицы и адреса бита соответствующего слова второй таблицы.г)Формирование адреса подканала для конкретного периферийного устройства выполняется следующим образом.Общее количество подканалов задается общим количеством бит, установ О ленных в нулевое состояние в словах второй таблицы. Причем наличие свободных подканалов, определяемых словом второй таблицы, характеризуется соответствующим битом указателя слов 15 второй таблицы. Например, если третий бит указателя слов второй таблицы установлен в "1", то свободных подканалов, которые адресуются битом слова второй таблицы по адресу три, 20 нет. Первоначальная установка минимального количества подканалов, которое определяется кодом, набранным на регистре 110 коммутации, осуществляется микропрограммно путем установки соответствующего количества бит указателя слов второй таблицы и бит слов второй таблицы в единичное состояние.30В начале выполнения команды ввода- вывода по адресу периферийного устройства, который задается в команде ввода-вывода и который запоминается в ячейке МП 4 в ячейку МП 2 выбирается строка первой таблицы. Цель этой выборки определить, назначен подканал для адресованного в команде ввода-вывода периферийного устройства или нет. Определение выполняется пу О тем анализа признака назначения подканала. Если подканал назначен, следовательно, адресованное в команде ввода-вывода периферийное устройство занято, выполнение команды ввода-вы вода прекращается. Если подканал не назначен, следовательно, периферийное устройство свободно, выполнение команды ввода-вывода продолжается и выполняется попытка назначения свободного подканала. Для этой цели анализируется наличие свободных подканалов. Анализ выполняется путем проверки наличия нулевых бит в указателе слов второй таблицы. Если нуле вых бит нет, т.е. свободных подканалов нет, канал прекращает выполнение команды ввода-вывода с признаком результата, характеризующим как-бы отсутствие адресуемого в команде ввода- вывода периферийного устройства, Если свободные подканалы есть, то формируется адрес свободного подканала,Анализ наличия свободных подканалов и формирование адреса свободного подканала выполняются следующим образом.Содержимое ячейки МП 1, т.е. указатель слов второй таблицы, по информационному входу 21 от процессора выдается в блок 14 шифраторов. При этом байт 0 поступает на вход приоритетного шифратора 87, байт 1 - на вход шифратора 88, байт 2 - на вход шифратора 89, байт 3 - на вход шифратора 90. Каждый из этих приоритетных шифраторов на своих первых, вторых и третьих адресных выходах формирует трехразрядный код, который является адресом первого бита (начиная с нулевого), который находится в нулевом состоянии и который говорит о том, что слово второй таблицы по этому адресу имеет хоть один свободный подканал, Если в байте О, например, нет ни одного нулевого бита, приоритет- ный шифратор 87 возбуждает четвертый управляющий выход, те. в группе слов второй таблицы, адресованных битами байта 0 указателя слов второй таблицы, ни одного свободного подканала нет. Четвертые выходы приоритетных шифраторов 87-90 поступают на первый - четвертый входы приоритетного шифратора 94. Следовательно, если в указателе слов второй таблицы нет ни одного бита, указывающего на наличие свободного подканала, то возбуждается управляющий выход приоритетного шифратора 94, Если свободные подканалы есть, то двухразрядный адресный код, полученный с первого и второго выходов приоритетного шифратора 94, указывает адрес первого байта (йачиная с нулевого), в котором есть по крайней мере один свободный подканал, а трехразрядный код, полученный на выходах мультиплексоров 91:93, указывает адрес первого бита в слове, который определяет свободный подканал, Информация из блока 14 шифраторов через информационный выход 48 заносится для запоминая в узел 15 регистров, по линии 97 запоминается признак наличия свободных подканалов, по линии 96 - адрес байта, по линии 95 - адрес бита в байте, Таким образом, анализом

СмотретьЗаявка

3976083, 18.11.1985

ПРЕДПРИЯТИЕ ПЯ М-5339

ПРОНИН ВЛАДИСЛАВ МИХАЙЛОВИЧ, АСЦАТУРОВ РУБЕН МИХАЙЛОВИЧ, МАЗИКИН БОРИС ВИКТОРОВИЧ, ЯНОВСКАЯ АЛЛА ГЕОРГИЕВНА, ИЗВОЗЧИКОВА ЛИДИЯ НИКОЛАЕВНА

МПК / Метки

МПК: G06F 13/00

Метки: канал, микропрограммный, мультиплексный

Опубликовано: 23.04.1987

Код ссылки

<a href="https://patents.su/17-1305693-mikroprogrammnyjj-multipleksnyjj-kanal.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный мультиплексный канал</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Устройство для сопряжения линии связи с приемником информации

Случайный патент: Астатическое звено устройства автоматической подстройки частоты