Система полунатурного моделирования динамических систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1121681

Авторы: Белюнов, Лукьянова, Овчинников, Пупков

Текст

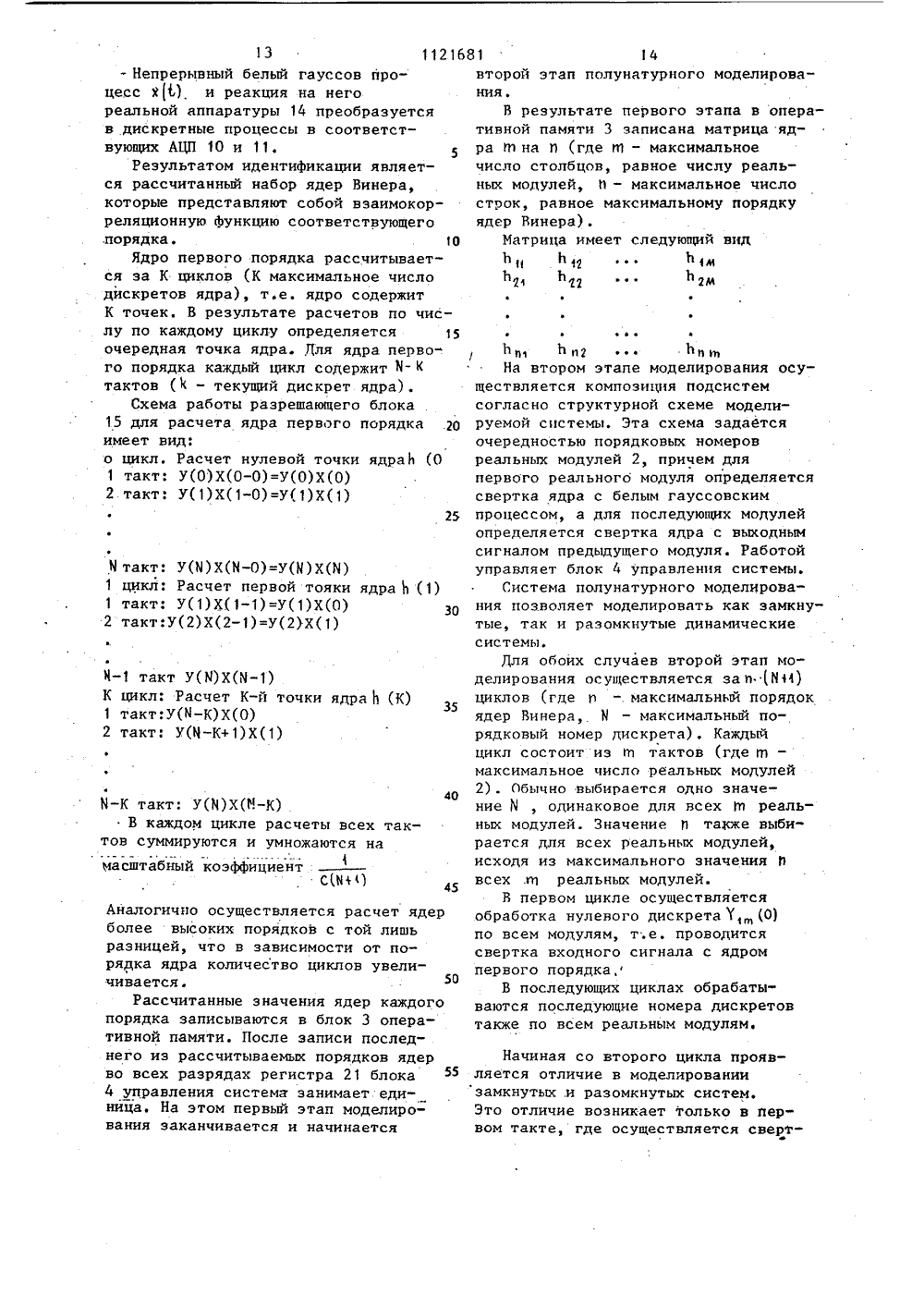

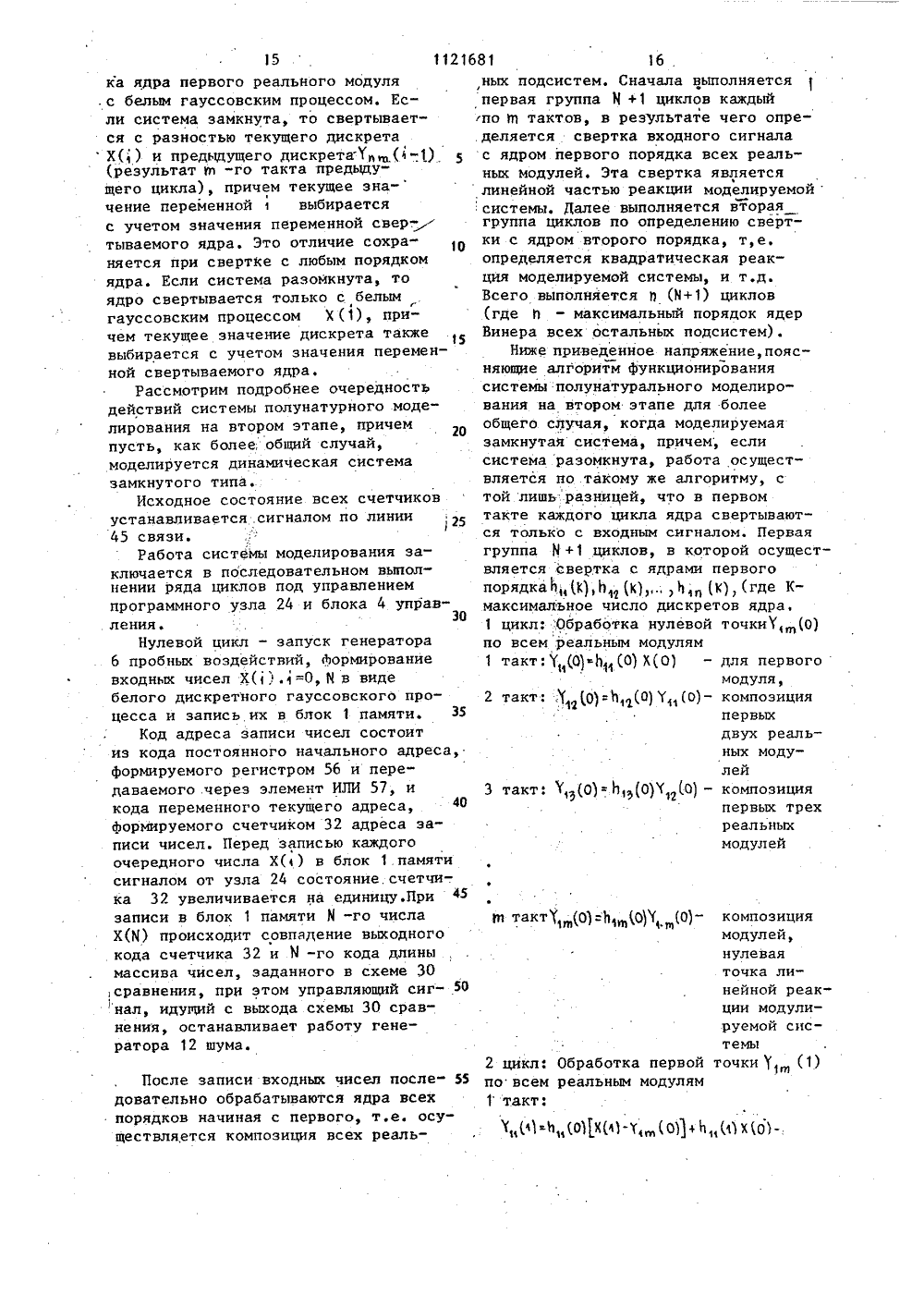

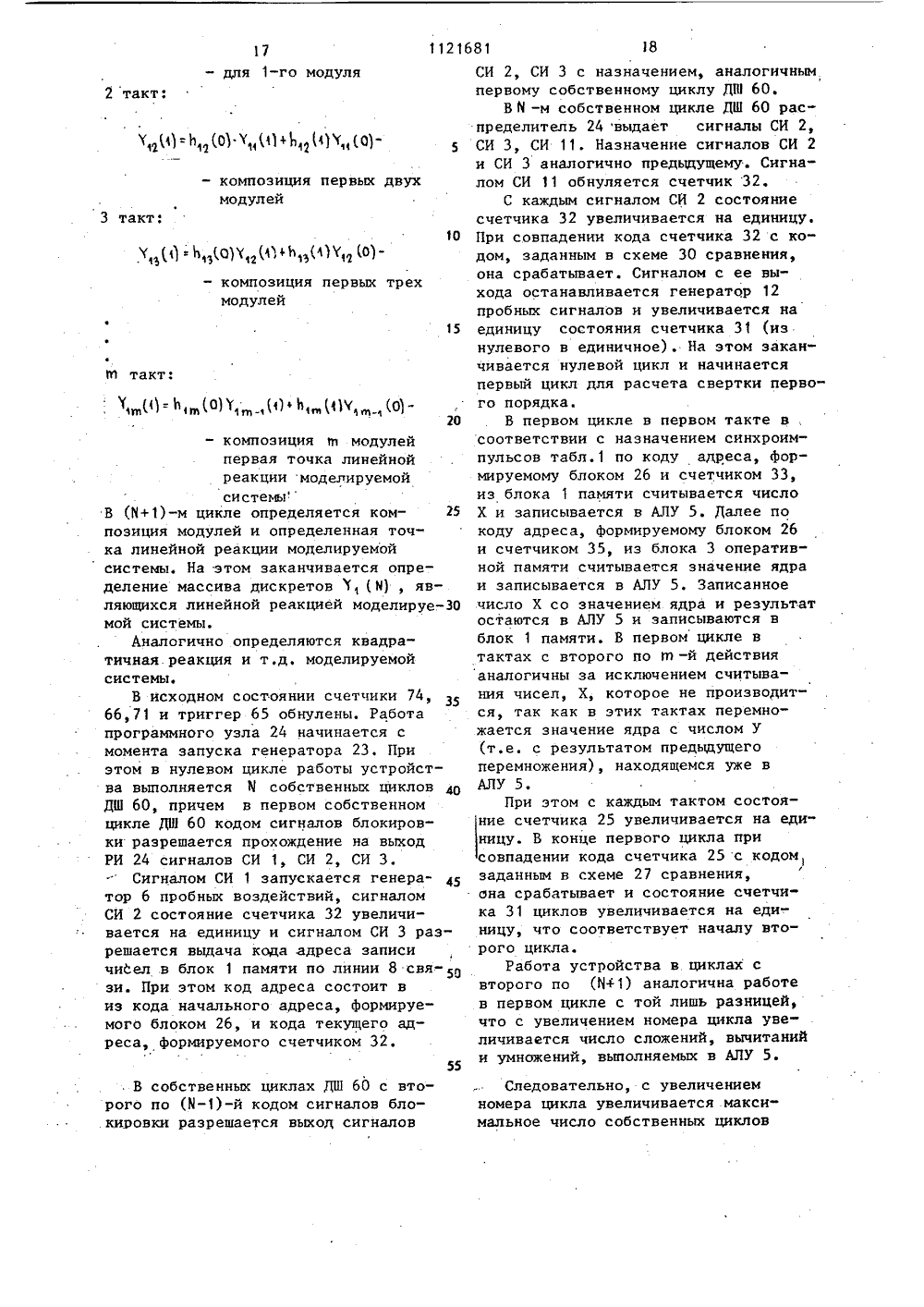

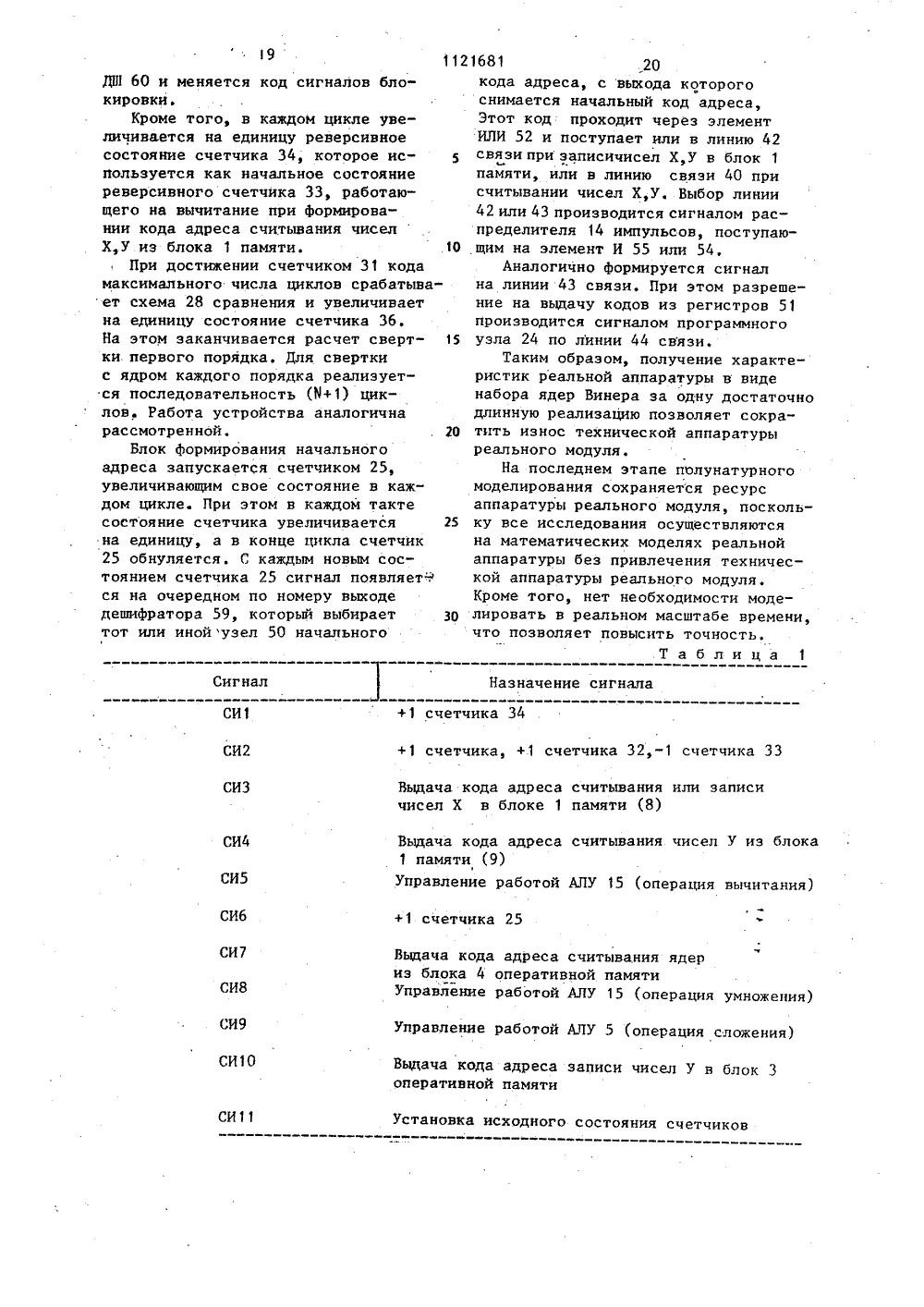

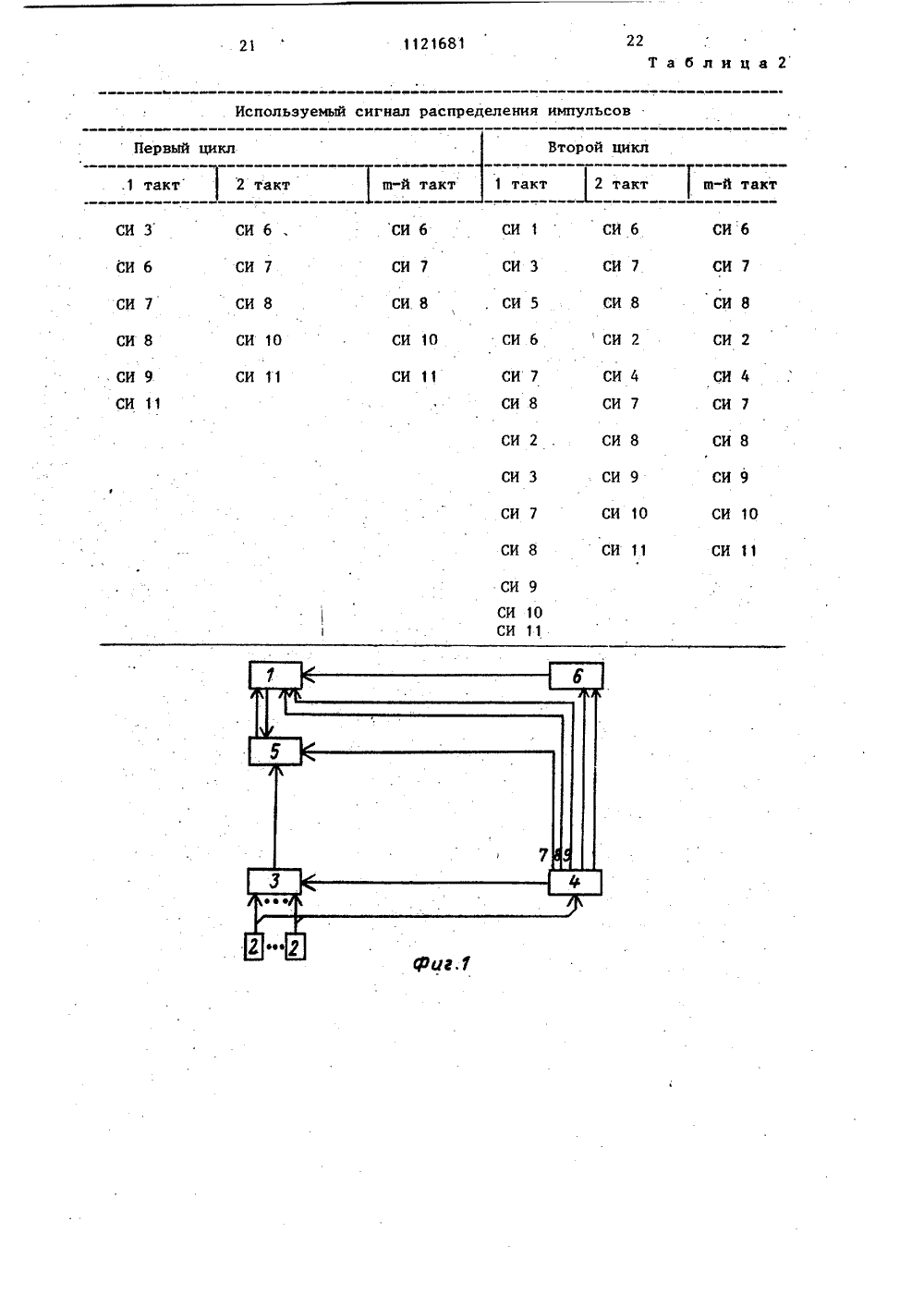

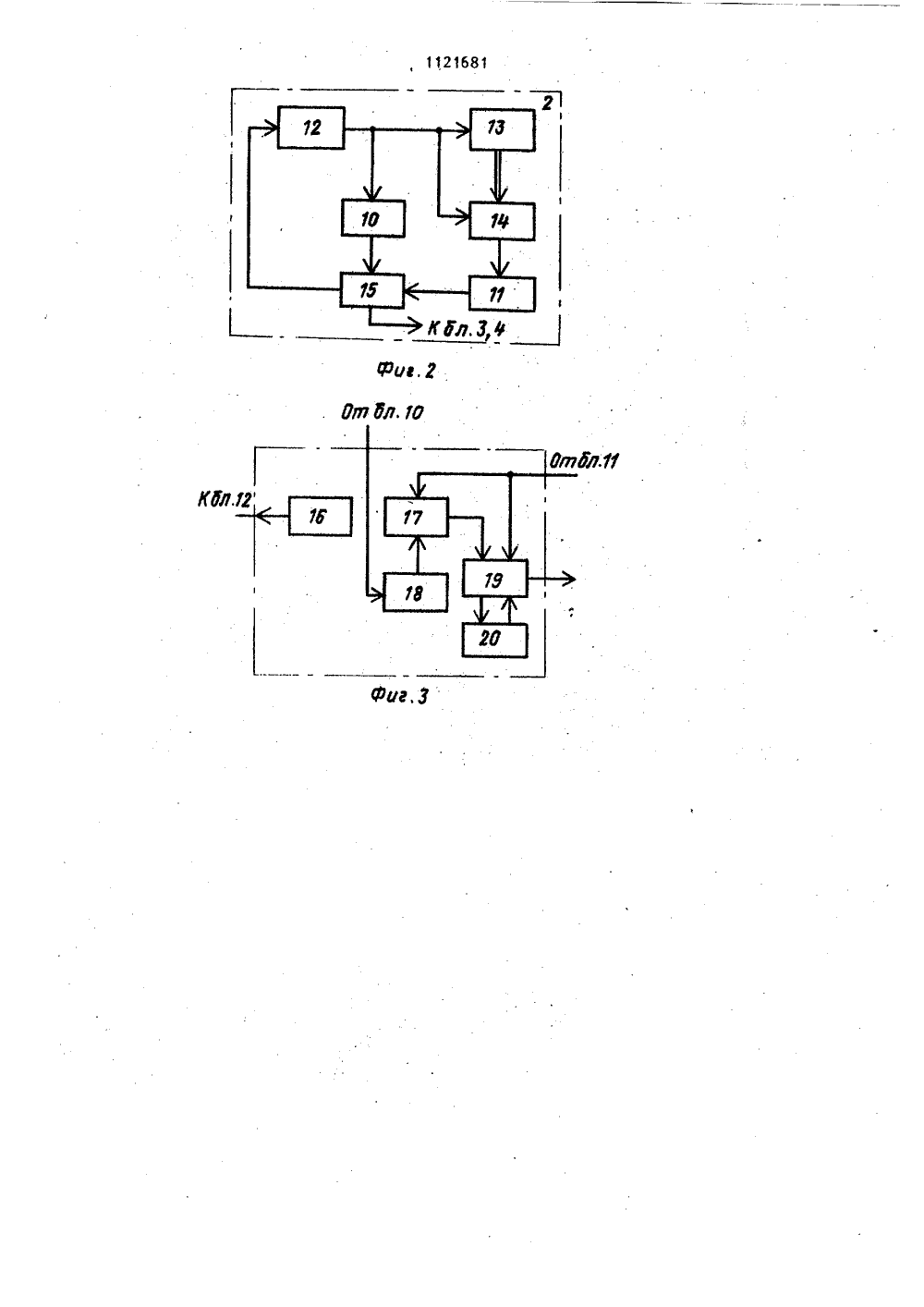

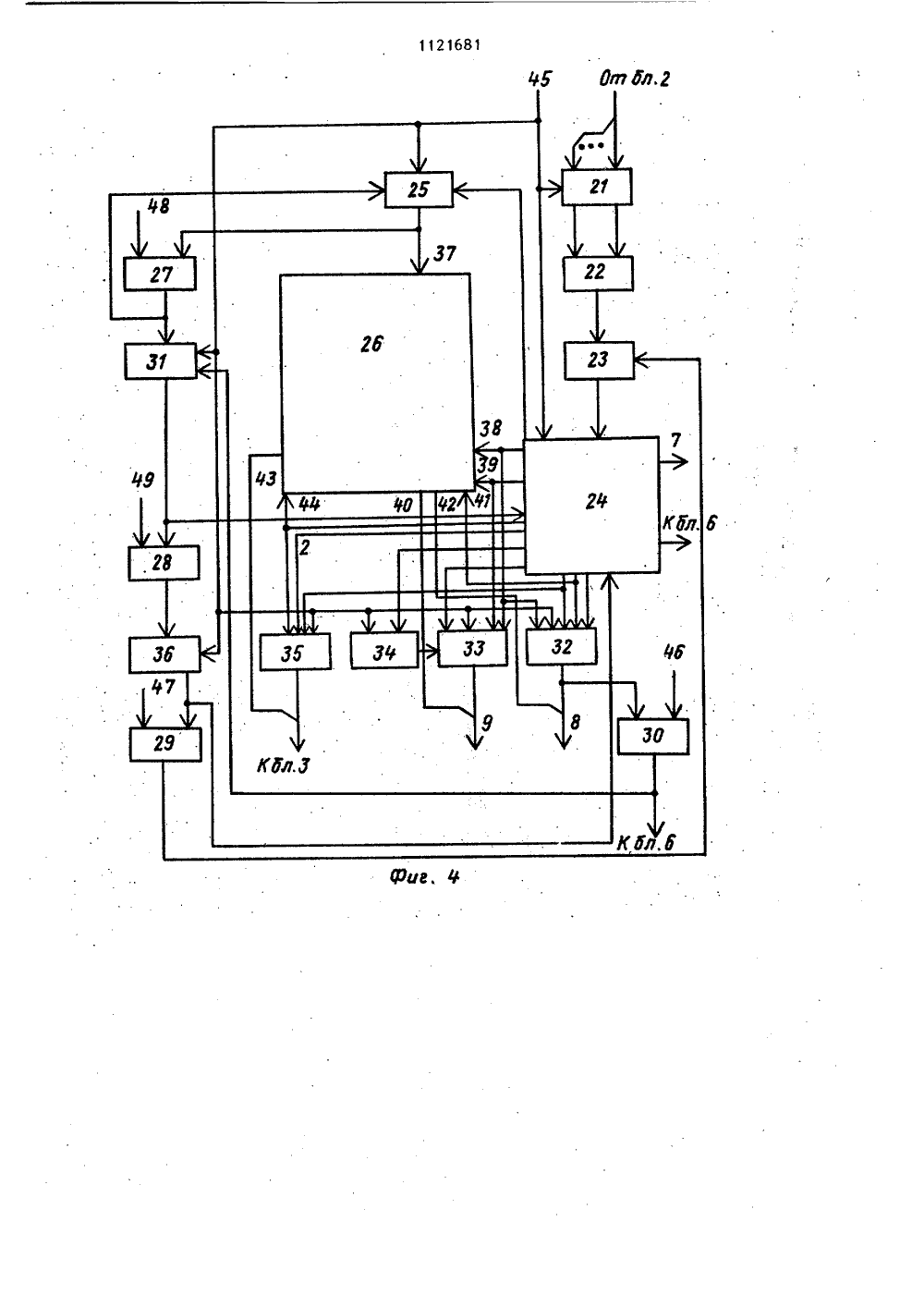

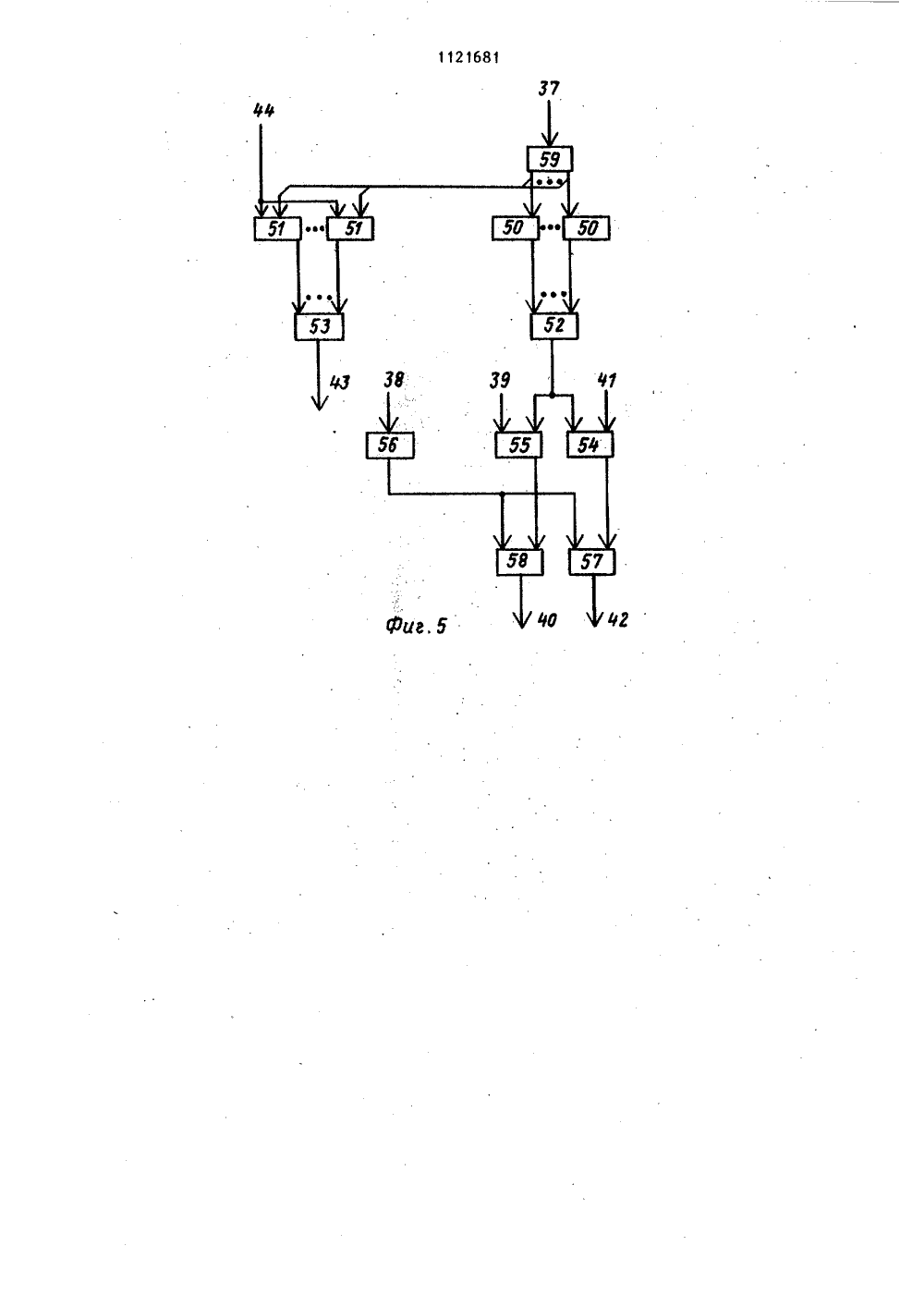

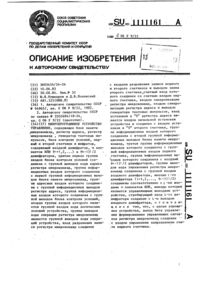

(19) (1) СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК зс 5 ц 6 06 б 7/48 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ. И ОТКРЫТЮОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 2( - (,1),з(71) Московский институт электронного машиностроения(54)(57) 1, СИСТЕМА ПОЛУНАТУРНОГОМОДЕЛИРОВАНИЯ ДИНАМИЧ СКИХ Сг 1 СТГМ,содержащая реальный модуль, включающий аналоговый генератор шума,выход которого подключен к входудинамического стецлл и входу исследуемой реальной аппаратуры, кицематически связанной с динамическимстендом, и ренгающий блок, первый выход которого. подключен к входу аналогового генератора шума, а второйвыход является выходом реальногомодуля, о т л и ч л ю щ а я с ятем, что, с целью повышения точностимоделирования и повышения надежностисистемы, она дополнительно содержитгенератор пробных воздействий, блокоперативной памяти, блок памяти,блок управления системой, арифметичес.кое устройство и группу реальных модулей по числу:моделипуемьж подсистемреальной аппаратуры, а каждый реальный модуль содержит первый и второйаггллого-цифровые преобрл зовдтеливходы которых соединены соответственно с выходом аналогового генераторашума и выходом исследуемой реальнойаппаратуры, л выходы подклн 1 чены ксоответствунагим входлм решлющего блока, вьход каждого рслльного модуляподклнлген к соответствующггм информлциоццым входам блока управлениясистемы ц блока оперативной пдмяти,выхол которого соелицец с первым инАормлггионнь 1 м входом арифметическогоустройства, выход и второй цнАормлциоццый вход которого соелццецысоответственно с первым инйормдцион-цьм входом и выходом блока памятц,второй иггформлциоггный вход которого,подключен к выходу генератора пробных воздействий, а блок управлениясистемой содержит регистр, элемент И, рпрограммный узел, четыре схемы сравнения, четыре счетчика, счетчик тактов, счетчик циклов, счетчик порядкаядер, узел гггормировлггия адреса, объедицеццые установочные входы регистра, программного узла, счетчика тактов, счетчика циклов, счетчика порядка ядер и четырех счетчиков являютсяустановочным входом блока управления, разрядные входы регистра являются инАормациоггными вхолами блока управления системы, а разрядные виходырегистра соединены соответственнос входами элемента И, вымол которого подключен к входу запуска генератора тактовых импульсов, выход которого подключен к тактовому входу программного узла, первые входы первой,второй, третьей и четвертой схемсравнения являются соответствующими1121ка ядра первого реального модуля(результат в -го такта предыдущего цикла), причем текущее зна-чение переменной 1 выбираетсяс учетом значения переменной свер-.тываемого ядра. Это отличие сохраняется при свертке с любым порядкомядра. Если система разомкнута, тоядро свертывается только с белымгауссовским процессом Х (1), причем текущее значение дискрета такжевыбирается с учетом значения переменной свертываемого ядра.Рассмотрим подробнее очередностьдействий системы полунатурного моделирования на втором этапе, причемпусть, как более, общий случай,моделируется динамическая системазамкнутого типа.Исходное состояние всех счетчиковустанавливается сигналом по линии45 связи.Работа системы моделирования заключается в последовательном выполнении ряда циклов под управлениемпрограммного узла 24 и блока 4 управления.30Нулевой цикл - запуск генератора6 пробных воздействий, формированиевходных чисел Х(,1=0, й в видебелого дискретного гауссовского процесса и запись их в блок 1 памяти. 35Код адреса записи чисел состоитиз кода постоянного начального адреса,формируемого регистром 56 и передаваемого .через элемент ИЛИ 57, икода переменного текущего адреса, 40формируемого счетчиком 32 адреса записи чисел. Перед записью каждогоочередного числа Х в блок 1.памятисигналом от узла 24 состояние,счетчика 32 увеличивается на единицу.При 45записи в блок 1 памяти Н -го числаХ(М) происходит совпадение выходногокода счетчика 32 и Й -го кода длинымассива чисел, заданного в схеме 30,сравнения, при этом управляющий сигнал, идущий с выхода схемы 30 сравнения, останавливает работу генератора 12 шума. После записи входных чисел после довательно обрабатываются ядра всех порядков начиная с первого, т.е. осуществляется композиция всех реаль в такт, (О)=Ь(О)У, (О)2 цикл: Обработка первойпо всем реальным модулям1 такт: композиция модулей, нулевая точка линейной реакции модулируемой системы точки 1 (1) 681 16ных подсистем. Сначала выполняетсяпервая группа М + 1 циклов каждыйпо В тактов, в результате чего определяется свертка входного сигналас ядром первого порядка всех реальных модулей. Эта свертка являетсялинейной частью реакции моделируемойсистемы. Далее выполняется втораягруппа циклов по определению свертки с ядром второго порядка, т,е.определяется квадратическая реакция моделируемой системы, и т.д,Всего выполняется 0 (И+1) циклов(где й - максимальный порядок ядерВинера всех остальных подсистем),Ниже приведенное напряжение, поясняющие алгоритм функционированиясистемы полунатурального моделирования на втором этапе для болееобщего случая, когда моделируемаязамкнутая система, причем, еслисистема разомкнута, работа осуществляется но такому же алгоритму, стой лишь разницей, что в первомтакте каждого цикла ядра свертываются только с входным сигналом. Перваягруппа 8 +1 циклов, в которой осуществляется свертка с ядрами первогопорядками,:,(К),Ь (К) Ь(К), (где Кмаксимальное чйсло дискретов ядра,1 циклОбработка нулевой точкиУщ(Опо всем реальным модулям1 такт: 1,(0) Ь 1(О) Х(0) - для первогомодуля,2 такт:;. (, (О) -" Ь,(О У(0) - композицияпервыхдвух реальных модулей3 такт: У,(0)= п,(0)Ч, (0) - композицияпервых трехреальныхмодулей+1 счетчика, +1 счетчика 32,-1 счетчика 33 СИ 2 Выдача кода адреса считывания или записичисел Х в блоке 1 памяти (8) СИЗ Выдача кода адреса считывания чисел У из блока1 памяти (9)Управление работой АЛУ 15 (операция вычитания) СИ 4 СИ 5 СИ 6+1 счетчика 25 Выдача кода адреса считывания ядериз блока 4 оперативной памятиУправление работой АЛУ 15 (операция умножения) СИ 7 СИ 8 СИ 9 Управление работой АЛУ 5 (операция сложения) Выдача кода адреса записи чисел У в блок 3оперативной памяти СИ 10 СИ 11 Установка исходного состояния счетчиков ДШ 60 и меняется код сигналов блокировки.Кроме того, в каждом цикле увеличивается на единицу реверсивное состояние счетчика 34, которое используется как начальное состояние реверсивного счетчика 33, работающего на вычитание при формировании кода адреса считывания чисел Х,У из блока 1 памяти.При достижении счетчиком 31 кода максимального числа циклов срабатывает схема 28 сравнения и увеличивает на единицу состояние счетчика 36. На этом заканчивается расчет свертки.первого порядка. Для свертки с ядром каждого порядка реализуется последовательность 9+1) циклов. Работа устройства аналогична рассмотренной.Блок формирования начального адреса запускается счетчиком 25, увеличивающим свое состояние в каждом цикле. При этом в каждом такте состояние счетчика увеличивается на единицу, а в конце цикла счетчик 25 обнуляется. С каждым новым состоянием счетчика 25 сигнал появляет ся на очередном по номеру выходе дешифратора 59, который выбирает тот или иной узел 50 начального 1681 20кода адреса, с выхода которого снимается начальный код адреса, Этот код проходит через элемент ИЛИ 52 и поступает или в линию 42 связи при записичисел Х,У в блок 1 памяти, или в линию связи 40 при считывании чисел Х,У. Выбор линии 42 или 43 производится сигналом распределителя 14 импульсов, поступающим на элемент И 55 или 54.Аналогично формируется сигнал на линии 43 связи, При этом разрешение на выдачу кодов из регистров 5 производится сигналом программного узла 24 по линни 44 связи.Таким образом, получение характеристик реальной аппаратуры в виде набора ядер Винера за одну достаточно длинную реализацию позволяет сократить износ технической аппаратуры реального модуля.На последнем этапе полунатурного моделирования сохраняется ресурс аппаратуры реального модуля, поскольку все исследования осуществляются на математических моделях реальной аппаратуры без привлечения технической аппаратуры реального модуля. Кроме того, нет необходимости моделировать в реальном масштабе времени, что позволяет повысить точность.Т а б. л и ц а 122 1121681 21 Таблица 2 Используемый сигнал распределения импульсов Второй цикл Первый цикл 1 такт 2 такт СИ 6 СИ 6 СИ 6 СИ 3 СИ 7 СИ 7 СИ 3 СИ 7 СИ 6 СИ 8 СИ 5 СИ 8 СИ 8 СИ 7 СИ 6 СИ 10 СИ 2 СИ 8 СИ 10 СИ 9 СИ 11 СИ 4 СИ 4 СИ 7 СИ 11 СИ 8 СИ 7 СИ 11 СИ 7 СИ 8 СИ 2 СИ 8 СИ 9 СИ 9 СИ 3 СИ 10 СИ 7 СИ 10 СИ 11 СИ 8 СИ 11 СИ 91121681 ректор Г, Решетн едакт ж 698омитетаоткрытушская Подписное аз 7983/38 Ти ВНИИПИ Государственногопо делам иэобретений 113035, Москва, Ж,д. 4/ ектная, 4 ППП "Патент", г. Ужгород, ул Составитель В. ФукаЛ, Пчелинская Техред Л.Микеши второму входу счетчика циклов, первый выход узла формирования адреса и выход первого счетчика блока управления системой соединены соответственно с первой группой адресных входов блока памяти, втораягруппа адресных входов которогоподключена соответственно к второмувыходу узла формирования адреса и выходу второго счетчика, третий выходузла формирования адреса и выход четвертого счетчика соединены с адресными входами блока оперативной памяти,группа управляющих выходов програм"много узла соединена соответственнос входами управления сложением,вычитанием и умножением арифметического устройства, а выход первогосчетчика соединен с вторым входомчетвертой схемы сравнения,2. Система по п.1, о т л и ч а ющ а я с я тем, что узел формирования адреса содержит дешифратор, регистр, две группы регистров, дваэлемента И и;,четыре элемента ИЛИ,причем вход дешифратора являетсяпервым входом узла формирования адреса, а выходы подключены соответственно к входам регистров первой группы и первым входам регистров второйгруппы, выходы регистров первой группы подключены к соответствующимвходам первого элемента ИЛИ, выходкоторого соединен с первыми входамипервого и второго элементов И, выходы. которых подключены соответственно к первым входам третьего ичетвертого элементов ИЛИ, вторыевходы которых соединены с выходомрегистра, выходы регистров второйгруппы соединены с соответствующимивходами второго элемента ИЛИ, вторымвходом узла формирования адреса яв-.ляется вход регистра, третьим входомузла формирования адреса является второй вход второго элемента И, четвертым входом узла форжрования адреса являются вторые входы регистроввторой группы, а пятым входом узлаформирования адреса является второйвход первого элемента И, первым ивторым выходами узла формированияадреса являются соответственно выходы третьего и четвертого элементовИЛИ, а третьим выходом - выход второго элемента ИЛИ.Ф3. Система по пп.1 и 2, . о т л ич а ю щ а я с я тем, что програминый узел содержит первый, второйи третий счетчики, дешифратор, двегруппы элементов И, три элементаИЛИ, постоянное запоминающее устройство, две схемы сравнения, эле1121681 мент И и триггер, причем тактовыйвход первого счетчика являетсятактовым входом программного узла,установочньм входом которого является установочный вход первого счетчика, соединенный с первыми входамипервого и второго элементов ИЛИ,первым и вторым информационными входами программного узла являютсясоответственно-первый и второй адресные входы постоянного запоминающего устройства, первый адресный входкоторого соединен также с входомтретьего элемента ИЛИ, разрядные выходы первого счетчика соединенысоответственно с входами дешифратора, первый - одиннадцатый выходыкоторого подключены соответственнок первым входам элементов И первойгруппы, вторые входы которых объединены и соединены с первым выходомпостоянного запоминающего устройства,второй и третий выходы которогоподключены соответственно к первымвходам первой и второй схем сравнения, вторые входы которых соединенысоответственно с выходами второгои третьего счетчиков, а управляющиевходы первой и второй схем сравнениясоединены с двенадцатым и тринадцатымвыходами дешифратора, одиннадцатыйвыход дешифратора соединен такжес информационным входом второгосчетчика, установочный вход которогоподключен квыходу второго элементаИЛИ, второй вход которого соединенс выходом первой схемы сравнения,первым входом элемента И и информационным входом третьего счетчика,установочный вход которого подключен к выходу первого элемента ИЛИ;первому входу триггера .и инверсномувходу элемента И, выход которогосоединен с вторым входом триггера,Изобретение относится к специали-. зированным средствам вычислительной техники и может быть использовано при полунатурном моделировании летательных аппаратов, энергоблоков, 5 технологических процессов и т.п. совместно с системами управления. выход которого подключен к первомуинверсному входу первого элементаИ второй группы и третьему адресномувходу постоянного запоминающего устройства, четвертый адресный входкоторого соединен с выходом второгосчетчика, выход второй схемы сравнения подключен к второму входу элемента ИЛИ, выход первого элементаИ первой группы соединен с первымпрямым входом первого элемента Ивторой группы и первыми входами второго и четвертого элементов И второй группы, выход второго элемента Ипервой группы соединен с первымивходами третьего и пятого элементовИ второй группы, выход второго элемента ИЛИ подключен к второму инверсному входу первого элемента И второйгруппы и вторым входам второго-пятогоэлементов И второй группы, первым выходам программного узла являетсявыход шестого элемента И первой группы, вторым, третьим, и четвертымвыходами программного узла являютсясоответственно вьжоды третьего и четвертого элементов И первой группы и .выход второго элемента И второйгруппы, пятым и шестым выходами программного узла являются соответственно выходы седьмого элемента И второй группы, седьмым выходом являются объединенные выходы четвертогои пятого элементов И второй группы,восьмым, девятым и десятым выходамипрограммного узла являются соответственно выходы одиннадцатого, десятогои второго элементов И первой группы,одиннадцатьи выходом программногоузла является выход .первого элементаИ второй группы, а группой управляющих выходов программного узла являются выходы пятого, восьмого и девятого,элементов И первой группы. Известны устройства предназначенные для полунатурного моделирования нелинейных систем, содержащие блок реальной аппаратуры, установленной на платформе вибрационного стенда, блок мбделирования, блок моделирования образиной передаточной функции,3 112168датчик колебаний, сумматор, усилитель и блок усреднения, причем выход датчикаколебаний соединен с входом блока моделирования, выход которого соединен с входом блока моделирования обратной передаточной функции, его выход и выход датчика колебаний через блок усреднения соединеныс входами сумматора, выход которогочерез усилитель соединен с вибрацион-Оным стендом, выходы которых подсоединены к входу блока реальной аппаратуры, а его выход соединен с входомдатчика колебаний 1 и 2,Однако укаэанные устройства имеют невысокую надежность, обусловленную замкнутой структурой полунатур-ной модели, состоящей из блока моде"лирования математической части моделируемой модели, сопряженного с. комплексом технической аппаратуры,низкую точность, обусловленную неоднократным использованием полунатурного моделирования для получения статистически устойчивых результатов 25моделирования, большую сложностьсоздания полунатурной модели в связи с необходимостью моделированияв реальном времени.Известно также устройство, содер- З 0 .жащее хронометр, регистр сдвига,блок управления, арифметическологическое устройство и блок памяти;с помощью которого возможно вычисление ядер винера 31,35Наиболее близкой к предлагаемомуявляется система полунатурного моделирования с динамическими стендами,включает в себя имитатор воздействий,динамический стенд, на подвижной 40платформе которого установлена исследуемая реальная аппаратура, а также решающее устройство, причем выходреальной аппаратуры подсоединенк входу решающего устройства, выход которого соединен с входами динамического стенда и имитаторавоздействий, выходы которых соединены,с входами реальной аппаратуры. Даннаясистема позволяет воспроизводить влабораторных условиях режимы полеталетательного аппарата, весьма близкиек реальным 141. Сложные динамические системы являются обычно многоконтурными, Поду" 55 натурное моделирование такой систе" мы осуществляется путем последовательного моделирования системы с наращиваемыми контурами управления Причем для решения задачтаких как установление источников отказов сис- темы и получение статистических характеристик системы, проводится МП циклов моделирования, где М - чис ло циклов моделирования по каждому контуру управления, и - число кон- туров управления,. Такое моделирование сопряжено со значительными материальными и временными затратами, поскольку приходится неоднократно привлекать динамические стенды и реальную аппаратуру. Многократное использование элемента приводит к уменьшению его ресурса, а следовательно, уменьшается вероятность безотказной работы всей полунатурной модели, представляющей последовательное соединение элементов,Поскольку полунатурное моделирование осуществляется по замкнутому контуру, необходимо, чтобы оно протекало в реальном масштабе времени, От реального времени зависит не только временная последователь- ность решения тех или иных задач но и получаемые в результате данные. ЭФфективность моделирования в реальном времени определяется задержкой сообщений перед их обработкой, вероятностью потери сообщений, необходимостью подключения дополнительных вычислительных средств, Поэтому одной из важных проблем полунатурного моделирования является проблема оперативного управления вычислительным процессом в реальном времени и высокого быстродействия вычислительных средств.Цель изобретения - повышение. точности моделирования и повышение надежности системы путем введения взаимосвязанных реальных модулей по числу подсистем реальной аппаратуры. Поставленная цель достигается тем, что в систему полунатурного моделирования динамических систем, содержащую реальный модуль; включающий аналоговый генератор шума, выход которого подключен к входу динамического стенда и входу исследуемой реальной аппаратуры, кинематически связанной с динамическим стендом., и решающий блок, первый выход которого подключен к .входу аналогового генератора шума, авторой выход является выходом реаль" ного модуля, введены генератор пробньм воздействий, блок оперативной памяти, блок памяти, блок управления системы, арифметическое уст ройство и группа реальных модулей по числу моделируемых подсистем реальной аппаратуры, а каждый реальный модуль содержит первый и второй аналого-цифровые преобразователи, 10 входы которых соединены соответственно с выходом аналогового генератора шума и выходом исследуемойреальной аппаратуры, а выходы подключены к соответствующим входам 15 решающего блока, выход каждого реального модуля подключен к соответствующим информационным входам блока управления системы и блока оперативной памяти, выход которого соединен 20 с первым информационным входом арифметического устройства, выход и второй информационный вход которого соединены соответственно с первым информационным входом и выходом блока памяти, второй информационный вход которого подключен к выходу генератора пробных воздействий,а блок управления системой содержит регистр, элемент И, программный узел, четыре схемы сравнения, четыре счетчика, счетчик тактов, счетчик циклов, счетчик порядка ядер, узел формирования адреса, объединенные установочные 35 входы регистра, программного узла, счетчика тактов, счетчика циклов, счетчика порядка ядер и четырех счет- чиков являются установочным входом блока ус 1 равления разрядные входы регистра являются информационными входами блока управлениясистемы, а разрядные выходы регист-ра соединены соответственно с входами элемента И, выход которого подключен ,к входу запуска генератора тактовых импульсов, выход которого подключен к тактовому входу программного узла, первые входы первой, второй, третьей и четвертой схем сравнения являются 50соответствующими установочными входами блока управления системой, выход первой схемы сравнения соединен с первым входом счетчика циклов и обнуляющим входом счетчика тактов, выход которого подключен к первому входу узла формирования адреса а также второму входу первой схемы сравнения, выход счетчика циклов соединен с первым ин"формационным входом программного узлаи вторым входом второй схемы сравнения, выход которой подключен к входусчетчика порядка ядер, выход которого соединен с вторым информационнымвходом программного узла и вторымвходом третьей схемы сравнения,выход которой подключен к входуостанова генератора тактовых импульсов, первый выход программного узлаподключен к информационному входусчетчика тактов, второй выход программного узла соединен с вторымвходом узла формирования адресаи первыми суммирующими входами первогои второго суммирующего счетчиков,третий выход программного узла соединен стретьим входом узла формированияадреса и вторым суммирующим входомвторого счетчика, четвертый выходпрограммного узла подключен, к входутретьего счетчика, выход которогосоединен с вычитающим входом второгосчетчика, пятый выход программногоузла подключен к четвертомувходуузла формирования адреса и первомувходу чегвертого счетчика, второйвход которого соединен с шестымвыходом программного узла, сеЛьмой выход которого соединен стретьим суммирующим входом второгосчетчика, второй вход первого счет-.чика и третий вход четвертого счетчика подключены к восьмому выходупрограммного узла, девятый выход которого соединен с пятым входом узлаформирования адреса и третьим входом первого счетчика, четвертыйвход которого подключен к десятомувыходу программного узла, одиннадцатый выход которого соединен с входом запуска генератора пробных воздействий, вход останова которогоподключен к выходу четвертой схемысравнения и второму входу счетчикациклов, первый выход узла формирования адреса и выход первого счетчикаблока управления системой соединенысоответственно с первой группой адресных входов блока памяти, втораягруппа адресных входов которого подключена соответственно к второму выходуузла формирования адреса и выходувторого счетчика, третий вьосодузла формирования адреса и выходчетвертого счетчика соединены садресными входами блока оперативнойпамяти, группа управляющих выходовпрограммного узла соединена соответственно с входами управления сложением, вычитанием и умножением арифметического устройства, а выход первого счетчика соединен с вторым вхо дом четвертой схемы сравнения.Узел формирования адреса содержит дешифратор, регистр, две группы регистров два элемента И и четыре элемента ИЛИ, причем вход дешифратора является первым входом узла формирования адреса, а выходы подключе-: ны соответственно к входам регистров первой группы и первым входам регистров второй группы, выхо ды регистров. первой группы подключены соответственно к входам первого элемента ИЛИ, выход которого соединен с первыми входами первого и второго элементов И, выходы которых подклю чены соответственно к первым входам третьего и четвертого элементов ИЛИ, вторые входы которых соединены с выходом регистра, выходы регистров второй группы соединены с соответст вующими входами второго элемента ИЛИ, вторым входом узла формирования адреса является вход регистра, третьим входом - второй вход второго элемен" та И, четвертым входом узла формирования адреса являются вторые входы регистров второй группы, а пятым входом узла формирования адреса является второй вход первого элемента И, первым и вторым выходами узла формирования адреса являются соответственно выходы третьего и четвертого элементов ИЛИ, а третьим выходом - вы-, ход второго элемента ИЛИ.Программный узел содержит первый, второй, и третий счетчики, дешифратор, две группы элементов И, три элемента ИЛИ, постоянное запоминающее устройство, две схемы сравнения, элемент И и триггер, причем тактовый45 вход первого счетчика является тактовым входом программного узла, установочным входом которого является установочный вход первого счетчика, соединенный с первыми входами перво" го и второго элементов. ИЛИ, первым50 и вторым информационными входами программного узла являются соответственно первый и второй адресные входы постоянного запоминающего устройства, первый адресный вход которого соединен также с входом третьего элемента ,ИЛИ, разрядные выходы первого счетчика соединены соответственно с входами дешифратора, первый - одиннадцатый выходы которого подключены соответственно к первым входам элементов И первой группы, вторые входы которых объединены и соединены с первым выходом постоянного запоминающего устройства, второй и третий выходы которого подключены соответственно к первым входам первой и второй схем сравнения, вторые входы которых соединены соответственно с выходами второго и третьего счетчиков, а управляющие входы первой и второй схем сравнения соединены с двенадцатым и тринадцатыми выходами дешифратора одиннадцатый выход дешифратора соединен также с информационным входом второго счетчика, установочный вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом первой схемы сравнения, первым входом элемента И и информационным входом третьего счетчика, установочный вход которого подключен к выходу первого элемента ИЛИ, первому входу триггера .и инверсному входу элемента И, выход которого соединен с вторым входом триггера, выход которого подключен к первому инверсному входу первого элемента И второй группы и третьему адресному входу постоянного запоминающего устройства, четвертый адресный вход которого соединен с выходом второго счетчика, выход второй схемы сравнения подключен к второму входу первого элемента ИЛИ, выход первого элемента И первой группы соединен с первым прямым входом первого эле- мента И второй группы и первыми входами второго и четвертого элементов И второй группы, выход второго элемента И первой группы соединен,с первыми входами третьего и пятого элементов И второй группы, выход второго элемента ИЛИ подключен к второму инверсному входу первого элемента И второй группы и вто" рым входам второго-пятого элементов,И второй группы, первым выходомпрограммного узла является выход шестого элемента И первой группы, вторым, третьим и четвертым выходами программного узла являются соответственно выходы третьего и четвертого элементов И первой группы и выход второго элемента И второй группы,На Фиг.1 представлена блок -схемасистемы полунатурного моделированиядинамических систем на Фиг.2блок-схема реального модуля, нафиг,3 - сумма решающего блока нафиг,4 - блок управления на фиг.5 -блок формирования начального адреса,на фиг.б - схема распределителяимпульсов.Система содержит блок 1 памяти,группу реальных модулей 2, блок 3оперативной памяти, блок 4 управлениясистемы, арифметический блок 5, ге-. ЗОнератор 6 пробных воздействий и выходи 7-9 блока управления системы. .Реальный модуль 2 содержит аналбго-цифровые преобразователи 10 и 11,аналоговый генератор,12 шума, динами-З 5ческий стенд 13, исследуемую реальную аппаратуру 14 и решающий блок 15,причем выход аналогового генератора12 шума соединен с входами динамического стенда 13 АЦП 10 и реальной 4 Оаппаратуры 14, второй вход которойсоединен с выходами динамическогостенда 13, выход реальной аппаратуры 14 подключен к входу АЦП 11,а его выход соединен с одним из 45входов решающего блока 15, другойвход которого соединен с выходомАЦП 10, первый выход решающего блока 15 соединен с входом аналогового генератора 12 шума, а второй его.выход является выходом модуля и соединен с входом блока оперативнойпамяти, 3 и входом блока 4 управления системы. 20 Решающий блок 15 реализован посхеме, предложенной в 31 и содержитхронометр 16, управляющий работойгенератора шума блок 17 управления,. пятым и шестым выходами программного,узла являются соответственно выходыседьмого элемента И второй группыседьмым выходом являются объединенныевыходы четвертого и пятого элемен" 5тов Ивторой группы, восьмым, девятыми десятым вьмодами программного узлаявляются соответственно выходы одиннадцатого, десятого и второго элементов И первой группы, одиннадцатым 1 Овыходом программного узла являетсявыход первого элемента И второйгруппы, а группой управляющих выхо-,дов программного узла являются выходыпятого, восьмого и девятого элементов И первой группы. регистр 18 сдвига, арифметико-логи"ческое устройство (АЛУ) 19 и блок20 памяти.Решающий блок 15 включается всхему реального модуля 2 следующимобразом.Выход АЦП 10 соединен с входом ре"гистра сдвига а выход АЦП 11 соединенс входами АЛУ 19 и блока 17 управления.Блок 4 управления системы (Фиг.4)содержит регистр 21, элемент И 22,генератор 23 тактовых импульсов,программный узел 24, счетчик 25 тактов узел 26 формирования адреса,первую - четвертую схемы 27-30 сравнения, счетчик 31 циклов, первыйчетвертый счетчики 32-35 импульсов,счетчик 36 порядка ядра, входы ивыходы 37-44 узла 26 Формированияадреса установочный вход 45 блокаи установочные входы 46-49.схемсравнения,Блок 26 формирования адреса содержит первую 50 и вторую 51 группырегистров, первый 52 и второй 53 элементы ИЛИ, первый 54 и второй 55элементы И, регистр 56, третий 57и четвертый 58 элементы ИЛИ, а такжедешифратор 59.Распределитель 24 импульсов реализован по схеме Фиг.б. Он содержитдешифратор 60 (ДШ) узел 61 блокировки, включающий в себя первую группуэлементов И 62, вторую группу элементов И 63, элемент ИЛИ 64, триггер65, второй счетчик 66, второй элементИЛИ 67, вторую и первую схемы 68,69сравнения, элемент 70, третий счетчик 7 1, элемент ИЛИ 72 и постоянноезапоминающее, устройство 73, а такжепервый счетчик 74,Назначение сигналов распределителя24 импульсов (РИ) приведено в табл.1,а порядок выдачи синхросигналов рас "пределителем импульсов в .в табл.2. Программный узел работает следующим образом.При подаче сигналов на 1-й (управляющий) вход. счетчика 74 от блока 23 на выходе ДШ 60 формируется повторяющаяся последовательность сигналов с 1 по 13, представляющих собой собственный цикл работы ДЦ 60, из которых сигналы с 1 по 11 используются для формирования выходных управляющих сигналов РИ 24 /СИ 1-СИ 11), 1121681а сигналы с 11 по 13 - для управления элементами узла 61 блокировки.Каждый из циклов работы системыпредставляет собой последовательность выполнения щ тактов. В свою очередь, 5 каждый такт представляет собой выполнение одного или ряда собственных циклов ДШ 60 в зависимости от порядка рассчитываемой свертки. В каждом собственном цикле ДШ 60 осуществляет ся блокировка его сигналов с 1 по 11.При этом в тактах с второго по щ -й каждого из В циклов условия блокировки сигналов СИ 1-СИ 11 одинаковы (табл.2). 15Блокировка сигналов 1-10 ДШ 60.осуществляется элементами И 62 и 63в соответствии с кодом сигналом блокировки, поступающим с первого выходаПЗУ 73.При подаче на ПЗУ 73 кода адресана его первом, втором и третьемвыходах формируется потенциальныйкод числа.Код адреса - А-разрядный код,начиная со старшего разряда состоящий из кода порядка ядра Ф-разрядов), снимаемого с выхода счетчика36 кода текущего номера цикла (гУ30разрядов) снимаемого с выхода счетчика 3 1 и выхода триггера 65 (1 разряд)и кода текущего номера собственногоцикла ДШ 60 ( разрядовснимаемогос выхода счетчика 66.Код числа, снимаемый с первого, 35второго, третьего выходов ПЗУ 73 это " В-разрядный код, Начиная с младмладшего разряда код числа состоитиз кода сигналов блокировки (11 разрядов), снимаемого с первого выхода 40ПЗУ 73 и используемого для блокировки сигналов СИ 1 - СИ 11, кода максимального числа собственных цикловДШ 60 в текущем такте ( 5 разрядов),снимаемого со второго выхода ПЗУ 73, 45и кода максимального числа тактовв цикле (разрядов), снимаемогос третьего выхода ПЗУ 73.С изменением любого из разрядовкода адреса с выхода ПЗУ 73 снимается новый код числа,Один из разрядов кода адресаформируется триггером 65, которыйнаходится в состоянии 0 в первомтакте и. в состоянии "1" во всех остальных тактах, Это вызвано тем,, что в тактах со 2-го по е -й каж, дого из циклов условия блокировки 12сигналов СИ 1 - СИ 11 одинаковы,и в то же время отличаются от условий блокировки в первом такте(табл.2).С каждым собственным циклом Д 11 60состояние счетчика 66 увеличиваетсяна единицу, при совпадении кодасчетчика 66 с кодом на втором выходаПЗУ 73 схема 69 сравнения выдаетсигнал окончания такта, обнуляющийсчетчик 66 и увеличивающий состояниесчетчика 71 на единицу. При этомтриггер 65 при выполнении 1-го тактанаходится в нуле, а при выполнениитактов с 2-го по а -й в единице.С каждым тактом состояние счетчика 71 увеличивается на единицу. Присовпадении кода счетчика 71 с кодомна 3-ем выходе ПЗУ 73 схема 68 сравнения выдает сигнал окончания цикла, обнуляющий счетчик 71 и триггер 65.Прежде чем начать пелунатурноемоделирование, динамическая системаподвергается расчленению, т.е. измоделируемой системы выделяетсяизготовленная реальная аппаратура,образующая реальную подсистему,оставшаяся часть системы 1 котораяне может быть воспроизведена реальнов лабораторных условиях, описывается математической моделью, причемвсе внешние связи между математической моделью и реальной аппаратуройразрываются,Принцип работы системы заключается в следующем.В реальных модулях 2 производит- .ся идентификация реальной аппаратурыс целью определения ее динамическиххарактеристик. В зависимости отсложности моделируемой системы онаможет содержать несколько реальныхподсистем, которые идентифицируютсяв несвязанных реальных модулях2, т.е. осуществляется независимаяидентификация реальных подсистем.lРабота каждого реального модуляпроисходит в следующем порядке.В качестве тестирующего воздействия на реальную аппаратуру, а также входного воздействия на динамический стенд выбирается белый гауссов процесс, который вырабатывается генератором 12. Работой генератора 12 управляет хронометр, включенный в решающий блок 15.- Непрерывный белый гауссов процесс 11 Ц и реакция на него реальной аппаратуры 14 преобразуется в дискретные процессы в соответствующих АЦП 10 и 11.5Результатом идентификации является рассчитанный набор ядер Винера, которые представляют собой взаимокорреляционную Функцию соответствующего .порядка, 1 ОЯдро первого порядка рассчитывается за К циклов (К максимальное число дискретов ядра), т.е. ядро содержит К точек. В результате расчетов по числу по каждому циклу определяется 15 очередная точка ядра. Лля ядра первого порядка каждый цикл содержит Н- к тактов (1 - текущий дискрет ядра).Схема работы разрешающего блока 15 для расчета ядра первого порядка .20 имеет вид:о цикл, Расчет нулевой точки ядрап (О 1 такт: У(0)Х(0-0)=У(0)Х(0) 2 такт: У(1)Х(1-0)=У(1)Х(1) й такт: У(Н)Х(Й)=У(И)Х(И)1 цикл: Расчет первой тояки ядра 11 (1)1 такт: У(1)Х(1-1)=У(1)Х(0)2 такт: У(2) Х(2-1) =У(2)Х(1) йтакт У(М)Х(Я)К цикл: Расчет К-й точки ядра 11 (К)1 такт:У(Й-К)Х(0)2 такт: У(Ц-К+1) Х(1) Н-К такт: У(Й)Х(И-К)В каждом цикле расчеты всех тактов суммируются и умножаются на масштабный коэффициентС(Н 11) Аналогично осуществляется расчет ядер более высоких порядков с той лишь разницей, что в зависимости от порядка ядра количество циклов увеличивается.50Рассчитанные значения ядер каждого порядка записываются в блок 3 оперативной памяти. После записи последнего из рассчитываемых порядков ядер во всех разрядах регистра 21 блока 4 управления система занимает единица. На этом первый этап моделирования заканчивается и начинается 81 14второй этап полунатурного моделирования.В результате первого этапа в оперативной памяти 3 записана матрица ядра В на П (где п 1 - максимальное число столбцов, равное числу реальных модулей, й - максимальное число строк, равное максимальному порядку ядер Винера).Матрица имеет следующий вид"м пегпоюНа втором этапе моделирования осуществляется композиция подсистемсогласно структурной схеме моделируемой системы. Эта схема задаетсяочередностью порядковых номеровреальных модулей 2, причем дляпервого реальногб модуля определяетсясвертка ядра с белым гауссовскимпроцессом, а для последующих модулейопределяется свертка ядра с выходнымсигналом предыдущего модуля. Работойуправляет блок 4 управления системы,Гистема полунатурного моделирования позволяет моделировать как замкнутые, так и разомкнутые динамическиесистемы.Для обоих случаев второй этап моделирования осуществляется за и 011)циклов (где р - максимальный порядокядер Винера, 8 - максимальный порядковый номер дискрета). Каждыйцикл состоит из 1 п тактов (где 1 п -максимальное число реальных модулей2)Обычно выбирается одно значение 8 , одинаковое для всех 1 п реальных модулей. Значение И таоке выбирается для всех реальных модулей,исходя из максимального значения Ьвсех .щ реальных модулей.К первом цикле осуществляетсяобработка нулевого дискрета У(0по всем модулям, т;е. проводитсясвертка входного сигнала с ядромпервого порядка,В последующих циклах обрабатываются последующие номера дискретовтакже по всем реальным модулям. Начиная со второго цикла проявляется отличие в моделировании замкнутых .и разомкнутых систем.Это отличие возникает только в первом такте, где осуществляется свертЮ

СмотретьЗаявка

3492651, 01.10.1982

МОСКОВСКИЙ ИНСТИТУТ ЭЛЕКТРОННОГО МАШИНОСТРОЕНИЯ

БЕЛЮНОВ АНАТОЛИЙ НИКОЛАЕВИЧ, ПУПКОВ КОНСТАНТИН АЛЕКСАНДРОВИЧ, ЛУКЬЯНОВА НАТАЛЬЯ ВИКТОРОВНА, ОВЧИННИКОВ ЕВГЕНИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: динамических, моделирования, полунатурного, систем

Опубликовано: 30.10.1984

Код ссылки

<a href="https://patents.su/17-1121681-sistema-polunaturnogo-modelirovaniya-dinamicheskikh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Система полунатурного моделирования динамических систем</a>