Устройство микропрограммного управления диагностированием и восстановлением цифровых систем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

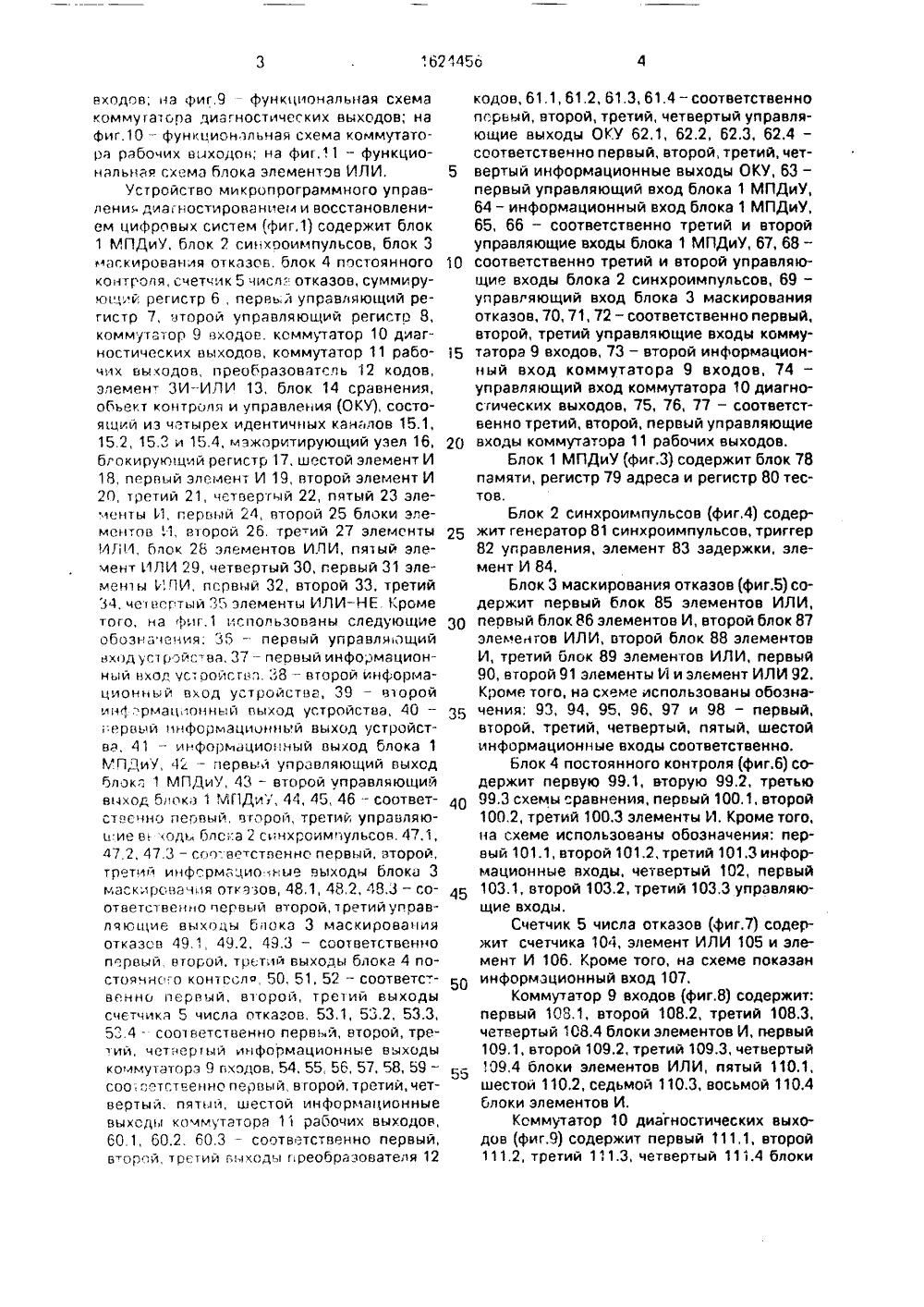

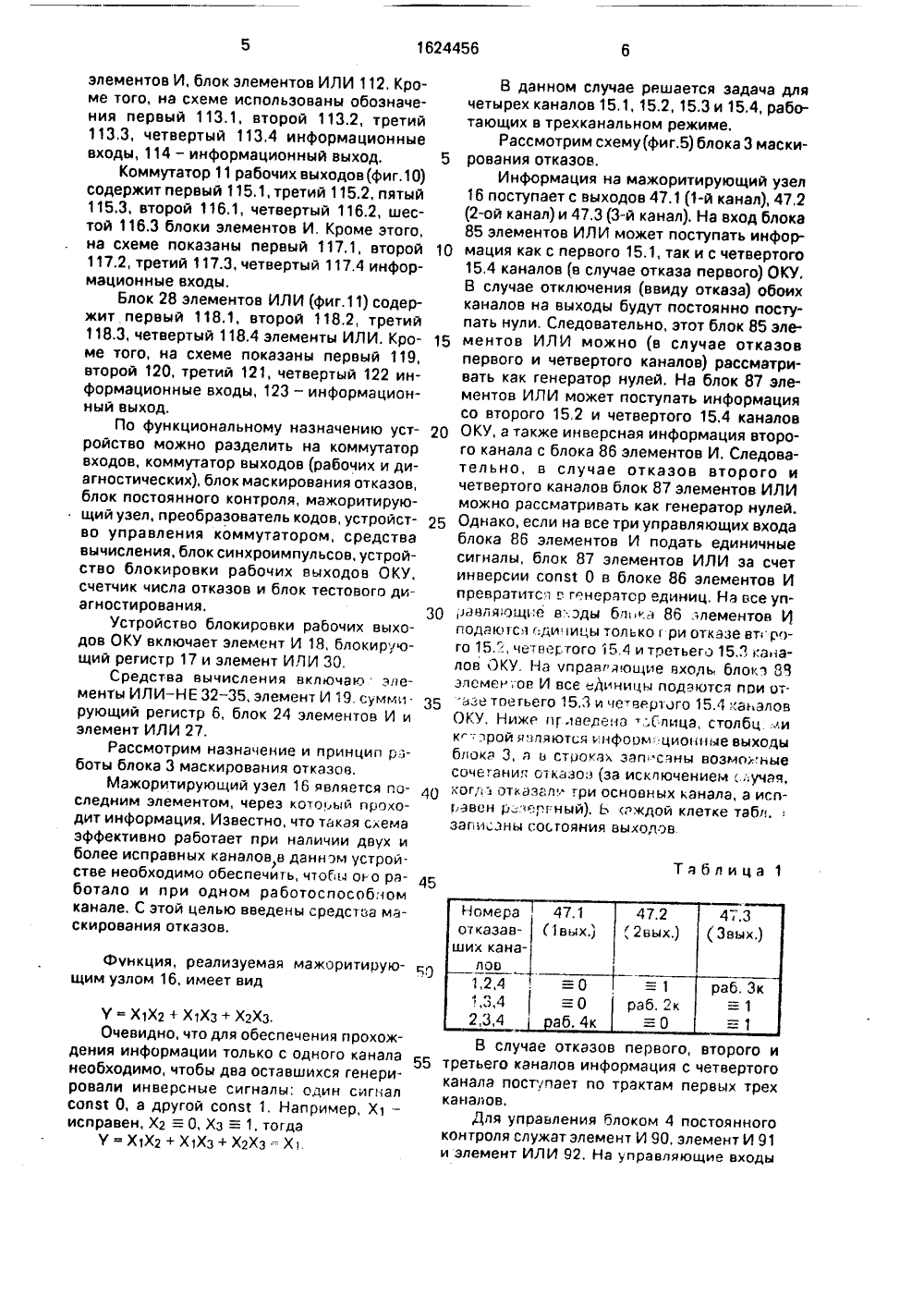

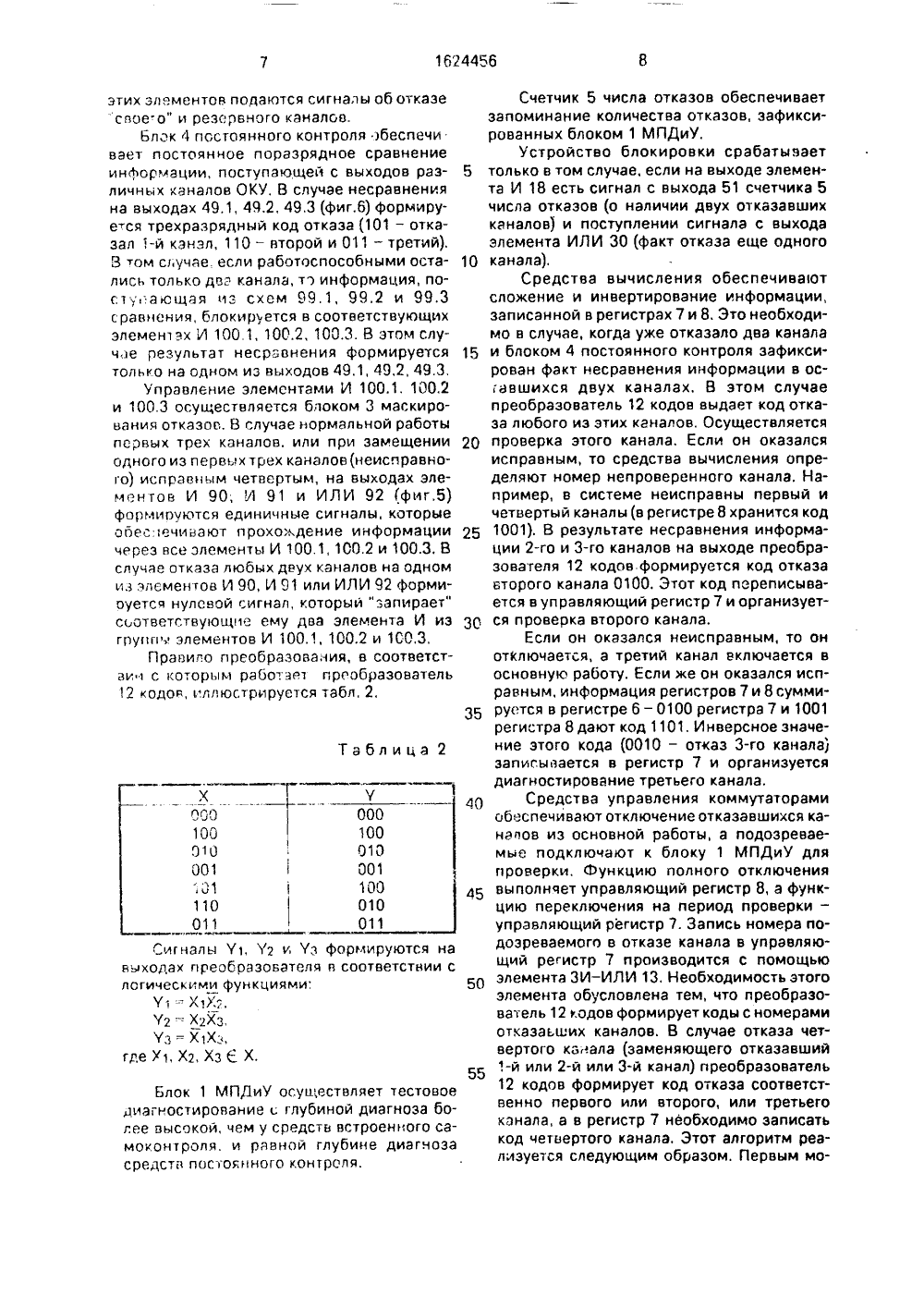

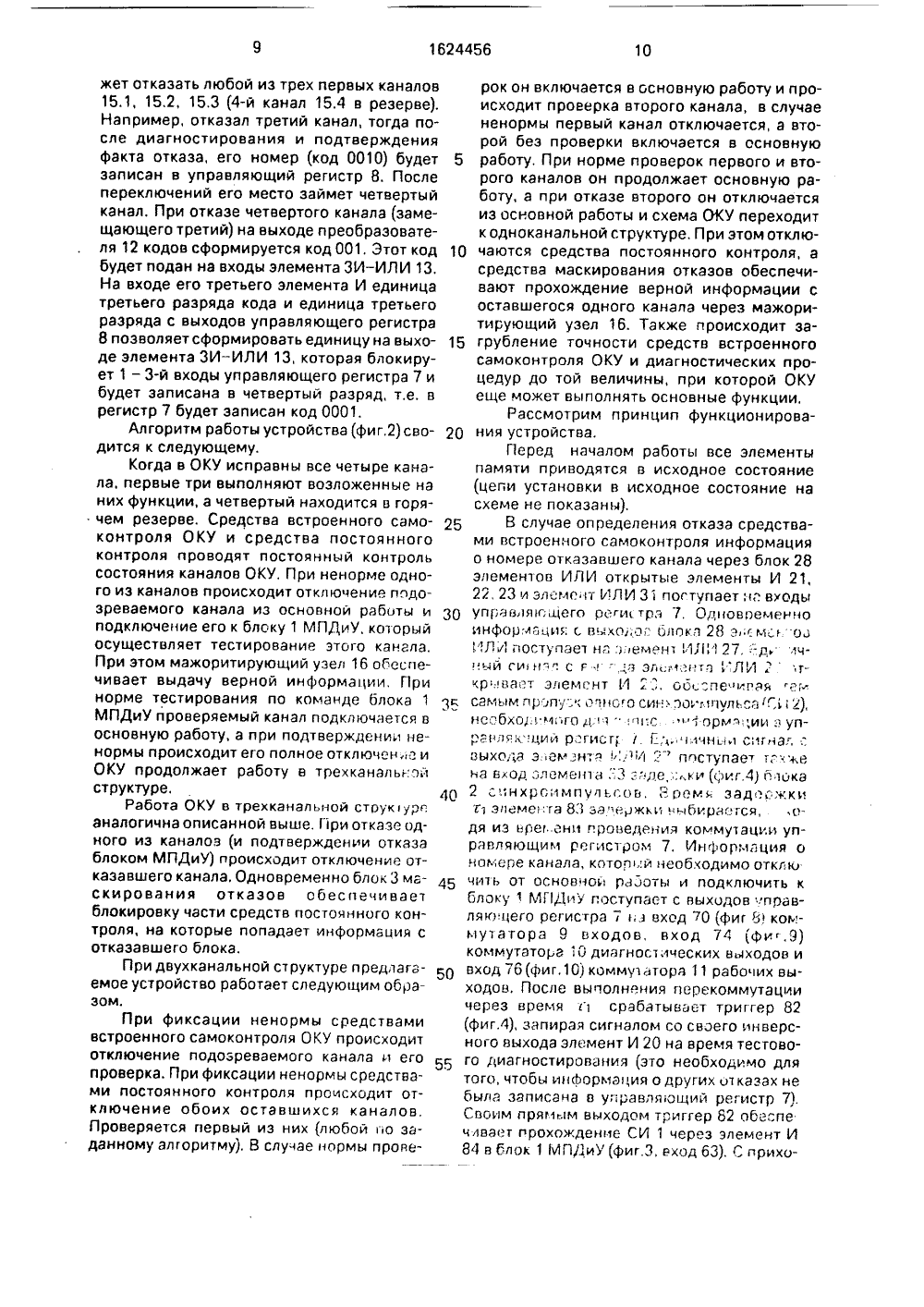

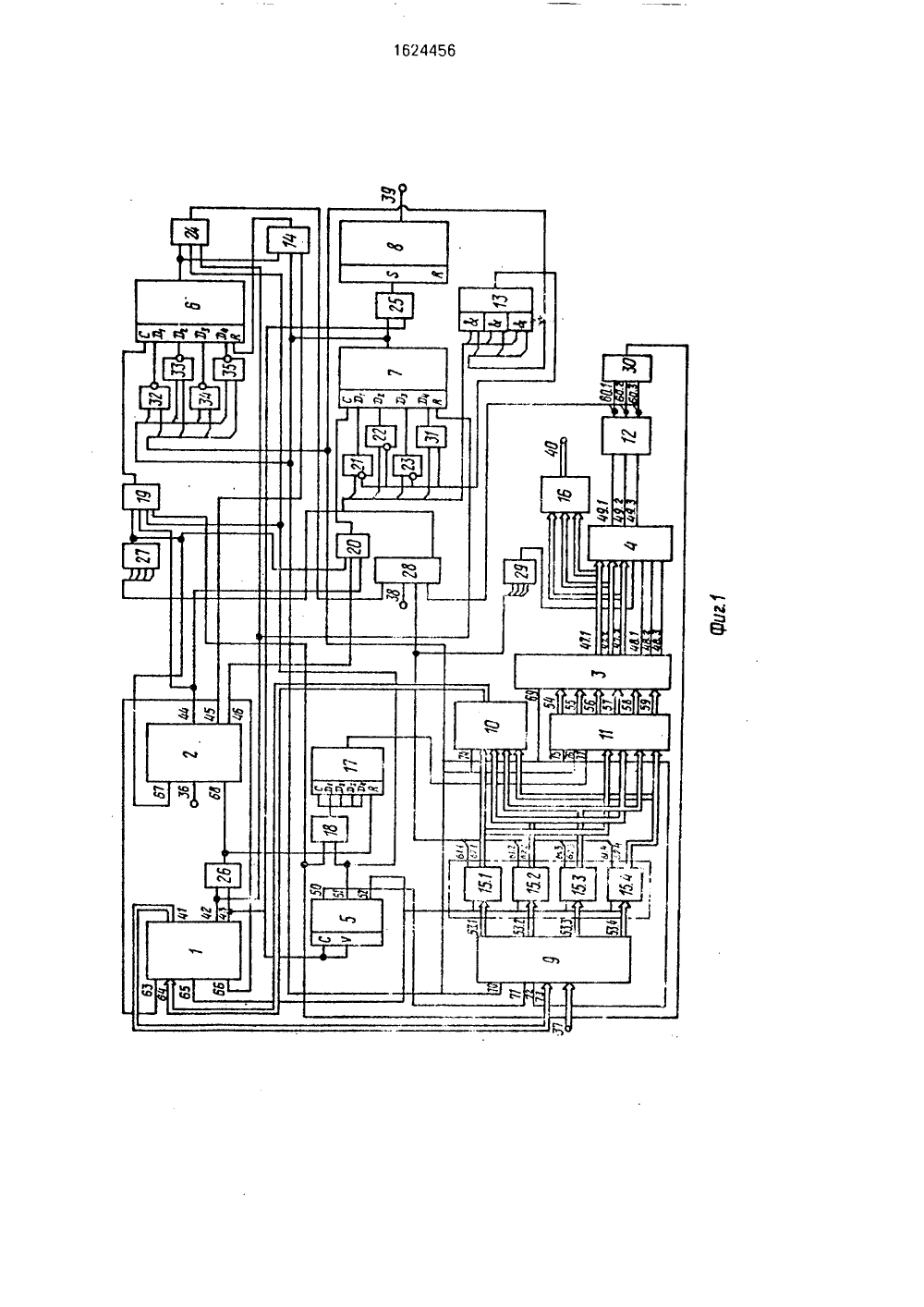

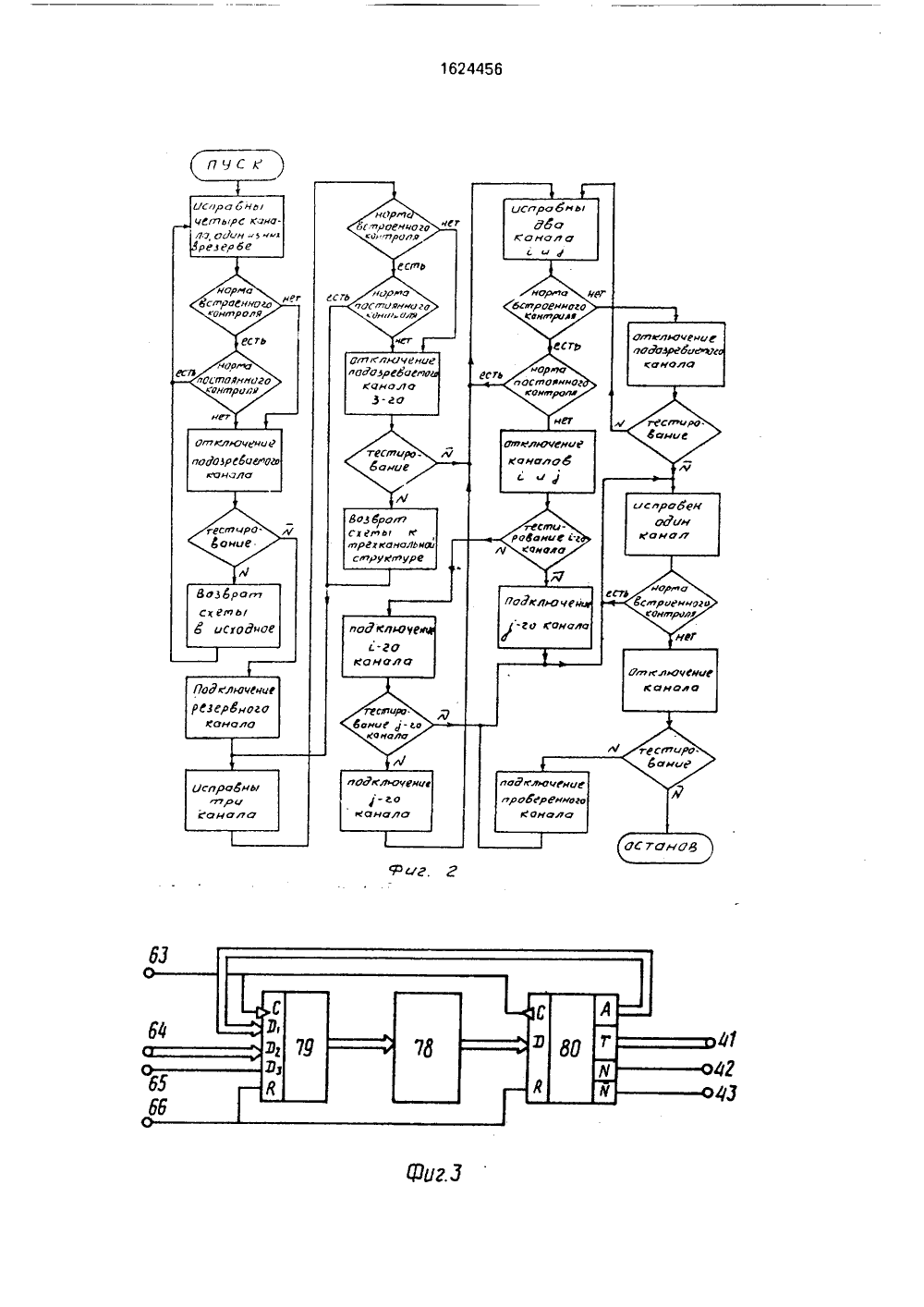

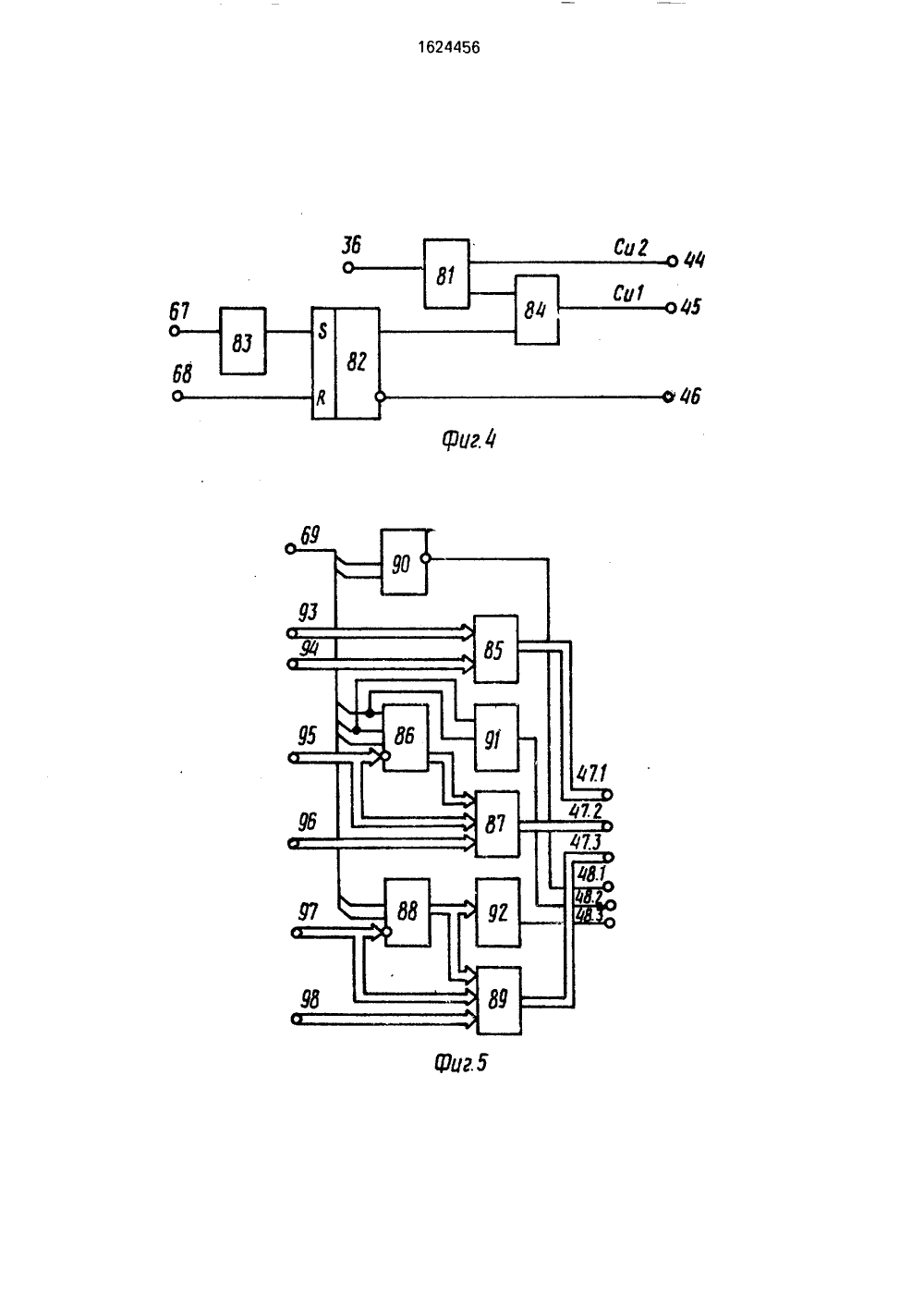

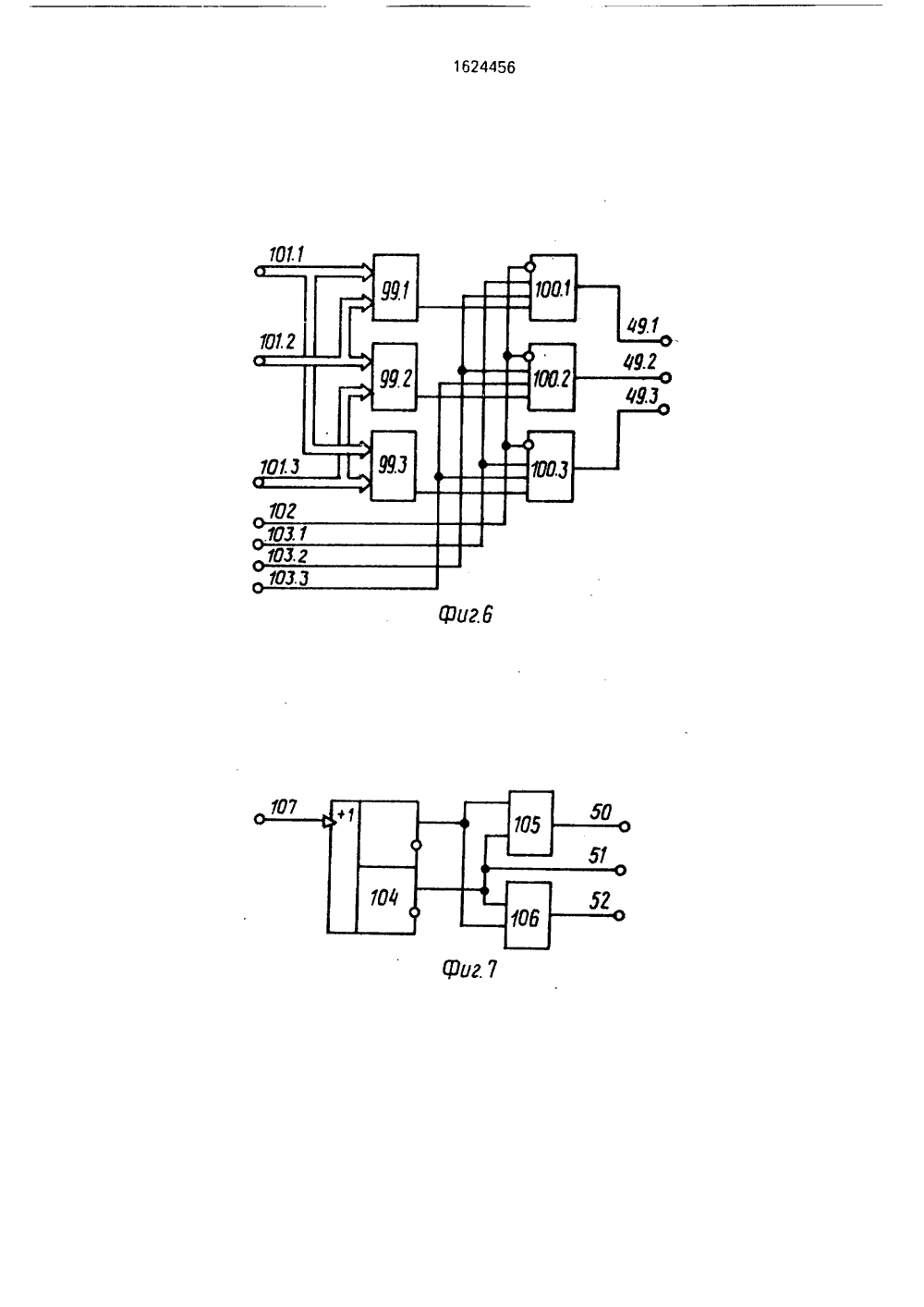

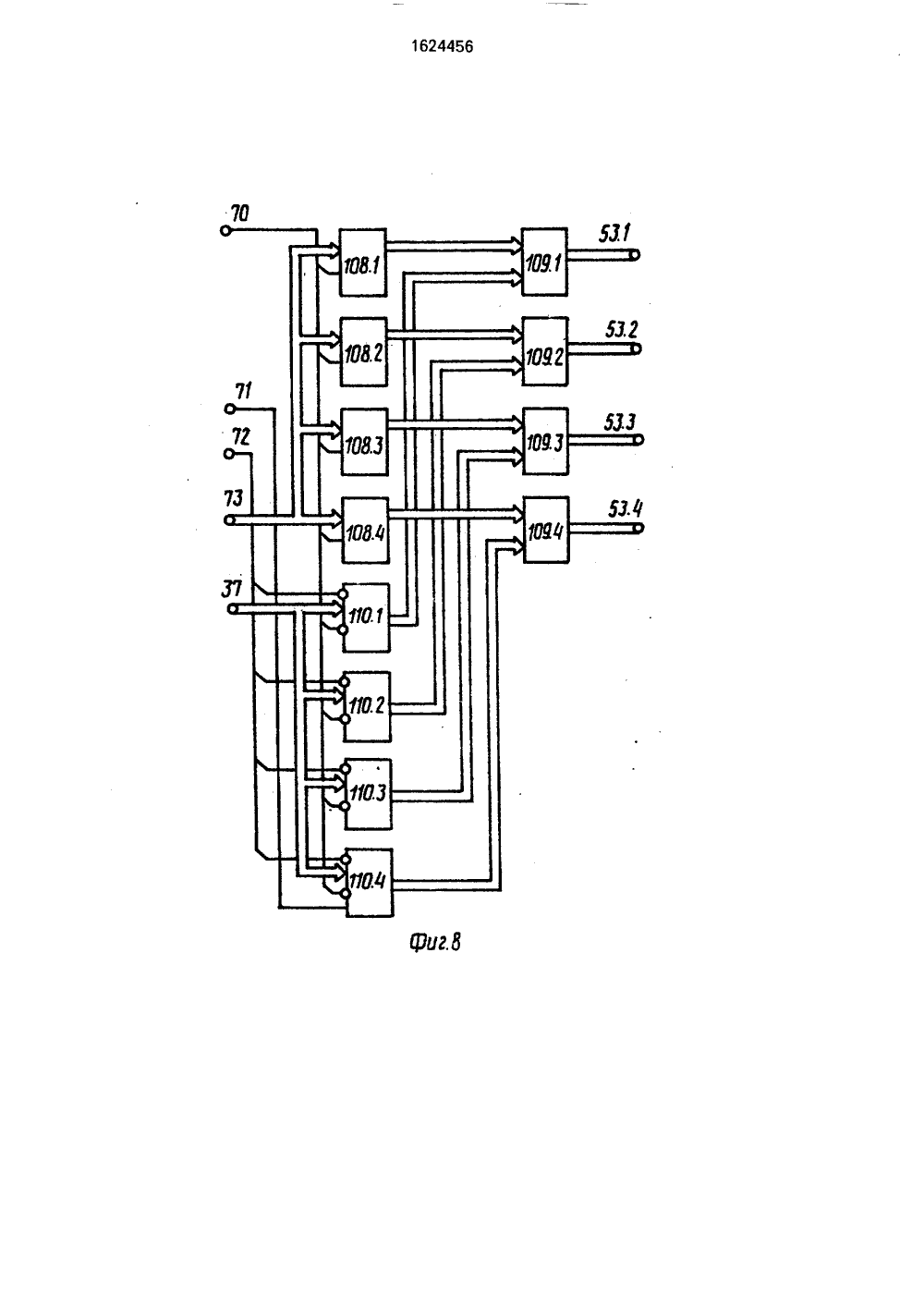

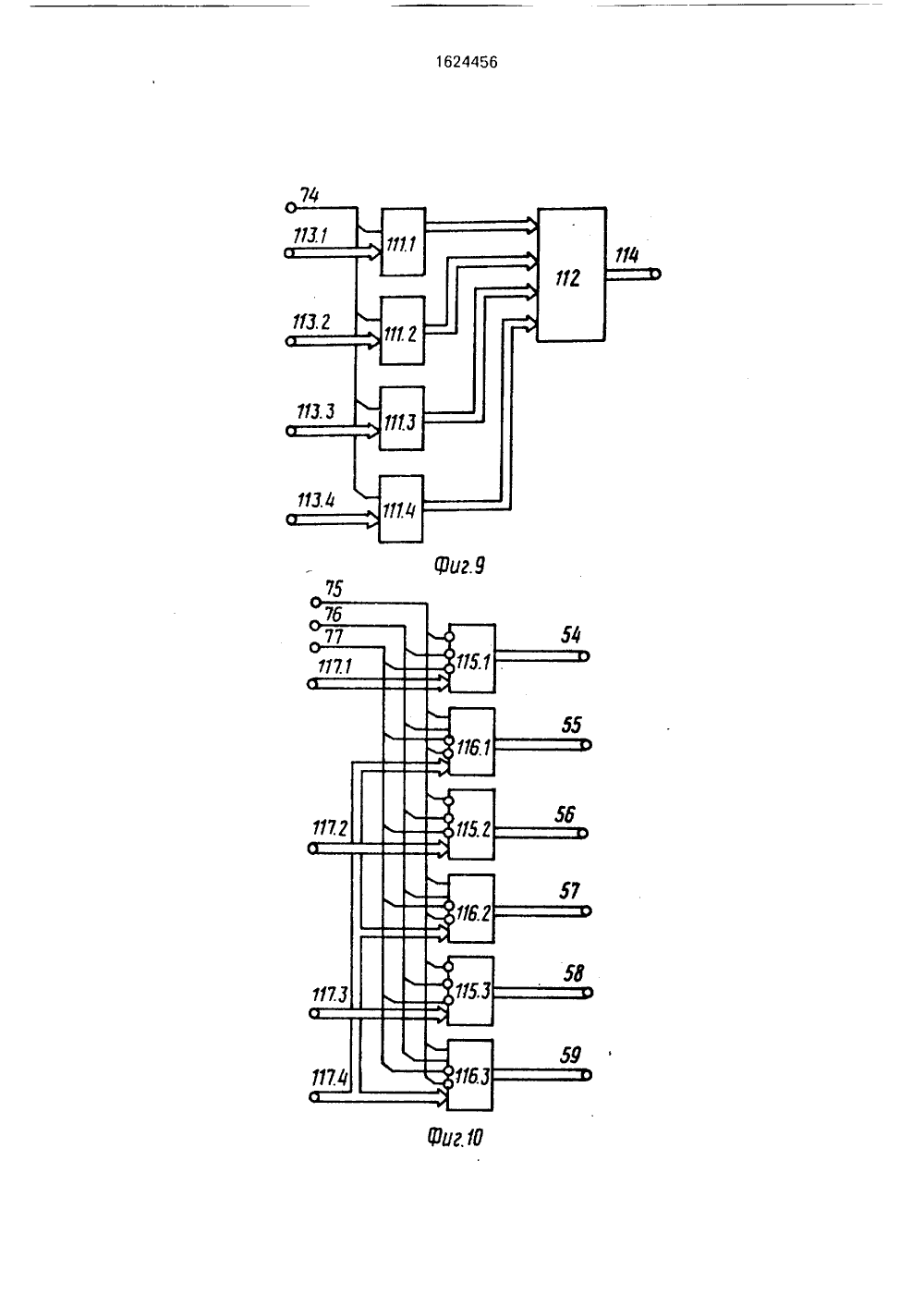

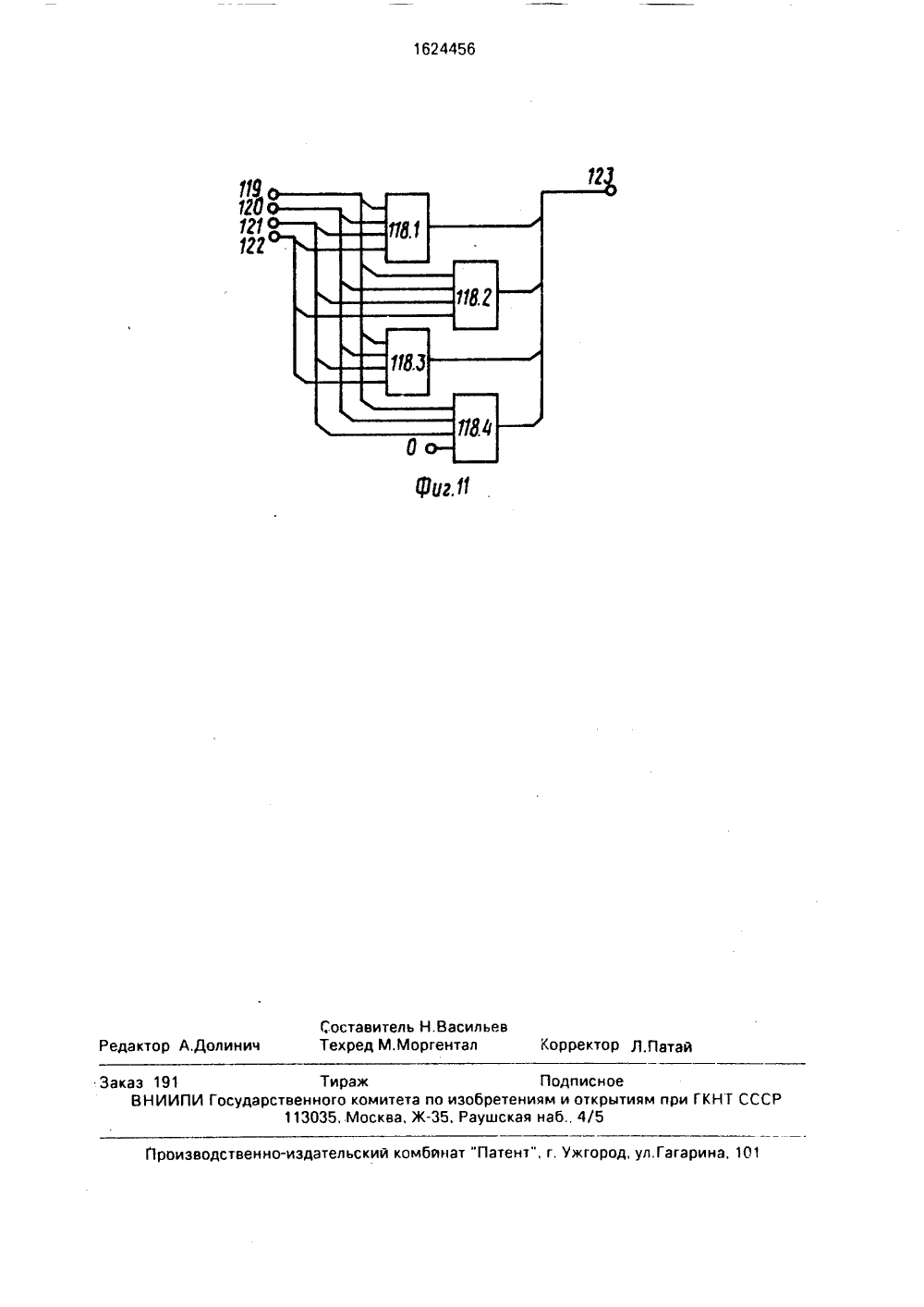

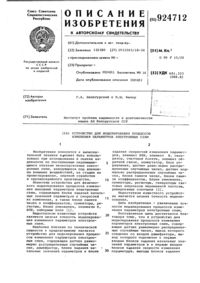

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1)5 0 06 Е 11/18 ГОСУДАРСТВЕННЫЙПО ИЗОБРЕТЕНИЯМПРИ ГКНТ СССР МИТЕТОТКРЫТИЯМ Е ИЗОБРЕ ПИСА ЕН(54) УС ГО УПР ЕМ И В СИСТЕ (57) Иэо и тех На фиг.1 пре ная схема устройс ма алгоритма рабо функциональная раммного диагнос (МПДиУ); на фиг,4 блока синхроимпу ональная схема бл зов; на фиг.б- фун пос-оянного контр нальная схема сче фиг.8 - функциона ычислительть использоуправления влением мастем, работаемени,АВТОРСКОМУ СВИДЕТЕЛЬСТ(56) Авторское свидетельство СССРМ 814108, кл, 6 06 Е 9/06,6 06 Е 11/00, 1979,Авторское свидетельство СССРМ 791044, кл. 0 06 Е 9/06, 1979.Авторское свидетельство СССРМ 849892, кл, 6 Об Е 15/00,6 06 Е 15/00, 1979.Авторское свидетельство СССРМ 972508, кл. 6 06 Е 9/22,6 06 Е 11/00, 1981,РОЙСТВО МИКРОПРОГРАММНОАВЛЕНИЯ ДИАГНОСТИРОВАНИОССТАНОВЛЕНИЕМ ЦИФРОВЫХ Мбретение относится к вычислитель- нике и АСУ и может быть использоИзобретение относится к ной технике и АСУ и может бь вано в качестве устройства диагностированием и восстан жоритарно-резервируемых си ющих в реальном масштабе вр Цель изобретения - повышение производительности путем обеспечения возможности параллельной реализации алгоритмов управления диагностирования и восстановления каналов. Я 2 1624456 А 1 вано для управления диагностированием ивосстановлением мажоритарно-резервируемых систем, работающих в реальном масштабе времени, Цель изобретенияповышение производительности путемобеспечения возможности параллельнойреализации алгоритмов управления, диагностирования и восстановления каналов.Устройство микропрограммного управления диагностированием и восстановлениемцифровых систем содержит блок микропрограммного диагностирования и управления, блок синхроимпульсов, шестьэлементов И, первый и второй блокг:.лементов И, счетчик числа отказов, коммутг горы входов и рабочих выход.,в, блок апостоянного контроля, преобразователь.кодов, первый и второй управляющие, сумми- друющий и блокирующий регистры и элеме тИЛИ, а также блок маскирования отказов,коммутатор диагностических выходов, эле- Ямент ЗИ - ИЛИ, блок сравнения, мажоритирующий узел, пять элементов ИЛИ, блокэлемснтов ИЛИ и четыре элемента ИЬИН Е. 11 ил 2 табл. дставлена функциональтва; на фиг.2 - блок-схеты устройства; на фиг.3 - хема блока микропрогтирования и управления - функциональная схемальсов; на фиг.5 - функциока маскирования откакциональная схема блока оля; на фиг.7 - функцио.тчика числа отказов; на ьная схема коммутаторалениоисФР сть нала тесл/иро- /ибание Воз боо/т/сггмь/и/рЕгконольисмуукрфуре1624456 119 180 121 128 Составитель Н.Васильевехред М,Моргентал Корректор Л.Патайолиничдакто аказ 191 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж. Раушская наб 4/5водственно-издательский комбанат "Патент", г, Ужгород, ул,Гагарина, 10входов; на фиг.9 - функциональная схема коммугатора диагностических выходов; на Фиг.10 - функциональная схема коммутатора рабочих выходов; на фиг1 - функциональная схема блока элементов ИЛИ,Устройство микропрограммного управлени диагностированием и восстановлением цифровых систем (фиг,1) содержит блок 1 МПДиУ, блок 2 си хооимпульсов, блок 3 маскирования отказов, блок 4 постоянного контроля, счетчик 5 числ; отказов, суммируюц, й регистр 6, первый управляющий регистр 7, второй управляющий регистр 8, коммутатор 9 входов, коммутатор 10 диагностических выходов, коммутатор 11 рабочих выходов, преобразователь 12 кодов, элемен ЗИ-ИЛИ 13, блок 14 сравнения, обьект контроля и управления (ОКУ), состоящий из четырех идентичных каналов 15.1, 15.2, 15,3 и 15,4, мэжоритирующий узел 16, блокирующий регистр 17, шестой элемент И 18, первый элемент И 19, второй элемент И 20, третий 21, четвертый 22, пятый 23 элементы И, первый 24, второй 25 блоки элементов 1, второй 26, третий 27 элементы ИЛ 4, блок 28 элементов ИЛИ, пятый злелент ИЛИ 29, четвертый 30, первый 31 элемен 1 ы ЕЛИ, первый 32, второй 33, третий 34, четвегтый 35 элементы ИЛИ-НЕ, Кроме того, на фиг.1 использованы следующие обозначения: 35 - первый управля ощий входустрэйсва, 37 - первый информационный вход ус;оойсгэ, 38 - второй информационный вход устройства, 39 - в 1 орой ин 4.; рмационный выход устройства, 40 - ервьй информационнь.й выход устройства, 41 - информдцио: ный выход блока 1 Ь" ПДиУ, 42 - первый управляющий выход блок;, 1 МПДиУ, 43 - второй управляющий выход блока 1 МПДиУ, 44, 45, 46 - соответственно первый, вгорой, третий управляюь ие в оды блока 2 с нхроимпульсов, 47,1, 47 2, 41,3 - сот ветственно первый, второй, трет 1 й инфсрма ио 1 ные выходы блока 3 маскирс ванля откэ зов, 48,1, 43,2, 48.3 - соответс 1 еенно первый второй, третий управляющие выходы блока 3 маскирования отказов 49,1, 49.2, 49.3 - соответственно первый, второй, третий выходы блока 4 постояннс го контсолц, 50, 51, 52 - соответстпервый, второй, третий выходы счетчика 5 числа отказов, 53,1, 53.2, 53,3, 53.4 - соответственно первь й, второй, тре 1 ий, чет 1 ерый информационные выходы коммутатора 9 входов, 54, 55, 56, 57, 58, 59 - соо;,",етственно первый вгорой, третий, четвертый, пятый, шестой информационные выходы коммутатора 11 рабочих выходов, 60 1, 60.2, 60,3 - соответственно первый, в орэй,третий гьходы преобразователя 12 10 15 20 25 30 35 40 45 50 55 кодов, 61,1, 61,2, 61.3, 61.4 - соответственно первый, второй, третий, четвертый управляющие выходы ОКУ 62.1, 62,2, 62.3, 62.4 - соответственно первый, второй, третий, четвертый информационные выходы ОКУ, 63 - первый управляющий вход блока 1 МПДиУ, 64 - информационный вход блока 1 МПДиУ, 65, 66 - соответственно третий и второй управляющие входы блока 1 МПДиу, 67, 68 -соответственно третий и второй управляющие входы блока 2 синхроимпульсов, 69 - управляющий вход блока 3 маскирования отказов, 70, 71, 72 - соответственно первый, второй, третий управляющие входы коммутатора 9 входов, 73 - второй информационный вход коммутатора 9 входов, 74 - управляющий вход коммутатора 10 диагностических выходов, 15, 76, 17 - соответственно третий, второй, первый управляющие входы коммутатора 11 рабочих выходов.Блок 1 МПДиУ фиг.З) содержит блок 78 памяти, регистр 79 адреса и регистр 80 тестов,Блок 2 синхроимпульсов (фиг,4) содержит генератор 81 синхроимпульсов, триггер 82 управления, элемент 83 задержки, элемент И 84.Блок 3 маскирования отказов (фиг,5) содержит первый блок 85 элементов ИЛИ, первый блок 86 элементов И, второй блок 81 элементов ИЛИ, второй блок 88 элементов И, третий блок 89 элементов ИЛИ, первый 90, второй 91 элементы И и элемент ИЛИ 92. Кроме того, на схеме использованы обозначения: 93, 94, 95, 96, 97 и 98 - первый, второй, третий, четвертый, пятый, шестой информационные входы соответственно.Блок 4 постоянного контроля (фиг.6) содержит первую 99.1, вторую 99,2, третью 99.3 схемы сравнения, первый 100.1, второй 100.2, третий 100,3 элементы И. Кроме того, на схеме использованы обозначения: первый 101.1, второй 101.2, третий 101,3 информационные входы, четвертый 102, первый 103.1, второй 103,2, третий 103,3 управляющие входы.Счетчик 5 числа отказов (фиг.7) содержит счетчика 104, элемент ИЛИ 105 и элемент И 106, Кроме того, на схеме показан информационный вход 107.Коммутатор 9 входов (фиг.8) содержит: первый 108,1, второй 108.2, третий 108.3, четвертый 108.4 блоки элементов И, первый 109,1, второй 109.2, третий 109,3, четвертый 09,4 блоки элементов ИЛИ, пятый 110.1, шестой 110,2, седьмой 110,3, восьмой 110,4 блоки элементов И.Коммутатор 10 диагностических выходов (фиг.9) содержит первый 111,1, второй 111.2, третий 111,3, четвертый 111,4 блоки1624456 Таблица 1 руюхожнала еригнал Х 1 -В случае о третьего канал канала поступа каналов.Для управл контроля служа и элемент ИЛИ первого, второго и рмация с четвертого рактам первых трех каз т по ения б оком 4 постоянногонт И 90, элемент И 91 управляющие входы т элем92. Н элементов И, блок элементов ИЛИ 112, Кроме того, на схеме использованы обозначения первый 113.1, второй 113.2, третий 113,3, четвертый 113,4 информационные входы, 114 - информационный выход.Коммутатор 11 рабочих выходов(фиг.10) содержит первый 115.1, третий 115.2, пятый 115.3, второй 116.1, четвертый 116.2, шестой 116.3 блоки элементов И, Кроме этого, на схеме показаны первый 117.1, второй 117.2, третий 117.3, четвертый 117.4 информационные входы.Блок 28 элементов ИЛИ (фиг.11) содержит первый 118.1, второй 118.2, третий 118.3, четвертый 118.4 элементы ИЛИ. Кроме того, на схеме показаны первый 119, второй 120, третий 121, четвертый 122 информационные входы, 123 - информационный выход.По функциональному назначению устройство можно разделить на коммутатор входов, коммутатор выходов (рабочих и диагностических), блок маскирования отказов, блок постоянного контроля, мажоритирующий узел, преобразователь кодов, устройство управления коммутатором, средства вычисления, блок синхроимпульсов, устройство блокировки рабочих выходов ОКУ, счетчик числа отказов и блок тестового диагностирования.Устройство блокировки рабочих выходов ОКУ включает элемент И 18, блокиру ощий регистр 17 и элемент ИЛИ 30,Средства вычисления включаю элементы ИЛИ-НЕ 32 - 35, элемент И 19, сумми. рующий регистр 6, блок 24 элементов И и элемент ИЛИ 27.Рассмотрим назначение и принцип работы блока 3 маскирования отказов.Мажоритирующий узел 16 является последним элементом, через кото 1 ый проходит информация, Известно, что такая схема эффективно работает при наличии двух и более исправных каналов в данн эм устрой.)стае необходимо обеспечить, чтоГ,ы оо работало и при одном работоспособном канале. С этой целью введены средства маскирования отказов. фчнкция, реализуемая мам узлом 16, имеет вид У = Х 1 Х 2 + Х 1 Хз + Х 2 Хз,Очевидно, что для обеспечения прдения информации только с одного канеобходимо, чтобы два оставшихся геровали инверсные сигналы: один ссопзт О, а другой сопи 1, Например,исправен, Х 2 = О, Хз - = 1, тогдаУ = Х 1 Х 2 + Х 1 Хз + Х 2 Хз . - Х к 5 10 15 20 25 30 35 40 В данном случае решается задача для четырех каналов 15.1, 15.2, 15.3 и 15.4, работающих в трехканальном режиме.Рассмотрим схему(фиг.5) блока 3 маскирования отказов.Информация на мажоритирующий узел 16 поступает с выходов 47,1(1-й канал), 47,2 (2-ой канал) и 47.3 (3-й канал). На вход блока 85 элементов ИЛИ может поступать информация как с первого 15.1, так и с четвертого 15,4 каналов (в случае отказа первого) ОКУ. В случае отключения (ввиду отказа) обоих каналов на выходы будут постоянно поступать нули. Следовательно, этот блок 85 элементов ИЛИ можно (в случае отказов первого и четвертого каналов) рассматривать как генератор нулей. На блок 87 элементов ИЛИ может поступать информация со второго 15,2 и четвертого 15.4 каналов ОКУ, а также инверсная информация второго канала с блока 86 элементов И. Следовательно, в случае отказов второго и четвертого каналов блок 87 элементов ИЛИ можно рассматривать как генератор нулей. Однако, если на все три управляющих входа блока 86 элементов И подать единичные сигналы, блок 87 элементов ИЛИ за счет инверсии сопз 1 0 в блоке 86 элементов И превратитс 1 в генератор единиц, На все уп;авляющие в.эды бъ к;. 86,лементовподаются г,.ди ицы толькори отказе вт рого 15., четвертого 15,4 и третьего 15.3 каналов ОКУ, На чпраят лющие вхолы блока 88 элеме:ое И все единицы подаются пои от:аве тоетьего 15,3 и четвертого 15.4 каналов ОКУ, Ниже п,веденз ;Слица, столбц,фи к -эрой являются информ .циокные выходы блока 3, а в строках зап саны возможные сочетания отказо (за исключением с;,учая, кот,м отказал. три основных канала, а испмвен р= 1 ергный), Ь сждой клетке табл. заки зны состояния выходов,01110 011 этих элементов подаются сигналы об отказе слоео" и резервного каналов.Блок 4 постоянного контроля )беспечи вает постоянное поразрядное сравнение информации, поступающей с выходов различных каналов ОКУ, В случае несравнения на выходах 49.1, 49.2, 49,3 (фиг.б) формируе ся трехраэрядный код отказа (101 - отказал 1-й канал, 110 - второй и 011 - третий). В том случае. если работоспособными остались только два канала, тэ информация, пос 1;.а сщая из схем 99,1, 99,2 и 99,3 с равнения, блокируется в соответствующих элемен 1 эх И 100 1, 100.2, 100.3. В этом случ.е результат несравнения формируется только на одном из выходов 49,1, 49,2, 49.3,Управление элементами И 100.1. 100,2 и 100.3 осуществляется блоком 3 маскирования отказов. В случае нормальной работы псрвых трех каналов, или при замещении одного из первых трех каналов(неисправного) исправным четвертым, на выходах элементов И 90, И 91 и ИЛИ 92 (фиг.5) формиоуются единичные сигналы, которые ооес ечивают прохождение информации через все элементы И 100.1, 100,2 и 100.3. В случае отказа любых двух каналов на одном иэ элементов И 90, И 91 или ИЛИ 92 формиоуется нулевой сигнал, которыи "запирает" соответствующие ему два элемента И иэ групп, элементов И 100,1, 100,2 и 100,3,Правило преобразования, в соответстаи 1 с которым работэе 1 прг образователь 2 кодо, иллюстрируется табл, 2,сигналы У 1 У 2 и Уз формируются на выходах преобразователя в соответствии с логическими функциями; У .= Х 1 Й,Уг = ХХз,Уз =- Х 1 Хз,где Х 1, Х 2, Хз б Х.Блок 1 МПДиУ осуществляет тестовое диагностирование с глубиной диагноза более высокой, чем у средств встроенного самоконтроля, и равной глубине диагчоза средств постоянного контроля. 10 15 20 25 30 35 40 45 50 55 Счетчик 5 числа отказов обеспечивает запоминание количества отказов, зафиксированных блоком 1 МПДиУ,Устройство блокировки срабатывает только в том случае, если на выходе элемента И 18 есть сигнал с выхода 51 счетчика 5 числа отказов (о наличии двух отказавших каналов) и поступлении сигнала с выхода элемента ИЛИ 30 (факт отказа еще одного канала),Средства вычисления обеспечивают сложение и инвертирование информации, записанной в регистрах 7 и 8. Это необходимо в случае, когда уже отказало два канала и блоком 4 постоянного контроля зафиксирован факт несравнения информации в ос.авшихся двух каналах. В этом случае преобразователь 12 кодов выдает код отказа любого иэ этих каналов, Осуществляется проверка этого канала. Если он оказался исправным, то средства вычисления определяют номер непроверенного канала. Например, в системе неисправны первый и четвертый каналы (в регистре 8 хранится код 1001), В результате несравнения информации 2-го и 3-го каналов на выходе преобразователя 12 кодов формируется код отказа ьторого канала 0100, Этот код переписывается в управляющий регистр 7 и организуется проверка второго канала.Если он оказался неисправным, то он отключается, а третий канал включается в основную работу, Если же он оказался исправным, информация регистров 7 и 8 суммируется в регистре б - 0100 регистра 7 и 1001 регистра 8 дают код 1101. Инверсное значение этого кода (0010 - отказ 3-го канала) записывается в регистр 7 и организуется диагностирование третьего канала,Средства управления коммутаторами обеспечивают отключение отказавшихся каналов из основной работы, а подозреваемые подключают к блоку 1 МПДиУ для проверки, Функцию полного отключения выполняет управляющий регистр 8, а функцию переключения на период проверки - управляющий регистр 7. Запись номера подозреваемого в отказе канала в управляющий регистр 7 производится с помощью элемента ЗИ - ИЛИ 13, Необходимость этого элемента обусловлена тем, что преобразователь 12 кодов формирует коды с номерами отказаьших каналов. В случае отказа четвертого ка дала (заменяющего отказавший ,-й или 2-й или 3-й канал) преобразователь 12 кодов формирует код отказа соответственно первого или второго, или третьего канала, а в регистр 7 необходимо записать код четвертого канала. Этот алгоритм реализуется следующим образом. Первым мо 1624456 10жет отказать любой из трех первых каналов 15.1, 15.2, 15,3 (4-й канал 15,4 в резерве).Например, отказал третий канал, тогда после диагностирования и подтверждения факта отказа, его номер (код 0010) будет записан в управляющий регистр 8. После переключений его место займет четвертый канал. При отказе четвертого канала (замещающего третий) на выходе преобразователя 12 кодов сформируется код 001. Этот код будет подан на входы элемента ЗИ - ИЛИ 13.На входе его третьего элемента И единица третьего разряда кода и единица третьего разряда с выходов управляющего регистра 8 позволяет сформировать единицу на выходе элемента ЗИ - ИЛИ 13, которая блокирует 1 - 3-й входы управляющего регистра 7 и будет записана в четвертый разряд, т.е. в регистр 7 будет записан код 0001.Алгоритм работы устройства (фиг,2) сводится к следующему.Когда в ОКУ исправны все четыре канала, первые три выполняют возложенные на них функции, а четвертый находится в горячем резерве. Средства встроенного самоконтроля ОКУ и средства постоянного контроля проводят постоянный контроль состояния каналов ОКУ. При ненорме одного из каналов происходит отключение падозреваемого канала из основной работы и подключение его к блоку 1 МПДиУ, который осуществляет тестирование этого канала, При этом мажоритирующий узел 16 ОГеспечивает выдачу верной информации, Гри норме тестирования по команде блока 1 МПДиУ проверяемый канал подключается в основную работу, а при подтверждении не- нормы происходит его полное отключен, е и ОКУ продолжает работу в трехканальной структуре.Работа ОКУ в трехканальной стаукуре аналогична описанной выше. Г 1 ри отказе Одного иэ каналов (и подтверждении отказа блоком МПДиУ) происходит отключение отказавшего канала, Одновременно блок 3 маскирования отказов обеспечивает блокировку части средств постоянного контроля, на которые попадает информация с отказавшего блока.При двухканальной структуре предлагаемое устройство работает следующим Образам.При фиксации ненармы средствами встроенного самоконтроля ОКУ происходит отключение подозреваемого канала и ега проверка. При фиксации ненармы средствами постоянного контроля происходит отключение обоих оставшихся каналов. Проверяется первый из них (любой ла заданному алгоритму). В случае нормы проверок он включается в основную работу и происходит проверка второго канала, в случае ненормы первый канал отключается, а второй беэ проверки включается в Основную 5 работу, При норме проверок первого и второго каналов он продолжает основную работу, а при отказе второго он отключается из Основной работы и схема ОКУ переходит к одноканальной структуре. При этом отклю чаются средства постоянного контроля, асредства маскирования отказов обеспечивают прохождение верной информации с оставшегося одного канала через мажоритирующий узел 16. Также происходит за грубление точности средств встроенногосамоконтроля ОКУ и диагностических процедур до тай величины, при которой ОКУ еще может выполнять основные функции.Рассмотрим принцип функционирава ния устройства.Перед началом работы все элементыпамяти приводятся в исходное состояние (цепи установки в исходное состояние на схеме не показаны).В случае определения отказа средствами встраеннога самоконтроля информация а номере отказавшего канала через блок 28 элементов ИЛИ открытые элементы И 21, 22, 23 и элема гг ИЛИ 31 поступает ,е входы 30 упрэвляю 4 ега регитра 7, Одновременнаинфар;дэция с выха,ас блока 28 эмац ИЛИ поступает нл :емент ИЛ 11 27, .-.Д.,чньй Ги н ", с г, э элс;1 л 1 гэ ИЛИ 2 Г- крьваат элемент И ";Оа."пеиггя к самым арапу анага син аа;пульса С ),нсабха. мага д.: ":т;с. " армции э упргвляь.;ции р;.гист;. г. Е; ь,1 чн и сигнал,;, выха,;а э. емгнтэ "И 2 поступает г;,+,е на в,кад лемен 1 э, 3:.;.де,.:ки (стиг.4) п 1 ака 40 2 сцнхраимпул ьсав, 2 ром ь здДаажкит эльме:тэ 83 зае,ежли цибирэагся, .адя из ьреь ени проведения коммутации управляющим регистрам 7. Информация о намере канала, катарь.й необходимо отклю 45 чи 1 ь От Основной рл аты и подключить кблоку 1 МПДиУ поступает с выходов;правляю;цега регистра 7 нэ вход 70 (фиг В, ком - мутатора 9 входов, вход 74 (Фи .Э) каммутата 1,г 10 Диагностических выходов и вход 76(фиг,10) камму 1 этара 11 рабочих выходов, После выполнения г 1 ерекоммутации через время 1 с рабаты ва ет три ггер 82 (фиг.4), запирая сигналом са сваего инверсного выхода элемент И 20 на время тестовога диагностирования (это необходимо для того, чтобы информация о других О 1 казах не была записана в уграеляащий регистр 7), Своим прямым выходам триггер 82 абеспе чивэ.т прохождение СИ 1 через элемент И 84 в блок 1 МПДиу (фиг.З, вход 63). С лрихо 1624456 12дом первого синхроимпульса начинается и р. цес тестового диагностирования, окончанлкоторого определяется наличием единицы в поле М или Й регистра 80 тестов (фи.З), что соответствует норме или ненорме диагностирования,Рассмотрим случай нормы проверок. Сигнал нормы поступает на Я-вход регистра 7 и приводит его в исходное состояние. В реэ льтате в исходное состояние приходят и ясе коммутаторы, возвращая тем самым ОкУ в исходное состояние (с точки зрения структуры ОКУ). Кроме описанного, сигнал нормы поступает на К-вход триггера 82, привод его в исходное состояние, В результате закрывается элемент И 84 (прекращается пропуск ГИ 1) и открывается элемент И 20, подготавливая тем самым тракт к записи информации о п,едующем отказе.При появлении в одном из каналов информации, отличной от информации других двух каналов, нэ выходах тех схем сравнения, куда эта (неверная) информация поступает, формируются единичные сигналы. Так, в случае искажения информации во втором канале единицы сформируются на выходах схем 99,1 и 99.2 сравнения (фиг,6), т.е, сформируется код 110. Эта информация через открыт, е элементы И 100,1, 100.2 поступит нэ всход преобразователя 12 кодов, где будет пре бра.ована в код 010, Этот код нера:., тек 2 С элемен гов ИЛИ поступает на цхсд злементэ ИЛИ 2", Далее происходит .ереоммутация, включение блока,ПДи и тестирование второго канала, Расслотриь, на примервторого канала), как ,.о;,вводится подключение канала на тести;ование. Запис-ный в управляющем с:. гистре 7 код 0109 поступает через управгя .чц.влод 70 (фи,В) в коммутатор 9 входоэ Б резал та.е .нкрывается блок 108,2 эзементо И и: акгывэется блок 110,2 элемгнгод И, Этот же код поступает на коммутатор 10 диагност.веских выходов (фиг.9) через вход 74 и открывает блок 111,2 элемен-,ое И. Аналогицным образом в коммутаторе 11 рабочих выходов (фиг.10) закрывается блок 115 2 элементов И,После перекоммугэции проходит про- ;есс диагностирования, Пусть в результате диагностирования выяснится факт отказа ьорого канала. Тогда в поле Й регистра 80 тестов (фиг.З) появится единица, которая через элемен ИЛИ 26 поступит на К-вход триггера 82 и приведет его в исходное состояние. В результате прекратится процесс диагностлрования и подготовится к работе элмен И 20. Единица с поля Й регистра 80 тестов будет подана также на управляющий вход блока 25 элементов И и на в; од счетчикэ 04 (Фиг,. единица с выхода 50 счегчикв -45 кодов единицы на выходах элемента ЗИ-ИЛИ 13 будет сформирована единица, которая закроет элементы И 21, И 22 и И 23, ачерез элемент ИЛИ 31 будет подана нэ вход 04, управляющего регистра 7 и записана внего с приходом синхроимпульса СИ 2 с выхода 44 блока 2 синхроимпульсов через элемент И 20. Таким образом, в управляющий регис" р 7 будет записан код 0001, что соответств ет отказу четвертого канала15.4. После этого по описанному алгоритму происходит отключение четвертого канала и его тестирование, В случае нормы тестирования происходит обнуление регистра 7 и схема ОКУ приводится к исходной, трехканальной структуре, При фиксации блоком 1 5 1030 3540 5 числа отказов через управляющий вход 71 (фиг.8) коммутатора 9 входов поступит навход блока 110.4 элементов И и подключит входы четвертого канала 15,4 ОКУ. Одновременно единица, поступившая на управляющий вход блока 25 элементов И, обеспечит запись информации (код 0100) с выходов управляющего регистра 7 в управляющий регистр 8, Код, записанный в управляющий регистр 8, поступит на управляющий вход 72 (фиг.8) коммутатора 9 входов, управляющийвход 75 (фиг.10) коммутатора 11 рабочих выходов и на управляющий вход 69 (фиг,5) блока 3 маскирования отказов, В результате в коммутаторе 9 входов будет закрыт блок 110.2 элементов И (отключение входов второго канала 15.2) в коммутаторе 11 рабочих выходов будет закрыт блок 115.2 элементов И (отключение выходов второго канала 15.2) и открыт блок 116,2 элементов И (подключение выходов четвертого канала 15.4); в блоке 3 маскирования отказов подготавливается к работе блок 86 элементов И (фиг,5),Таким образом, выявленный отказ второго канала привел к его отключению и замене четвертым каналом,Работа устройства при наличии трех исправных каналов ОКУ аналогична описанной. Отличие имеется лишь при фиксации факта отказа и в том случае, когда отказ четвертого канала фиксируется средствами постоянного контроля. Рассмотрим этот случай. При искажении информации в четвертом канале 15.4 (замещающем второй) средства постоянного контроля блока 4 выдадут в преобразователь 12 код 110, который будет преобразован к виду 010. Этот код через блок 28 элементов ИЛИ поступит на входы элементов ИЛИ 27, И 21, И 22, И 23, ИЛИ 31 и ЗИ-ИЛИ 13. Кроме того, на других входах элемента ЗИ-ИЛИ 13 находится информация с первых трех разрядовуправляющего регистра 8 - код 010. В результате наличия во вторых разрядах обоихМПДиУ факта отказа происходит запись информации из регистра 7 в регистр 8 и запись еще одной единицы в счетчик 5 числа отказов. Появление единицы на втором выходе счетчика 5 числа отказов обеспечивает подготовку к работе элемента И 19, элемента И 18 и блока 24 элементов И. Информация с выхода управляющего регистра 8 поступает на коммутаторы 9 и 11 входов и рабочих выходов, где производится отключение отказавшего (в рассматриваемом г римере четвертого) канала, а также в блок 3 маскирования отказов, где происходит операция по маскированию отказов. В рассматриваемом примере на выходе элемента И 91 (фиг.5) формируется единица, которая поступает на инверсные входы элементов И 100.1 и 100.2 (фиг.б) и закрывает их, тем самым из блока 4 постоянного контроля через открытый элемент И 100.3 будет проходить информация о результатах сравнения первого и третьего каналов,Работа устройства с двумя исправными каналами, При несравнении информации з блоке 4 постоянного контроля преобразователь 12 кодов формирует на своих выходах код отказа одного из них, В результате на выходе элемента ИЛИ 30 формируется единица, которая через открытый элемент И 18 записывается в блокируюс;ий регистр 17.Информация с выходов блок,1 рующсго регистра 17 поступает на коммутатор 11 рабочх выходов и отключает выходы всех каналов, Одновременно код с выхода пг еобраэояателя 12 кодов (в рассматриваемом пр. мера 001) через блок 28 элементг. а ИЛИ ао синхроимпульсу СИ 2 записываьтся в упр;щий регистр 7, Кроме ТО: о, по синхроимпульсу СИ 2 происход т запись информации иэ управля ощих регистров 7 и 8 через элементы ИЛИ-НЕсуммируют регистр 6 (в рассматриваемом примере ь регистр б записываются коды 0100- и 100") Таким образом, в суммирующий регистр 6 записывается код второго из подозреваемых в отказе каналов (в рассма ривае 1 ом примере 0010). Через вра ля г 1 по:ле перекоммутации) происходит процесс тестового диагностирования, При любом исходе диагностирования происходиОбнуление блокирующего регистра 17.При ненорме проверок единич ый сигнал й с выхода регистра 80 тестов обеспечивает перезапись информации из регистр 7 в регистр 8 (открывает блок 25 элементов И) и устройство переходит в одноканальный режим работы Кроме того, синал М привсдит в иСходное состояние блок 2 синхроимпульсов, а также увеличивает на единицу содержимое счегчика 5 числа отказав,Сформированная таким образом единицана третьем выхсде счетчика 5 числа отказовпроизводит отключение блока 4 постоянного контроля (вход 102, фиг.б) и переводит5 блок 1 МПДиУ в режим работы по загрубленному алгоритму, т.е, производит изменениеначального адреса программы диагностирования, Выбранная таким образом новаяпрограмма не фиксирует факта тех отказов,10 которые не оказывают значительного влияния на основную работу ОКУ.При норме проверок обнуляется регистр 7 и проверенный канал включается восновную работу. Одновременно с прихо 15 дом синхроимпульса СИ 2 происходит перезапись информации из суммирующегорегистра 6 через открытый блок 24 элементаИ, блок 28 элементов ИЛИ в управляющийрегистр 7. В результате в регистрах б и 7окажется записана одна и та же информация, которая поступает на входы блока 14сравнения, на выходе которогосформируется единица, которая с приходом синхроимпульса СИ 1 (чараэ время, необходимое дляперезаписи информации из регистра б в регистр 7) поступит на Р-вход суммирующегорегистра б и приведет его в исходное состояниеПосле а 1 ог." бда г исоа д,и тест,1 рован е,:то; Ог: п,ол",еваамьх : алв. БСяуЧоар; Ге;т 1 рэвдНЛ ХТройСТЬ . арей.",;.1 у 1 кан,.;,ьно. г хама ьэбо,. вГЛУЧс.НОГ)К 1 Ы, , . 1-"О.ДО 1. О 11, Ючакаэ .,н, . гс ка -,л ьха;а .)КУ будет Ораоб35 раэ.",а к Однокл 1 л нойВ . у,ас О .Оружс; ь ээ, астрэанНЫ 1 ИраС, . аК,: КОН рОЛя г рь ууХ ИСПРае ,4 Х ;.сН " 1 / ) 11 нф)ПМЗЦИЯ О : ГКа 3 С-. Од канальной .,хаме ОКУ раоотаюттГЛ.- Э Вь, ЭО.ННЫа СрадСТВа ПО ОПИСаННОму выш алгспи:му), При этом возможно поаобходим.сл) прзизвпдить,.сто ьый контроль с меньшей гочность:О без учета втсростепенных Огка Ов ОКУ. йля ОбеспеченияЭТСго СИ НЗЛ О НаЛИЧ 111 ТРЕХ ОТКаЗОВ СИ.:ТЕмы блокирует ту часть средств встроенног эСалОКОН 1 РОЛЯ, КОТОРа. фИКСИРУСг УКаэаНные Отказы, Крома того, этим же сигнэ 1 омобеспечиваегсл выбор тестовой процедурыс меньшими диагнос 1 ическими нозможностями,Кроме оп 1 саннога выше алгоритма уевтройс 1 во может работать при наличии сигна-,ов от внешних систем. Для этогонеобходимо : вход 38 задать ко;. Отказалкдог;1 нг, и на выходе ЗР получи отват, справно Оно или нег, Эту Возможносте можно, в,:;т, Ос 1 и. использсвать д 1: прад 1 Ь:4456 16раб чей проверки ОКУ. Подавая на Вход 38 В любой очередности коды сомерами ка-алов ОКУ, можно определить, в каком сос 1 оянии Они находятся, Этот же алгоритм моа О использовать и для самопроверки предлагаемого устройства, не прерывая работы ОКУ, С этой целью может быть проверен неисправный канал ОКУ, По результатам проверки (Выход 39) можно судить О работоспособности предлагаемого устрой- СВЯ. Формула изобретения Ус 1 ро ст ВО микропрограммного управления диз;ностированием л восстаночление;:,и ропых систем, содзржще блок микропро раммногп диагностирования и упоавпения, блок синхроимпульсов, шесть зпементов И, суммирующий регистр, первый и Второй блоки элементов И, счетчик оспа отказОВ, коммутатоп входов, коммутг гор рэбочих выходов, блок постоянного контроля, преобоазовагель кодов, блокирующий регистр, первый и второй управляющие рег; стры, первый элемент ИЛИ, приц м Выход первого элемента И соединен с С-входом суммирующего регистра, Выход НОТО;,ЗОГО СОДИНРН С ИНфОРМдЦИОННЬМ ВХОДом первого блока элементов И, управляющий Вход устройства соединен с первым упрчвпяющи Входом бгока синхроимпуль- ООР нерве,й информационный Вход устройс В соединен с первым информациочным Входом коммутатора входов, первый-четв;, тый инфдрма.нончые выходы кпторосоединены соотВРтственно первым- четвертым информационнь.ми Вдали Обье та контроля и управления, "есвый четвертый информационные вь;- ходы которого соединены с первым-четВе;,; ым информационными Входами не 4 Уутд 10 рв рабо 1 их ВыхОДОВ спотВРтст Венно, выход блокирующего регистра соедпненпервым управляющим входом к ммутатора рабочих Выходов, Выхед второго элемент-а И соединен с С-Входом первого УПРВВЛЯнЗЩРГО РЕГИСтРа, ВЫХОД ПЕРВОГО ЭЛЕ- и нта ИПИ соединен с первым О-входом первого унравпяащего Оегистра, выход вторег: бпскз элементов И соединен с Я-Входом Вто; Огс управляющего регистра, о т л и- , а ю щ г ". с з тем, что, с целью повышения производительности путем обеспечения возможности параллельной реализации алгсритмов управления, диагностирования и восстановления каналов, оно дополнительно содержит блок маскирования отказов, коммутатор диагностических выходов. элемен-, ЗИ - ИЛ 1, блок сравнения, мажоритиг,ующий узел, Второй, третий, четвертый и 5 10 15 20 25 30 35 40 45 50 55 ятый элементы ИЛИ, блок элементов ИЛИ, первый - четвертый элементы ИЛИ - НЕ, причем первый и второй управляющие выходы блока микропрограммного диагностирования и управления соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с й-Входом блокирующего регистра и вторым управляющим входом блока синхроимпульсов, первый выход блока синхроимпульсов соединен с первыми входами персого и второго элементов И, второй выход блока синхроимпульсов соединен с первым управляющим входом блока микропрограммного управления и диагностирования и с управляющим входом блока сравнения, выход которого соединен с В-входом суммирующего регистра, третий выход блока синхроимпульсов соединен с вторым управляющим входом блока микропрограммного управления и диагностирования и вторым входом второго элемента И, второй информационный вход устройства соединен с первым информационным входом блока элементов ИЛИ, выход которого соединен с входами третьего элемента ИЛИ, прямыми входами третьего, четвертого и пятого элементов И, первым входом первого элемента ИЛИ и с первым, вторым и третьим информационными входами элемента ЗИ - ИЛИ, выход элемента ЗИ - ИЛИ соединен с втооым входом первого элемента ИЛИ, инверсными входами третьего, четвертого и пятого элементов И, выходы которых соединены соответственно с вторым, третьим и четверты,О-входами первого управляющего регистра, выход первого управляющего регистра соединен с информационным входом второго блока элементов И, вторым информационным входом блока сравнения, первыми входами первого, второго, третьего и четвертого элементов ИЛИ - НЕ, первым управляющим входом коммутатора входов, управляющим входом коммутатора диагноСтических выходов и вторым управляющим входом коммутатора рабочих выходов, первый-шестой информационные Выходы которого соединены соответственно с первым - шестым информационными входами блока маскирования отказов, первый, второй и третий информационные выходы блока маскирования отказов соединены соответственно с первым, вторым и третьим инфоомационными входами бл.:ка постоянного контроля и с первым, вторым и третьим входами мажоритирующего узла. выход которого соединен с первым информационным выходом устройства, перзый, второй и третий управляющие выходы блока маскирования отказов соедине 162445630 35 ны соответственно с первым, вторым и третьим управляющими входами блока постоянного контроля, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами преобразователя кодов, первый, второй и третий выходы преобразователя коров соединены с вторым информационным входом блока элементов ИЛИ и с первым, вторым и третьим входами четвертого элемента ИЛИ, выход которого соединен с первым входом шестого элемента И и вторым входом первого элемента И, выход второго управляющего регистра соединен с первым, вторым и третьим управляющими входами элемента ЗИ - ИЛИ, вторым информационным выходом устройства, первым управляющим входом блока маскирования отказов, третьим управляющим входом коммутатора рабочих выходов, третьим управляющим входом коммутатора входов и вторыми входами первого, второго, третьего и четвертого элементов ИЛИ - НЕ, инверсные выходы которых соединены соответственно с первым-четвертым О-входами суммирующего регистра, выход суммирующего регистра соединен с вторым информационным входом блока сравнения, первый управляющий выход блока микропрограммного диагностирования и управления соединен с В-входом первого управляющего регистра и первым управляющим входом первого блока элементов И, выход которого соединен с третьим информационным входом блока элементов ИЛИ, второй управляющий выход блока микропрограммного диагностирования и управления соединен с управляющим входом 5 10 15 20 25 второго блока элементов И и входом счетчика числа отказов, первый управляющий выход которого соединен с третьим управляющим входом коммутатора входов, второй управляющий выход счетчика числа отказов соединен с третьим входом первого элемента И, вторым управляющим входом первого блока элементов И и вторым входом шестого элемента И, выход которого соединен с С-входом и с первым-четвертым О- входами блокирующего регистра, третий управляющий выход счетчика числа отказов соединен с третьим управляющим входом блока микропоограммного диагностирования и управления и управляющим входом объекта контроля и управления, первый - четвертый управляющие выходы которого соединены с четвертым информационным входом блока элементов ИЛИ и с первым- четвертым входами пятого элемента ИЛИ, выход пятого элемента ИЛИ соединен с четвертым управляющим входом блока постоянного контроля, первый - четвертый информационные выходы объекта контроля и управления соединены соответственно с первым - четвертым информационными входами коммутатора диагностических выходов, выход которого соединен с информационным входом блока микропрограммного диагностирования и управления, информационный выход блока микропрограммного диагностирования и управления соединен с вторым информационным входом коммутатора входов, выход третьего элемента ИЛИ соединен с третьим управляющим входом блока синхроимпульсов, с третьим входом второго элемента И и с четвертым входом первого элемента И.

СмотретьЗаявка

3691357, 06.01.1984

ПРЕДПРИЯТИЕ ПЯ М-5156

СИДОРЕНКО НИКОЛАЙ ФЕДОРОВИЧ, СВИЩ ВЛАДИМИР МИТРОФАНОВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ПЕТУНИН СЕРГЕЙ ЮРЬЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, КИРСАНОВ СТАНИСЛАВ ПЕТРОВИЧ, ОСТРОУМОВ БОРИС ВЛАДИМИРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/18

Метки: восстановлением, диагностированием, микропрограммного, систем, цифровых

Опубликовано: 30.01.1991

Код ссылки

<a href="https://patents.su/16-1624456-ustrojjstvo-mikroprogrammnogo-upravleniya-diagnostirovaniem-i-vosstanovleniem-cifrovykh-sistem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления диагностированием и восстановлением цифровых систем</a>

Предыдущий патент: Сигнатурный анализатор

Следующий патент: Устройство для формирования тестовых сигналов

Случайный патент: Скользящая опалубка для возведения железобетонных сооружений башенного типа