Микропроцессорная вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

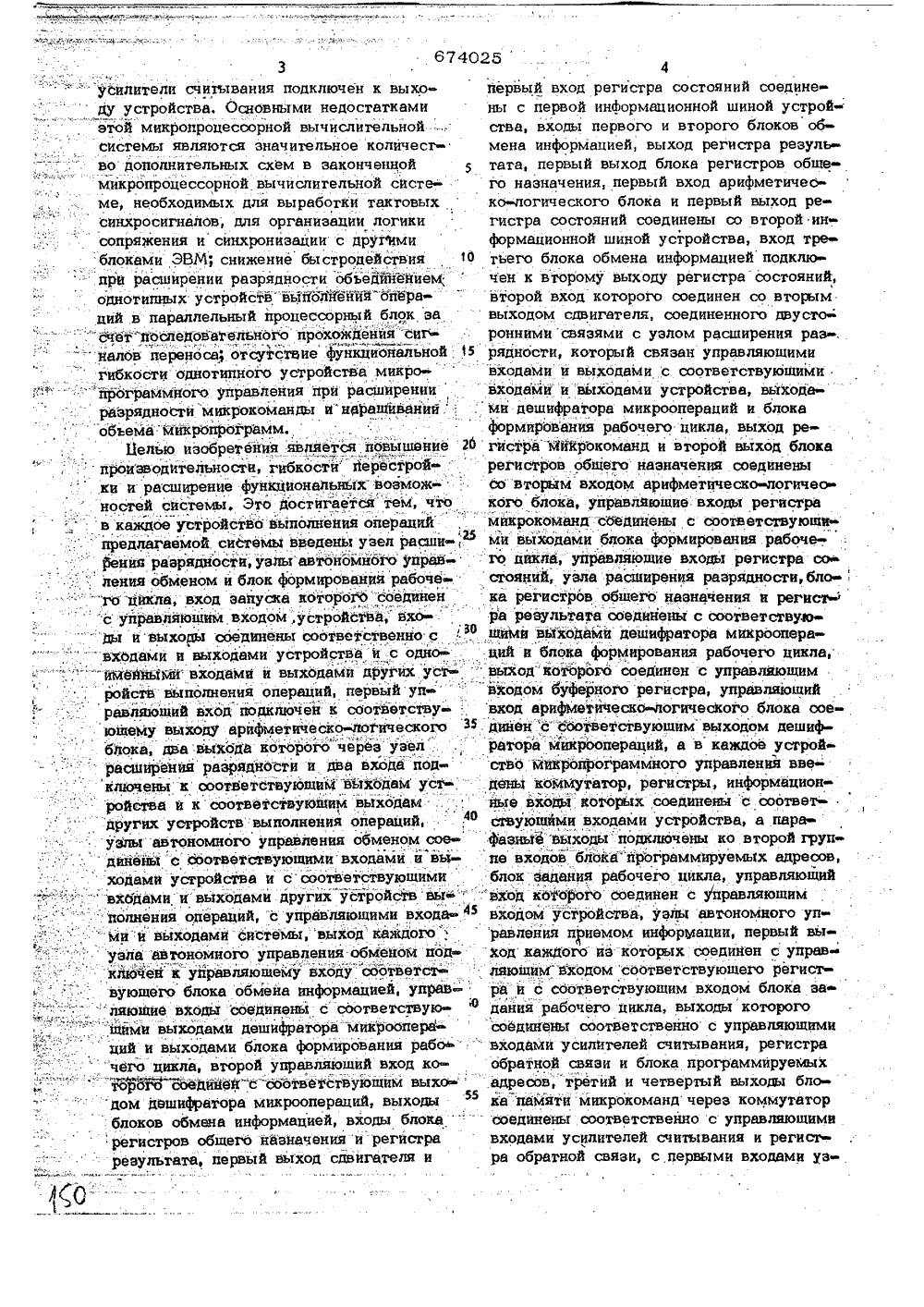

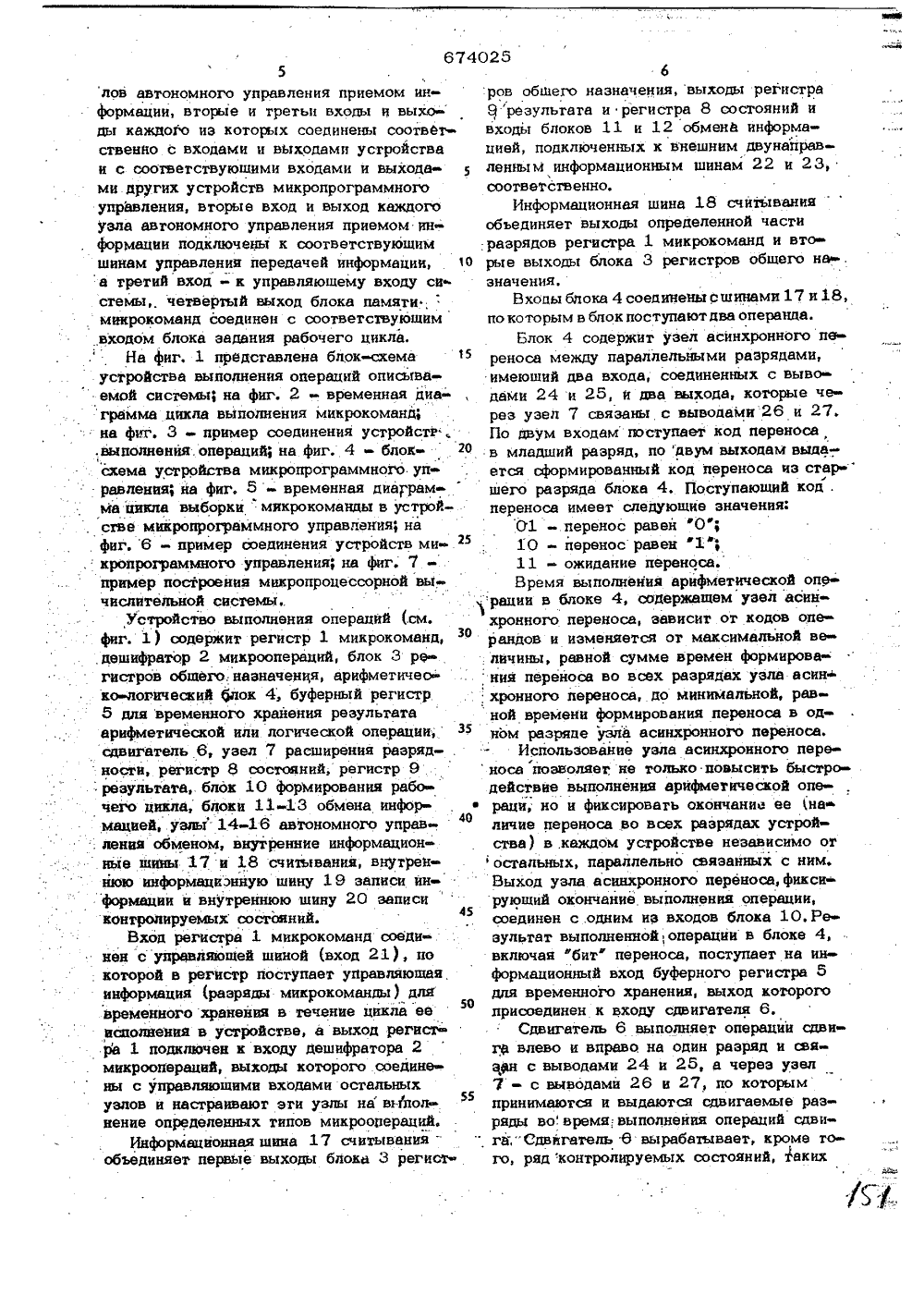

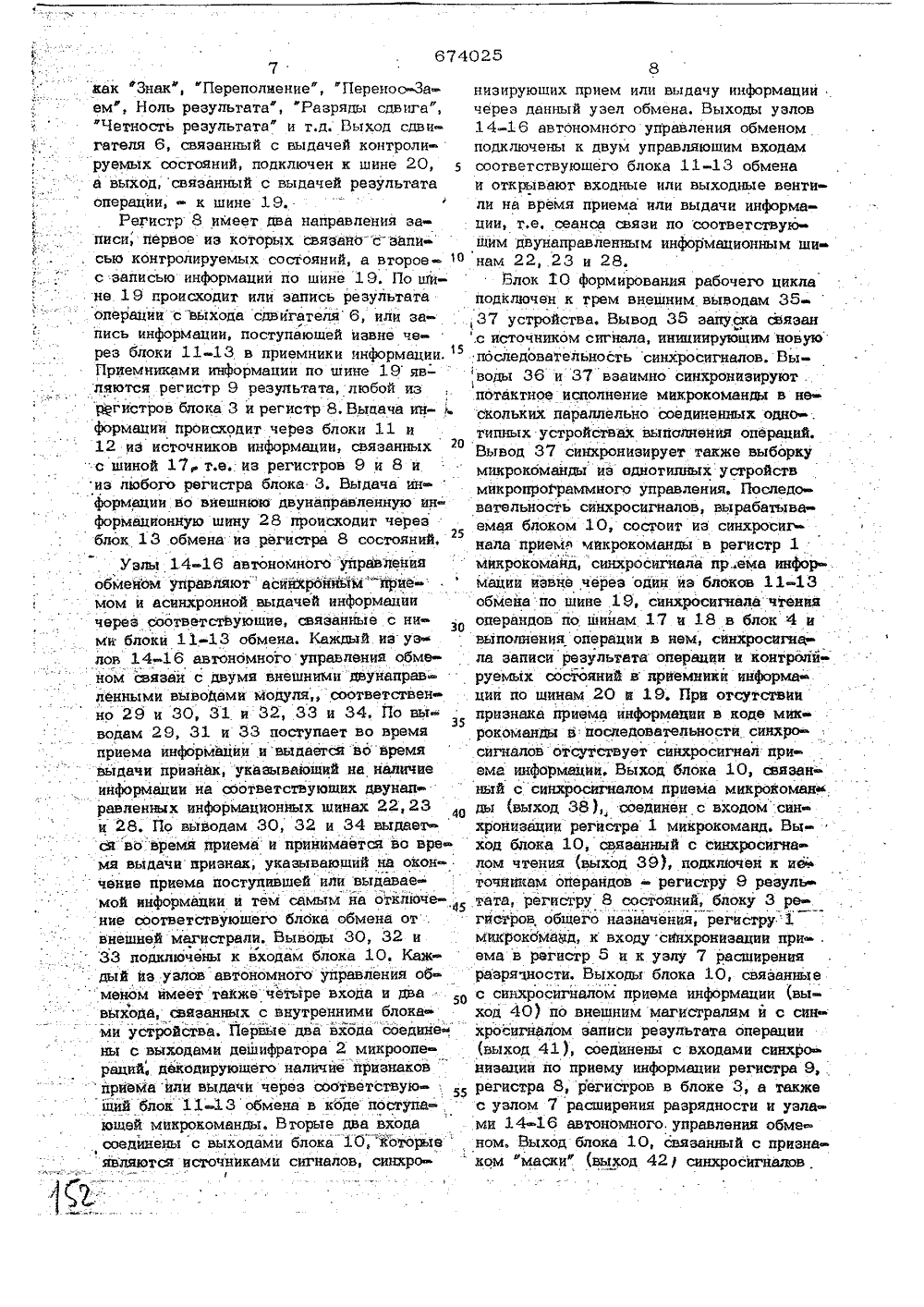

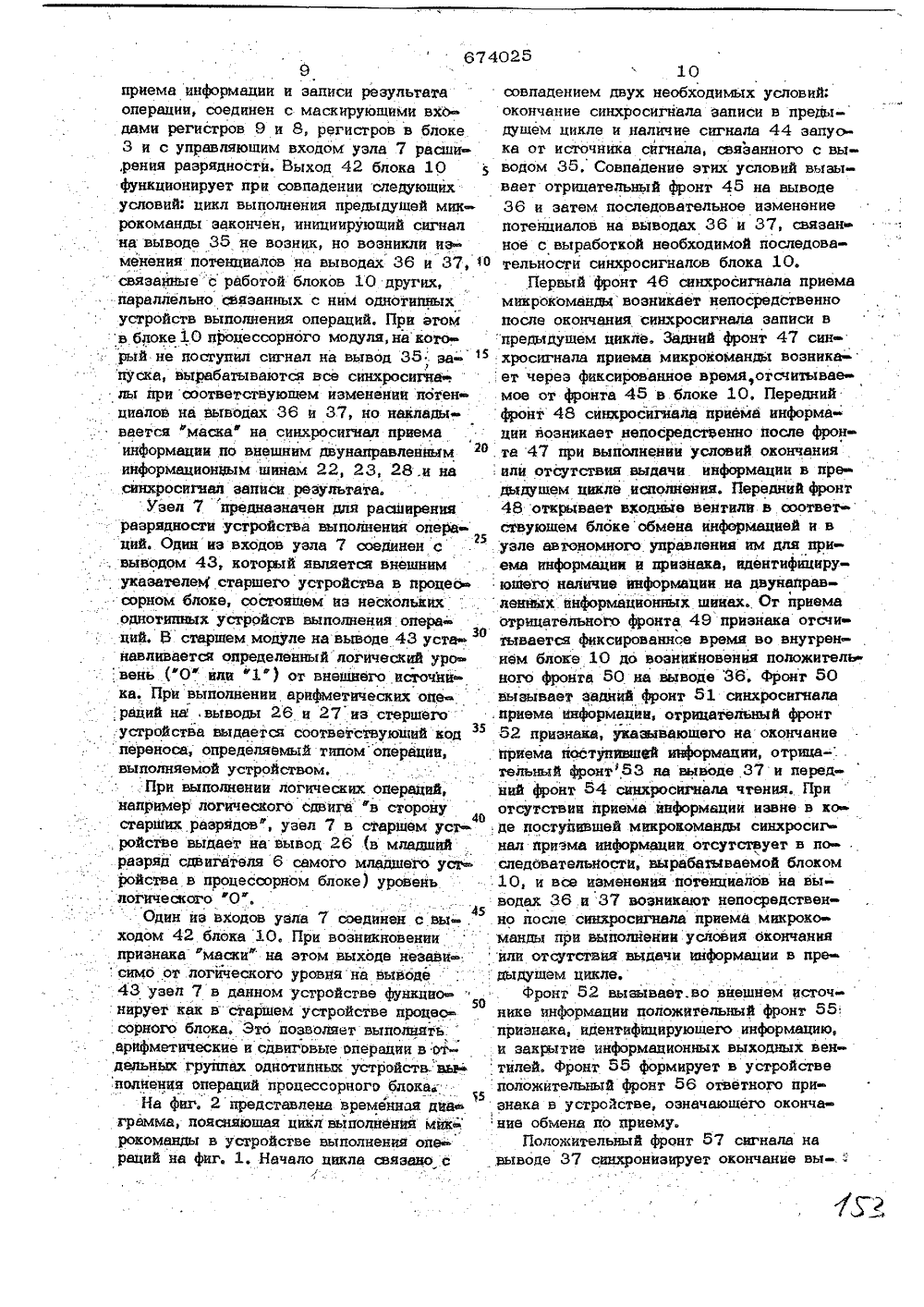

ОП ИСА Ьсосс:лзнап ец 64 О 25 Союз Советскик Социалист ицесюа Республик)М. Кл 606 Р 1 21) 2170458/18-24 22) Зая еио 22.09.75инением заявитет 16 Гесуаервтвеиный СССР ее делан иееб а етернте(71) Заявите КРОПРОЦЕССОРНАЯ ВЫ ЧИСЛИТЕЛЬНАЯ(54 1 2Изобретение относитси к области вы- . регистр результата, регистр состояний; числительной техники и может быть иск . регистр микрокоманд, дешифратор микропользовано в вычислительных устройствах операций, блоки обмена информацией, подразличного назначения, ключенные к двунаправлейиым информациИзвестны микропроцессорные вычисли-онным машинам, и блок регистров общего тельные системы с жестким управлениемЗ, назначения, выход арифметическо логически 12, содержащие арифметическо иоги- кого блока, через буферный регистр соеческий блок, блок регистров, блок деши динен с входом сдвигатейи, вход регистра рации команд, блоки обмена информациеи, микрокоманд подвцочен к управляющей ширегистр состояний и узел распределенйя не, а выход - к входу дешифратора микросинхросигналов. Однако наращивание раз . 1 О операций; каждое однотипное устройство ,рядности обрабатываемой информации Й-та- микропрограммного управления содержит ких микропроцессорных вычислительных си- последовательно соединенные блок програмстемах приводит к значительному снижз- . мируемых адресов и блок Памяти микроконию их быстродействия, а изменение си манд, группы йрограммируемых элементов стемы команд невозможно. 1 з НЕ, регистр обратной связи, парафазныеИзвестна также микропроцессорная вы выходы которого йодключены к первой числительная система с микропрограммным групде входов блока программируемых адуправлением 3,содержащая однотипные ресов, а информационный вход через перустройства выполнения операций и одиотип; вую группу программируемых элементов ные устройства микропрограммного уЩаво. НЕ соедяней с первым выходом блока памялещщ, причем каждое оанотипное,устрой- ти микрокоманд, второй выход которогоство вь 1 нолнения операций содержит ариф через последовательно соединенные вторую метичвско-логический блок, сдвигатель, группу программируемых элементов НЕ и19674025подключен к управляющей шине, а выход- первого и второго блоков обмена информак входу дешифратора микроопераций, каж- цией, выход регистра результата, первыйдое однотипное устройство микропрограм- выход блока регистров общего назначения,много управления содержит последователь- первый вход арифметическо логическогоно соединенные блок программируемыхблока и первый выход регистра состоянийадресов и блок памяти микрокоманд, груп- соединены со второй информационной шипы программируемых элементов НЕ, ре- ной устройства, вход третьего блока обгистр обратной связи, парафазные выходы мена информацией подключен к второмукоторого подключены к первой группе вхо- выходу регистра состояний, второй входдов блока программируемых адресов, а 1 о которого соединен со вторым выходоминформационный вход через первуюгруппу сдвигателя, соединенного двустороннимипрограммируемых элементов НЕ соединен связями с узлом расширения разрядности,с первым выходом блока памяти микроко- который связан управляющими входами имана, второй выход которого через после- выходами с соответствующими входами ндовательно соединенные вторую группу . 15 выходами устройства, выходами дешифрапрограммируемых элементов НЕ й усиля- тора микроопераций и блока формированиятели считывания подключен к выходу уст-рабочего цикла, выход регистра микрокоройства, о т л и ч а ю щ а я "ся тем, манд н второй выход блока регистров обч.о, с целью.повйшенняпроизводительноо- щего назначения соединены со вторым вхоти, гибкости перестройки и расширения о дом арифметическо-логнческого блока, упфункциональных возможностей,"в "каждое равляющие входы . регистра микрокомандустройство выполненйя операций системы: соединены с соответствующими выходамивведены узел расширения разрядности,уз- блока формирования рабочего цикла, управ лы автономного управленияобменом и йиющие входы регистра состояний, узлаблок формирования рабочего цикла, вход 5 расширения разрядности, блока регистров " - запуска которого соединен с управляющим общего назначения и регистра результатавходом устройства, входы и вйходы сое- соединены с соответствующими выходами " динены соответственно с входами и выхо- дешифратора "микроопераций и блока фордами устройстве и с одноименнйми вхо- мирования рабочего цикла, выход которогодами и выходами других устройств выпол ЗО соединен с управляющим входом буфернонения ойераций,:первый управляюший вход го регистра, управляющий вход арифметинодключен к соотвегствующему выходу . ческо-логического блока соединен с соотарйфметическо логического блока, два ви- ветствующим выходом дешифратора микрохода которогочерез узел расширения раз операций, а в каждое устройство микрорядности и два входа подключены к соот программного. управления введены коммуветствующим выходам устройства и к со- татор, регистры, информационные входыответстеующим выходам других устройств которых соединены с соответствующимивыполнения операций, узлы автономноговходами устройства, а парафазные выходыуправления обменом.соединены с соответ- подключены ко второй группе входов блокаствующнми входамн и вйходами устройс фо программируемых адресов, блок заданияваи с соответствующими входами и вы-, рабочего цикла, управляющий вход котороходами других устройств выполнения опе-" го соединен с управляющим входом устройацйй, с управлявшими входами и выхода- ства, узлы автономного управления при-ми системы, выход каждого узла. автоном- емом информации, первый выход каждого-нож управления обменом подключен к уп" ф нз которых соединен с управляющим вхорааляющежу входу соответствующего бло"дом соответствующего регистра и с соотка обмена информацией, управляющиевход; ветствуюшим входом блока задания рабо-.ды соединены с соответствующими выхо-чего цикла, выходы которого соединеныдами дешифратора микроопераций и выхо- "соответственнос управляющими входамидами блока формирования рабочего цикла, 5 О усилителей считывания, регистра обратнойвторойуправляющий вход которого соеди" связи и блока программируемых адресов,нен с соответствующим выходом дешифра- третий и четвертый выходы блока памятитора мккроопераций, выходы блоков обме- микрокоманд через коммутатор соединенына информацией, входы блока регистровсоответственно с управляющими входамиобщего назначения и регистра результата, 5 усилителей считывания и регистра обратпервый выход сдвигателя и первый вход нойсвязи, с первыми входами узлов авторегистра состояний соединены с первой номного управления приемом информации,информационной шиной устройства, входы вторые и третьи входы и выходы каждого67402522 з которых соединены соответственно с команд соединен с соответствующим вховходами и выходами устройства и с соотг дом блока задания рабочего цикла.ветствуюшими входами и выходами других Источники информации, принятые во устройств микропрограммноМ упрбвления, внимание йрй экспертизе вторые вход и выход каждого узла ав-1,фЭлектроника ", пер. с англ., изд. тономного управления приемом информа- Мир",18, 1974 ции подключены к соответствующим шинам2, Патент США М 3878514, управления передачей информации, а тре- кл. 340-172,5, 08.04.75.тий вход - к управляющему входу "систе-3, фЭлектроника", пер. с англ., изд. ьы, четвертый выход блока памяти микро- о, Мир,12, 1973, с. 44-54.674025усилители считывания подключен к выхо- первый вход регистра состояний соедине ду устройства, Основными недостатками ны с первой информационной шиной устрой- этой микропроцессорной вычислительнойства, входы первого и второго блоков об системы являютси значительное количест мена информацией, выход регистра резуль во дополйительных схем в законченнойтата, первый выход блока регистров обще- микропроцессорной вычислительной систе- го назначения, первый вход арифметичесме, необходимых для выработки тактовыхко логического блока и первый выход ресинхросигналов; для организации логики гистра состояний соединены со второй инсопряжения и синхронизации с другими формационной шиной устройства, вход треблоками ЭВМ; снижение быстродействия 0 тьего блока обмена информацией подклю пре расширении разрядности объедйнениемчен к второму выходу регистрасостояний, однотипных устройств"выйолйейия"опта-"второй вход которого соединен со вторым ций в параллельный йроцессорный блок за выходом сдвигателя, соединенного двусто-.Жет-последовательного прохождения си ронними связями с узлом расширения раз .налов переноса, отсутствие фуйкцйональной 15 рядности, который связан управляющими гибкости однотипного устройства микро-входами и выходами с соответствующими.прбграммНого управления при расширении входами и вйходами устройства, выходараэрядности микрокоманща и" наращиваний, ми дешифратора микроопераций и блока обьемамйсрбпрбграмм.формирований рабочего цикла, выход реЦелью изобретения является повышение 6 гйстраЯйкрокоманд и второй выход блокапроизводительности, гибкости ЙерестрМ- регистров общего назначения соединены ки и расширение функциональнйх-возмож-: со вторым входом арифметическо-логичео ностей системы. Это достигаетбя тем, что кого блока, уйравляющие входы регистра в каждое устройство выполнения операций макрокоманд соединены с соответствующнпредлагаемой. системы введенй узел расши-,ф ми выходами блока формирования. рабоче.рениа разрядности, узлы автономного управ: го дйкл 6, уйРавляющие входы регистра сом пения обменом й блок формирования рабоче. стояний, узла расширения разрядности, бла-"го цикла, вход зайуска которого соединен ка регистров общего назначения и регистс управляющим входом .устройства:, вхо- . ра результата соедйнены с соответствую Фа и выходы соединены соответственно с . 0 Шими выходами дешифратора микроопера входами и выходами устройства и с одно- ций и блока формирования рабочего цикла, -" , Ваайййаг входами и выходами других уст- " вйход" которого соединен с управляющимройств выполнения операций, первый упвходом оуферного регистра, управляощий рюляющий вход подкаочен к соотвэтству-вход арифметическо-логического блока соеющеМу выходу арйфметическо-лиического З динан с сбответствуюшим выходом дешифблока, два вихра которого через узелратора мйкроопераций, а в каждое устрой расщирения разрядности и два входа под- ство мйкрйфограммного управления ввеключень к соответствующим."выходам уст-. - денй коммутатор, регистры, информацион ройетва и к соответствующим выходам .;йые входы которых соединены с соответ:40других уогройств выполнения операций,:; 0 ствуюшими входами устройства, а пара узлы автономного управления обменом сое- разные выходыподключены ко второй групдиненыс соответствующими входами и вы- пе входов блока"программируемых адресов, ходами устройства и с соответствующими блок задания рабочего цикла, управляющий ":." " :вхбдами и- выходами других устройстввы "вход котброго соединен с управляющимполнения операций, с управляющими входавходом устройства, узлы автономного упми:и выходами системы, выходкаждого.равления приемом информации, первый выузла автономного управления обменом под "ход каждого нз-которых соединен с управкййчен к управляющему входу ооответстляющим"Входом соответствующего региствующего блока обмена информацией, управ- ра и С соответствующим входом блока эаляющие входй соединены с соответствую дания рабочего цикла, выходы которогощйми выходами дешифратора микроопера-. соединены соответственно с управляющими ций и выходами блока формирования раба- " входами усилителей считывания, регистра чего цикла, второй управляющий вход ко- обратной связи и блока программируемых торбж соедйней с" соотвИ 3 твующим выхо.адресов, третий и четвертый выходы бло дом дешифратора микроопераций, выходы 5 ка памяти микрокоманд через коммутатор блоков обмена информацией, входы блока " - соединены соответственно с управляющими регистров общего назначения ирегистра входами усилителей считывания и регистрезультата, первый вйход сдвигателя и ра обратной связи, с первыми входами уз674025 6ров обаего назначения, выходы регистраЯрезультата и регистра 8 состояний ивходы блоков 11 и 12 обмена информацией, подключенных к внешним двунайравленным информационным шинам 22 и 23,соответственно.Информационная шина 18 считыванияобъединяет выходы определенной частиразрядов регистра 1 микрокоманд и вторые выходы блока 3 регистров общего назначения,Входы блока 4 соединены сшннамн 17 н 18,по которым в блок поступают два операнда.Блок 4 содержит узел асйнхронного переноса между параллельными разрядами,имеющий два входа, соединенных с выводами 24 и 25, и два выхода, хоторые через узел 7 связаны с выводами 26 и 27.По двум входам поступает код переносав младший разряд, по двум выходам выдается сформированный код переноса из старщего разряда блока 4. Поступающий код .переноса имеет следующие значения:О 1 - перенос равен ф 010 - перенос равен Х",11 - ожидание переноса.Время выполнения арйфметической операции в блоке 4, содержащем узел асинхронного переноса, зависит от кодов операндов и изменяется от максимальной величины, равной сумме времен формирова ния переноса во всех разрядах узла асин, хронного переноса, до минимальной, равной времени формирования переноса в одном разряде узла асинхронного переноса,Использование узда асинхронного переноса позволяет, не только повысить быстродействие выполнения арифметической опереди; но и фиксировать окончание ее (наличие переноса во всех разрядах устройства) в каждом устройстве независимо отостальных, параллельно связанных с ним.Выход узла асинхронного переноса, фиксирующий окончание выполнения операции,соединен с.одним из входов блока 10.Результат выполненной, операции в бдоке 4,включая "бит" переноса, поступает на информационный вход буферного регистра 5для временного хранения, выход которогоприсоединен к входу сдвигателя 6.Сдвигатедь 6 выполняет операцйи сдвига влево и вправо на один разряд и связуя с выводами 24 и 25, а через узел7 - с выводами 26 и 27, по которымпринимаются и выдаются сдвигаемые разряды во.время, выполнения операций сдви га;"Сдвигатель 6 вырабатывает, кроме того, ряд контролируемых состояний, таких 5лов автономного управления приемом информации, вторые и третьи входы и выхо" ды каждого из которых соединены соотвз- ственно с входами и выходами устройства и с соответствующими входами и выхода ми других устройств микропрограммного упрюления, вторые вход и выход каждого узда автономного управления приемом информации подключены к соответствующим шинам управления передачей информации, 10 а третий вход - к управляющему входу си" стемы,. четвертый выход блока памяти мнкрокоманд соединен с соответствующим входом блока задания рабочего цикла.На фиг, 1 представлена блок-схема устройства выполнения операций описываемой системы; на фиг. 2 - временная диаграмма цикла выполнения микрокоманд; на фиг. 3 - пример соединения устройств, ,выполнения. операций; на фиг. 4 блок20 схема устройства микропрограммного уп равления; на фиг, 5 временная пиастрам ма цикла выборки микрокоманды в устройстве микропрограммного управления; на фиг. 6 - пример соединения устройств ми кропрограммного управления, на фиг, 7- пример построения микропроцессорной вычислительйой системы,.Устройство выполнения операций (.см, фиг. 1) содержит регистр 1 микрокоманд, дешифратор 2 микроопераций, блок 3 регистров общего. наэначенця, арифметичеоко логический едок 4, буферный регистр 5 для временного хранения результата арифметической иди логической операции, З 5 сдвигатель 6, узел 7 расширения разряд- . ности, регистр 8 состояний, регистр 9 : результата, блох 10 формирования рабочего цикла, блоки 11 13 обмена инфор-манией, узды 14-16 автономного управ 40 . пения обменом, внутренние информацион.ийе шины 17 и 18 считывании, внутреннюю информациэнйую шину 19 записи информации и внутреннюю шину 20 записиконтролируемых состояний.45Вход регистра 1 микрокоманд соединен с управляющей шиной (вход 21), по . которой в регистр поступает управляющая информация (разряды микрокоманды) для50 временного хранения в течение цикла ее исполнения в устройстве, а выход регнст- .рЬ 1 подключен к входу дешифратора 2 микроопераций, выходы которого соедине ны с управляющими входами остальных узлов и настраивают зти узлы на выпол55 нение определенных типов микроопераций.Информационная шина 17 считыванияобьединяет первые выходы блока 3 регист67как Знак", "Переполнение", "Перенос Заем, Ноль результата", "Разряды сдвига", "Четность результата" и т.д, Выход сдвигателя 6, связанный с выдачей контролируемых состояний, подключен к шине 20, а выход, связанный с выдачей результата операции, к шине 19.ФРегистр 8 имеет два направления записи, первое из которых связано"с запи. сью контролируемых состояний, а второе О с записью информации по шине 1 9. По шине 1 9 происходит или запись результата операции с выхода сдвигателя 6, или запись информации, поступающей извне через блоки 11-13 в приемники информации.Приемниками информации по шине 19 являются регистр 9 результата, любой изрегистров блока 3 и регистр 8, Выыдача информации происходит черве блоки 11 и12 из источников информации, связанныхсшиной 17, т.в из регистров 9 и 8 и из любого регистра блока 3. Выдача информации во внешнюю двунаправленную ин-формационную шину 28 происходит черезблок 13 обмена из регистра 8 состояний,Узлы 14-16 автономного управленияобменом управляют асинхройным" фив- .мом и асинхронной выдачей информациичерез соответстЬующие, связанные с ними блоки 11-13 обмена. Каждый из уз.лов 14-16 автономного управления обмвйом связан с двумя внешними двунаправленными выводами модулясоответственно 29 и 30, 31 и 32, ЗЗ и 34. По вылводам 29, 31 и 33 поступает во времяприема инф РМЬ и и дажю во ьрвыдачи признаки, указывающий на наличиеинформации на соответствующих двунаправленных информационных шинах 22, 23 4и 28, По выводам 30, 32 и 34 выдаетсаво времй приема и принимается во время выдачи признак; указывающий на окон чение приема поступившей или выдаваемой информации и тем самым на отключение соответствующего блбка обмена от .внешней магистрали. Выводы 30, 32 и33 подключены к входам блока 10. Каждый из узлов автономного управления обменом ймеет тмже четыре входа и двавыхода, связанных с внутренними блоками устройства. Первые два входа "соедине;ны с выходами дешифратора 2 микроопе раций, двкодируюшего наличие признаковприема или выдачи через соответствую- . щий блок 11 13 обмена в коде постуи- ющей микрокоманды, Вторые два входасоедйнены с выходами блока 10, которыеВявляются источниками сигналов, синхроф 8ниэирующих прием или выдачу информации через данный уэел обмена, Выходы узлов 14-16 автономного управления обменом подключены к двум управляющим входам соответствующего блока 11-13 обмена и открывают входив или выходные вентили на время приема или выдачи информации, т,е, сеанса связи по соответствую щим двунаправленным информационным ши нам 22, 23 и 28.Влок 10 формирования рабочего цикла подключен к трем внешним выводам 35,37 устройства. Вывод 35 зайуска связан ,с источником сигнала, иннпиирующим новую последовательность синхросигналов. Выводы 36 и 37 взаимно синхронизируютпотактное исполнение макрокоманды в нв скольких параллельно соединенных одно-, типных устройствах внпалнения операций. Вывод 37 синхронизирует также выборку микрокоманды иэ однотипных устройств микропрограммного управления. Последо вательность сйнхросигналов, вырабатыва вмая блоком 10, состоит из синхросит- нала приемд чакрокоманша в регистр 1 микрокоманд, синхросигиала према инфор- . мации иэвне через один из блоков 11-13 обмена по шине .19, синхросигнала чтения операндов по шинам 17 и 18 в блок 4 и выполнения операции в нем, синхросигна;- ла записи результата операции и контроли- руемых состояний в приемники информа ции по шинам 20 и 19. При отсутствии признака приема информации в коде мик рокоманды в последовательности синхросигналов отсутствует синхросигнал приема информации, Выход блока 10, связанный с" синхросигналом приема микрокоман ды (выход 381 соединен с входом син хронизации регистра 1 микрокоманд. Вы-ход блока 10, саяэанный с синхросигналом чтения (выход 39 у, нодключен к ие. точнниам операндов - регистру 9 резуль тата, регистру 8 состояний, блоку 3 ре гиетров общего назначения, регистру:1 микрокомаюд, к входу синхронизации при ема в регистр 5 и к узлу 7 расширении разрячности. Выходы блока 10, связанные с сйнхросигйалом приема информации (выход 40) по внешним магистралям й с синхросигналом записи результата операции (выход 41), соединены с входами синхро ниэации по приему информации регистра 9, регистра 8, регистров в блоке 3, а также с узлом 7 расширения разрядности и узлами 1416 автономного, управления обме" ном. Выход блока 10, связанный с признаком "маски" (вьход 42синхросигналсв .6740259 10приема информации и записи результата - совпадением двух необходимых условийоперации, соединен с маскирующими вхо- окончание синхросигнада записи в преды-дами регистров 9 и 8, регистров в блоке душем цикле и наличие сигнала 44 эапуо 3 и с управляющим входом узла 7 расши- ка от источника сигнала, связанного с вы,рения разрядности. Выход 42 блока 10водом 35, Совпадение этих условий вызыфункционирует при совпадении следующих веет отрицательный фронт 45 на выводеусловий цикл выполнения предыдущей мик и затем последовательное изменениерокоманды закончен, инициирующий сигнал потенциалов на выводах 36 и 37, связанна выводе 35 не возник, но возникли из ное с выработкой необходимой последоваменения потенциалов на выводах 36 и 37, 1 О тельности синхросигналов блока 10.связанные с работой блоков 10 других, Первый фронт 46 синхросигнада приемапараллельно связанных с ним однотипных микрокоманды возникает непосредственноустройств выполнения операций. При этом после окончания синхросигнада записи в в блоке 10 процессорного модуля,накото "предыдущем цикле, Задний фронт 47 синрый не поступил сигнал на вывод 35 за-хросигнала приема микрокоманды возника)пуска, вырабатываются все синхросигна", ет через фиксированное время,отсчитывавлы прв соответствующем изменении потев- мое от фронта 45 в блоке 10, Переднийпиалов на выводах 36 в 37, но накдадыфронт 48 синхросигнада приема информавается дамаска на синхросигнад приема: цив возникает непосредственно после Фронинформации по внешним двунаправленным о. та 47 при выполнении условий окончанияинформационным шинам 22, 23, 28.и на иди отсутствии выдачи информации в пресинхросигнад записи результата. . дыдущем цикле исполнения. Передний фронтУзел 7 предназначен ддя расширения 48 открывает входнйе вентили в соответразрядности:устройства выполнения опера- ствующем блокеобмена информацией и вций. Один из входов узда 7 оддинен с .5 узде автономного управления им для при выводом 43, которьй является внешним ема информации в признака, идентифицирууказателеМ старшего устройства в процео юшего наличие информации на двунаправсорном блоке, состоящем из несколькихденных информационных шинах. От приемаоднотипных устройств выполнении опера- отрицательного фронта 49 признака отсчиций. В старшем модуле на выводе 43 уста- Зо тывается фиксированное время во внутреннавливается опредедейный логический уро нем блоке 10 до возникновения положитель .вень ("0" или "1) от внешнего источай ного фронта 50 на выводе 36. фронт 50ка. При выполнении арифметических оце- вызывает задний фронт 51 синхросвгнада : раций на выводы 26 и 27 вз стершего . приема информации, отрицательный фронтустройства выдается соответствующий код з 5 52 признака, указывающего на окончаниепереноса, определяемый типомоперации, приема иоступившей информации отрицавыполняемой устройством,тедьный фронт 53 на выводе 37 и передПри выполнении логических операций, ний фронт 54 синхросигнала чтения. Принапример логического сдвига фв сторону отсутствии приема информации извне в костарших разрядов, узел 7 в старшем ус 1 ,де поступившей микрокоманды синхроси40ройстве выдает на вывод 26 (в младший над призма информации отсутствует в по- .разряд сдвигатедя 6 самого младшего уст. следовательноств, вырабатываемой блокомройства в процессорном блоке) уройень. 10, и все изменения потенциалов на вы логического "0". водах 36 и 37 возникают непосредственОдин из входов узла 7 соединен с вы, . но после синхросигнада приема микроко45ходом 42 блока 10. При возникновенииманды при выполйенив условий окончаниипризнака- "маски" на этом выходе ненавиили отсутствия выдачи информации в пресимо от логического уровня на выводедыдущем цикде.43 узел 7 в данном устройстве функциофронт 52 вызывает.во внешнем источнирует как в "старшем устройстве процео- нике информации подожвтельный фрон 555 О. сорного блока. Это позволяет выполнять. " признака, идентифицирующего информацию, ,арифметические и сдвиговые операции в от- и закрытие информационных выходных вендедьных груйпйх однотипных устройств. Внь,тилей. Фронт 55 Формирует в устройстве полнения операций процессорного блока; положительный Фронт 56 ответного приНа Фвг. 2 представлена временная дар знака в устройстве, означающего оконча 15грамма, поясняющая цикл выполйенвя мнк".ние обмена по приему. Рокоманды в устройстве выполнения опе Положительный фронт 57 сигнала наРаций на Фиг. 1. Начало цикла связано с .выводе 37 синхронизирует окончание вы- -Г.М 67402511 12 полнения арифметической, логической или четырех устройств, Одноименные выводы пересылочной операции. Для логических 29-34 всех устройств объединены. Вы,и пересылочных операций окончание выпол. воды 28 всех устройств поразрядно объе ненни операций связано с фиксированным динены, образуя общую магистраль состо временем, отсчитываемым от отрицателт 5 яний, Одноименные выводы 35 объединеного фронта 53, а для арифметическихны в устройствах 67 и 68, 69 и 70, об операций, сэязанных с исиихройным-пере- разуя две группы в процессорном блоке, . носом, окончание выполнения, отсчитыва Это позволяет подачей раздельных иницииемое от фронта 53, зависит от числовых рующих сигналов выполнять раздельно опекодов, поступающих на входы арифметичео 1 О рации над полусловами в отдельной груп кологического блока 4 и вырабатывается пе (разрядность слова равна разрядностиузлом асинхронного переноса в этом бпо процессорного блока). Выводы 36 и 37ке, фронт 57 вызывает задний фронт 58 выполняют функцию Проводное И". Это синхросигнапа чтения, передний фронт 59 позволяет в объединенных устройствах5 "синхросигйапа записи и отрицательный взаимно синхрбнизировать окончание прифронт 60 сигнала на вь 1 воде 36. Положи- ема информации, окончание записи иначательный фронт 61 сигнала на выводе 36 ло выдачи информации.возникает через определенное время, сея- Устройство микропрограммного управзанное сокончанием записи результата пения (см. фиг. 4) содержит входные ре операции, отсчитываемое в блоке 10 от гистры 71 и 72, информационные входы20фронта 60, и вызывает задний фронт 62, которых сэязаны с выводами 73 и 74 уст синхросигнала записи, передний фронт 46 ройства, узлы 75 и 76 автономного упсинхросигнала приема следующей микроко равления асинхронным приемом информа манды. При. необходимости осуществления ции в них, последовательно соединенйые25 выдачи информаций через один из блоков блок 77 программируемых адресов и блок 11-13 обмена фронт 61 открывает выход памяти микрокоманд, группу црограмнье вентили соответствующего блока об- мируемых,элементов НЕ 79, выходные мена и формирует отрицательный фронт .усилители 80 считывания, регистр 81 об признака, идентифицирующего выдава-ратной сваей и блок 82 задания рабочего30емую информацию. Этап выдачи информа- цикла. Блоки 77 и 78 представляют собойции совмещается с приемом следующейряд горизонтальных шин (строк) и ряд вермикрокоманды в устройство выполнения тикальных шин (столбцов), в перекрести операций и продолжается до появления от : ях между которыми находятся программирицательного фронта 64 ответного" при-руемые вентильные элементы (диод, тран 35 знака от внешнего приемника информации на зистор). на одном из выводов 30, 32 и 34,свя К входам (строкам) блока 77 присоеди занйом с соответствующим узлом уйравле- иены парафазные выходы регистров 71, ния обменом. Отрицательный фронт 64 фор и 81. Выходы блока 77 (столбцы) мирует, положительный фронт 65 йризна 4, присоедийены к входам (строкам) блока , ка, идентифицирующего выдаваемую инфор, выходы (столбцы) которого в свою майю," и закрывает выходные вентили в очередь объединенц с.входаМи груням про соответствующем блоке обмена. Фронт 65 граммируемых" элементов НЕ 79. Группа юрмирует фронт 66 во внешйеМ приемни программируемых элементов НЕ 79 либо ке информации, что и определяет оконча-транслирует логический уровень соотвез45 ние обмена по выдаче информации,ствующего выхода матрицы 78 либо инНа фиг. 3 представлен пример постро вертируев этот. погичежий уровень. Вы-. ения процессорного блока из четырех уст- ходные усилители.80 считывания представройств 67-70, выполнения операций. Од- ляют собой набор мощных выходных уси;ноименные выводы 36 и 37 всехустройств;пйтельных каскадов, имевших раздельные50 , выполнения операций объединены. Вывод информационные входы, объединенные че 43 устанабливаеВЗГв"оЯном" из"эИВ"уст рез группу программируемых элементов ройств, которое является старшим, в по- НЕ 79 с определенной частью выходов ложение, отличное от положения одноимен- блока 78, и общие стробирующий и маодругих устройствах т э 5 кируф ший входы тробирующий вход обыьфф объединен для примера с земляной шиной. дийен через выход 83 устройства с одним Выводы 24 и 25 каждого устройства объе- из выходов блока 82 задания рабочего ,динены с выводами 26 и 27 соседнего цикла, Выходы усилителей 80. считыванияустройства, образуя кольцевую сэязь всех объединены с выводами 84 устройства и67402513 14позволяют выподнять логическую функцию но вход узда 76 обьединен с выходом сду"Проводное И". Вторая часть выходов бло. жебного разряда 85, являющимся признака 78 .через группу элементов 79 обье- ком необходимости приема информации вдинена с информационными входами регист- регистр 72. Блок 82 задания рабочегора 81 обратной связи, Третья часть вы . 5 цикла подключен через вывод 97 к источходов блока 78 представляет собой четы- нику внешнего сигнала запуска устройстре служебных разряда 85-88 кода микроко ва микропрограммного управления. Одинманды,два из которых (85 и 86)являются из выходов блока 82 объединен со стропризнаками, определяющими необходимость бирующим входом 98 блока 77, и с входомприема информации соответственно в ре О дополнительного (фиктивного) элементагистры 71 и 72 перед выборкой кода слев этом блоке, Выход этого элемента чедующей микрокоманды, а следующие два рез инвертор обьединен со стробирующимразряда 87 и 88 являются признаками,входом 99 и.входом дополнительного (фик"маски". Выход разряда 87 обьединей с . тивного)элементаблока 78,Выход этогомаскирующим входом усилителей 80 счи 5 второго элемента подключен ко входу блоюйвании,- -:ка 82,Регистр 81 обратной связи, кроме вхо- Дополнительные элемент не выполняда синхронизации по приему, обьединенно- ют логических фуйкцнй и предназначены.го с одним из выходов блока 82, имеет для моделирования переходных процессоввход, маскирующий прием информации от.20 происходящих в блоках. Один иэ входовнего, Этот вход соединен с выходом слу блока 82 через вывод 100 устройстважебного разряда 88. .; подключен к источнику внешнего сигнала,Каждый из узлов 75 и 76 автономно разрешающего считывание информации изго управления приемом информации в ре.- устройства. Это позволяет последовательгистр обьединен с четырьмя выводами со" но (каскадно) соединять устройства мик-25ответственно 89-92 и 93-96 устройства. -:.ропрограммного управления для увеличенияВыводы 89 и 93 подключены к источкигдубинымикроподпрограммифункцнонадЬиойкам внешних сигналов, устанавливающих .мощности блока микропрограммного управна выводах 73 и 74 извне признаки йеоб-:ления.ходимости приема информации в управля- . На фиг. 5 представлена временная диазоемые ими регистры, Выводы 90 и 94 под- грамма, поясняющая цикл выборки кодаключены к источникам внешних сигналов, мнкрокомащу в устройстве микропрограмидентифицируюших наличие информации на много управления.выводах.73 и 74, Выводы 91 и 95 под=Цйкл выборки вкаочает в себя этапключены к внутренним .источникам в уз- приема информации во входные регист 1 ы;. дах 75 и 76, формйрующих ответные сиг,и регенерации блоков 77 н 78, этап счинади об окончании приема информации. На . тывания информации иэ блоков и этап вывыводах 92 и 06 устанавливаются узла-.дачи сформированного кода макрокоманды.ми 75 и 76 потенциальные уровни, раэ- Регенерация блоков необходима при дина40решающие прием сигналов по вйводам 90, мическом хранении информации в них (наи 94. Выводы 92 и 96 нри объедйненйи пример, в матрицах; Реализованных по техс одноименными выводами других устройств . вологин КМОП схем, информация хранит,микропрограммного управдения выподня- ,ся во времясчитывания на внутренних лают логическую функцию Проводное И и разитных емкостях)предназначены ддя одновременного приема " Этап приема и регенерации начинаетсясигнадов по выводам 90 и 94 и, соответ с поступления на вывод 97 отрицательноственно, идентифицируемой ими информа- го фронта 101 сигнала. фронт 101 форции в несколько параллельно обьединенвыхмирует в блоке 82 отрицательный фронтустройств. , " 102 синхроси 1 нала выдачи на выходе 83,50Каждый иэ узлов 75 и 76 формирует передний фронт 103 синхросигнала приемасинхросигвад приема информации,который в регистр 71 в узле 75, передний фронтпоступает на вход синхронизации по при синхросигнала "приема "в регистр 72ему управляемого этим узлом регистра и в узде 76 и передний фронт 105 синхро-на один иэ входов блока 82, Кроме того, сигнала, поступающего на стробирующий55,вход узла 75 объединен с выходом слу- вход блока 7. фронт 103 устанавливаетжебного разряда 86 кода микрокоманды, в узде 75 логический уровень, разрешаюявдяющимся признаком необходимости при- ший прием отрицательного фронта 106 приема информации в регистр 71. Аналогич- знака, поступающего на вывод 90 и ин67402515 161формации, поступающей на входы регист запись части выходного кода в регистрра 71. Аналогично фронт 104 в узле 76 раэ-, обратной связи при отсутствии признакарешает прием отрицательного фронта 107 маски" в разряде 88, установка признапризнака, поступающего на вывод 94. Раэ- ков необходимости приема информации в "решающие логические уровни на выводах 1 узлах 75 и 76. При наличии признака92 и 95 устанавливаютсяпри выполнении майси" в разряде 87 на выводы. 84 вы-условия окончания предыдущего обмена дается код ф 1, 1; , 1 ф. При поступлепо приему в соответствующие регистры. " "нии отрицательного фронта 101 на выводЧерез оппеделенйое время, отсчитываемое 97 начинается новый цикл выборки следув узле 75 автономного приема от поступ 10 ющемкода микрокоманды.ления фронта 106, формируются задний Для увеличения разрядности выходногофронт 108 синхросигнала приема в регистр кода микрокоманды необходимо объединить71 и отрицательный фронт 109 ответного . одноименные выводы 73, 74, 83, 89 сигналаоб окончании приема, поступав и 100 нескольких устройств. При этом"щего на вывод 91. фронт 109 вызываетразрядностьвыходного кода увеличиваетво внешнем источнике информацииположи-. . ся вдвое, Йтров и т.д. в зависимости оттельный фронт 110 сигнала на выводе-: : чисЮ параллельно соединенных устройств90, котор 1 В в свою очередь фдрмйрувт.; в блоке. Объедийение выводов 83, выполв узле 75 положительный фронт 111 о" няющих" логическую функцию "Проводноеветного. сигнала. Аналогйчно в узле 76 о И".,позволяет синхронизировать одновреформируются задний фронт 112 синхрбсигй . менность вьдачи выходного ода из всехнала приеме в регистр 72 и отрицатель"."устройств вне зависимости от временныхный фронт 113 ответного сигналю наЬы- . переходных характеристик в каждом изводе 95; вцжвающего йоложительный .: них. Для увеличения объема мйкроподфронт 114 на выводе 94, который в своюйрбграммможнопредложить несколькоочередь формирует положительный фронт".:. ," " способов построения блоков микропрограм 115 на"выводе 95,фронт 105 произвьдит много управХейия.регенерацию блока 77 через время, опрв.: При одном способе построения необходелявмое временной задержкой на рвгене- ". димо соединить параллельно несколько усЬрацию дополнительйого элемента блока 77, . Ройсов:микройрограммном управления,30который формирует фронт 116, Фронт 116: объединиводноименнйв выводы 73, 74,производит регенерацию блока 78 через,. 83, 89-95, 97, 100 и 84, При этом сувремя,определяемоевременнойзадержкойна . шествуют два способа распределения мик-регенерапию дополнительного элемента блока;: ройрограмм для множества входных .кодов.78,которыйфЬрмируетфронт 117-признак В одном способе это множество раэдвля 35окончания регенерации блоков. При сов-ется на отдельные "подмножества, микройайении условий окончания приема инфор". ."программы которых упйковываются размации в регистры и окончания регенвра- : дельно по устройствам; т.в. на поступлениеции в блоках и блоке 82 формируетсйопределенноговходного кода откликаетсй40фронт 118, вызйвающий при наличий раз- , только одноумройство, а в остальныхрешающем логического .уровня на "Йыводв, устройствах йа этот код вырабатываются100 считывание информации из блока 77,признаки фмаски" в разрядах 87 и 88.Вопрограммируемых адресов. Через время,втором способе на постуйление входногоонределяемов временем считыванияв до" . кода откликаются йесколько устройств45-: -полнительном элементе блока 77, возника- формирующих совместно код микрокоманет фронт 119, вызывающий считывание ды на объединенйыхвыводах 84, выпол. информации в блохе 78. Через время, оп. няющих логическую функцию фПроводное,ределяемое временем считывания в допол И" при выдачеЦелесообразно использонительном элементе блока 78, вознйкает - вать,оба эти способа при распределениифронт 120, который является признаком микпопрограмм.готовностиустройства к вйдаче микроко- Максимальная глубина микроподпрограмманды. При совпадении этом условия с: мы в одйом устройстве микропрограммнонапичием уровня логической;1 на ФЫво" го управления ограничивается разрядностьюдв 97 возникает передний фронт 121 син регистра обратной связи.55хросигнала выдачи на выводе 88.И тече- На фиг,.6 представлен пример парал.ние синхросигнала выдачй проиасодит. вы- лельно-последовательного построения блодача кода микрокоманды через выходные ка микропрограммного управления на трехусилители 80 считывания на выводы 84, устройствах 122-124, Выводы 73 и 8967402517 1892 устройства 122 объединены с входной По информационной магистрали в блок магистралью, по которой поступает в блок микропрограммного управления поступает командная информация с признаком, идеН-, командная информация, декодируемая в тифицирующим ее наличие во времени,Обье этом блоке в последовательность микрокодиненные выводы 74, 93, 94 и 96 уст- з манд, и принимается и выдается числовая ройств 122-124 объединень 1 с входной информация, обрабатываемая в процессормагисралью, по которой поступает в блок ном блоке. Выборка микрокоманцы в блоке информация для .внутренних условных пере микропрограммного управления совмещаевходов. Объединенные выводы 84 устройств, ся во времени с вйполнением предыдущей123 и 124 подключены к выходной мик омикрокоманды в пропессорном блоке. Код ., рокомайцной магистрали, На выводы 97,;прерывания, поступает на входы блока мик объединенйые в устройствах 123 и 124, , ропрограммного управления и принимается. поступает внешний сигнал (например, иэ,одновременно с командной информацией. процессорного блока), инициирующий цикл Введение блоков формирования рабоче- выборки микрокоманды, На вывод 100 в .1 го цикла и узлов автономного управления устройствах 123 и 124 подается логи- обменом позволяет при построении вычиоческий уровень, разрешающий считываниелительных систем снизить аппаратурные информации. Выводы 84 в устройствах,затраты на 10%, Этизатраты связаны с 123 и 124 объедйнены длясинхронйза, йостроением блоков синхронизации и уэции одновременной выдачи кода микроко 2 О лов организацииобмена. маем. Один из выводов 84, выводы 97 . . Так как время выполнения арифметии 100 устройства 122 подключены соот- ; ческихопераций в устройстве выполнения ветственно к выводам 90 92 устройств:операций зависит от кодов операндов, а 123 и 124.Остальные выводы 84 устрой-: ;также только. от собственных задержек,25ства 122 пойаочены к выводам 73 усл . то среднее время .выполнения операций для ройств 123, и 124. - : .процессорного блока разрядностью 16-32Код команды, поступившей на выводыуменьшается йа,15-25%, соответственно, . 73 устройства 122, разворачивается в: : по сравнению с иэвестййми микропроцео последовательность кодов, возйикаюаих насорными вычислиельными системами.ЗОвыводах 84 этого устройства. Кажжй изГибкая организация управления и сыэтйх кодов поступает в устройства:123 .:хрониэации в устройстве микропрограммнои.-12;4 разворачивается в последователь"го управления позволяет строить парадйость микрокоманд на объединенных ви-: . ,цельные" :последовательные и параллельно водах 84 этих устройств.": последовательныеблоки микропрограммно". 35На фиг. 7 представлен пример поетро- го управления с различными сйособами увеения микройроцессорной вычислительной;.лйчения объема микропрограмм, глубины . систеьйю, состоищей из одного процессор" .: микропоццрограмм,". разрядности микроконого блсжа 125 и блока 126 микропрог: .манд; что особенно важно для систем ко раммного управления. Процессорный блок . 4 мана языкового .уровня,. цо микрокомандной магистрали (выводы21 и 35) объединен с блоком микропрограммного уйравлений (выводы 84)при- : ф о р м у л а. и з о б р е те н и я чем объедйненные выводы 37 интегральных процессорных устройств в процессор-: Микропроцессорная вычислительная си ф45. ном блоке подключены к выводу 97 интег стема, содержащая однотипные устройства ральш 1 х устройств в блоке микропрограм" .выполнения ойераций и однотипные устрой- много управления, Магистраль состояний ства микропрограммного управления, при(выводы 28, 33 и 34) процессорного бло ,чем каждое однотипное устройство выпол ка обьединена с входной магистралью со- нения операций содержит арифметическостояний (выводы 74, 94 и 95) блока мик- логический блок, сдвигатель, регистр реропрограммного управления. Йве другие зультата, регистрсостояний, регистр микмагистрали процессорного блока подключе- рокоманд, дешифратор микроопераций, блоны к адресной и информационной магистра ки обмена информацией, подключенные к лям блоков ЗУ н бпоков; УВВ. Входная двунаправленным информационным шинам,командная магистраль (выводы 73, 90 и и блок регистров общего назначения, вьг) блока микропрограммного управления ход арифметическологического блока че-" обьединена с информационной магистралью реэ буферный регистр соединен о входом (выводы 23, 31 и 32). сдвигателя, вход регистра микрокомаид

СмотретьЗаявка

2170455, 22.09.1975

ПРЕДПРИЯТИЕ ПЯ Р-6429

ВАСЕНКОВ АЛЕКСАНДР АНАТОЛЬЕВИЧ, ДШХУНЯН ВАЛЕРИЙ ЛЕОНИДОВИЧ, МАШЕВИЧ ПАВЕЛ РОМАНОВИЧ, НЕСТЕРОВ ПЕТР ВЛАДИМИРОВИЧ, ТЕЛЕНКОВ ВЯЧЕСЛАВ ВИКТОРОВИЧ, ЧИЧЕРИН ЮРИЙ ЕГОРОВИЧ, ЮДИЦКИЙ ДАВЛЕТ ИСЛАМОВИЧ

МПК / Метки

МПК: G06F 15/16

Метки: вычислительная, микропроцессорная

Опубликовано: 15.07.1979

Код ссылки

<a href="https://patents.su/15-674025-mikroprocessornaya-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессорная вычислительная система</a>

Предыдущий патент: Устройство для контроля времени выполнения программы

Следующий патент: Устройство для управления распределением воды на полив

Случайный патент: Прибор для определения уровня жидкости в скважине