Модуль для вычисления булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

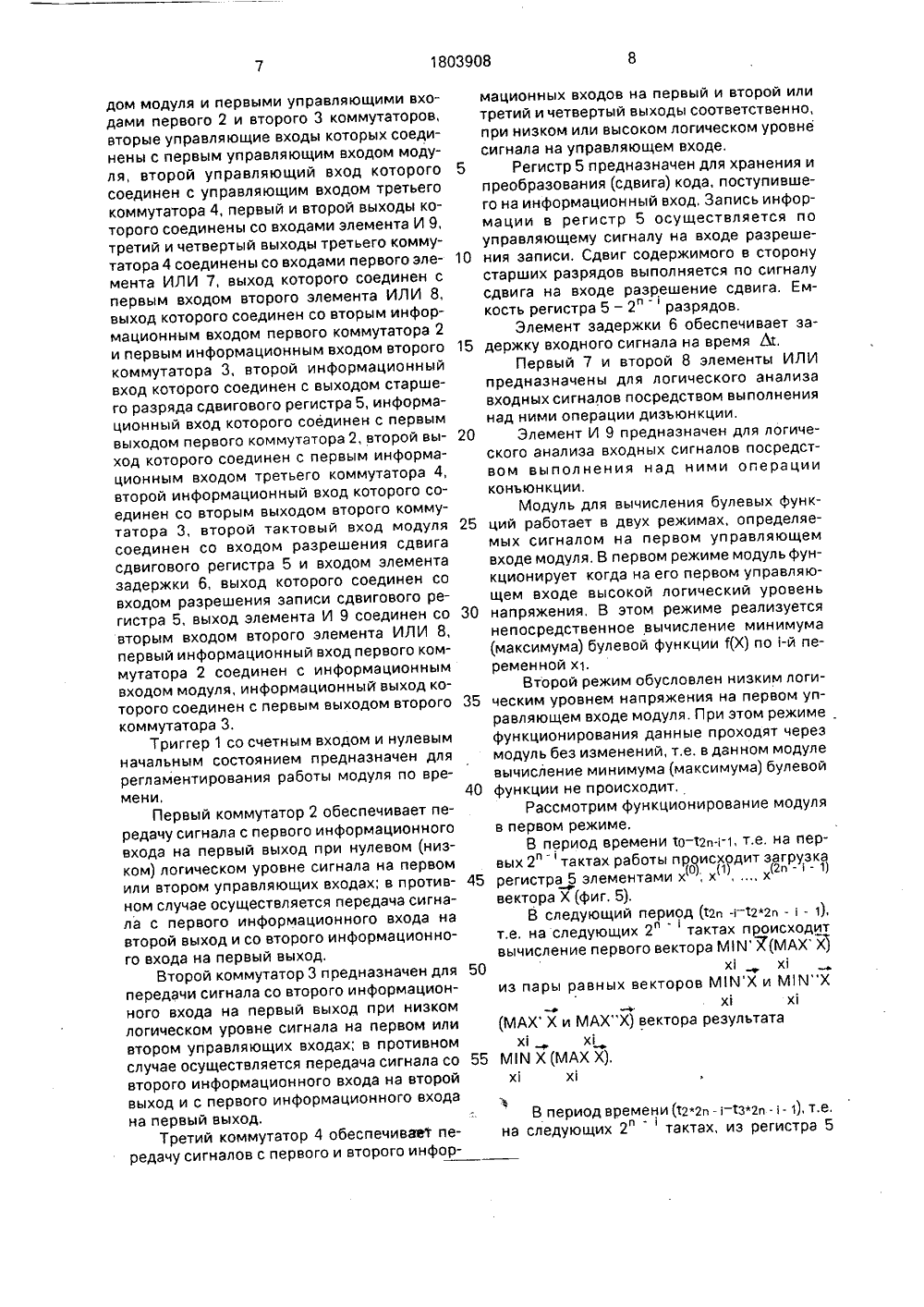

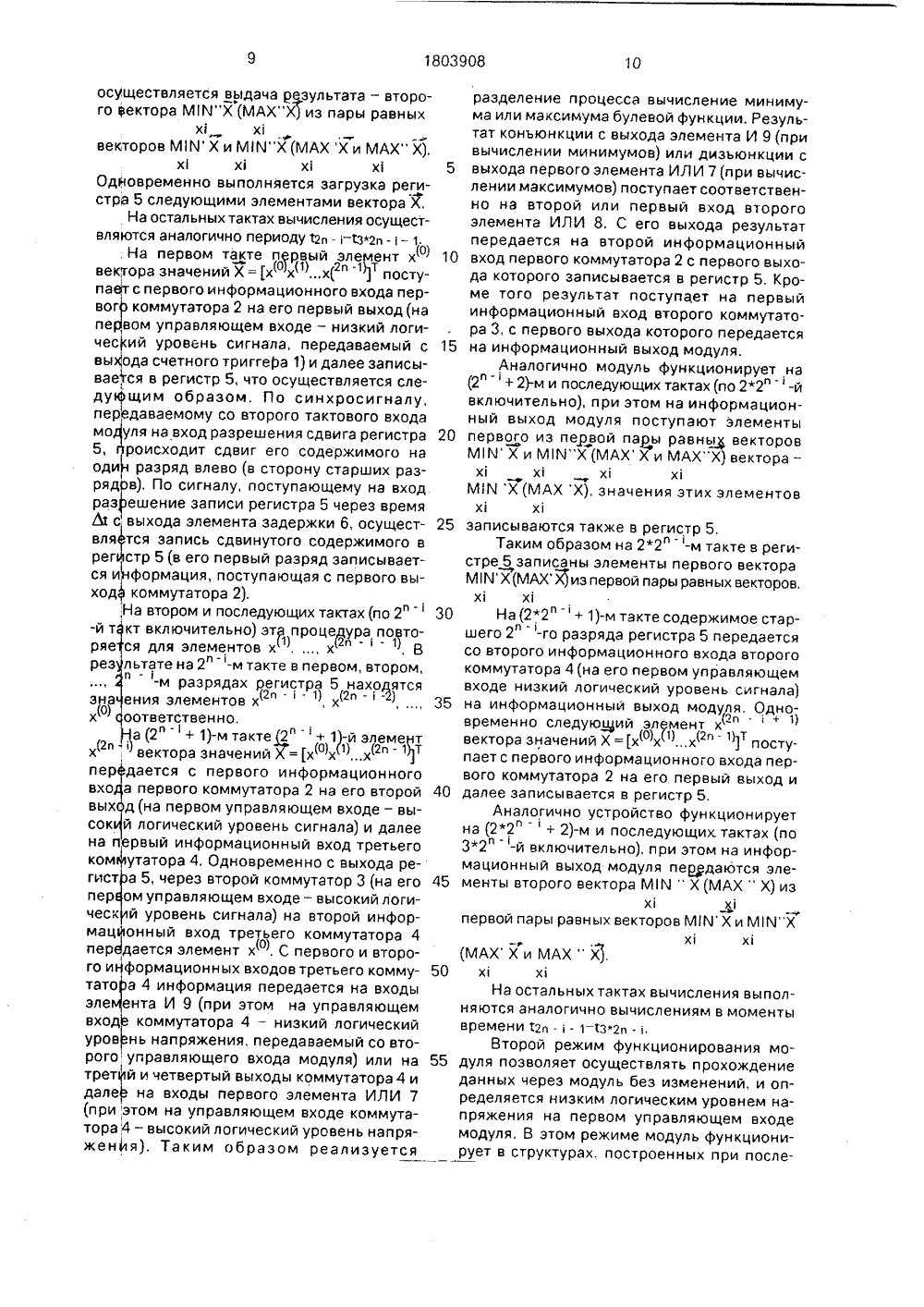

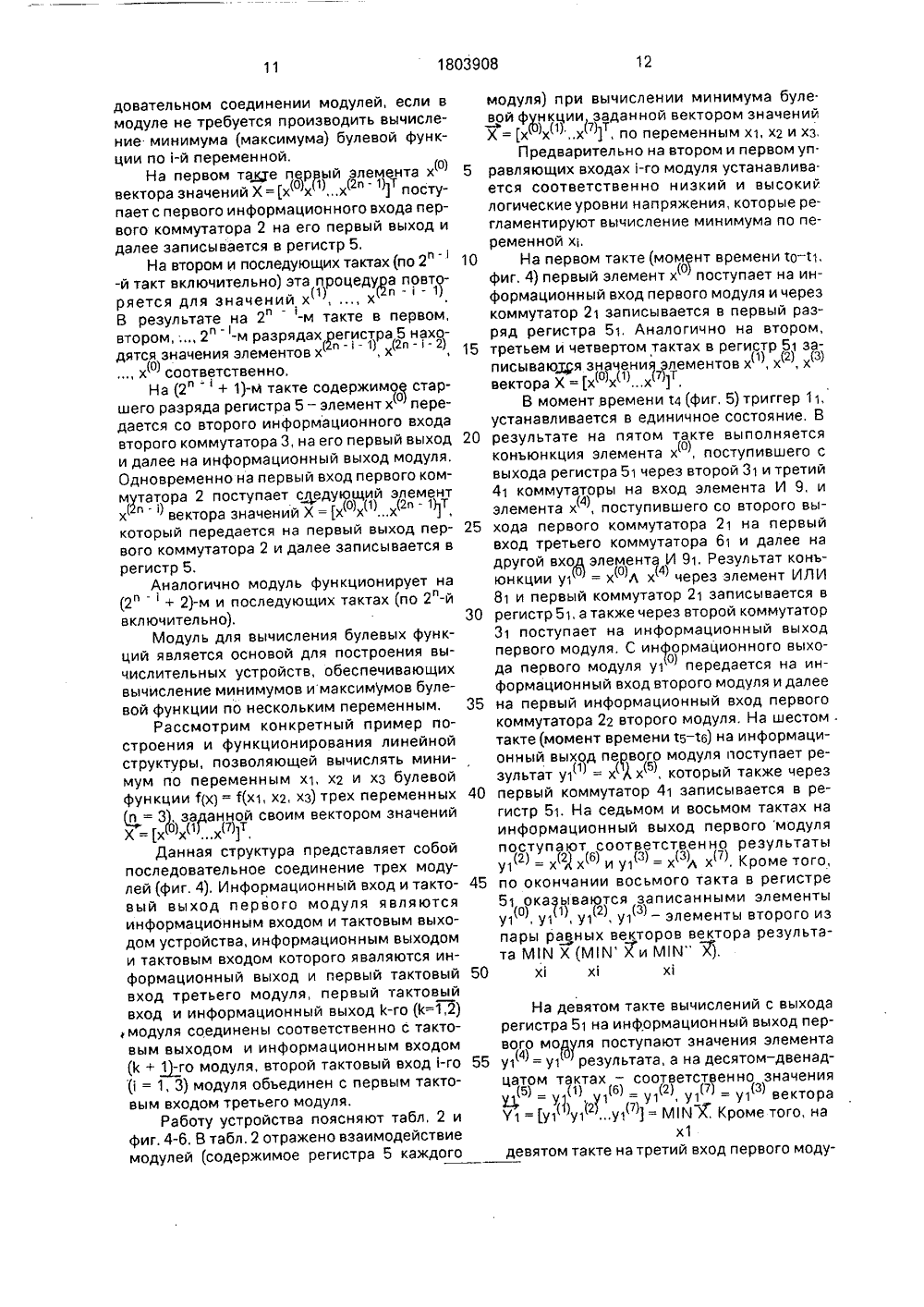

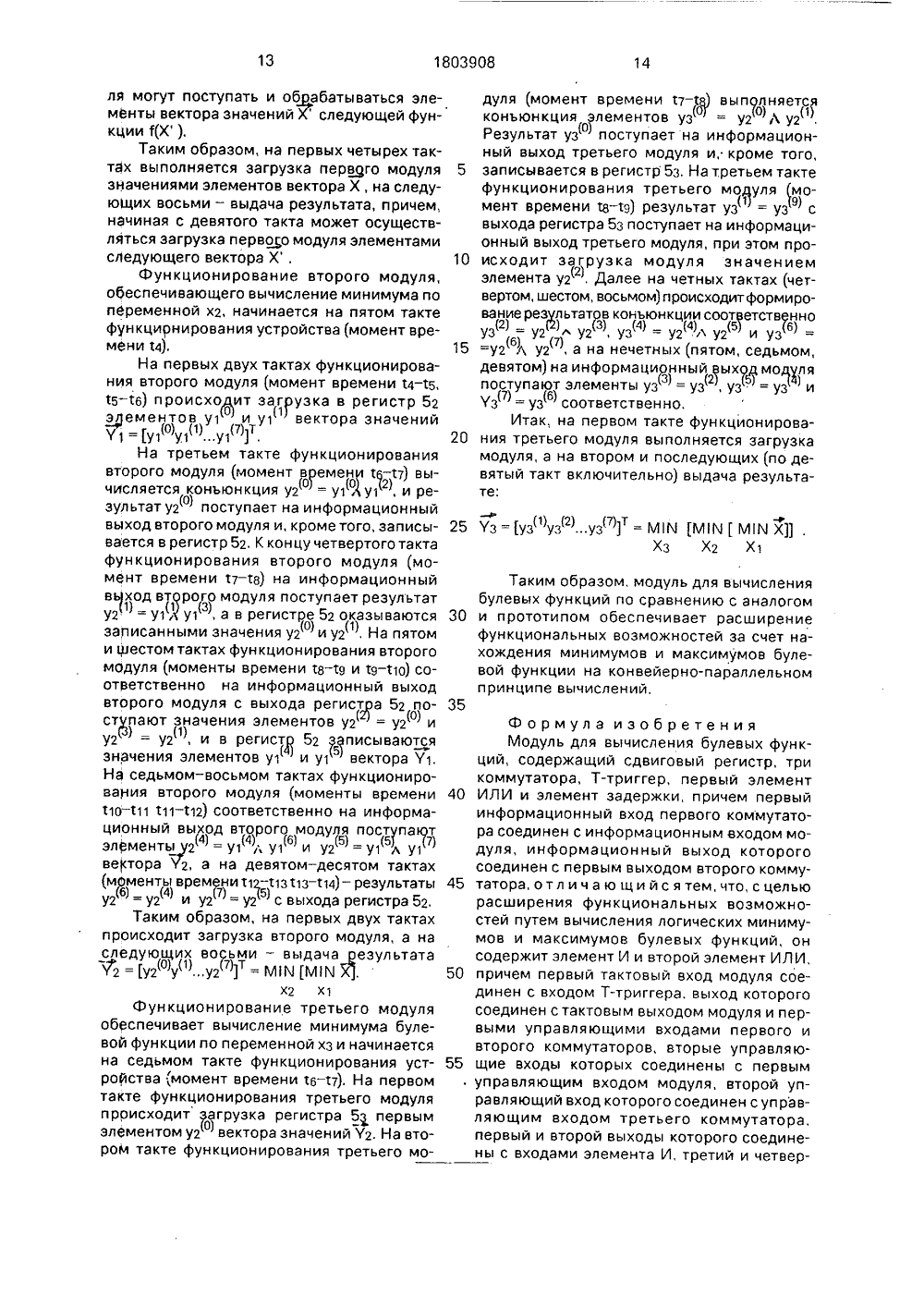

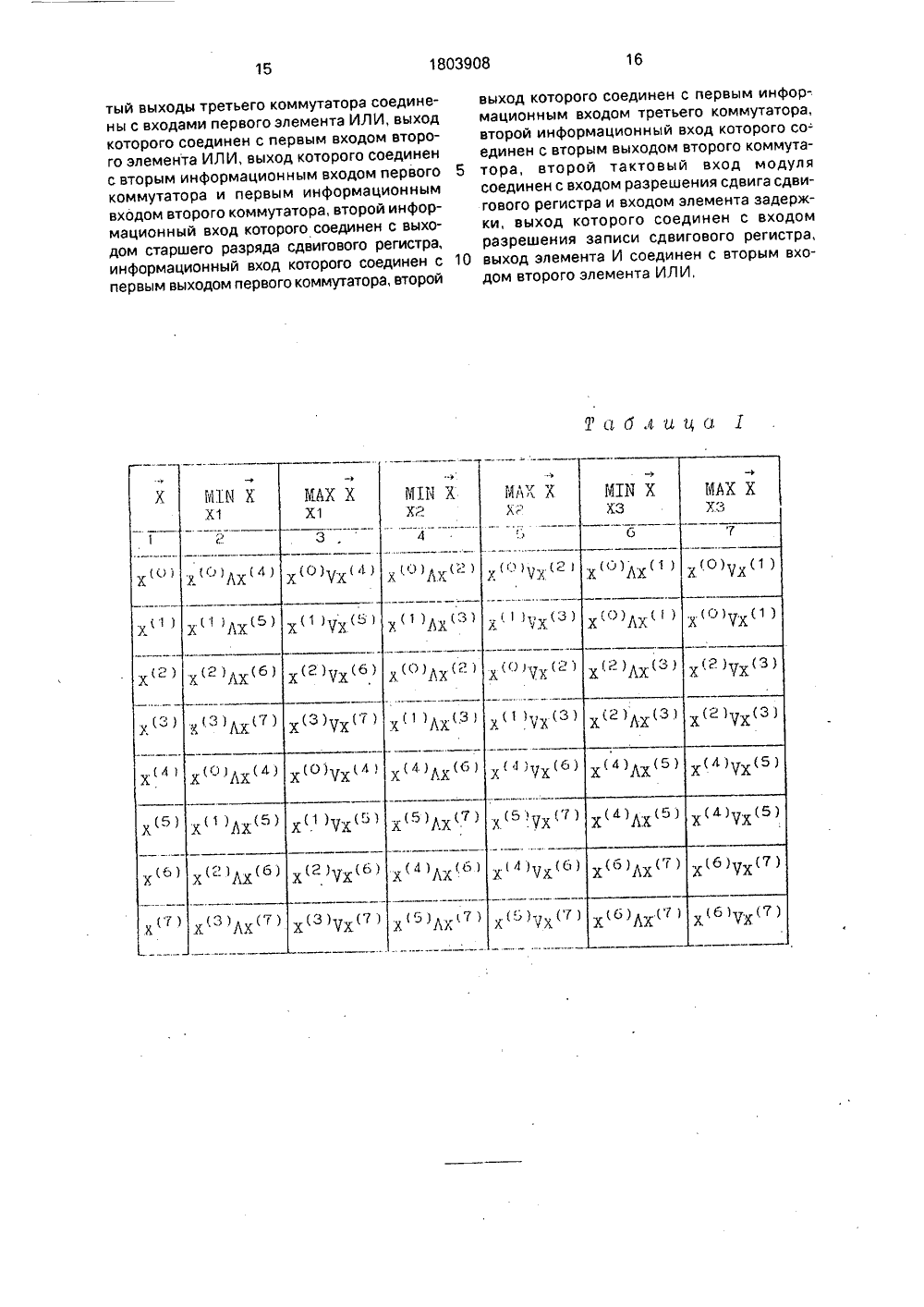

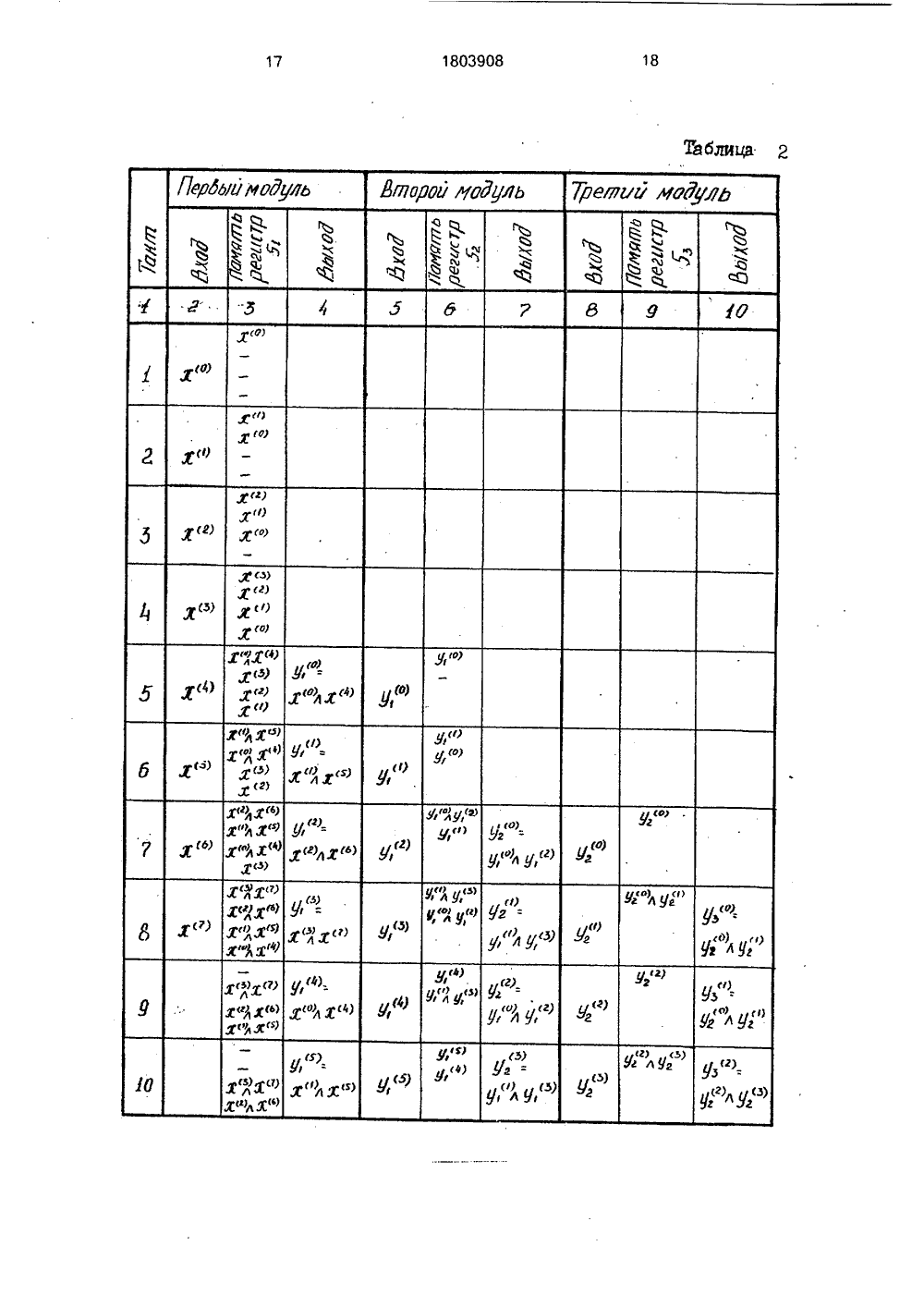

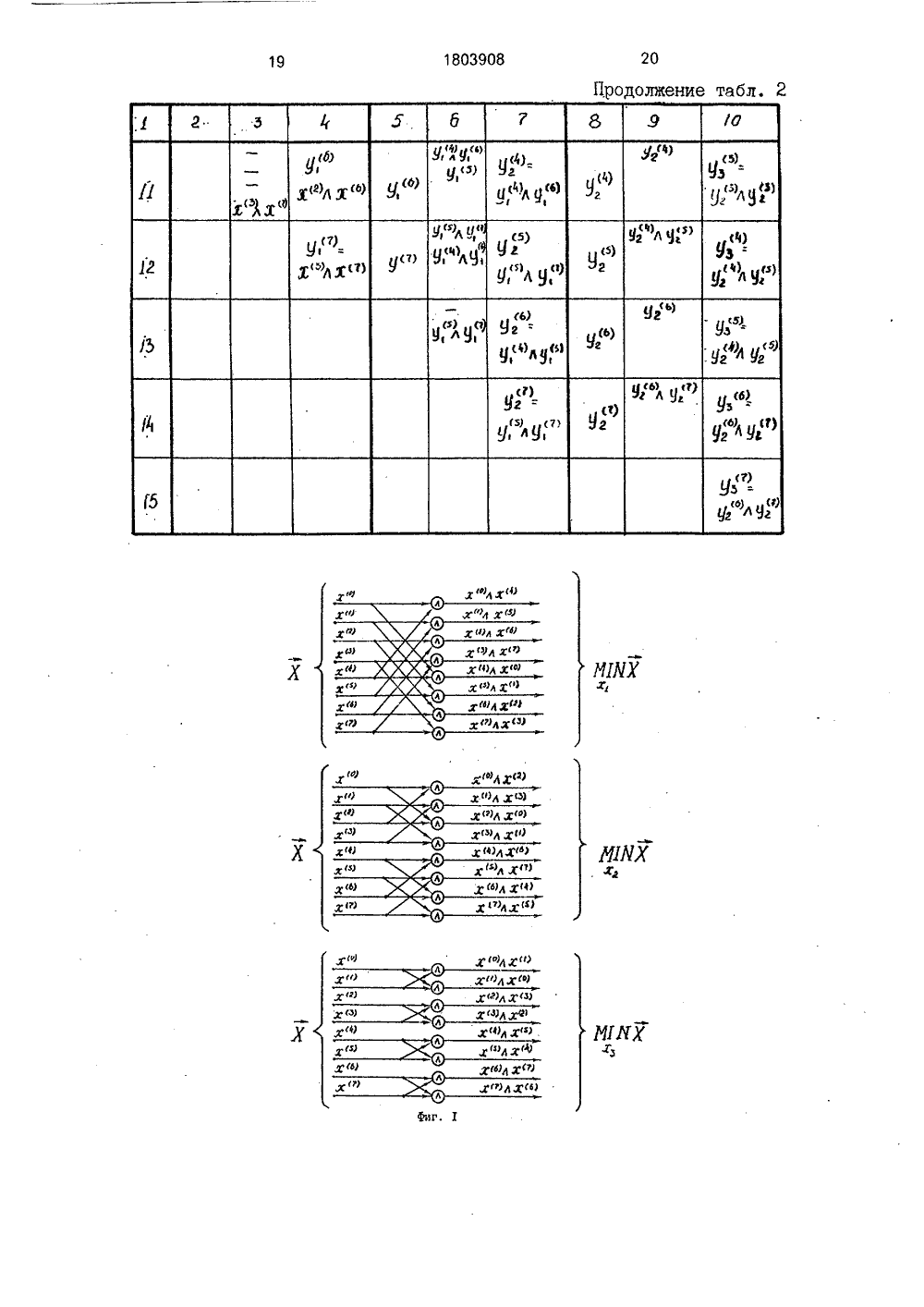

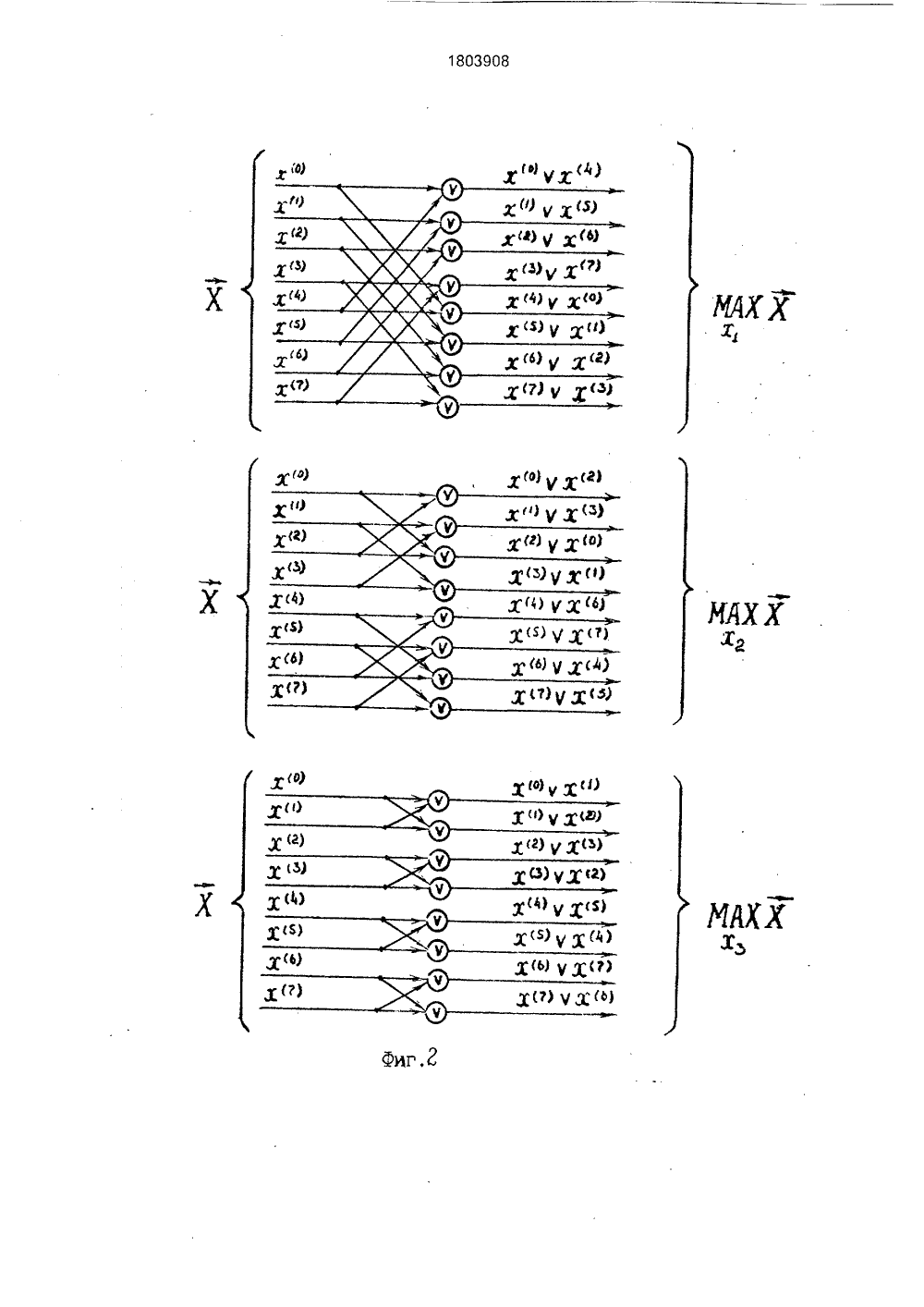

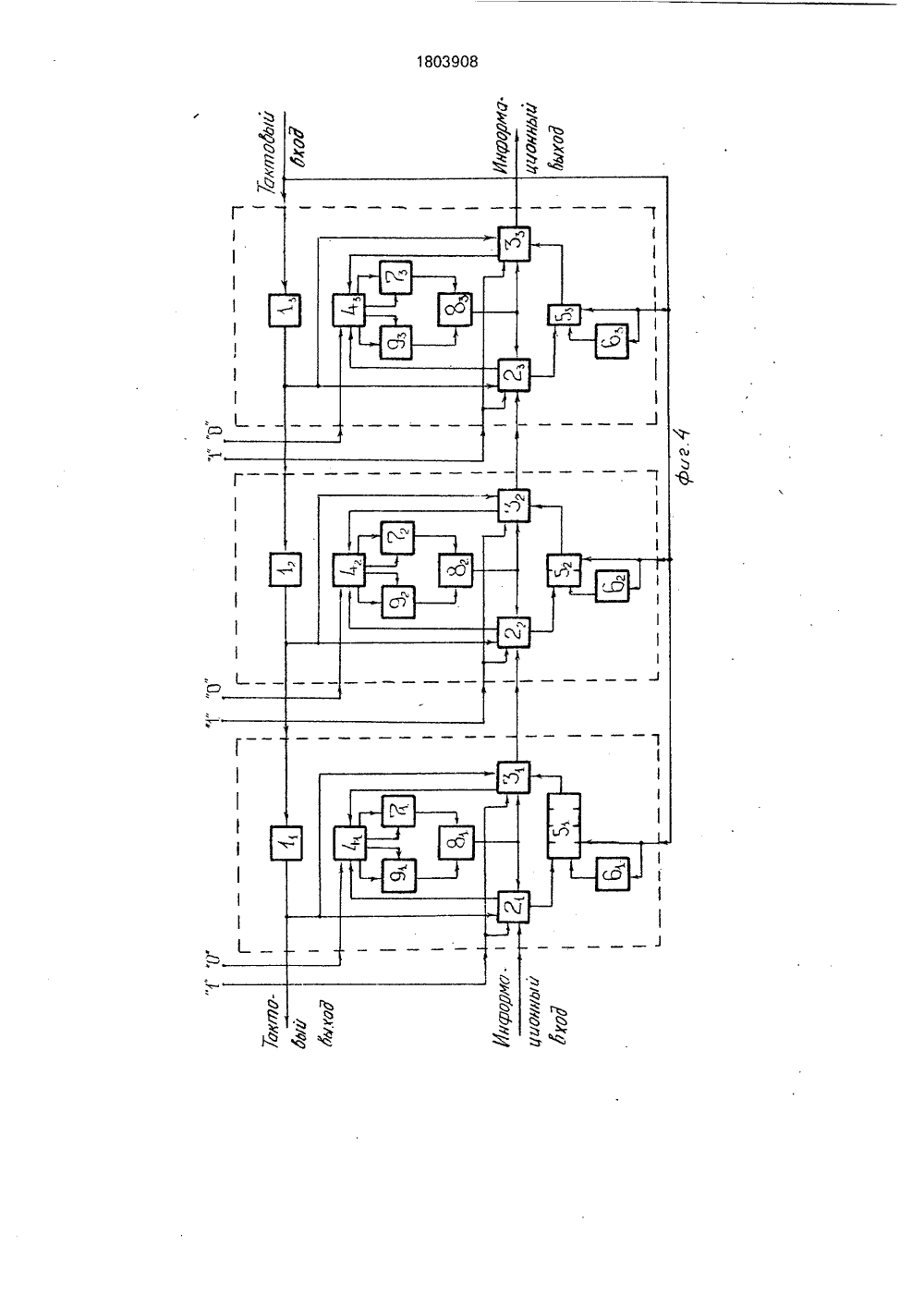

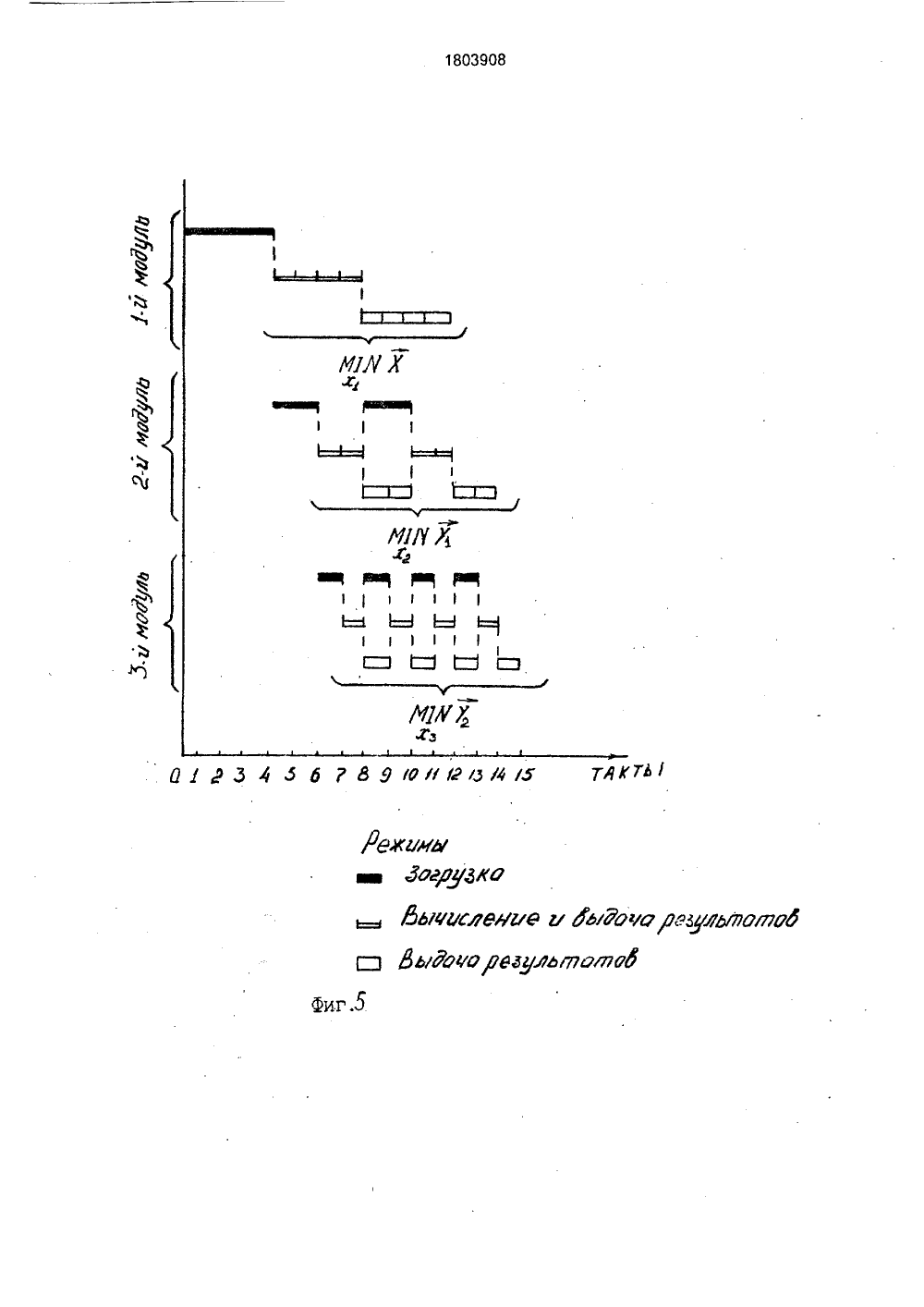

(51)5 6 06 Е 7/04 СА Т Б ЛЬ Т ехнический инс В,Г,Левашенко, отельство СССР Е 7/04, 19.05,89 тельство СССР Е 7/04, 11.10,89 ВЫЧИСЛЕНИЯ титут УЛ й вы- поль- ения относится цифрово нике и может быть и нова для постро 00 ение функройства за нимумов и,СОюиаЪ ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(57) Изобретениечислительной техзовано как ос Изобретение относится к области цифровой вычислительной техники и может бьТь использовано как основа для построения устройств аппаратной поддержки вычислений в системах автоматизированного анализа и синтеза цифровых автоматов, при их диагностике и контроле, в системах анализа и синтеза изображений, логического управления сложными объектами,Цель изобретения - расширциональных возможностей устсчет вычисления логических мимаксимумов булевых функций,Поставленная цель достигается тем, что в модуль для вычисления булевых функций, содержащий Т-триггер, первый, второй и третий коммутаторы, сдвиговый регистр, элемент задержки, первый элемент ИЛИ, причем первый информационный вход первого коммутатора соединен с информационЫ 1803908 А 1 устроиств аппаратнои поддержки вычислений в системах автоматизированного анализа и синтеза цифровых автоматов, при их диагностике и контроле, в системах анализа и синтеза изображений, логического управления сложными объектами, Цель изобретения - расширение функциональных возможностей устройства за счет вычисления логических минимумов и максимумов булевых функций. Цель достигается тем, что в модуль, содержащий Т-триггер, первый, второй и третий коммутаторы, сдвиговый регистр, элемент задержки, первый элемент ИЛИ, введены элемент И и второй элемент ИЛИ. б ил 2 табл,ным входом модуля, информационный выход которого соединен с первым выходом второго коммутатора, введены элемент И и второй элемент ИЛИ, причем первый тактовый вход модуля соединен со входом Т-триггера, выход которого соединен с тактовым выходом модуля и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с первым управляющим входом модуля, второй управляющий вход которого соединен с управляющим входом третьего коммутатора, первый и второй выходы которого соединены со входами элемента И, третий и четвертый выходы третьего коммутатора соединены со входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен со вторым информационным входом первого коммутатора и первым информаци,д л М) уГи Щ С 2 2 егиспр 5 преп Руля у(5) уГ 6) у ус 5) уй) Л витель С, Янушкевичд М.Моргентал Корректор Л Ливрин Редактор ванО Тираж ПодпиСтвенного комитета по изобретениям и отк113035, Москва, Ж, Раушская наб., 4 Го ГКНТ ССС иям/5 льский комбинат "Патент", г, Ужго л.Гагарина, 101 водственно-из аказ 1057 ВНИИ Со Те 0 а адйд111111 1111 1111 11 Вычисление минимума и максимума по переменной х 1 булевой функции 1(Х) = 25 =7(х 1,хг,хз) (и = 3) трех переменных,"1) (вг)(зе)м(4 о) (5) й) (7) т следующим образом:)и) х = ,з хх Что эквивалентно матричной форме записи:(2) 45 В табл. 1 приведены значения минимума и максимума булевой функции 1(Х) поПЕРЕМЕННЫМ Х 1, Х 2, ХЗ,50 Из табл, 1 видно, что результат вычисления минимума булевой функции трех перехрнных (и = 3), заданной вектором значенийХ, по переменной х 1 можно представить ввиде двух одинаковых векторов;55МХ = х(М х х(Я х(5) хЯ х 6 х(Ахи)х 1 Ма "Х = (хЯ х(4) хЩх(5) х(г,(6) (З),7)Т х 1 онным входом второго коммутатора, второй информационный вход которого соединен с выходом старшего разряда сдвигового регистра, информационный вход которого соединен с первым выходом первого коммутатора, второй выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен со вторым выходом второго коммутатора, второй тактовый вход модуля соединен со входом разрешения сдвига сдвигового регистра и входом элемента задержки, выход которого соединен со входом разрешения записи сдвигового регистра, выход элемента И соединен со вторым входом второго элемента ИЛИ.Суть данного изображения заключается в реализации вычислений логических минимумов и максимумов бинарных данных на однородных компонентах,В основу изобретения положены следующие математические модели функционирования компонентов и модуля в целом.Операторы логического минимума и максимума булевой функции т(Х) = т(х 1, хг, хп) п переменных по -й переменной х определяются соответственно соотношениями; МАХ т(Х) = т(х 1, , х), ., хп) Ч(х 1х)хп) х где Х - вектор значений булевой функции1(Х) (столбец обычной таблицы истинности,интерпретируемь(й как вектор бинарныхданных; Х = (х( )х(1) х(гп 1 т)02 П - МатрИца раЗМЕрНОСтИ 2 п Х 2", фсрМИруемая по соотношениюРгп=2 Э 11), (3) ГДЕ 2) -1 И 2 п - ( ЕДИНИЧНЫЕ МатРИЦЫ РаЗМЕР- настей 2 - 1 х 2 - 1 и 2 п -х 2 п- соответственно;- символ кронекеровского произведения матриц, В выражении (1) вместо опе ации сложения при умножении вектора на матрицу 0 и необходимо выполнять операцию конъюнкцию а в (2)дизъюнкциючто указано справа от фор-,мул,25 30 М 1 К ы Х = х(4) х(5) хз МАХ (х 1 хгъхз) = хгмхз.х 1 40 рармерности 2 каждый (в общем случае для функции п переменных эти два вектора имеют размерность 2" "). В результате вычисления минимума булевой функции по втОрой -еременной хг можно выделить четыре вектора; М 1 К Х = х(о 1 х(г) ХЯ х(з)т хг(о) (г) (1 л 1 (з)тХ 2Мф" Х = хфхф х(ЯХ 7)Х 2 М 14Х = =х(4), (б) ХЯ х(7)Храамериссти 2 кахкдыи (а общем саукае1размерность каждого из четырех вектороврана 2" ), причем два из этих векторовпо 1 арно равны, т,е,1Ма х= ма" х и ма" х= ма х)х 2 х 2 х 2 хг Аналогично для оператора нахождения минимума по переменной хз;мпг х = х(оЬ(1), ма" х = х(о), (1)т,хз хзМ 11 Х(2) (з)т МК,(гд (з) тхз хзМ 1 Ь Х = х х)Х МЙ "Х =(е х(тт М (С ф " Х = хщ х(тт хз хз Здесь выделены восемь векторов размерности 2 каждый (в общем случае 2" ), приоэто(1 попарно уавны следующие вектора: м 1 к, х = ма "х, м 1 к" х = м 1 к Г М 1 К" Х = М 1 К Х, М 1 К" "Х = М 1 К" "Х,хз хз хз Аналогичные результаты получаются при вычислении максимума булевой функции о переменной х;( = 1 и) (табл. 1),Таким образом, искомый результат, т,е, вектор минимаксной операции по 1-1 переменнойй М 1 К Х (МАХ Х) состоит их 2 векторовх 1 хразм(ертотси 2"каждый, среди которых имефтся попарно равные, Следовательно необходимо вычислять только один вектор из пр. Пусть требуется вычислить минимум имаксимум по переменной х булевой функции 1(Х) = Х 1 хгъ хз трех (и = 3) переменных, Вектор значений булевой функции имеет 5 вид Х = 0101 0111 . В соответствии с матетматическими моделями (1) и (2) определим минимум и максимум булевой функции х 1 х 2(хз по переменной х: По векторам значений МК Х 0101 0101 иее Х 1МАХ Х = 0111 0111 строим их аналитичехские выражения; 35 М 1 К (Х 1 хггхз) = х 2 хзХ На фиг. 1 и 2 представлены операционные графы алгоритма реализации математической модели (1) и (2): на фиг, 3структурная схема модуля; на фиг, 4 - струк 45 тура, позволяющая вычислять логическийминимум булевой функции 1(Х) трех переменных; на фиг. 5 - диаграмма функционирования этой структуры; на фиг, б - процессвычисления логического минимума булевой50 функции(л = 3) переменных,Модуль (фиг, 3) содержит Т-триггер 1,первый 2, второй 3 и третий 4 коммутаторы,сдвиговый регистр 5, элемент задержки б,первый 7 и второй 8 элементы ИЛИ, элемент55 И 9, два тактовых входа 10 и 11, два управляющих входа 12 и 13, информационныйвход 14, информационный выход 15, тактовый выход 16, причем первый тактовый входмодуля соединен со входом Т-триггера 1,выход которого соединен с тактовым выхо 1803908дом модуля и первыми управляющими входами первого 2 и второго 3 коммутаторов, вторые управляющие входы которых соединены с первым управляющим входом модуля, второй управляющий вход которого соединен с управляющим входом третьего коммутатора 4, первый и второй выходы которого соединены со входами элемента И 9, третий и четвертый выходы третьего коммутатора 4 соединены со входами первого элемента ИЛИ 7, выход которого соединен с первым входом второго элемента ИЛИ 8, выход которого соединен со вторым информационным входом первого коммутатора 2 и первым информационным входом второго коммутатора 3, второй информационный вход которого соединен с выходом старшего разряда сдвигового регистра 5, информационный вход которого соединен с первым выходом первого коммутатора 2, второй выход которого соединен с первым информационным входом третьего коммутатора 4, второй информационный вход которого соединен со вторым выходом второго коммутатора 3, второй тактовый вход модуля соединен со входом разрешения сдвига сдвигового регистра 5 и входом элемента задержки 6, выход которого соединен со входом разрешения записи сдвигового регистра 5, выход элемента И 9 соединен со вторым входом второго элемента ИЛИ 8, первый информационный вход первого коммутатора 2 соединен с информационным входом модуля, информационный выход которого соединен с первым выходом второго коммутатора 3.Триггер 1 со счетным входом и нулевым начальным состоянием предназначен для регламентирования работы модуля по времени,Первый коммутатор 2 обеспечивает передачу сигнала с первого информационного входа на первый выход при нулевом (низком) логическом уровне сигнала на первом или втором управляющих входах; в противном случае осуществляется передача сигнала с первого информационного входа на второй выход и со второго информационного входа на первый выход,Второй коммутатор 3 предназначен для передачи сигнала со второго информационного входа на первый выход при низком логическом уровне сигнала на первом или втором управляющих входах; в противном случае осуществляется передача сигнала со второго информационного входа на второй выход и с первого информационного входа на первый выход,Третий коммутатор 4 обеспечивает передачу сигналов с первого и второго инфор 5 10 15 20 25 30 35 40 45 50 55 мационных входов на первый и второй илитретий и четвертый выходы соответственно,при низком или высоком логическом уровнесигнала на управляющем входе.Регистр 5 предназначен для хранения ипреобразования (сдвига) кода, поступившего на информационный вход, Запись информации в регистр 5 осуществляется поуправляющему сигналу на входе разрешения записи. Сдвиг содержимого в сторонустарших разрядов выполняется по сигналусдвига на входе разрешение сдвига. Емкость регистра 5 - 2"разрядов.Элемент задержки 6 обеспечивает задержку входного сигнала на время Ж,Первый 7 и второй 8 элементы ИЛИпредназначены для логического анализавходных сигналов посредством выполнениянад ними операции дизъюнкции,Элемент И 9 предназначен для логического анализа входных сигналов посредством выполнения над ними операцииконъюнкции,Модуль для вычисления булевых функций работает в двух режимах, определяемых сигналом на первом управляющемвходе модуля. В первом режиме модуль функционирует когда на его первом управляющем входе высокой логический уровеньнапряжения, В этом режиме реализуетсянепосредственное вычисление минимума(максимума) булевой функции 1(Х) по -й переменной х 1Второй режим обусловлен низким логическим уровнем напряжения на первом управляющем входе модуля. При этом режимефункционирования данные проходят черезмодуль без изменений, т,е. в данном модулевычисление минимума (максимума) булевойфункции не происходит,Рассмотрим функционирование модуляв первом режиме,В период времени то-т 2 м, т.е, на первых 2"тактах работы происходит загрузкарегистра 5 элементами х, х 1, ., х "вектора Х (фиг, 5).В следующий период (тгп -гтгп -- ),т,е. на следующих 2"тактах происходитвычисление первого вектора ММ Х(МАХ Х)х хиз пары равных векторов МйХ и ММ"Хх х(МАХ Х и МАХ" Х) вектора результатах хМй Х (МАХ Х),х х В период времени (т 22 п - -132 п -- 1), т,е,на следующих 2"тактах, из регистра 5о существляется выдача результата - второго вектора М 1 М "Х (МАХ"ХТиз пары равныхх х векторов М 1 М Х и МЮ "Х (МАХ Х и МАХ" Х),х 1 х х х 5 Одйовременно выполняется загрузка регистра 5 следующими элементами вектора Х,На остальных тактах вычисления осуществляются аналогично периоду т 2 п -- з 2 п - -1.На первом такте первый элемент х у 10 вектора значений Х = (ху хх(2" 1)т посупает с первого информационного входа первог коммутатора 2 на его первый выход(на первом управляющем входе - низкий логический уровень сигнала, передаваемый с 15 выХода счетного триггера 1) и далее записываеТся в регистр 5, что осуществляется следующим образом. По синхросигналу, перйдаваемому со второго тактового входа мо уля на вход разрешения сдвига регистра 20 5, роисходит сдвиг его содержимого на одав разряд влево (в сторону старших разряд в), По сигналу, поступающему на вход раз ешение записи регистра 5 через время Ж с выхода элемента задержки 6, осущест вля тся запись сдвинутого содержимого в рег стр 5 (в его первый разряд записывается информация, поступающая с первого выход коммутатора 2).На втором и последующих тактах(по 2" 30 -й т кт включительно) эта процедура порторяе ся для элементов х , , х ", В рез льтате на 2" -м такте в первом, втором,-м разрядах регистра 5 наход 2 ятся зна ения элементов х " У, х( "),35 хи оответственно,а (2" + 1)-м такте 2" + 1)-й элемент х " У вектора значений Х = хУ Ух У.х( " пер дается с первого информационного вхо а первого коммутатора 2 на его второй 40 вых д(на первом управляющем входе - высок й логический уровень сигнала) и далее на первый информационный вход третьего ком 1 утатора 4, Одновременно с выхода регист а 5, через второй коммутатор 3 (на его 45 пер омуправляющем входе - высокийлогическ й уровень сигнала) на второй информац 1 онный вход третьего коммутатора 4 передается элемент х 1. С первого и второ(о) го иНформационных входов третьего комму татора 4 информация передается на входы элемента И 9 (при этом на управляющем входв коммутатора 4 - низкий логический уровень напряжения, передаваемый со второгоуправляющего входа модуля) или на 55 трет 1 й и четвертый выходы коммутатора 4 и дале на входы первого элемента ИЛИ 7 (приэтом на управляющем входе коммутатора 4 - высокий логический уровень напряженйя). Таким образом реализуется разделение процесса вычисление минимума или максимума булевой функции. Результат конъюнкции с выхода элемента И 9 (при вычислении минимумов) или дизъюнкции с выхода первого элемента ИЛИ 7(при вычислении максимумов) поступает соответственно на второй или первый вход второго элемента ИЛИ 8. С его выхода результат передается на второй информационный вход первого коммутатора 2 с первого выхода которого записывается в регистр 5, Кроме того результат поступает на первый информационный вход второго коммутатора 3, с первого выхода которого передается на информационный выход модуля.Аналогично модуль функционирует на (2" +2)-ми последующихтактах(по 22" -й включительно), при этом на информационный выход модуля поступают элементы первого из первой пары равны; векторов М 11 у Х и М 1 М"Х (МАХ Х и МАХ"Х) вектора - х х х хМ 1 М Х (МАХ Х), значения этих элементов х хзаписываются также в регистр 5.Таким образом на 22" -м такте в регистре 5 записаны элементы первого вектора МЯХ(МАХ Х) из первой пары равных векторов,х х 1На (2 у 2" + 1)-м такте содержимое старшего 2" -го разряда регистра 5 передается со второго информационного входа второго коммутатора 4(на его первом управляющем входе низкий логический уровень сигнала) на информационныи выход модуля, Одновременно следующий элемент х(2"векторазначенийХ=(х х ух" ) поступает с первого информационного входа первого коммутатора 2 на его. первый выход и далее записывается в регистр 5,Аналогично устройство функционирует на (22" + 2)-м и последующих тактах (по 32" -й включительно), при этом на информационный выход модуля пеоедаются элементы второго вектора М М " Х (МАХ " Х) изх х первой пары равных векторов М й Х и М 1 М "Хх х (МАХ Х и МАХ " Х.х хНа остальных тактах вычисления выполняются аналогично вычислениям в моментыВРЕМЕНИ 12 п --1 - тз 2 п - ЬВторой режим функционирования модуля позволяет осуществлять прохождение данных через модуль без изменений, и определяется низким логическим уровнем напряжения на первом управляющем входе модуля, В этом режиме модуль функционирует в структурах. построенных при после 1803908 12довательном соединении модулей, если вмодуле не требуется производить вычисление минимума (максимума) булевой функции по)-й переменной,На первом тауе первый элемента хвектора значений Х= хфхф,х(2" 1)т поступает с первого информационного входа первого коммутатора 2 на его первый выход идалее записывается в регистр 5,На втором и последующих тактах(по 2"-й такт включительно) эта процедура повто)ряется для значений х(1),хВ результате на 2" -м такте в первом,втором,; 2" -м разрядах 2 оегистра 5 находятся значения элементов х( "1), х(2"х( ) соответственно,На (2" + 1)-м такте содержимое старшего разряда регистра 5 - элемент х( пере(0)дается со второго информационного входавторого коммутатора 3, на его первый выходи далее на информационный выход модуля,Одновременно на первый вход первого комму 2 татора 2 поступает сгедудщий элементх( " ) вектора значений Х = х )х( )х( "который передается на первый выход первого коммутатора 2 и далее записывается врегистр 5.Аналогично модуль функционирует на(2" + 2)-м и последующих тактах (по 2"-йвключительно).Модуль для вычисления булевых функций является основой для построения вычислительных устройств, обеспечивающихвычисление минимумов и максимУмов булевой функции по нескольким переменным,Рассмотрим конкретный пример построения и функционирования линейнойструктуры, позволяющей вычислять минимум по переменным х 1, х 2 и хз булевойфункции 1(х) = 1(х 1, х 2, хз) трех переменных(и = 3), заданной своим вектором значенийХ = х(0)х(1 .х(7 тДанная структура представляет собойпоследовательное соединение трех модулей (фиг. 4), Информационный вход и тактовый выход первого модуля являютсяинформационным входом и тактовым выходом устройства, информационным выходоми тактовым входом которого яваляются информационный выход и первый тактовыйвход третьего модуля, первый тактовыйвход и информационный выход К-го (1=1 2)модуля соединены соответственно с тактовым выходом и информационным входом(К + 1-го модуля, второй тактовый вход 1-гоф = 1, 3) модуля объединен с первым тактовым входом третьего модуля.Работу устройства поясняют табл, 2 ифиг. 4-6, В табл, 2 отражено взаимодействиемодулей (содержимое регистра 5 каждого5 10 15 20 25 30 35 40 45 50 На девятом такте вычислений с выхода регистра 51 на информационный выход первого морля поступают значения элемента у 1( ) = у 1 результата, а на десятом - двенад(4)цатом тактах - соответственно значения(5) (1) (5) (2) (7) (3) У 1=у 1у 1(,у 1( = Мй Г Кроме того, нах 1девятом такте на третий вход первого моду 55 модуля) при вычислении минимума буле.вой функции заданной вектором значенийХ = х(0)х( )х( , по переменным х 1, х 2 и хз,Предварительно на втором и первом уп.равляющих входах -го модуля устанавливается соответственно низкий и высокийлогические уровни напряжения, которые регламентируют вычисление минимума по переменной хьНа первом такте (момент времени т 0 - й 1,фиг. 4) первый элемент х поступает на ин(0)формационный вход первого модуля и черезкоммутатор 21 записывается в первый разряд регистра 51, Аналогично на втором,третьем и четвертом тактах в регистр 51 записывают:я значени) элементов х ), х( ), х )вектора Х = х(0 хх) г,В момент времени 14 (фиг, 5) триггер 11,устанавливается в единичное состояние, Врезультате на пятом такте выполняетсяконъюнкция элемента х, поступившего с(0)выхода регистра 51 через второй 31 и третий41 коммутаторы на вход элемента И 9, иэлемента х, поступившего со второго выхода первого коммутатора 21 на первыйвход третьего коммутатора 61 и далее надругой вхо(0 д элемента И 91, Результат коньюнкции у 1 = хЛ х через элемент ИЛИ(О) (4)81 и первый коммутатор 21 записывается врегистр 51, а также через второй коммутатор31 поступает на информационный выходпервого модуля. С информационного выхода первого модуля у 1 ) передается на инО)формационный вход второго модуля и далеена первый информационный вход первогокоммутатора 22 второго модуля. На шестом .такте(момент времени с 5 - т 5) на информационный выхо)д первого модуля поступает результат у 1( = х(Ах, который также черезпервый коммутатор 41 записывается в регистр 51. На седьмом и восьмом тактах наинформационный выход первого модуляпоступают соответственно результатыу 1 = хх и у 1 = х л х, Кроме того,по окончании восьмого такта в регистре51 оказываются записанными элементыу 1( , у 1 , у 1, у 1 ) - элементы второго из(0 11 (21 (3)пары равных векторов вектора результата М)й Х (М 1 М Ки Мй" 7).х х х)ля могут поступать и обоабатываться элементы вектора значений Х следующей функции тХ ).Таким образом, на первых четырех тактах выполняется загрузка первго модуля 5значениями элементов вектора Х, на следующих восьми - выдача результата, причем,начиная с девятого такта может осуществляться загрузка первого модуля элементамиследующего вектора Х, 10Функционирование второго модуля,обеспечивающего вычисление минимума попеременной х 2, начинается на пятом тактефункционирования устройства момент времЕни 14). 15На первых двух тактах функционирования второго модуля момент времени 14 - 15,т 5 - с 5) происходит заг)оузка в регистр 52э)ементов у 1 и у 1( вектора значений0 (1т 1= У 1( )У 1( )У 1( ) . 20На третьем такте функционированиявторого модуля момент времени с - с 7) вычисляется конъюнкция уг = У 1.лу 1, и результат уг поступает на информационный(о)выход второго модуля и, кроме того, записывается в регистр 52, К концу четвертого тактафункционирования второго модуля (момент времени 17 - тв) на информационныйвыход второго модуля поступает результату 2 = у 1 Я У 1(, а в регистре 52 оказываются 30записанными значения у 2( и у 2( ). На пятом(0) (1)и фестом тактах функционирования второгомодуля моменты времени тв - т 9 и т 9 - 110) соответственно на информационный выходвторого модуля с выхода регистра 52 поступают значения элементов уг = у 2 и,5,- мзначения элементов у 1("у и у 1вектора у 1.На седьмом - восьмом тактах функционирова-сия второго модуля (моменты времени 40110 - т 11 111 - 112) соответственно на информационный выход второго модуля поступактэлрменть 2(4) у(4) У 1(6) и уг(5) = у 1(51 л у 1(7)веКтора г, а на девятом - десятом тактахмоменты времени т 12( - т 1 з т 1 з - т 14) - результаты 45У 2 ) =У 2 и У 2 =У 2 с выхода регистра 52,(4) 7) 5)Таким образом, н а первых двух тактахпроисходит загрузка второго модуля, а наследующих восьми - выдача результатаГ 2 = У 2 У У 2= Му) ММ 5(. 50Х 2 Х 1Функционирование третьего модуляобеспечивает вычисление минимума булевой функции по переменной хз и начинаетсяна седьмом такте функционирования устройства,момент времени 15 - 17). На первомтакте функционирования третьего модуляпроисходит загрузка регистра 5 з первым(О)элвментом уг вектора значений Уг. На втором такте функционирования третьего модуля Гмомент времени тт-тф вылрлняетоаконъюнкция элементов уз( = уг )А уг( .(О)Результат уз( ) поступает на информационный выход третьего модуля и, кроме того,записывается в регистр 5 з. На третьем тактефункционирования третьего мок)уля (момент времени тв - т 9) результат уз( = уз ) с(1 9)выхода регистра 5 з поступает на информационный выход третьего модуля, при этом происходит загрузка модуля значениемэлемента УР, Далее на четных тактах четвертом, шестом, восьмом) происходит формирование результатрв конъюнкции соответственноУЗ У 2 уиуг УЗ У 2 улуг и УЗ(з) (гтз = уз( ) соответственно,Итак, на первом такте функционирования третьего модуля выполняется загрузкамодуля, а на втором и последующих по девятый такт включительно) выдача результате:Уз=узузуз = Мй М)М ММ ХХз Х 2 Х 1Таким образом, модуль для вычисления булевых функций по сравнению с аналогом и прототипом обеспечивает расширение функциональных возможностей за счет нахождения минимумов и максимумов булевой функции на конвейерно-параллельном принципе вычислений,Формула изобретения Модуль для вычисления булевых функций, содержащий сдвиговый регистр, три коммутатора, Т-триггер, первый элемент ИЛИ и элемент задержки, причем первый информационный вход первого коммутатора соединен с информационным входом модуля, информационный выход которого соединен с первым выходом второго коммутатора, о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей путем вычисления логических минимумов и максимумов булевых функций, он содержит элемент И и второй элемент ИЛИ, причем первый тактовый вход модуля соединен с входом Т-триггера, выход которого соединен с тактовым выходом модуля и первыми управляющими входами первого и второго коммутаторов, вторые управляющие входы которых соединены с первым управляющим входом модуля, второй управляющий вход которого соединен с управляющим входом третьего коммутатора, первый и второй выходы которого соединены с входами элемента И, третий и четвер(7 тый выходы третьего коммутатора соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, выход которого соединен с вторым информационным входом первого коммутатора и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом старшего разряда сдвигового регистра, информационный вход которого соединен с первым выходом первого коммутатора, второй выход которого соединен с первым информационным входом третьего коммутатора, второй информационный вход которого со- единен с вторым выходом второго коммута тора, второй тактовый вход модулясоединен с входом разрешения сдвига сдвигового регистра и входом элемента задержки, выход которого соединен с входом разрешения записи сдвигового регистра, 10 выход элемента И соединен с вторым входом второго элемента ИЛИ, 1803908

СмотретьЗаявка

4757265, 09.11.1989

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЯНУШКЕВИЧ СВЕТЛАНА НИКОЛАЕВНА, ЛЕВАШЕНКО ВИТАЛИЙ ГРИГОРЬЕВИЧ, МОРОЗОВА АННА АНАТОЛЬЕВНА, ШМЕРКО ВЛАДИМИР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 7/04

Метки: булевых, вычисления, модуль, функций

Опубликовано: 23.03.1993

Код ссылки

<a href="https://patents.su/15-1803908-modul-dlya-vychisleniya-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Модуль для вычисления булевых функций</a>

Предыдущий патент: Устройство для управления весовым порционным дозатором

Следующий патент: Устройство для упорядочения массива чисел

Случайный патент: Распылитель жидкости