Устройство для вычисления булевых дифференциалов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1777132

Авторы: Колодиева, Парамонова, Шмерко, Янушкевич

Текст

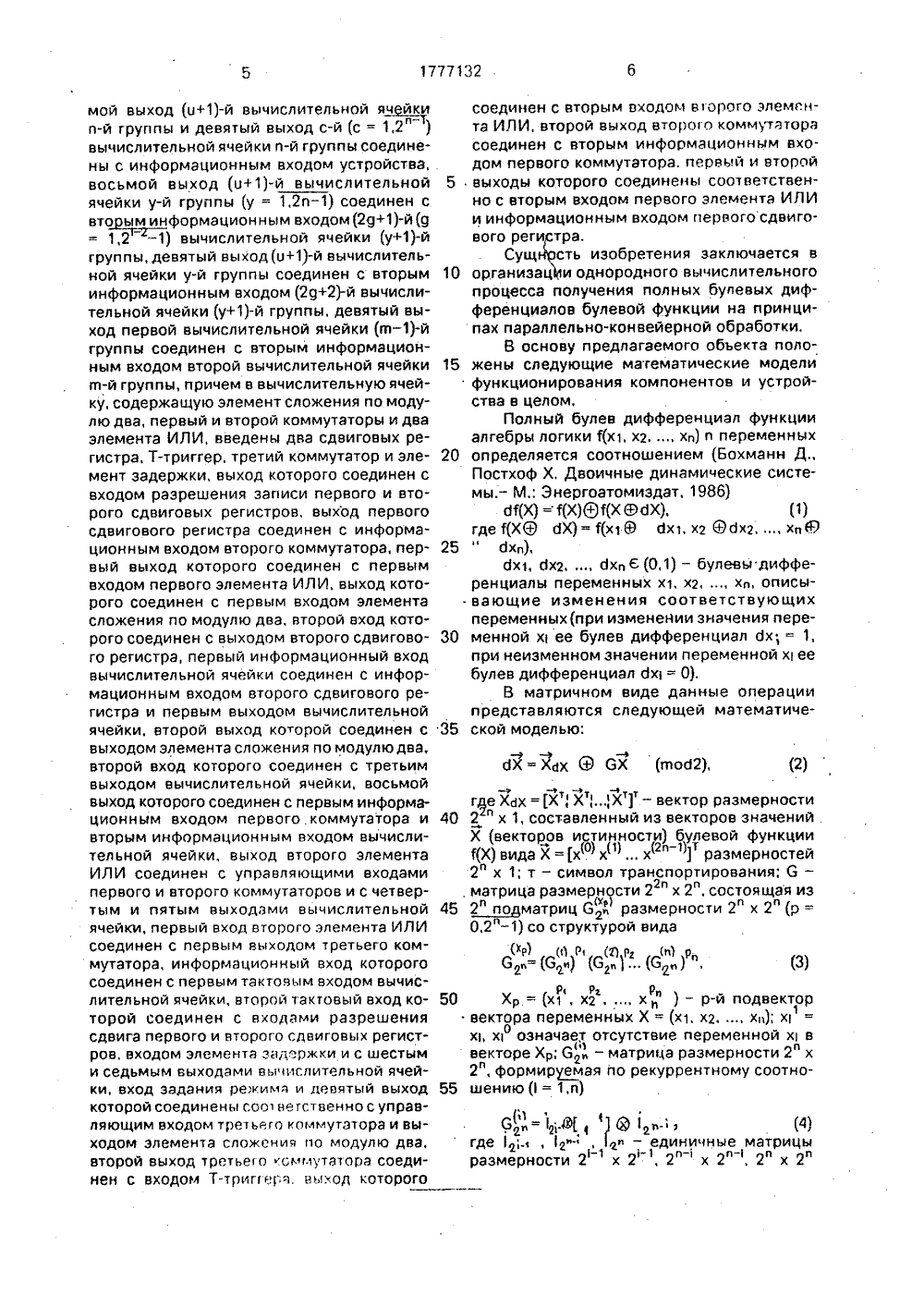

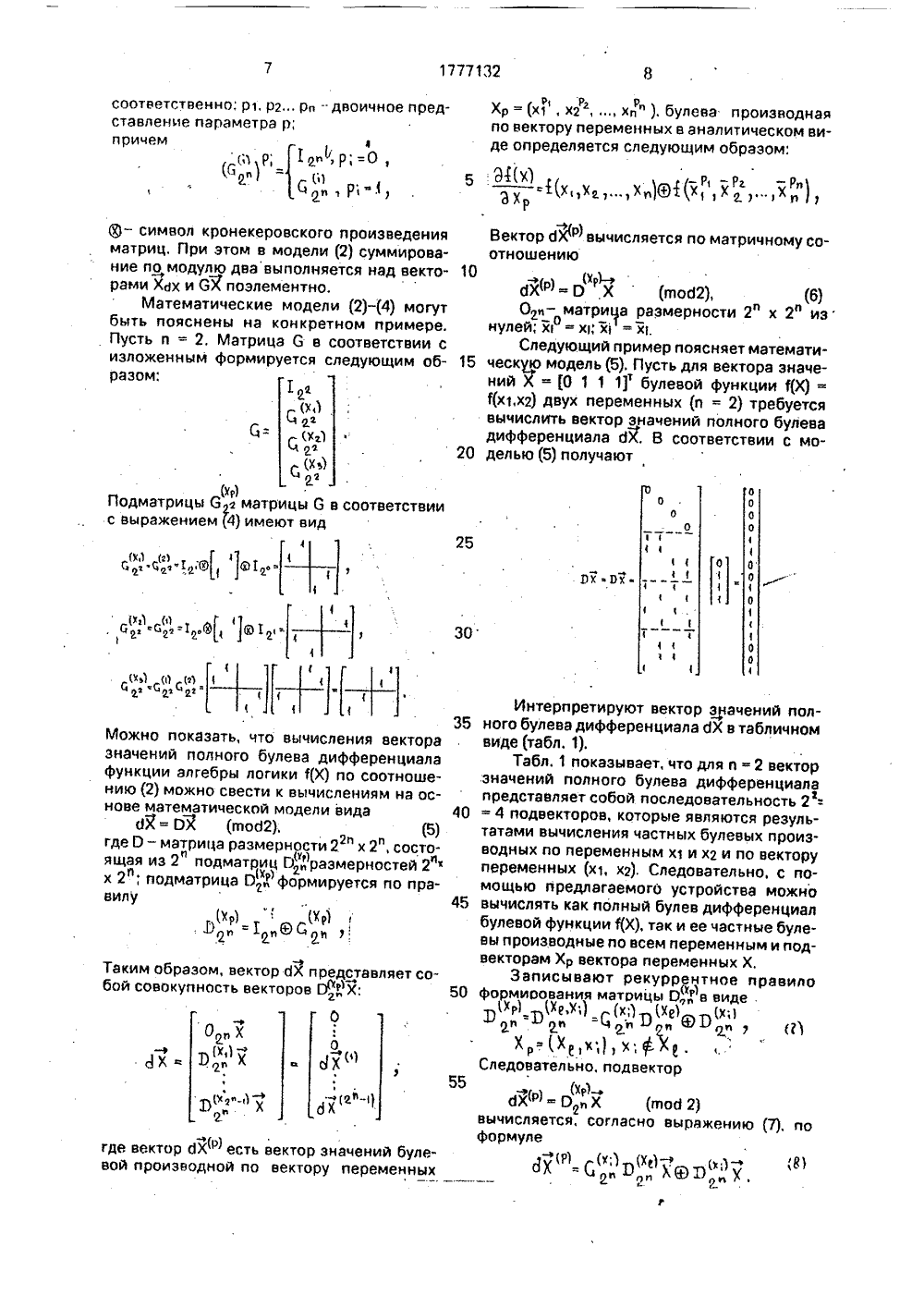

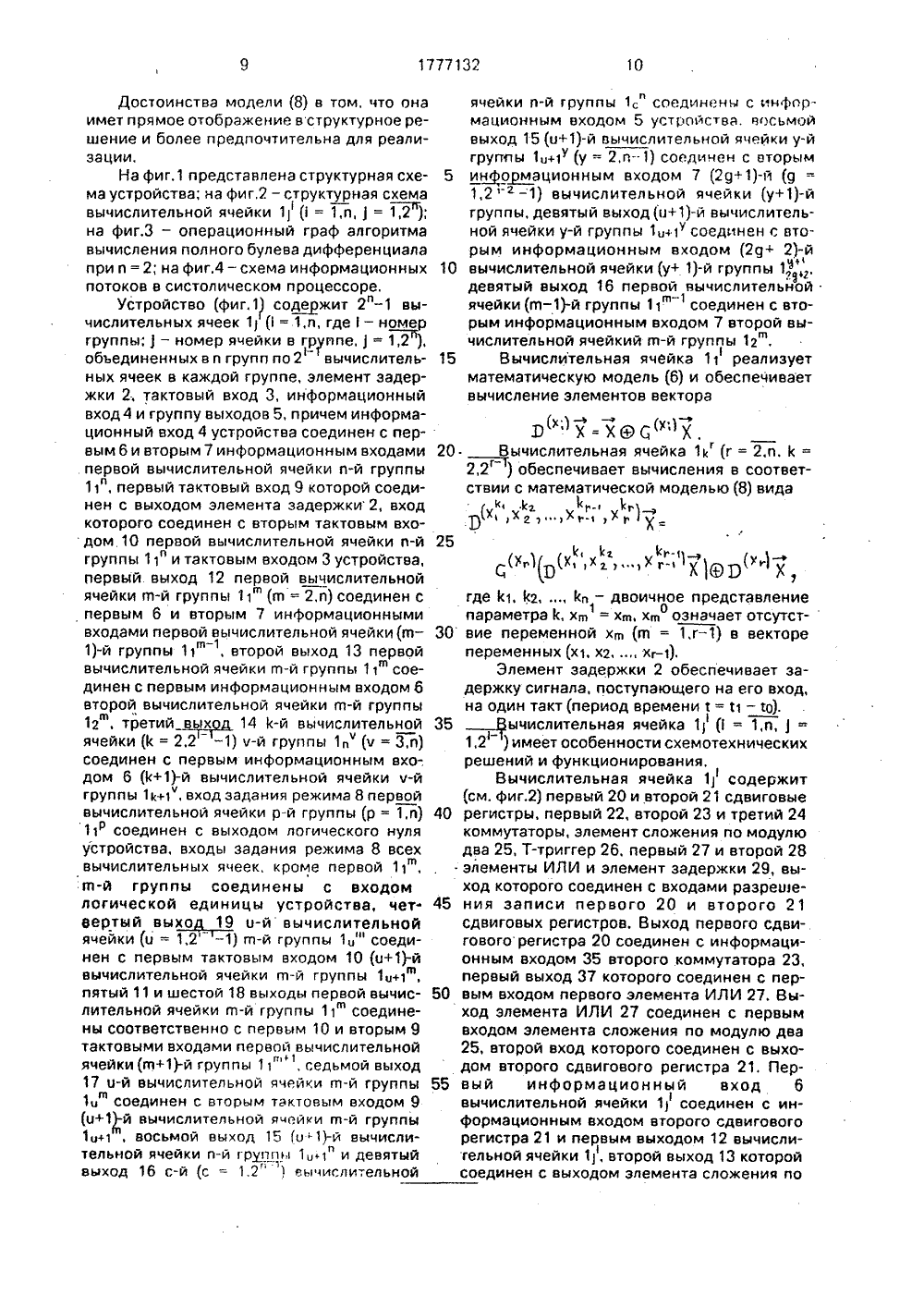

( о)5)5 6 06 Г 7/00, 7 132 Н ГОСУДАРСТВЕННОЕ ПАТЕНТВЕДОМСТВО СССРГОСПАТЕНТ СССР) ОПИСАНИЕ ИЗОБРК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Минский радиотехнический институт(56) Авторское свидетельство СССРМ 1370651, кл, 6 06 Г 7/00. 1986,Авторское свидетельство СССРМ 1317430, кл, 6 06 Е 7/00. 1986.Авторское свидетельство СССР(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ БУЛЕВЫХ ДИФФЕРЕНЦИАЛОВ(57) Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной поддержки вычислении в системах автоматизированно. го анализа и синтеза цифровых автоматов. при их диагностике и контроле. при анализе комбинационных схем, для исследования статических и динамических ограничений при их проектировании, Цель изобретения - расширение функциональных возможностей за счет вычисления булевх производных по всем переменным и векторам переменных, Устройство содержит и групп вычислительных ячеек 1) по 2 ячейки в каждой (и - количество переменных булевой функции; = 1,п; ) = 1,2) и элемент задержки 2. На первом такте работы осуществляется загрузка ячеек, на последующих тактах производится формирование элементов подвекторов результата. 4 ил., 4 табл,тельных ячеек (и - количество переменных булевой функции 1(Х, каждая из которых содержит элемент сложения по модулю два, первый и второй коммутаторы и два элемента ИЛИ, о т л и ч а ю щ е е с я тем, что, с .целью расширения функциональных воэможностей за счет вычисления булевых производных по всем переменным и векторам переменных, оно содержит 2"-и 1 вычислительных ячеек, объединенных в и групп по 21 ( = 1,п) вычислительных ячеек в каждой, и элемент задержки, причем информационный вход устройства соединен с первым и вторым информационными входами первой вычислительной ячейки п-й группы, первый тактовый вход которой. соединен с выходом элемента задержки, вход которого соединен с вторым тактовым входом первой вычислительной ячейки и-й группы и тактовым входом устройства, первый выход первой вычислительной ячейки а-й группы (а = 2,п) соединен с первым и вторым информационными входами первой вычислительной ячейки (а)-й группы, второй выход - с первым информационным входом второй вычислитвпвиои вчвИхи птй группы, трдтии выход Ьй вычислительной ячейки (к =- 2,2 - 1) ч-й группы (ч = З,п) соединен с первым информационным входом(1+1)-й вычислительной ячейки ч-й группы, вход задания режима первой вычислительной ячейки р-й группы (р = 1,п) соединен с входом логического нуля устройства, входы задания режима всех вычислительных ячеек, кроме первой, а-й группы соединен с входом логической единицы устройства, четвертый выход о-й вычислительной ячейки (ц = 1,2 - 1) а-й руппы соединен с первым тактовым входом (о+1)-й вычислительной ячейки а-й группы, пятый и шестой выходы первой вычислительной ячейки а-й группы соединены соответственно с первым и вторым тактовыми входами первой вычислительной ячейки (а+1)-й группы, седьмой выход ц-й вычислительной ячейки а-й группы соединен с вторым та кто вьем входом (ц+1)-й вычислительной ячейки а-й группы, восьмой выход (о+1)-й вычислительной ячейки и-й группы и девятый выход с-й (с - 1.2" ) вычислительной ячейки и-й группы соединены с информационным входом устройства, восьмой выход(в+Я-й вычислительной ячейки у-й группы (у - 2.п) соединен с вторым и нор маци он н ы м входом (29+1)-й . (я = 1,2 -1) вычислительной ячейки (у+1)-й группы, девятый выход (и+1)-й вычислительной ячейки у-й группы соединен с вторым информационным входом (2 од)-й вычислительной ячейки (у+1)-й группы, девятый выход первой вычислительной ячейки (а - 1)-й группы соединен с вторым информационным входом второй вычислительной ячейки а-й группы, причем каждая вычислительная ячейка содержит два сдвиговых регистра. Т-триггер, третий коммутатор и элемент задержки, выход которого соединен с входамиразрешения записи первого и второго сдвиговых регистров, выход первого сдвигового регистра соединен с информационным входом второго коммутатора, первый выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом элемента сложения по модулю два, второй вход которого соединен с выходом второго сдвигового регистра, первый информационный вход вычислительной ячейки соединен с информационным входом второго сдвигового регистра и первымвыходом вычислительной ячейки, второй выход которой соединен с выходом элемента сложения по модулю два. второй входкоторого соединен с третьим выходом вычислительной ячейки, восьмой выход которой соединен с первым информационным входом первого коммутатора и вторым информационным входом вычислительнойячейки, выход второго элемента ИЛИ соединен с управляющими входами первого и вто-, рого коммутаторов и с четвертым и пятым выходами вычислительной ячейки, первый вход второго элемента ИЛИ соединен с первым выходом третьего коммутатора, информационный вход которого соединен с первым тактовым входом вычислительной ячейки, второй тактовый вход которой соединен с входами разрешения сдвига первого и второго сдвиговых регистров, входом элемента задержки и с шестым и седьмым выходами вычислительной ячейки, вход заданиярежима и девятый выход которой соединены соответственно с управляющим входом третьего коммутатора и выходом элемента сложения по модулю два, второй выход третьего коммутатора соединен с входом Т-триггера, выход которого соединен с вторым входом второго элемента ИЛИ, второй выход второго коммутатора соединен с вторым информационным входом первого коммутатора. первый и второй выходы которого соединены соответственно с вторым входом первого элемента ИЛИ и информационным входом первого сдвигового регистра,1777132 22 ТаблицаПолный булевди 00 еренциалдХ еренциалы перемен еменные г 0 1 0 1 1 0 1 0 1 Таблица Номер выхода, на который передается сигнал Второй коммутато23 Третин коммутато24 Первый коммутат Вход 35 ход 23 Вх Ниэкий (лог,О). Высокий (лог.1) Выход 42Выход 41 38 абли в е в Такты конвейера Режим работы 1 "й вычислительной ячейк ерв второй гистра Яагруэка регистров 9 и 10 в 2 у((2 -1) 21+1) 2 + 21+1) 2 + У(Р (2 ) У( (2 +1(2 Логический уровеньсигнала на управляюцевходе коммутатора) Х о) Х) Х 01 Х ( Х 5) Х( Х 51 (И х с (И Х(Ч ХИ) Х Х 1777132 Выиислитепьнал яцейка Солернимое регистров) Х рЮх ль И,КолодиеваМоргентал Корректор Н,Мил)оков Состав Техред Редактор Г,Бельская Заказ 4122 Тираж Подписное ВНИИПИ Государственного ком ета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 105 10 15 20 25 30 35 40 45 Изобретение относится к автоматике ивычислигельной технике и может быть использовано для аппаратной поддержки вычислений в системах автоматизированногоанализа и синтеза цифровых автоматов, приих диагностике и контроле, при анализекомбинационныхсхем, для исследованиястатических и динамических ограниченийпри проектировании комбинационныхсхем.Известно устройство, предназначенноедля вычисления булевых производных и содержащее элементы неравнозначности,блок определения значений функции с соответствующими связями,Известно также устройство, содержащеесчетчик, группу элементов неравнозначности. мультиплексор, элемент И, генератор импульсов, демультиплексор, группу триггеровс соответствующими связями, обеспечивающее вычисление булевых производных,Наиболее близким к изобретению повыполняемым функциям и технической сущности (является устройство, содержащее регистр, и ячеек (и - количество переменныхбулевой функции Щ) с соответствующимисвязями, причем ячейка состоит из двух мультиплексоров (коммутаторов), двух элементовИ. двух элементов ИЛИ, элемента НЕРАВНОЗНАЧНОСТЬ (сумматора по модулю два).Известные устройства реализуют однуи ту же математическую модель,Недостатки этих устройств заключаются в следующем: устройства не позволяют вычислять булевы дифференциалы, а в лучшем случае обеспечивают вычисление составных частей булевых дифференциалов, которые представляют собой булевы производные по частным переменным; нетехнологичны в изготовлении из-за неоднородности объекта по структуре, что вызывает трудности при изготовлении на современной технологической базе сверхбольших интегральных схем; не ориентированы на конвейерные принципы обработки информации, позволяющие одновременно вычислять булевы производные по различным переменным,В результате не обеспечивается эффективное решение большого класса прикладных задач, контроль и диагностика цифровых автоматов, решение логических уравнений как составного этапа синтеза цифровых устройств и функционирования систем принятия решений в управлении ресурсами, распознавании и классификации обьектов, управлении роботами-манипуляторами и гибкими автоматизированными производствами. Эффективность решения здесь понимается прежде всего в плане наиболее простого отображения решения задачи в виде алгоритма в структуры вычислительных средств, ориентированных на современную и перспективную микроэлектронную технологию. Это обеспечивает создание мощных средств аппаратной поддержки вычислений в ЭВМ и комплексах различного назначения.Предлагаемое техническое решение устраняет перечисленные недостатки.Цель изобретения - расширение функциональных воэможностей устройства за счет вычисления полного булева дифференциала логической функции, в том числе - булевых производных по всем переменным и векторам переменных.Указанная цель достигается тем, что вустройство, содержащее и вычислительных ячеек (и - количество переменных булевой функции 1(Х, введены (2" - и - 1) вычислительных ячеек, объединенных в и групп по 2( = 1,и) вычислительные ячейки в каждой, и элемент задержки, причем информационный вход устройства соединен с первым и вторым информационныи входами первой вычислительной ячейки и-й группы, первый тактовый вход которой соединен с выходом элемента задержки, вход которого соединен с вторым тактовым входом первой вычислительной ячейки и-й группы и тактовым входом устройства, первый выход первой вычислительной ячейки щ-й группы (а = 2,и) соединен с первым и вторым информационными входами первой вычислительной ячейки (ги)-й группы, второй выход первой вычислительной ячейки в-й группы соединен с первым информационным входом второй вычислительной ячейки ги-й группы, третьей выход 1-й вычислительной ячейки (к - 2,2 -1) ч-й группы (ч = З,и) соединен с первым информационным входом (1+1)-й вычислительной ячейки ч-й группы, вход задания режима первой вычислительной ячейки р-й группы (р = 1,и) соединен с входом логического нуля устройства, входы задания режима всех вычислительных ячеек, кроме первой, ги-й группы соединены с входом логической единицы устройства, четвертый выхрд о-й вычислительной ячей ки (ц - 1, 2 -1) е-й группы соединен спервым тактовым входом (01)-й вычислительной ячейки т-й группы, пятый и шестой выходы первой вычислительной ячейки в-й группы соединены соответст венно с первым и вторым тактовыми вхо.. дами первой вычислительной ячейки(щ+1)-й группы, седьмой выход в-й вычислительной ячейки из-й группы соединен с вторым тактовым входом (о 41)-й вычислительной ячейки гп-й группы. вась.мой выход (о+1)-й вычислительной ячейки и-й группы и девятый выход с-й (с = 1,2" ) вычислительной ячейки и-й группы соединены с информационным входом устройства, восьмой выход (о+1)-й вычислительной ячейки у-й группы (у = 1,2 п) соединен с вторым информационным входом(2 д+1).й(р1,2 - 1) вычислительной ячейки (у+1)-й группы, девятый выход(о+1)-й вычислительной ячейки у-й группы соединен с вторым информационным входом (2 д+2)-й вычислительной ячейки (у+1)-й группы, девятый выход первой вычислительной ячейки (е - 1)-й группы соединен с вторым информационным входом второй вычислительной ячейки в-й группы, причем в вычислительную ячейку, содержащую элемент сложения по модулю два, первый и второй коммутаторы и два элемента ИЛИ, введены два сдвиговых регистра, Т-триггер, третий коммутатор и элемент задержки, выход которого соединен с входом разрешения записи первого и второго сдвиговых регистров, выход первого сдвигового регистра соединен с информационным входом второго коммутатора, первый выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с первым входом элемента сложения по модулю два, второй вход которого соединен с выходом второго сдвигового регистра, первый информационный вход вычислительной ячейки соединен с информационным входом второго сдвигового регистра и первым выходом вычислительной ячейки, второй выход которой соединен с выходом элемента сложения по модулю два, второй вход которого соединен с третьим выходом вычислительной ячейки, восьмой выход которого соединен с первым информационным входом первого коммутатора и вторым информационным входом вычислительной ячейки, выход второго элемента ИЛИ соединен с управляющими входами первого и второго коммутаторов и с четвертым и пятым выходами вычислительной ячейки, первый вход второго элемента ИЛИ соединен с первым выходом третьего коммутатора, информационный вход которого соединен с первым тактовым входом вычислительной ячейки, второй тактовый вход которой соединен с входами разрешения сдвига первого и второго сдвиговых регистров, входом элемента зад"ржки и с шестым и седьмым выходами вычислительной ячейки. вход задания режима и девятый выход которой соединены соо 1 вегственно с управляющим входом третьего комлйутэтора и выходом элемента сложения по модулю два, второй выход третьего олч.1 утатора соединен с входом Т-триггера. выход которого(п 1 об 2), (2) гд 2 е Хсх = (Х а Х", Х - вектор размерности40 2 "х 1, составленный из векторов значенийХ (векторов истинности) булевой функциид(Х) Х(2 -2" х 1; т - символ транспортирования; 6 -, матрица размерности 2 "х 2", состоящая иэ45 2",подматриц йразмерности 2 х 2"(р =П0,2 - 1) со структурой вида(3)Ра Ра Рп50 Хр = (х 1, х 2 х) - р-й подвекторвектора переменных Х = (х 1. х 2, , хл); ххь х 1 означает отсутствие переменной х вовекторе ХР, 6- матрица размерности 2" х2", формируемая по рекуррентному соотно 55 шению(1=1,п) 6,.= ,;.а(, 9 ,.;,(4)ГДЕ 12,.а, )2-, п - ЕДИНИЧНЫЕ МатРИЦЫразмерности 2 х 2, 2"х 2" , 2" х 2" соединен с вторым входом вгорого элемента ИЛИ, второй выход второго коммутаторасоединен с вторым информационным входом первого коммутатора, первый и второй5 . выходы которого соединены соответственно с вторым входом первого элемента ИЛИи информационным входом первого сдвигового реги тра.Сущ сть изобретения заключается в10 организац и однОродного вычислительногопроцесса получения полных булевых дифференциалов булевой функции на принципах параллельно-конвейерной обработки.В основу предлагаемого объекта поло 15 жены следующие математические моделифункционирования компонентов и устройства в целом,Полный булев дифференциал функцииалгебры логики 1(х 1, х 2, , хп) и переменных20 определяется соотношением (Бохманн Д.,Постхоф Х, Двоичные динамические системы. - М,: Энергоатомиэдат, 1986)Ю(Х) = 1(Х)(+) 1(Х Ю б Х), (1)гдЕ т(ХО+ бХ) = т(х 19 Ьх 1, х 2 О+бх 2, ., хай25 " бхай),бх 1, бх 2, , бхл 6(0,1) - булевы дифференциалы переменных х 1, х 2, , х описы. вающие изменения соответствующихпеременных(при изменении значения пере 30 менной х ее булев дифференциал бх; = 1,при неизменном значении переменной х еебулев дифференциал бх = О).В матричном виде данные операциипредставляются следующей математиче 35 ской моделью:Достоинства модели (8) в том, что она имет прямое отображение в структурное решение и более предпочтительна для реализации.На фиг.1 представлена структурная схема устройства; на фиг,2 - структурная схема вычислительной ячейки 1 ( = 1,п,) = 1,2 ); на фиг.З - операционный граф алгоритма вычисления полного булева дифференциала при и =2; на фиг.4 - схема информационных потоков в систолическом процессоре,Устройство (фиг.1 содержит 2" - 1 вычислительных ячеек 1) ( = 1,п, где - номер группы; ) - номер ячейки в грппе,= 1,2"), объединенных в и групп по 2 вычислительных ячеек в каждой группе, элемент задержки 2, тактовый вход 3, информационный вход 4 и группу выходов 5, причем информационный вход 4 устройства соединен с первым 6 и вторым 7 информационным входами . первой вычислительной ячейки и-й группы 11, первый тактовый вход 9 которой соединен с выходом элемента задержки 2, вход которого соединен с вторым тактовым входом 10 первой вычислительной ячейки и-й группы 11 и тактовым входом 3 устройства, первый выход 12 первой вычислительной ячейки т-й группы 11 (гп = 2,п) соединен с первым 6 и вторым 7 информационными входами первой вычислительной ячейки(в - 1)-й группы 11 , второй выход 13 первой вычислительной ячейки п 1-й группы 11 соединен с первым информационным входом 6 второй вычислительной ячейки в-й группы 12, третий еыхрд 14 1-й вычислительной ячейки (к = 2,2 -1) ч-й группы 1 П" (ч = З,п) соединен с первым информационным вхо-, дом 6 (1+1)-й вычислительной ячейки ч-й группы 1+1", вход задания режима 8 первой вычислительной ячейки р-й группы (р = 1,п) 11 Р соединен с выходом логического нуля устройства, входы задания режима 8 всех вычислительных ячеек, кроме первой 11, в-й группы соединены с входом логической единицы устройства, чет. еертый выход 19 о.й вычислительной ячейки (ц = 1,2 -1) гп-й группы 1" соединен с первым тактовым входом 10 (и+1)-й вычислительной ячейки т-й группы 1+1, пятый 11 и шестой 18 выходы первой вычислительной ячейки п 1-й руппы 11 соединены соответственно с первым 10 и вторым 9 тактовыми входами первой вычислительной ячейки (гп+1)-й группы 11", седьмой выход 17 ц-й вычислительной ячейки п 1-й группы 1 е соединен с вторым тактовым входом 9 (ц+1 й вычислительной яцейки п 1-й группы 1 в+1, восьмой выход 15 Ьт 1)-й вычислительной ячейки и-й групгы 1+1 и девятый выход 16 с-й (с =- 1,21 вьчислительной51015 ячейки и-й группы 1 С соединены с информационным входом 5 устройства. восьмой выход 15 (о+1)-й вычислительной ячейки у-й группы 1+1" (у =- 2,п) соединен с вторым информационным входом 7 (2 у+1)-й (д =- 1,2 -1) вычислительной ячейки (у+1)-й группы, девятый выход (и+1)-й вычислительной ячейки у-й группы 1+1" соединен с вторым информационным входом (2 у+ 2)-й вычислительной ячейки (у+ 1)-й группы 1,",очаг девятый выход 16 первой вычислительйой . ячейки(т - 1)-й группы 11 соединен с вторым информационным входом 7 второй вычислительной ячейкий т-й группы 12.Вычислительная ячейка 11 реализуетматематическую модель (6) и обеспечивает вычисление элементов вектора г("х = хо+с(Х 1)(.20. Вычислительная ячейка 1 (г = 2,п, М =2,2 ) обеспечивает вычисления в соответствии с математической моделью (8) вида1 сг - г 1)(Хь тХр е, Хт-е тХтт 1 Х251 а Ь М(п(х,хт )Х т в (р дд(т 4ГДЕ К 1. К 2, Кп - ДВОИЧНОЕ ПРЕДСтаВЛЕНИЕпараметра К хр = хп, х означает отсутст 1 О30 вие переменной хв (а = 1,г - 1) в векторепеременных (х 1, х 2, .хг).Элемент задержки 2 обеспечивает задержку сигнала, поступающего на его вход,на один такт (период времени 1 = 11 - то).35 вычислительная ячейка 11 ( = 1,п, ) =1,2 ) имеет особенности схемотехническихрешений и функционирования,Вычислительная ячейка 1 содержит(см. фиг.2) первый 20 и второй 21 сдвиговые40 регистры, первый 22, второй 23 и третий 24коммутаторы, элемент сложения по модулюдва 25, Т-триггер 26, первый 27 и второй 28. элементы ИЛИ и элемент задержки 29, выход которого соединен с входами разреше 45 ния записи первого 20 и второго 21сдвиговых регистров. Выход первого сдвигового регистра 20 соединен с информационным входом 35 второго коммутатора 23,первый выход 37 которого соединен с пер 50 вым входом первого элемента ИЛИ 27. Выход элемента ИЛИ 27 соединен с первымвходом элемента сложения по модулю два25, второй вход которого соединен с выходом второго сдвигового регистра 21. Пер 55 вый информационный вход бвычислительной ячейки 1 соединен с информационным входом второго сдвиговогорегистра 21 и первым выходом 12 вычислигельной ячейки 11, второй выход 13 которойсоединен с выходом элемента сложения помодулю два 25, Второй вход последнего соединен с третьим выходом 14 вычислительной ячейки, восьмой выход 15 которой соединен с первым информационным входом 30 первого коммутатора 22 и вторым информационным входом 7 вычислительной ячейки 11, Выход второго элемента ИЛИ 28 соединен с управляющими входами 30 и 36 первого 22 и второго 23 коммутаторов и с четвертым 18 и пятым 17 выходами вычислительной ячейки 11. Первый вход второго элемента ИЛИ 28 соединен с первым выходом 41 третьего коммутатора 24, Информационный вход 39 коммутатора 24 соединен с первым тактовым входом 9.вычислительной ячейки 1, вторым тактовым входом 10. соединенный с входами разрешения сдвига первого 20 и второго 21 сдвиговых регистров, входом элемента задержки 29 и шестым 11 и седьмым 19 выходами вычислительной ячейки, вход задания режима 8 и девятый выход 16 которой соединены соответственно с управляющим входом 40 третьего коммутатора 24 и выходом элемента сложения по модулю два 25. Второй выход 42.третьего коммутатора 24 соединен с входом Т-триггера 26, выход которого соединен с вторым входом второго элемента ИЛИ 28. Второй выход 38 второго коммутатора 23 соединен с вторым информационным входом 32 первого коммутатора 22, первый 33 и второй выходы которого соединены соответственно с вторым входом первого элемента ИЛИ 27 и информационным входом первого сдвигового регистра 20,Первый сдвиговый регистр 20 (сдвиговый регистр, например, на элементах ИР 8 серии К 155) обеспечивает прием информации, поступающей на его информационный вход(младший разряд) по сигналу записи на его входе управления записью, сдвиг информации по сигналу на его входе управления сдвигом и выдачу информации с выхода старшего разряда, разрядность равна 2"в каждом такте работы вычислительной ячейки 11,Второй сдвиговый регистр 21 (сдвиговый регистр, например, на элементах ИР 8 серии К 155) обеспечивает прием информации, поступающей на его информационный Вход(младший разряд) по сигналу записи на его входе управления записью, сдвиг информации по сигналу на его входе управления сдвигом и выдачу информации с выхода старшего разряда, разрядность равна 2"для вычислительных ячеек 11; разрядностьравнга 2" +" для вычислительных ячеек 1 к, М "2,2, в каждом такте работы вычислительных ячеек.10 Первый коммутатор 22 обеспечивает передачу информации с первого информационного входа 30 на второй выход 34 принизком логическом уровне сигнала на управляющем входе 31 и с второго информационного входа 32 на второй выход 34, а спервого информационного входа 30 на первый выход 33 при высоком логическом уровне сигнала навходе 31 (табл, 2),Второй коммутатор 23 обеспечивает передачу информации с информационноговхода 35 на первый 37 или второй 38 выходы соответственно при низком или высоком логическом уровне сигнала на управляющем входе 36 (табл. 2).Третий коммутатор 24 обеспечивает передачу информации с информационного входа 39 на первый 41 и второй 42 выходы соответственно при высоком или низком ла 20 гическом уровне сигнала на управляющемвходе 40 (табл. 2),Элемент сложения по модулю два 25предназначен для реализации операциисложения по модулю два операндов, посту25 пающих на его первый и второй входы, ивыдачи результатов суммирования на выход,Т-триггер 26 предназначен для управления работой первого 22 и второго 23 комму 30 таторов Ь вычислительных ячейках 11 (- 1,п). Конструктивно это триггер со счетнымвходом, управляемый по перепаду входногосигнала из мО" в "1". Начальное состояние. его - нулевое.35 Первый 27 и второй 28 элементы ИЛИпредназначены для логического анализавходных сигналов посредством выполнениянад ними операции дизьюнкции,Элемент задержки 29.обеспечивает за 40 держку сигнала, поступающего на его вход,на 1/2 такта(период времени т- (Ъ - 1 о)/2).гВычислительная ячейка 111 функциони-.: рует следующим. образом.В период времен то -.;, т,е. на первых45 2"тактах работы устройства, вычислительная ячейка 11 функционирует в первом ре 1жиме (табл. 3). При этом осуществляетсязагрузка свигвых метисров 20 иЯ 1 элв.ментами х, х, , хвектора Х.50 В период 1; - 1, ;, т.е, на следующих2 тактах вычйслительная ячейка 11 функционирует во втором режиме (табл. 3), Прйэтом выполняется вычисление элементов55 (у0) уф(1), , у(2" -1)".(е 2" ) путесуммиювания по моулб два элементов х(ч - 0,2 -1) и х" " вектора Х. поступающих на входы элемента сложения по модулк,два 21, т,е. нв еыхоое лооледнего фермеруется у "(ч) - х"9 х " "В следуощии период времени 1 .т 1.-и- гги ат.е, на следующих 2 тактах, вычислительная ячейка 1 функционирует в первом режиме, на выходе элемента сложения по модулю два 25 фоомдиуются элементь у( (ч+2" ) = у(ч) (ч = 0,2 -1) вектора оХ(. На этих же тактах в регистр 20 по сигналу записи на его входе управления записью последовательно записываются следующие 2Ф элементов (хф, х, , х ) вектора Х.На остальных (2" - 2 2" ) тактах вычисления выполняются аналогично вычислениям в период времени т .; - 1, -т, При этом первый и второй режимы функционирования вычислительной ячейки 11 чередуютсячерез каждые 2" такта (табл. 3).Компоненты вычислительной ячейки 11в процессе работы функционируют следующим образом.На вход задания режима 8 вычислительной ячейки 11 поступает низкий логический уровень сигнала, который обеспечивает передачу сигналов с первого тактового входа 9 вычислительной ячейки 11 на вход 39 коммутатора 24, а с его выхода 42 - на вход триггера 26, На выходе триггера 26 формируется управляющий сигнал для коммутаторов 22 и 23, Первый 6 и второй 7 информационные входы вычислительной ячейки 11 объединены и обеспечивают о(-новременнОе поступление элементов х х, , х "вектора 2( на информационный вход сдвигового регистра 21 и вход 30 коммутатора 22.С первого по (2" +1)-й такты вычислительная ячейка 1 функционирует в первомрежиме, При этом на первом такте (1 о) на второй тактовый вход 10 вычислительной ячейки 11 поступает тактовый сигнал, который передается на вход элемента задержки 29 и на входы управления сдвигом сдвиговых регистров 20 и 21. В результате по этому сигналу осуществляется сдвиг содержимого сдвиговых регистров 20 и 21 на один разряд вправо в сторону старших. В момент времени то + г по сигналу записи, поступающему с выхода элемента задержки 29 на входы управления записью сдвиговых регистров 20 и 21, в младшие разряды этих регистров)- хйх 1, х( ". На втором и последующих тактах(по 2" -й включительно) эта процедура выполняется над элементами х( 2, х , , х(21 (а -На (2" + 1)-м такте вычислительнаяячейка 11 начинает функционировать во втором режиме. При этом о сигналу на первом тактовом входе 9с . -.цтельной ячейки 1 (по спаду из и 1" в П"), пог 1 чпа 1 ол 1 ч)на вход 39 комму 1 атора 21, нл . соде элемента ИЛИ 28 устанавливается высокий ло гический уровень сигнала В результате 5 элемент х"вектора значений Х передается с первого информационного входа 6 вычислительной ячейки 1 на вход 30 коммутатора 22 и далее на его выход 33. а затем поступает на первый вход э 1 лемента 10 ИЛИ 27; одновременно элемент х из стар(о 1шего (2" -го) разряда сдвигового регистра 20 передается на входе 35 коммутатора 23 и далее на его выход 38, а затем с входа 33 коммутатора 22 на его выход и записывает ся в младший разряд сдвигового регистра 20по сигналу записи на его управляющем входе, На первый вход элемента сложения по модулю два 25 поступает элемент х( 2 из(о)старшего разряда сдвигового регистра 21, 20 на его второй вход - элемент х " 2 с выходаэлемента ИЛИ 27. В результате на выходе элемента сложения п модулю два 25 формируется результат (х х 2 ) . Этот результат передается на второй 13 и девятьй 16 25 информационные выходы вычидлительнойячейки 11. Кроме того, элемент х 2 с выхода сдвигового регистра 21 передается на третий выход 14 вычислительной ячейки 11. В результате повторения этой процедуры на 30 тактах с (2 к 2 то оо 2" и-и фоомиоукттсксуммы по модулю два х Офх( " 1. х( +(Я фй (2 4 (2. -1 т 22-1+х х ох ), С 2 -го по 2 -й такты вычислительная ячейка 11 раи-+2- 35 ботает в первом режиме функционирования, на управляющие входы 31 и 36 коммутаторов 22 и 23 поступает низкий логический уровень сигнала. В этом режтлме,л -длительность которого 2" тактов. элементы х, х, х вектора Х, поступающие на первый информационный вход 6 вычислительной ячейки 11, последовательно записываются в сдвиговый регистр 20 по 45 сигналу записи на его входе управления за(2 -1писью. При этом элементы х( 2, х(2, х хранящиеся в сдвиговом регистре 20, последовательно передаются по информационно му тракту: вход 35 коммутатора 23 - выход37 коммутатора 23 - элемент ИЛИ 27 - второй вход элемента сложения по модулю два .25. На первый вход последнего с выхода сдвигового регистра 21 поступает в соот ветствующие такты элементы вектора Х. Результаты вычислений с выхода элемента сложения по модулю два 25 передаются на второй 13 и девятый 16 выходы вычислительной ячейки 11.)аким образом, вычислительная ячейка 1 с первого по 2 -й такты работает в пер ээ вам режимережиме загрузки данных (без выдачи результатов), на тактах с (2" +1)-го по(2" +").и - в дожиме выдачи элементов 5 у (О), у"(1)у" (2"-1) вектора результата с)Х 1) (чч = 2). При этом продолжается загрузка элементов вектора значений Х. На (2 "+1)-м также можно начинать загрузкуследующего из обрабатываемых векторов Х, 10Функционирование вычислительной ячейки 1 ( = 2,2 ) отличается от функционирования вычислительной. ячейки 11. Отличие заключается в следующем.При функционировании вычислительной 15 ячейки 1 на ее вход задания режима 8 поступает высокий логический уровень сигнала, обеспечивающий передачу сигналов по инфор. мационному тракту: первый тактовый вход 9 вычислительной ячейки 1 - вход 39 коммутатора 2024 - выход 41 коммутатора 24 - первый вход элемента ИЛИ 28, Таким образом, сигналы, поступающие на первый тактовый вход 9 вычислительной ячейки 1, являются управляющими для первого 22 и второго 23 коммутаторов. 25В период времени тгиг" т 1 г"(с 21 - 1)2" +1)-го по 21-1)2" +2" -й тактыработы устройства) вычислительная ячейка1 функционирует во втором режиме, При 30этом осуществляется загрузка сдвигового(2 2" +1)-го по (212" +2 )-й такты работы устройства) вычислительная ячейка 1 функционирует в первом режиме, На этих тактах 40 происходит загрузка сдвигового регистра(у ) х,) х). ,20 элементами у ) (О), у (1). У Р ")вектора ОХ ч) (ц - -1 2" +1) и продолжается загрузка сдвигового регистра 21 следующи 45(х,)ми элементами вектора бХВ следующий период времени (т д) и. -- тгц)гд-). т.е. на следующих 2"тактах, навыходе элемента сложения по модулю два(Ь,к,) - в(х х 1у(2" -1) вектора бХ . которыепредставляют собой суммы по модулю два (ух)(чук) (ч+2"(ч - 0.2" -1). и пос 1 уг 1 ают надевятый выход 16 вычислительной ячейки 1. На следующих тактах проигходит выи-числение следующих 2 элементов вектора- .(У,к,)с 1 Х за счет суммирования по модулю двана элементе сложения по модулю два 25М и- Я и элементов у (ч+2" ) и у (ч) (ч = 0,2" -1),Результаты суммирования передаются на девятый выход 16 вычислительной ячейки 1 г,Следовательно, вычислительная ячейка1 на тактах с 21 - 1)2" +1)-го по 2+1)2" 1)-йфункционирует в режиме загрузки данных,а на следующих 2" тактах - в режиме выдачирезультата (табл, 3),Компоненты вычислительной ячейки 1в первом и во втором режиме работают также. как и компоненты вычислительной ячейки 11,Функционирование устройства в совокупности составляющих его компонентов можетбыть рассмотрено на конкретном примере вычисления пол ного булева диффере н циала дляфункции трех переменных (и = 3,.Исходный вектор значений Х =(х х(о),1,х 1 т функции 1(Х) подается поэлементно (начиная с младшего элемента хна информационный вход устройства. Устройствосо)держит 2 - 1 = 7 вычислительных ячеек:э11 11 112 11 14Вычислительные ячейки 11, 1 . 11 ивычислительные ячейки 12, 12 - 14 (фиг.4)работают следующим образом,На первом такте работы устройства вычислительные ячейки 11, 11 и 11 функционируют в первом режиме, При этом первыйо)элемент х вектора значений Х(момент времени то) передается с первых информацзионных входов 6 вычислительных ячеек 11 . 112и 11, Обьединенных С входами 7 Этих ячеек,1на вхооды 30 коммутаторов 22, Далее элемент х с входа 30 каждого иэ коммутаторов22 по низкому логическому уровню сигналана их управляющих входах 31 передается наинформационный вход каждого из сдвиговых регистров 20 и записывается в его младший разряд, Кроме того, элемент х 1) спервых информационных входов 6 вычислительных ячеек поступает на информационный вход каждого из сдвиговых регистров21 и записывается в его младший разряд(посигналу записи на входе управления записью сдвигового регистра 21) (табл, 4). На втором такте (момент времени 11)вычислительные ячейки 11 и 11 продолжа 2ют функционировать в первом режиме, вних выполняются аналогичные вычисленияЦдля элемента х вектора значений .Х, кадля элемента х, Б ычис питал ь ад чче 1 м аОз1 переходит ао о 1 ооей ре. цг 1нэ парэ ирования, и в ней вычисления осущтвляютЯся следующим образом: элемент х с входа 30 коммутатора 22 передается на его выход 33 и далее на первый вход элемента ИЛИ 27, с выхода которого хпередается на второй 5 вход элемента сложения по модулю два 25, При этом коммутаторы 22 и 23 вычислительной ячейки 11 функционируют во втором режиме, и элемент х с выхода одноразрядного регистра 20 передается на информаци онный вход этого регистра и по сигналу записи на его входе управления записью перезаписывается в свиговый регистр 20. Кроме того, элемент х записывается в одноразрядный регистр 21, а элемент х(, хра нившийся в сдвиговом регистре 21, передается с его выхода на первый вход апемента сложения по модулю дал 5. Ре. зультат суммирования у (О) =- х"Юх( с выхода элемента сложения по модулю два 25 20 передается на выходы 13 и 16 вычислительной ячейки 11, с вуфода 1 Д вычислительной ячейки 11 сумма у (О) = х х . передается на первый информационный вход 6 вычислительной ячейки 1 г и записывается в ее 25 сдвиговый регистр 21.На третьем такте (момент времени 1 г) на первый информационный вход 6 вычислит ьных ячеек 11 - 11 поступает элементЭх , При этом вычислительная ячейка 11 з пе реодит в первый режим работы, и элемент х(, хранившийся в сдвиговом регистре 20 вычислительной ячейки 11, передается с его выхода на второй вход элемента сложения по модулю два 25 и суммируется с эле ментом х, поступившим,с выхода сдвитового регистр 21. Результат суммирования у (1) х Вх у передается на второй(ц13 и девятый 16 выходы вычислительной ячейки 11 и на первый информационный 40 вход 6 вычислительной ячейки 1 гз и записывается в сдвиговый регистр 21 по сигналу записи на его входе управления записью (табл. 4), Одновременно в сдвиговые регизстры 21 вычислительных ячеек 11, 1 и 1 и 45 в сдвиго 1 вые регистры 20 вычислитеных ячеек 11 и 11 записываетсяэлементх, На этом же такте вычислительная ячейка 11 переходит во второй режим функционирования, и на выходе элемента сложения пог 50 модулю два 25 вычислительной ячейки 11 формируется первый элемент вектора бХ":ур(О) - х у х", который передается на девятый выход 16 вычислительной ячейки 11 и на второй информационный вход 7 55 вычислительной ячейки 1 г . где элемент у (0) записывается в сдвиговый регистр 21,Не пятом такте формируются слеуюотие апелаенты лектора олзуллтата: у (З, у (2) и у (1) в вычислительнь.х ячейках 11,11 и 1 г соответственно, Вычислительнаягячейка 11 на этом такте переходит во второй режим функционирования и на ее вых 4 одах формируется элемент у)(0) = х(Рх( 1который с девятого выхода 16 вычислительной ячейки 11 передается на второй информационный вход 7 вычислительной ячейки11, где записывается в сдвиговый регистр20, и с девятого выхода 16 вычислительнойячейки 11 передается на второй информационный вход 7 вычислительной ячейки 14и записывается в ее сдвиговый регистр 20.Вычислительные ячейки 1 г, 1 з, 14 функцизонируют в соответствии с табл. 4,Таким образом; на тактах с второго подевятый в вычислительной яйке 11 ррмируются элементы у (О), у (1), , у (7)вектора бХ , элементы вектора бХ- ввычислительной ячейке 11 на тактах стретьего по десятый, элементы вектора бХ- в вычислительной ячейке 1 г на тактах с3четверто по одиннадцатый, элементы вектора бХ - в вычислительной ячейке 11 натактах с пятого по двенадцатый, элементывектора бХ( у - в вычислительной ячейке 1 зна тактах с шестого по тринадцатый, эле(б)менты вектора бХ - в вычислительнойячейке 1 г на тактах с седьмого по четырнад(7)цатый, элементы вектора бХ - в вычислительной ячейке 14 на тактах с восьмого попятнадцатый, в соответствии с табл, 4,Таким образом, в целом функционирование устройства заключается в следующем; на первом такте происходит загрузкавычислительных ячеек 11, 11 и 11, на сле 1дующих четырнадцать- выд(ача результи)ующих элементов у( О)у(1), у (7)подвекторов результата бХ) (з = 1,7). Приэтом, начиная с девятого такта, можно осуществлять загрузку устройства элементамиследующего вектора значений Х следующейбулевой функции 1(Х),Таким образом, изобретение характеризуется следующими технико-экономическими преимуществами по сравнению саналогами и прототипом: расширениемфункциональных возможностей за счет того, что устройство позволяет вычислять полный булев дифференциал и булевыпроизводные по переменным и векторампеременных функции алгебры логики, приэтом вычисление отдельных частей полногобулева дифференциала осуществляется параллельно; простотой технических решенийи технологичностью изготовления на основеСБИС-технологии; сокращением затрат наизготовление.Формула изобретенияУстройство для вычисления булевыхдифференциалов, содержащее и вычисли

СмотретьЗаявка

4771326, 18.12.1989

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

КОЛОДИЕВА ИННА ЛЕОНИДОВНА, ПАРАМОНОВА НАТАЛЬЯ НИКОЛАЕВНА, ШМЕРКО ВЛАДИМИР ПЕТРОВИЧ, ЯНУШКЕВИЧ СВЕТЛАНА НИКОЛАЕВНА

МПК / Метки

Метки: булевых, вычисления, дифференциалов

Опубликовано: 23.11.1992

Код ссылки

<a href="https://patents.su/14-1777132-ustrojjstvo-dlya-vychisleniya-bulevykh-differencialov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления булевых дифференциалов</a>

Предыдущий патент: Стохастический генератор функций уолша

Следующий патент: Программируемое логическое устройство

Случайный патент: 190211