Устройство для вычисления степенной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

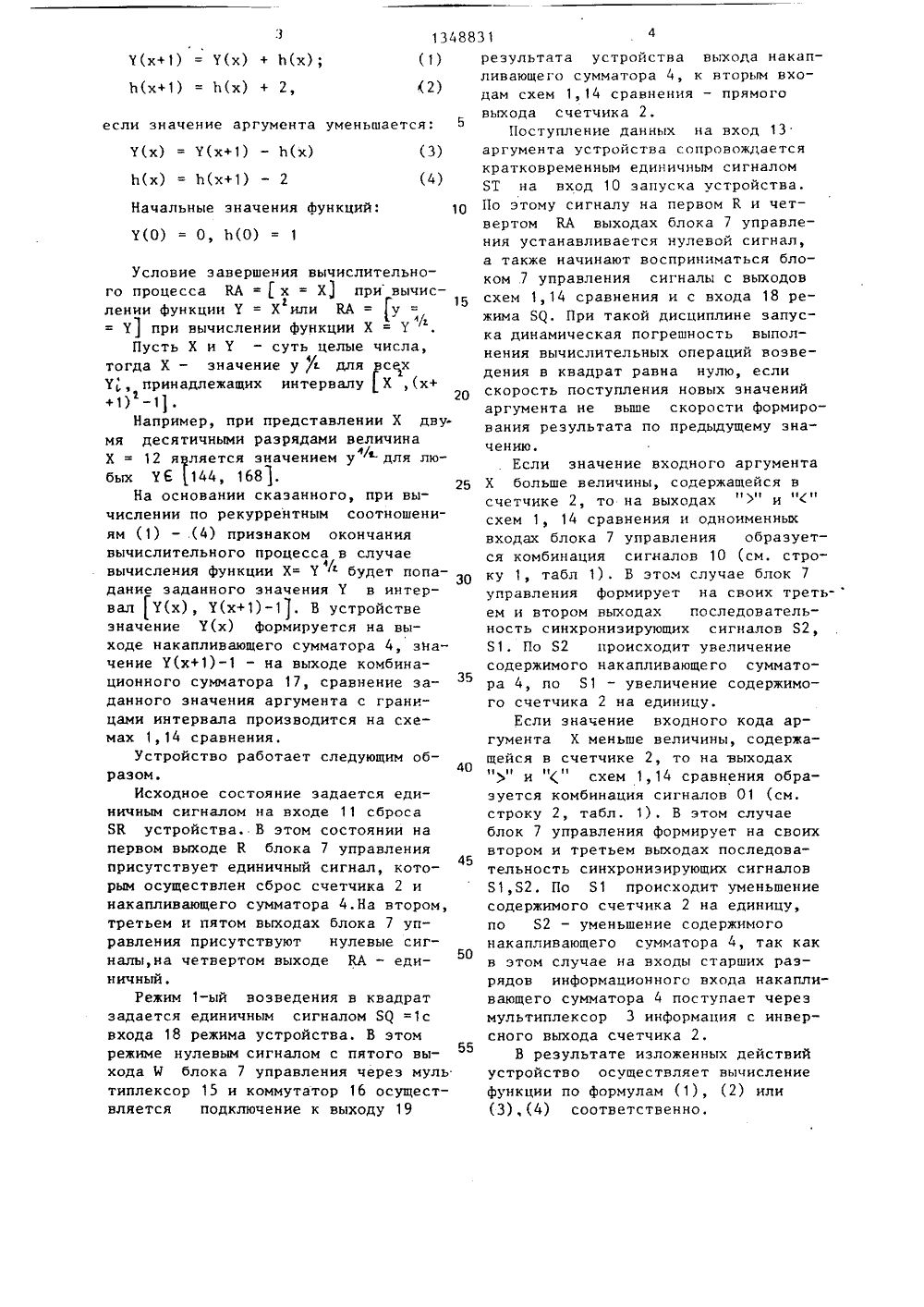

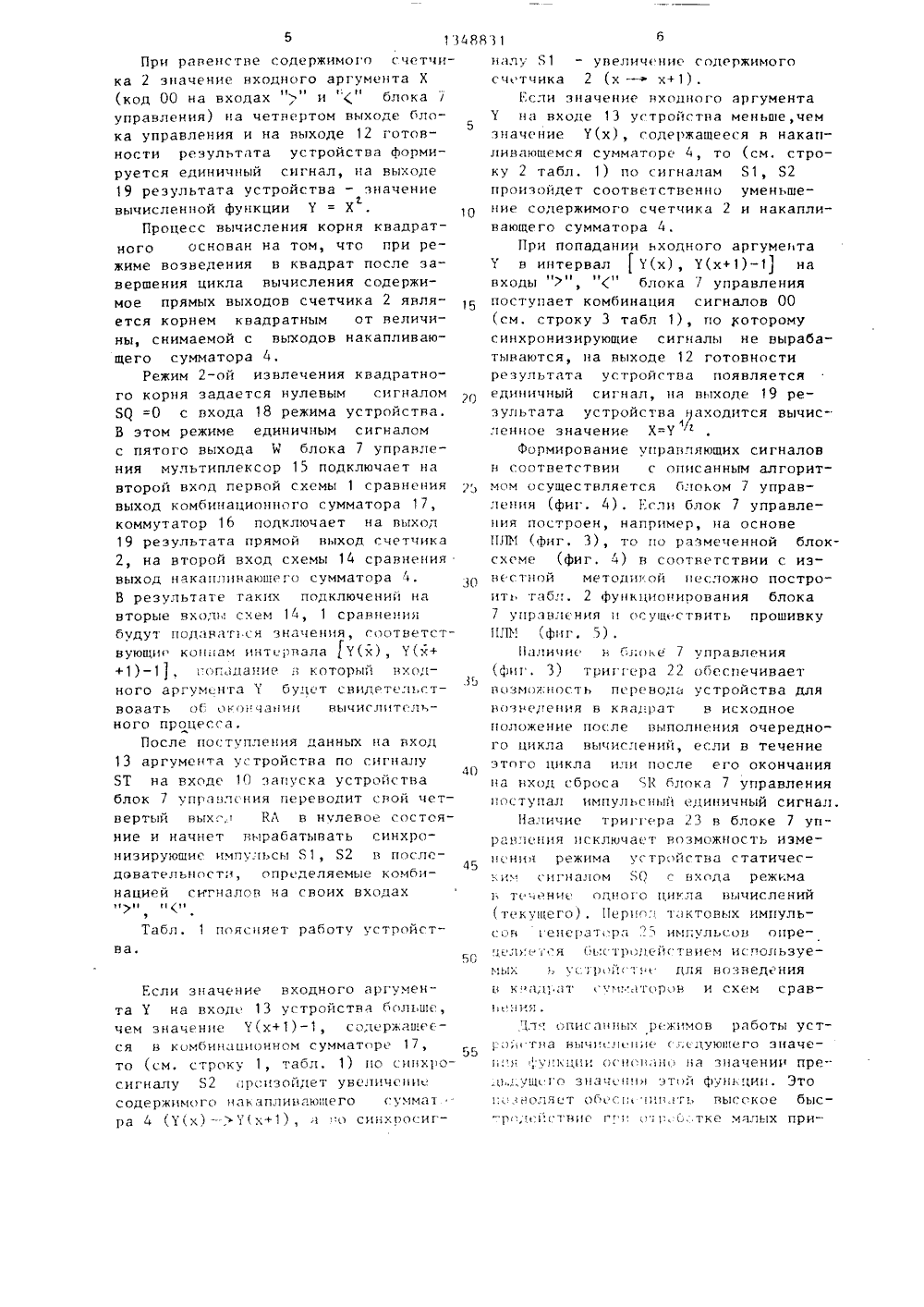

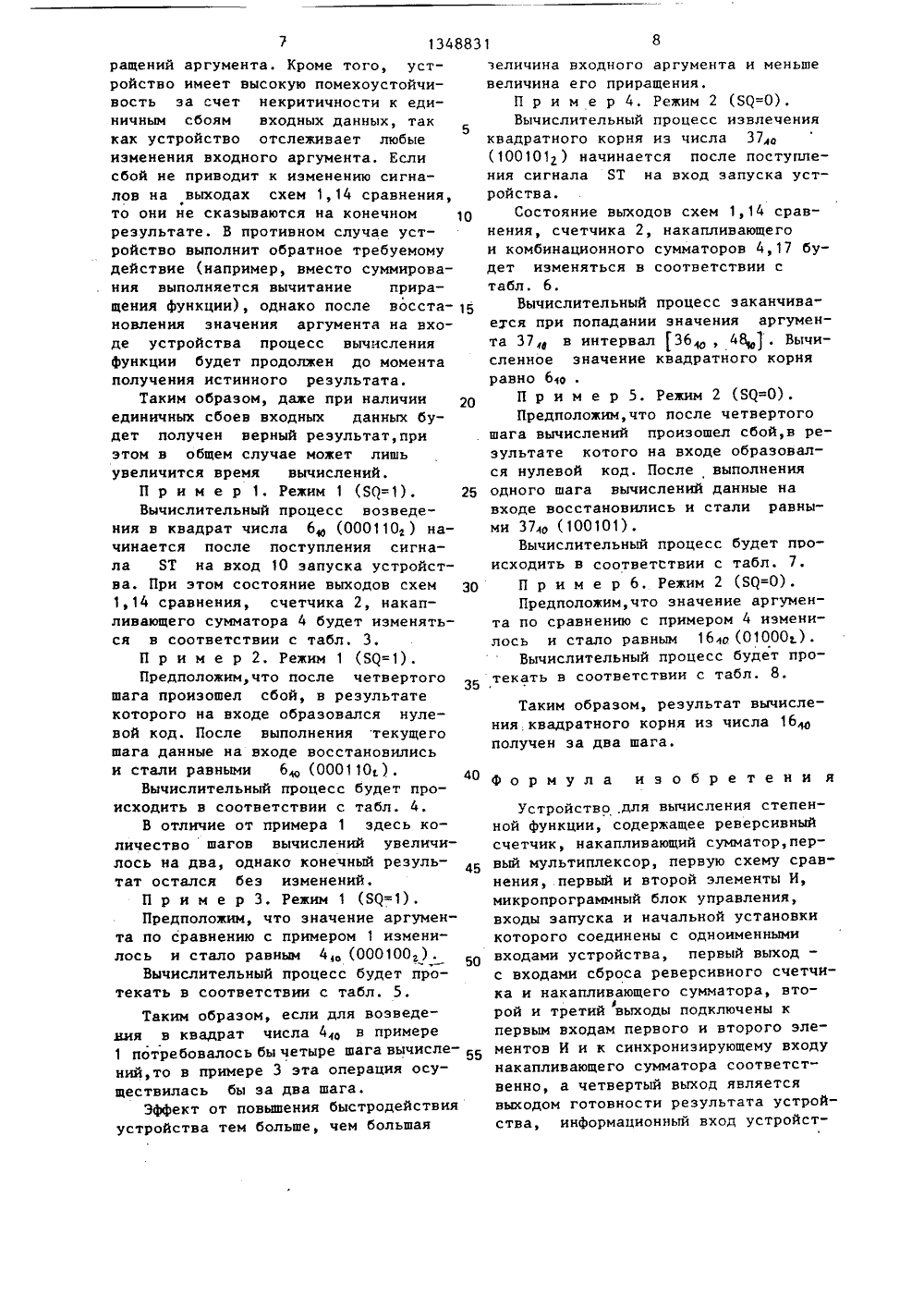

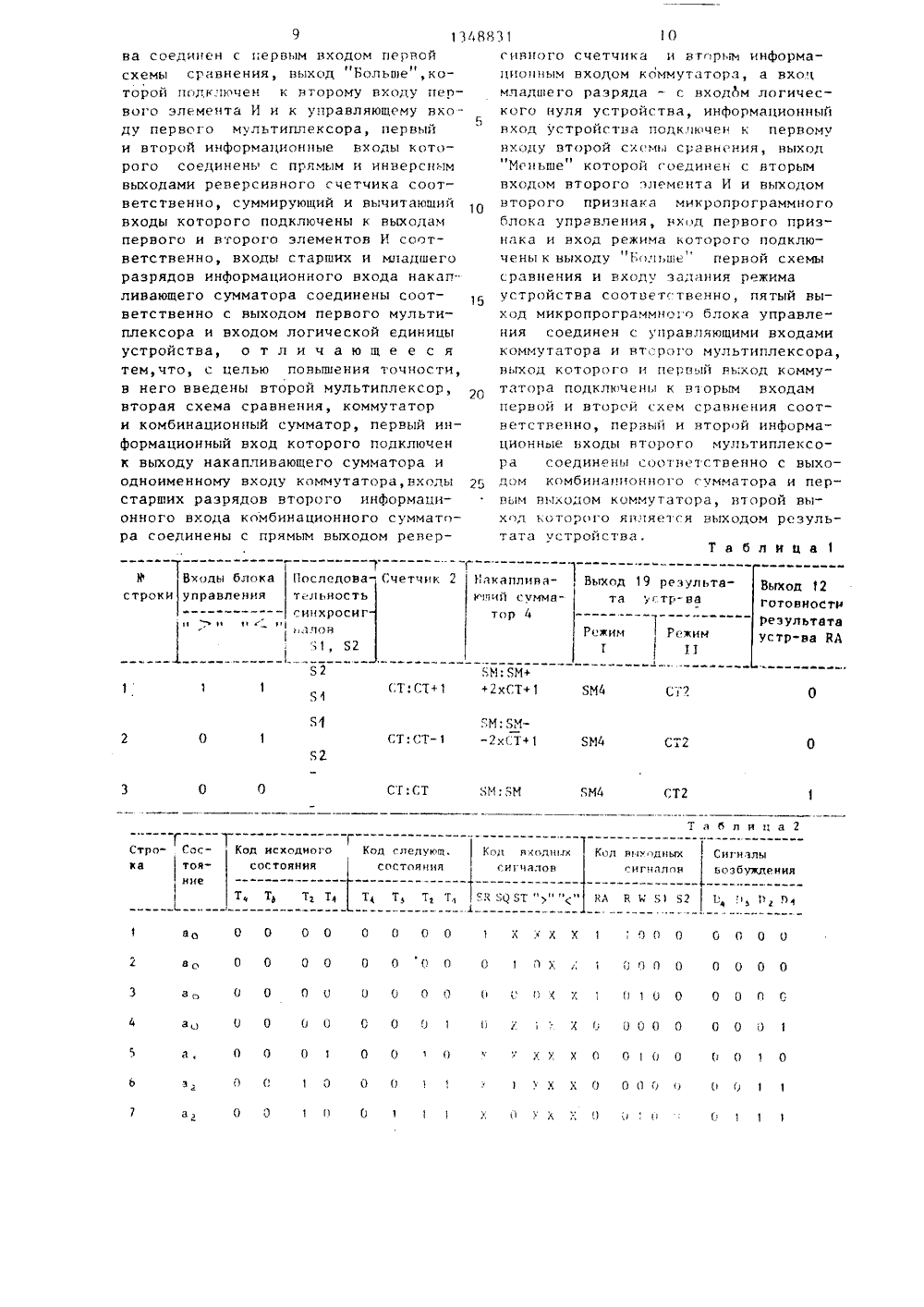

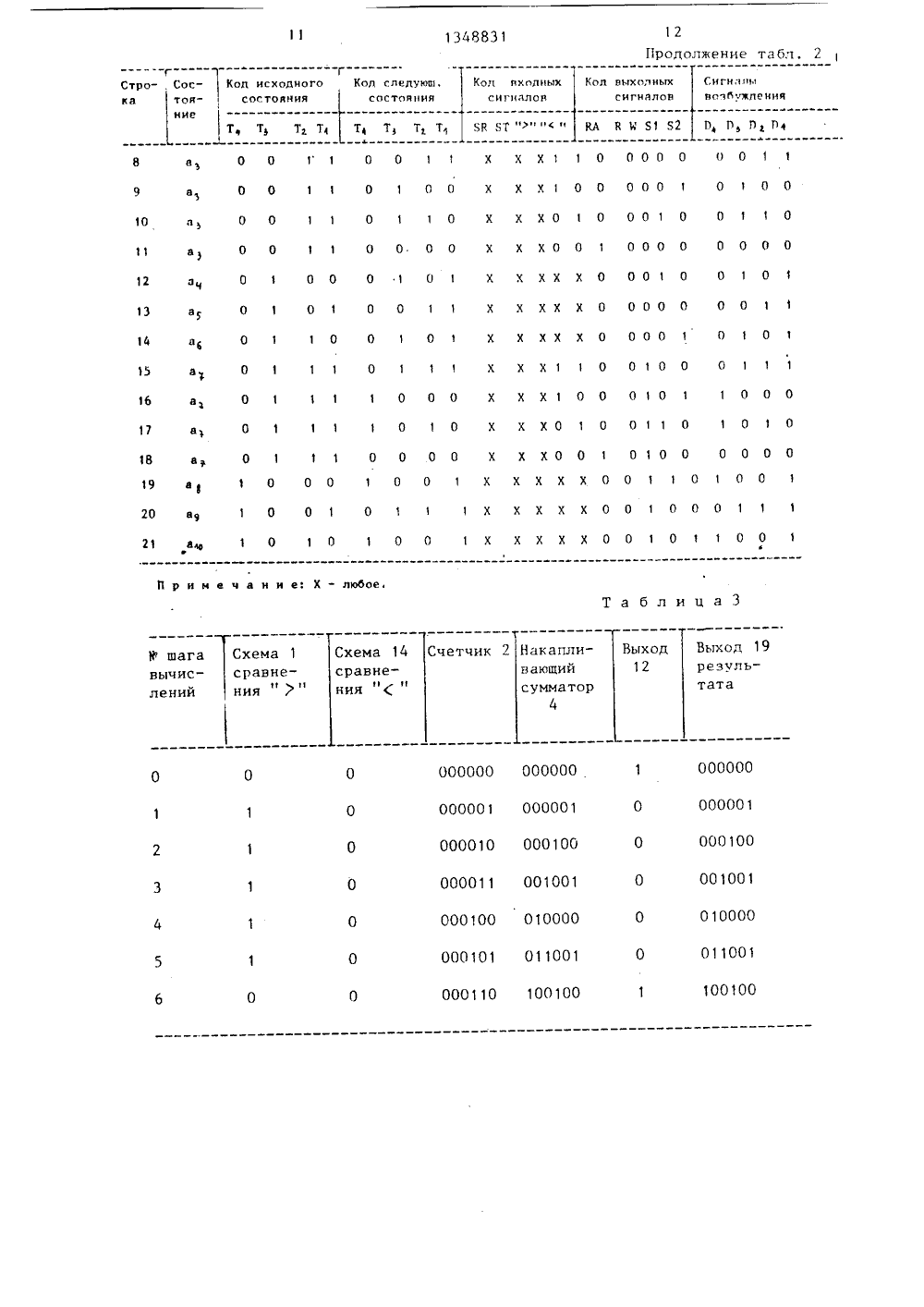

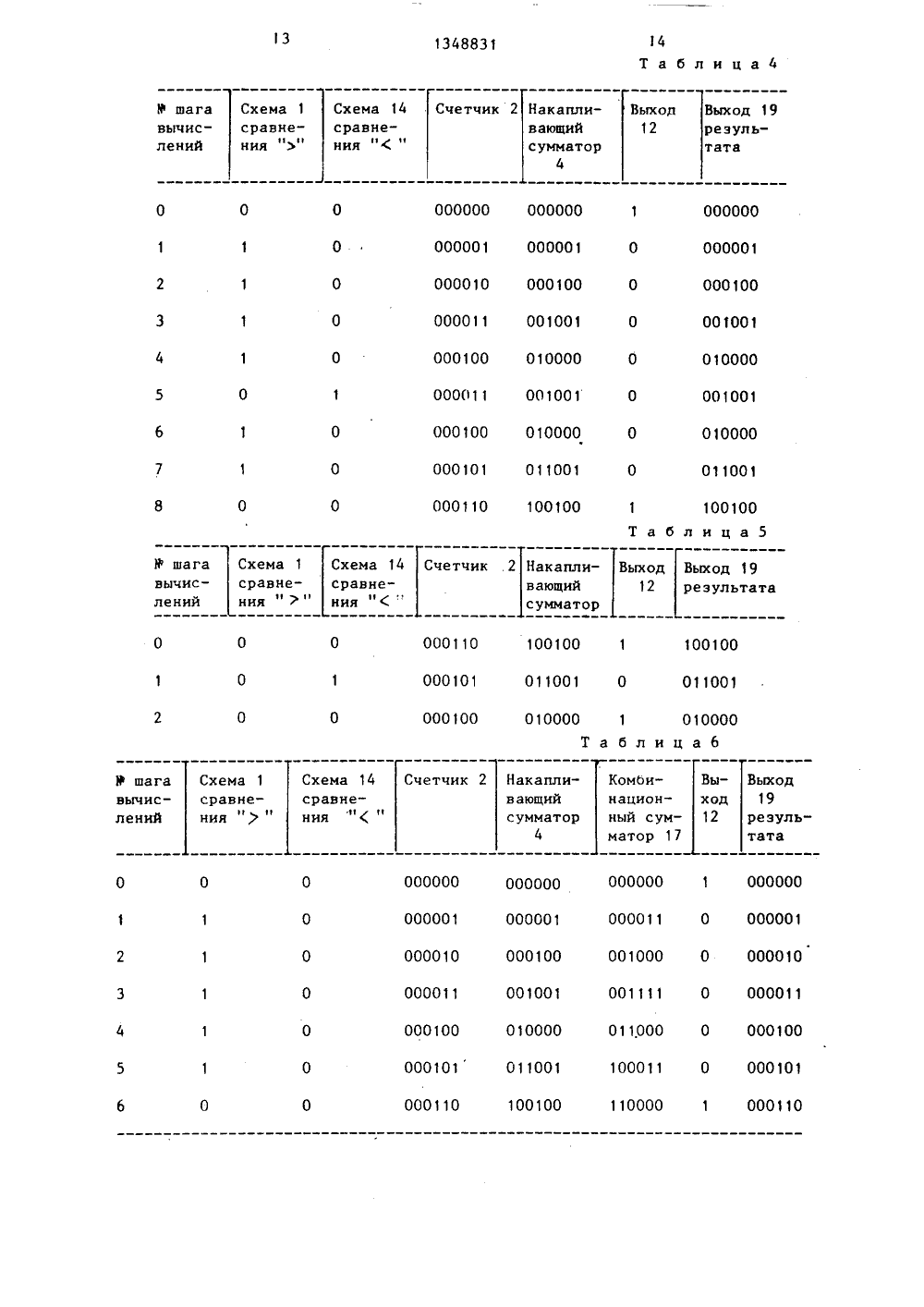

(19) (11) 1)4 С Об Р 7/552 ОПИСАНИЕ ИЗОБРЕТЕНИ ВИДЕТЕЛЬСТВУ К АВТОР чес- Лени екурси 5 ил.,Мь ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(71) Ленинградский электротехникий институт им. В.И.Ульянова (на)(56) Авторское свидетельство СССР1( 1167605, кл. С 06 Р 7/552, 1985.Авторское свидетельство СССРУ 1280616, кл, С 06 Г 7/552, 1985. 54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СТЕННОИ ФУНКЦИИ(57) Изобретение относится к вычисли тельной технике и может быть использовано для аппаратной реализации операций вычисления степенной функции с показателями 2 и 1/2 в универсальных и специализированных вычислителях. Цель изобретения - повышение точности при вычислении функциис показателем 1/2. Поставленнаяцель достигается тем,что в устройство,содержащее схему сравнения 1, счетчик 2, мультиплексор 3, накапливающий сумматор 4, элементы И 5,6,блок7 микропрограммного управления,введены вторая схема сравнения 14,второй мультиплексор 15, коммутатор16 и комбинационный сумматор 17 ссоответствующими связями. Устройствопозволяет вычислять степенные функции с показателями 2 и 1/2 с высокойпомехоустойчивостью и высоким быстродействием при отработке малых приращений аргумента за счет организации р вного процесса вычисления. 8 табл, 1348831. Сло Редак одписно е предприятие, г. Ужгород, ул, 1 роектная,1 роизнодственн полпграфическ аказ 5191/ч 8 Тираж 670 ВНИИ 1 И 1 осударственного комитета СССР по делам изобретений и открь.ий 113035, Москва, Ж, Раушская наб д. ч/13)8831 ЛОЧЕСКО О Н,ничцый вход по)к )у ПЛМ 24.Б качестве тр быт), использовлц сх:ь 11 К 155 ТМ 2, 26 - К 155 И 1 ц Е 5) РТ 2. Г е иг геров 22, 23 могуты, например, микрои к,)честве регистра клчстве ПЛМ 241)л г)р.) 1 мутьсов нных, являфунсции.Е:ИЧИГЛ)з 1;), т;нн)1) И ф.ЦЦ 1 И л;1) л тичоотцошация И) б 1т е и и) т ц о . и т с Я к 1 ) 11 Г л и - тельной т янике и может быть ис польэовлнс для ,ппаратной реализации операций вычисления степенной функции с покаэлте:ем 2 и 1/2 в уциверсальных и специализированных вычислителях.Цель изобретения - повьпнение точности при воспроизведении степеннойфункции с показателем 1/2.Ца фиг. 1 приведена функциональная схема устройства; на фиг, 2вариант реализации коммутатора; цафиг, 3 - вариант схемотехнической 15реализации микропрограммного блокауправления; на фиг. 4 - блок-схемаего работы; на фиг, 5 - прошивкапрограммируемой логической матрицы(ПЛМ) блока управления соответствеццо, 2 С)На схеме устройства (фиг, 1) приняты следующие обозначения; первая схемасравнения, реверсивныйсчетчик 2, первый мультиплексор 3,75накаливангщий сумматор 4, первый 5и второй 6 злсметы И, микропрограммный блок 7 упрлвления, вход 8 логического нуля и вход 9 логическойединицы устройства, входы 10, 11сс)ответствено ьходы запуска и ,)становкц устроиотвл,выход 12 готовности ре э ,.;т лтаНц ),рклционный вход13 уст )оствл, н )рля схема 14срлнцс ция, цторои и)льтиплексор 15,комму гат 1 16, ко)1,цлционн Р сумма- З 6тор 17, вход 18 рсжима и выход 19результата ус.тройства,Все р)ементы устройства могутбыть реапизовлцы нл основе широкоиспольэусмьх в вычислительцой технике микро х и; ; прим р схемы 1, 14сравнсия - нл микрсс омах К 155 СП 1,счетчик 2 в . ц: микросхемах К 155ИЕ 7, к.:мбицлпиоццый сумматор 17 - нлмикросхе. ля К 155 ИГ 13, мультиплексоры 3,15 - на микросхемах К 155 КП 11.Илклпливлн)ший сумматор может быть реллизовлц, наприм-р, цл микросхеме 802 ИМ 1 путс.м подключения выхода с,мматорл нл его свобогный вх),.Му ) - 5 О типлексоры 3,1 подклн)чают ца выход свой первый или второй информационные вхс);п при наличии на управ.)нющем входе соотцет;твенно единичцсНу:;ЕВО) О СИГНЛ:Л, Варнацт рс:Л 111 Л -Ъции коммутлторл 16, цлпример, цлмикросхемах Е 155 КП 11 пригеденфиг, 2. К,ммутлтор со;тержит му.втиплек орь 21 и 21. При нулевом с 1; -цлле цл упрлцлянш)ем цх Не к)мму глторл 16 ео первый 1 вт 1)ой ицф рмлцио)Ные входы по,к;к)ч ны соотнетстенцо к его и рному и второму выходам,При ЕдицИЧНС)М с.ц НЛЛЕ НЛ у)ранпяЮщЕМ вхсще - соотн т "нецо к второму и первому выхо;лм. 1)лок 7 упрлвления содержит первый 22 и второй 23 триггеры,ПЛМ 24, гс-нерлт р 25 импульсов и регистр 26, сикропиирук)щий вход которого связлнвыходом генератора 25 импульсов, первый - четвертый информационные вх.ы . одключены на первый - четвертый выходы ПЛМ 24 соответственно, а первый - четвертый выходы на первый - четвертый входы ПЛМ соответственно, пятый - седьмой входы ко)т о р о й я вляют с я ц ход лми с , ) , э а- пуска 8 Т блока 7 у 11 р л нл е ния со о тв етств е ц н о , пятый - д е ц я тый выходы являются первым - пятым выходами К , 8 1 , 8 2 , ВЛ , Ы блока 7 у п р л вл е ни я с о отв е тс тв е ц н овосьмой ц х од ГМ 2 4 подключен к и ц в е р с цом у ых од у ир в о г о триггера2 , л де л я тый - к 1. ям ом у выходу К)второго риггсрл 23, Синхронизирующий вход триггс рл 23 соелицен с девя) ым выходом ПЛМ . , ормлционный вход - с вх)г )м р жмл 811 блока 7 управ:ения. . цх)оц)эирующий вход тр:г с рл 22 .,)Н ) с входом сброса Б бл )к7 управления, ин - ф)рмсцеоный ).)Ходом 8 я; стр иствл, а едицкц к пятому выхо 1;жс т бьть ,)бр 111, н рир, на основ: икросхем К 1) 5):1 А 3. Елботл , с:тр й 11 о н звана . лре 1)снц)м11)обе ос лниЯ )ВлдР Г)11 О 1) РУ.К 11 Ц 1: Л).)11)ЧЛ 1.ЯВЫ чис:1 ии по рс 11 н г 11 с о тнсше)иЯм о .сДу)Цх ) )11 чН 1 функ)ии дл л.л 1)ог )1)уь ) ) ., ). ли и 11 естно ПР,Ь)ДУЦЛ;Н в Ъ)1 КЦР 1 И. 1 Е: УР 1) ) ) ,1.1 ц,)11:1 я од)сЯ)сяются 1 рупгы, ;л,.1, я : з которых учи" и . я )цл).ц; )1ь;.На 1, .)111 1)л 1; .)Р .:" ц л(1) У(х+1) = У(х) + Ь(х);Ь(х+1) = Ь(х) + 2,(2) если значение аргумента уменьшается: 5 У(х) = у(х+1) - Ь(х)Ь(х) = Ь(х+1) - 2(4) Начальные значения функций: 10У(0) = О, Ь(0) = 1 Условие завершения вычислительного процесса ВА = х = Х при вычислении функции У = Х или ВА = У1 Г 15/ = У при вычислении функции Х = УПусть Х и У - суть целые числа, тогда Х - значение у а для всех4/У, принадлежащих интервалуХ ,(х+ +1) - 11 .20Например, при представлении Х двумя десятичными разрядами величина Х = 12 является значением у ф для любых Уб 144, 1681.На основании сказанного, при вычислении по рекуррентным соотношениям (1) - .(4) признаком окончания вычислительного процесса в случаей/вычисления функции Х= У " будет попа 30 дание заданного значения У в интервел у(х), Т(х+1)-1. В устройстве значение У(х) формируется на выходе накапливающего сумматора 4, значение У(х+1)-1 - на выходе комбинационного сумматора 17, сравнение заданного значения аргумента с границами интервала производится на схемах 1,14 сравнения.Устройство работает следующим образом.Исходное состояние задается единичным сигналом на входе 11 сброса БК устройства. В этом состоянии на первом выходе К блока 7 управления присутствует единичный сигнал, кото 45 рым осуществлен сброс счетчика 2 и накапливающего сумматора 4.На втором, третьем и пятом выходах блока 7 управления присутствуют нулевые сигналы,на четвертом выходе ВА - еди 50 ничный.Режим 1-ый возведения в квадрат задается единичным сигналом БЯ =1 с входа 18 режима устройства. В этом режиме нулевым сигналом с пятого выхода Ч блока 7 управления через муль типлексор 15 и коммутатор 16 осуществляется подключение к выходу 19 31результата устройства выхода накапливающего сумматора 4, к вторым входам схем 1,14 сравнения - прямого выхода счетчика 2.Поступление данных на вход 13 аргумента устройства сопровождается кратковременным единичным сигналом ЯТ на вход 10 запуска устройства. По этому сигналу на первом К и четвертом КА выходах блока 7 управления устанавливается нулевой сигнал, а также начинают восприниматься блоком .7 управления сигналы с выходов схем 1,14 сравнения и с входа 18 режима БЯ. При такой дисциплине запуска динамическая погрешность выполнения вычислительных операций возведения в квадрат равна нулю, если скорость поступления новых значений аргумента не выше скорости формирования результата по предыдущему эначению.Если значение входного аргументаХ больше величины, содержащейся всчетчике 2, то на выходах и "("схем 1, 14 сравнения и одноименныхвходах блока 7 управления образуется комбинация сигналов 10 (см. строку 1, табл 1). В этом случае блок 7управления формирует на своих треть-ем и втором выходах последовательность синхронизирующих сигналов 52,51. По 52 происходит увеличениесодержимого накапливающего сумматора 4, по 81 - увеличение содержимого счетчика 2 на единицу,Если значение входного кода аргумента Х меньше величины, содержащейся в счетчике 2, то на выходах")" и "(" схем 1,14 сравнения образуется комбинация сигналов 01 (см.строку 2, табл. 1), В этом случаеблок 7 управления формирует на своихвтором и третьем выходах последовательность синхронизирующих сигналов51,52. По 51 происходит уменьшениесодержимого счетчика 2 на единицу,по 82 - уменьшение содержимогонакапливающего сумматора 4, так какв этом случае на входы старших разрядов информационного входа накапливающего сумматора 4 поступает черезмультиплексор 3 информация с инверсного выхода счетчика 2,В результате изложенных действийустройство осуществляет вычислениефункции по формулам (1), (2) или1 О 15 О 40 45 ва. гсдуюшего зцачео ца зцачении претой функции. Этоцть выгокое быс,сь,ущс га зцач.глац з ц. цепляет обс сцс пп При равецстве содержимого счетчика 2 значение входного аргумента Х(код 00 на входахи ( блокауправления) ца четвертом выходе блока управления и на выходе 12 готовности результата устройства формируется единичный сигнал, ца выходе19 результата устройства - значениевычисленной функции У = ХПроцесс вычисления корня квадратного основан на том, что при режиме возведения в квадрат после завершения цикла вычисления содержимое прямых выходов счетчика 2 является корнем квадратным от величины, снимаемой с выходов накапливающего сумматора 4.Режим 2-ой извлечения квадратного корня задается нулевым сигналомБЯ =0 с входа 18 режима устройства.В этом режиме единичным сигналомс пятого выхода 4 блока 7 управления мультиплексор 15 подключает навторой вход первой схемы 1 сравнениявыход комбинационного сумматора 17,коммутатор 16 подключает на выход19 результата прямой выход счетчика2, на второй вход схемы 14 сравнения .выход накаплицаюшгго сумматораВ результате таких подключений цавторые входы схем 14, 1 сравнениябудут подаватгся значеция, гоответствующгц концам интервала У(х), У(.с++1)-1, ног,;ггацие ц который входного аргумента У будет свидетельствовать об окончании вычиглитглт -ного процесс а,После поступления данных ца вход13 аргумента устройства по сигналу8 Т на входе 10 запуска устройстваблок 7 управлсния переводит свой четвертый выхг, КЛ в нулевое состояние и начнет вырабатывать синхронизируюшие импу:гьсы 81, Я 2 в последовательности, определяемые комбинацией сигналов ца гвоих входахффю г (ффЪТабл, 1 поясняет работу устройстЕсли значение входного аргумента У на входс 13 устройства больше, чем значение У(х+1) - 1, содержащееся в комбинационном сумматоре 17, то (см, строку 1, табл. 1) по синхросигналу 82 цризойдет уве.шчс цис содержимого накапливающего суммат ра 4 (У(х) . У 1 х+1), . о сихоосигцалу 81 - увеличение годержимого гчс тчика 2 (х - х+1),Если значение входного аргумента У ца входе 13 угтройстна меньше,чем значение У(х), годержащееся в накапливающемся сумматорс 4, то (см. строку 2 табл, 1) по сигналам 81, 82 произойдет соответственно уменьшение содержимого счетчика 2 и накапливающего сумматора 4.При попадании ьходного аргумента У в интервалУ(х), У(х+1) - 1 на входы ) , ( блока 7 управления поступает комбинация сигналов 00 (см. строку 3 табл 1), по которому синхронизирующие сигналы не вырабатываются, ца выходе 12 готовности результата устройства появляется единичный сигнал, ца выходе 19 результата устройства аходится вычис 1/2ленное значение Х=УФормирование управляющих сигналов ц соответствии с описанным алгоритмом осуществляется блоком 7 управления (фиг, 4). Если блок 7 управления построен, например, ца основе П 1311 (фиг, 3), то по размеченной блоксхеме (фиг. 4) н соответствии с известной методикой несложно построить табл. 2 функционирования блокауправления ц осущсствить прошивку 11% (фгг. 5) .Наличис ц блоке 7 управления (фцг. 3) триггера 22 обеспечивает возможность псревода устройства для возцсдеция в квацрат в исходное положение после гзыполнеция очередного цикла вычислений, если в течение этого цикла или после его окончания ца вход сброса сН блока 7 управления поступал импульсный единичный сигнал.Наличие триггера 23 в блоке 7 управления исключает возможность изменения режима устройства статическим сигналом 50 с входа режиматсчс.ние одного цикла вычислений (текущего), 11 ери . тактовых импульсов генерат ра 25 имгульсов опреполке я оыгтродсцгтнием используемых ь ус;рс й тцс для возведния в к д 1,ат г.мматс ров и схем срав(счин1 л; описанных рсжимов работы устро;ц тца нычиолсцсцс уцкггии ос ц ццц134ращений аргумента. Кроме того, устройство имеет высокую помехоустойчивость за счет некритичности к единичным сбоям входных данных, таккак устройство отслеживает любыеизменения входного аргумента. Еслисбой не приводит к изменению сигналов на выходах схем 1,14 сравнения,то они не сказываются на конечномрезультате. В противном случае устройство выполнит обратное требуемомудействие (например, вместо суммирования выполняется вычитание приращения функции), однако после восстановления значения аргумента на входе устройства процесс вычисленияфункции будет продолжен до моментаполучения истинного результата.Таким образом, даже при наличииединичных сбоев входных данных будет получен верный результат,приэтом в общем случае может лишьувеличится время вычислений.П р и м е р 1. Режим 1 (Я=1).Вычислительный процесс возведения в квадрат числа 6 (000110 ) начинается после поступления сигнала БТ на вход 1 О запуска устройства. При этом состояние выходов схем1,14 сравнения, счетчика 2, накапливающего сумматора 4 будет изменяться в соответствии с табл, 3,П р и м е р 2. Режим 1 (Я=1).Предположим,что после четвертогошага произошел сбой, в результатекоторого на входе образовался нулевой код. После выполнения текущегошага данные на входе восстановилисьи стали равными 6+, (000 10) .Вычислительный процесс будет происходить в соответствии с табл. 4.В отличие от примера 1 здесь количество шагов вычислений увеличилось на два, однако конечный результат остался беэ изменений,П р и м е р 3. Режим 1 (Б 0=1).Предположим, что значение аргумента по сравнению с примером 1 изменилось и стало равным 4 (000100).Вычислительный процесс будет протекать в соответствии с табл. 5. 8831 Формула Устройство для вычисления степенной функции, содержащее реверсивныйсчетчик, накапливающий сумматор,пер вый мультиплексор, первую схему сравнения, первый и второй элементы И,микропрограммный блок управления,входы запуска и начальной установкикоторого соединены с одноименнымивходами устройства, первый выход -с входами сброса реверсивного счетчика и накапливающего сумматора, второй и третий выходы подключены кпервым входам первого и второго элементов И и к синхронизирующему входунакапливающего сумматора соответственно, а четвертый выход являетсявыходом готовности результата устройства, информационный вход устройстТаким образом, если для возведения в квадрат числа 4 щ в примере 1 потребовалось бы четыре шага вычислений,то в примере 3 эта операция осуществилась бы за два шага.Эффект от повышения быстродействия устройства тем больше, чем большая величина входного аргумента и меньшевеличина его приращения.П р и м е р 4. Режим 2 (БЯ=О).5Вычислительный процесс извлеченияквадратного корня из числа 37(100101) начинается после поступления сигнала ЯТ на вход запуска устройства.Состояние выходов схем 1,14 сравнения, счетчика 2, накапливающегои комбинационного сумматоров 4,17 будет изменяться в соответствии стабл. 6.Вычислительный процесс заканчивается при попадании значения аргумента 37, в интервал 36.ю, 48 ю, Вычисленное значение квадратного корняравно 6 о .П р и м е р 5. Режим 2 (ЯЯ=О).Предположим,что после четвертогошага вычислений произошел сбой,в результате котого на входе образовался нулевой код. После выполнения 25 одного шага вычислений данные навходе восстановились и стали равными 37.ю (100101).Вычислительный процесс будет происходить в соответствии с табл. 7.30 П р и м е р Ь. Режим 2 (БЦ=О).Предположим,что значение аргумента по сравнению с примером 4 изменилось и стало равным 16 о (ООООЙ)Вычислительный процесс будет протекать в соответствии с табл. 8. Таким образом, результат вычисления квадратного корня из числа 16 д получен за два шага. и з о б р е т е н и я13 Таблица1 оспедова Счетчиктельностьсихросигалов Накаплива Выход 11 Входы блокастроки управления 19 реэультаустрват Выход 12 готовности реэультвтаустр-ва КД юв)ий суммА" тор 4 та Режим 1Сигналыьоэбуждения состояния иие Т Т Т Т Т Т т Эк ьо Зткт к5 я 2 н; ) 1 т,О О О О ОООО)ХХХХ 1)ООООООО 0 0 0 0 0 0 О О О 0 0 О О О 0 0 О 0 О О 0 0 О 1 о Ао) ) Х Х О ООО ) О О 1 1 О О У Х Х 0 О 1 1 1 а ва соединен серным входом первой11 11 схемы сравнения, выход Больше ,которой пгдк:)очен к второму входу пепвого элемента И и к управляющему входу первого мультиплексора первый и второй информационные входы которого соединень с прямым и инверсным выходами реверсивного счетчика соответственно, суммирующий и вычитающий входы которого подключены к выходам первого и второго элементов И соответственно, входы старших и младшего разрядов информационного нхода накапливающего сумматора соединены соответственно с выходом первого мультиплексора и входом логической единицы устройства, о т л и ч а ю щ е е с я тем,что, с целью повышения точности, в него введены второй мультиплексор, вторая схема сравнения, коммутатор и комбинационный сумматор, первый информационный вход которого подключен к выходу накапливающего сумматора и одноименному входу коммутатора,нходы старших разрядов второго информационного входа комбинационного сумматора соединены с прямым выходом ревер 48831 1 О сиплого счетчика и вторым информациоым входом коммутатора а вход младшего разряда - с входм логического нуля устройства, информационный 5вход устройства подк)ючен к первому входу второй схсмь) сравн( ния, выход "Меньше которой соедине с вторым входом второго элемента И и выходом второго признака микропрограммного блока управления, вход первого признака и вход режима которого подключены к выходу Б.1)ьшео первой схемы сравнения и входу задания режима устройства соответственно, пятый выход микропрограммного блока управления соединен с упранляющими входами коммутатора и вт;рого мультиплексора,ныход которого и первый выход коммутатора подключены к нторым входам первой и второй схем сравнения соответственно, первый и второй информационн)е входы второго мультиплексора соединены соотетственно с выхо 20 дом комбинаиионного сумматора и первым выходом коммутатора, второй выход котор(го является выходом результата устройства. 010 ХХ 100000000О О ) х х 1 О 1 О 0 0 0 и 012 1348831 Продолжение табл. 2 Г Коп слепуюп 1. состояния Г Стро-, Сосна тояКод исходного состоянияСигнввывочбумления ние КА К51 52 т, т,Вя т нон н т, т т, т, т, т О, Л,П,О о о г Ооо О О О 1 о о 0 1 О О Х Х Х 1 О О ООО 1 0О О 0 Х Х ХоО ОО 1 О О 1 1 О О 0 0 О О О 1 1 О О О О Х Х ХО 0 1 Ооо О 0 0 0 ОО 1 О 0 0 1 ОХ Х ХХ Х О О 01 О О 1 0О О О 1 1 О О 1 О 1 Х Х ХХ Х О ООО 1 О 1 О о Х Х Х 1 1 О О 1 О О О О 1 1 1 О О 1 11 1 О О О Х Х Х 1 О О О 1 О 1 1 О О О О 1 О Х Х ХО 1 О О 11 О 1 О 1 О о О 1 1 1 О О О О Х Х Хо О 1 О 1О О О 1 О О 1 Х Х Х Х Х О О 1 1 О 1 О О 1 О О 1 О 1 1 1 Х Х Х Х Х 0 О 1 О О О 1 10 1 О 1 0 О 1 Х Х Х Х Х О 0 1 О 1О 0 П р и и е ч а н н е: Х - любое,Та блица 3 Выход 19 резуль- тата Счетчик 2 Схема 14 Выход 12Накапливающий Схема 1 У шага сравнения(сравнения ) вычис лений сумматор 4Счетчик 2 В шага Схема 1сравнения инаваюций ционный сравнения "(" вычислений сумматор 4

СмотретьЗаявка

4078351, 17.06.1986

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

ВАЛОВ АЛЕКСАНДР АЛЕКСАНДРОВИЧ, ВИТКИН ЛЕВ МИХАЙЛОВИЧ, ГЕРАСИМОВ ИГОРЬ ВЛАДИМИРОВИЧ, КУБОВЭ МИРОСЛАВ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, степенной, функции

Опубликовано: 30.10.1987

Код ссылки

<a href="https://patents.su/12-1348831-ustrojjstvo-dlya-vychisleniya-stepennojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления степенной функции</a>

Предыдущий патент: Устройство для вычисления синуса и косинуса угла табличным методом

Следующий патент: Устройство для вычисления экспоненциальной функции

Случайный патент: Устройство для контроля хода программы