Зонд для проверки сигналов цифровых микросхем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1348759

Автор: Кордюмов

Текст

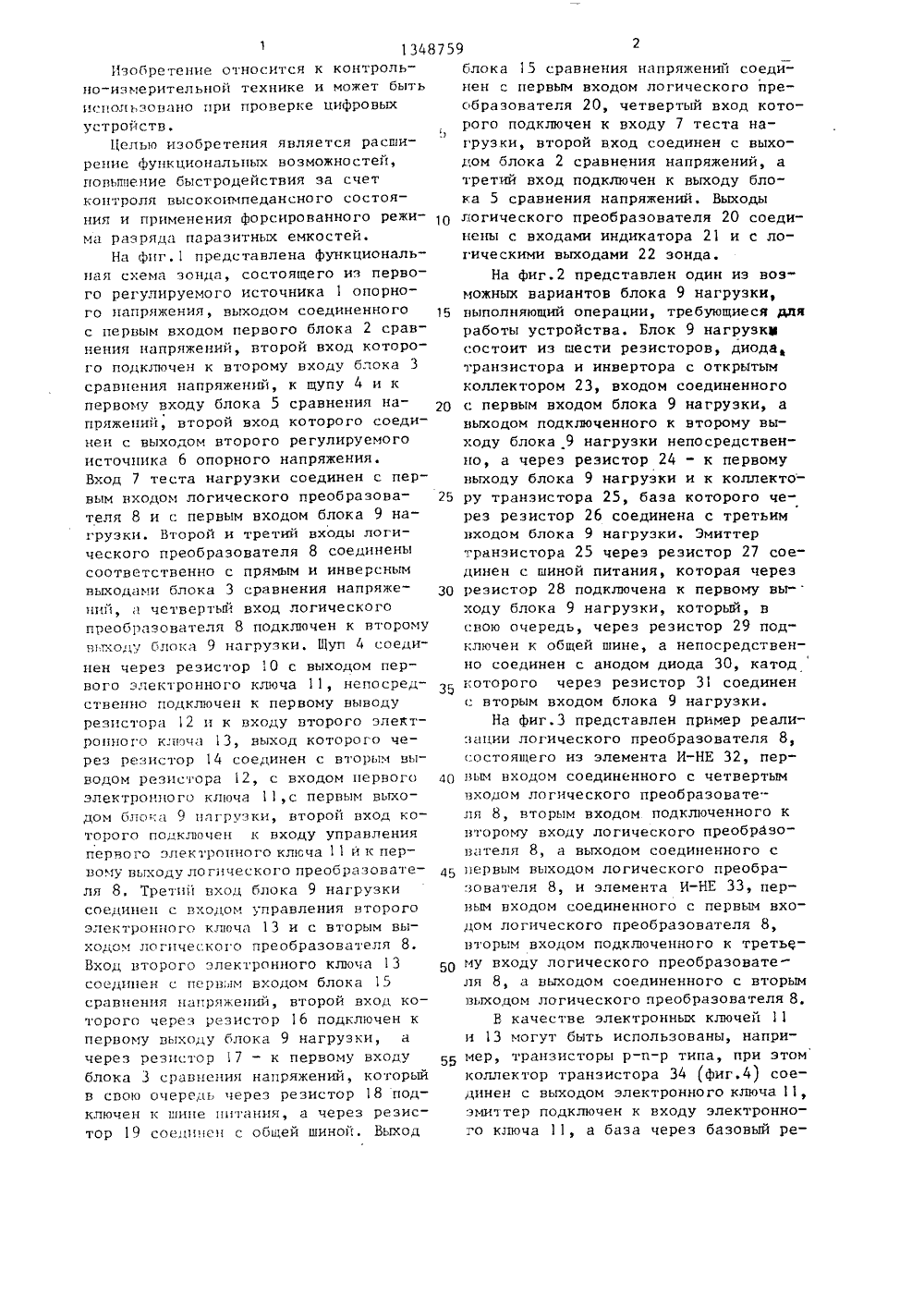

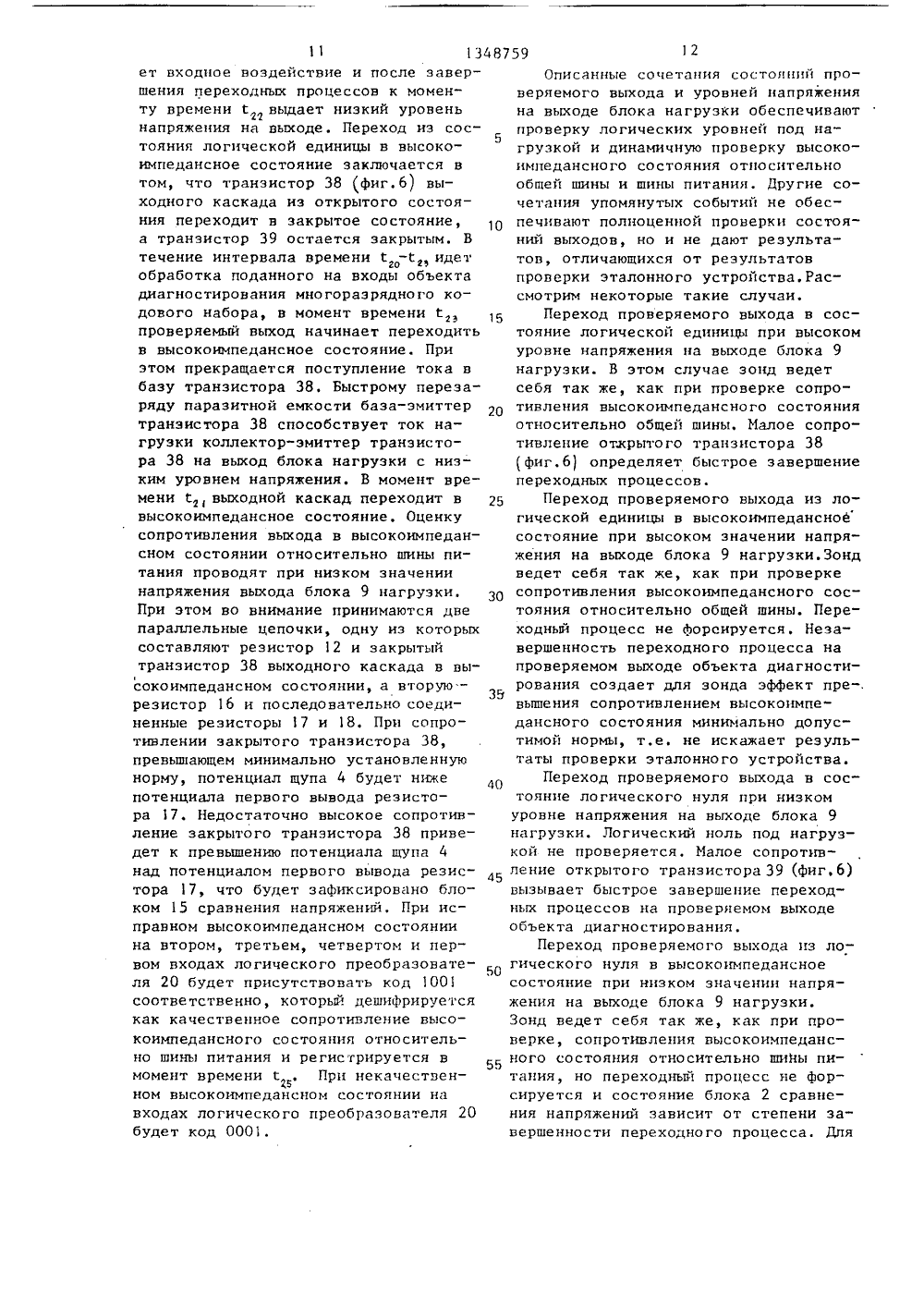

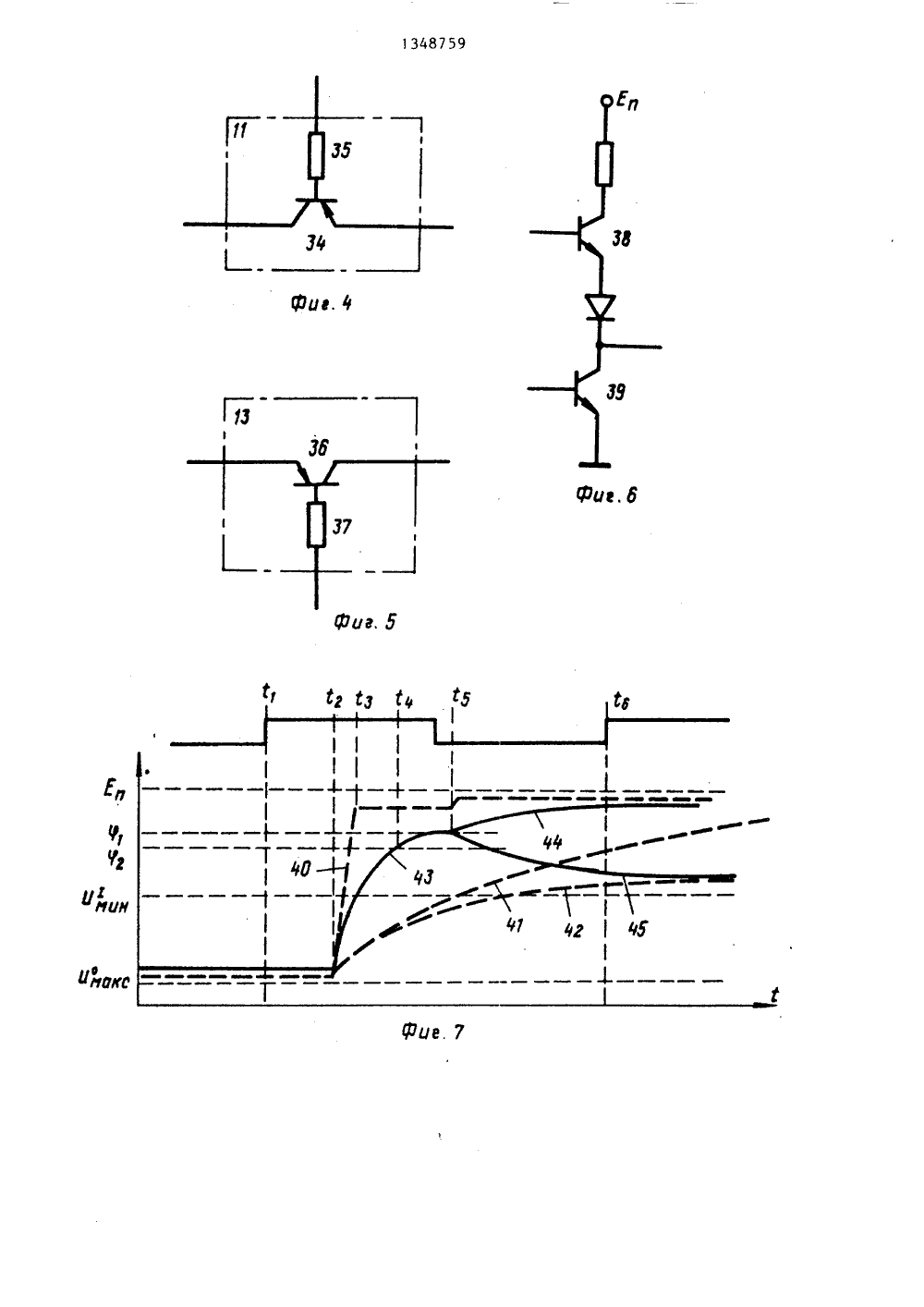

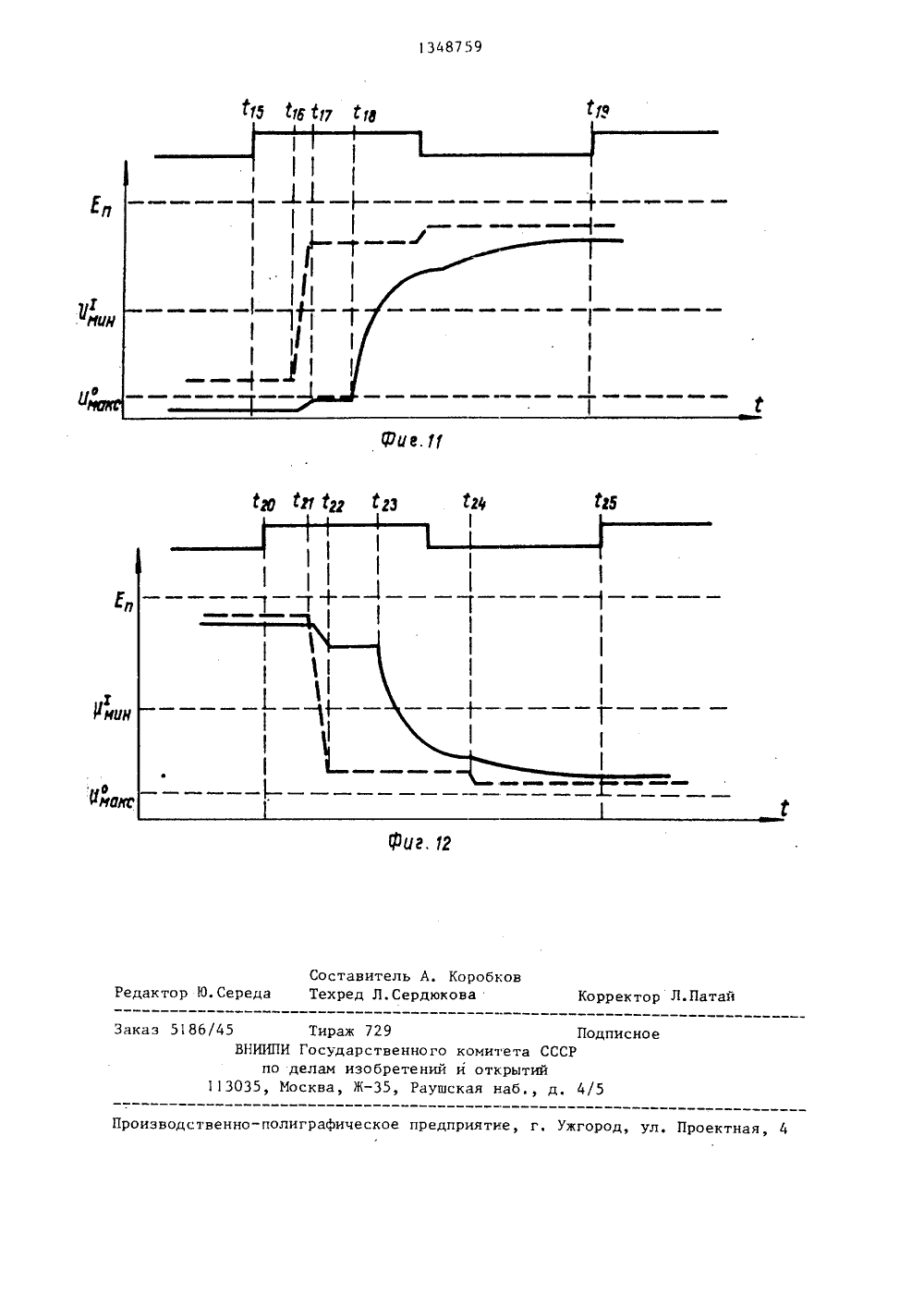

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК БО 1348759 А 1(50 4 С 01 К 31/28 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(46) 30,10.87. Бюл. У 40 (71) Харьковский политехнический институт им. В.И.Ленина(53) 621.317.799 (088.8) (56) Авторское свидетельство СССР У 1228055, кл. С 01 К 31/28, 1985.Авторское свидетельство СССР У 513330, кл. С 01 К 31/28, 1974.(54) ЗОНД ДЛЯ ПРОВЕРКИ СИГНАЛОВ ЦИФРОВЫХ МИКРОСХЕМ(57) Изобретение позволяет расширитьфункциональные воэможности устройства и повысить его быстродействие.Устройство содержит регулируемые источники 1 и 6 опорного напряжения,блоки 2, 3 и 5 сравнения напряжений,логический преобразователь 8, резистор 10 и индикатор 21. Введение блока 9 нагрузки, электронных ключей 11и 13, блока 15 сравнения напряжений,логического преобразователя 20 и резисторов 12, 14, 16-19 позволяетконтролировать высокоимпедансное состояние и применить форсированный режим разряда паразитных емкостей,12 ил. ОПИСАНИЕ ИЗОБРЕТЕНИЯ:Фи Составитель А. КоробковТехред Л.Сердюкова едактор 1 О.Сере аи оррек каз 5186/4 Тираж 729 Государстведелам изобреосква, Ж,одписно ВНИИП ого комитета СССний и открытий 13 4/ ушская на оизводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 1134Изобретение относится к контрольно-измерительной технике и может быть использовано при проверке цифровых устройств.Целью изобретения является расширение функциональных возможностей, повышение быстродействия за счет контроля высокоимпедансного состоя - ния и применения форсированного режима разряда паразитных емкостей.На фцг.1 представлена функциональная схема зонда, состоящего иэ первого регулируемого источника 1 опорного напряжения, выходом соединенного с первым входом первого блока 2 сравнения напряжений, второй вход которого подключен к второму входу блока 3 сравнения напряжений, к щупу 4 и к первому входу блока 5 сравнения напряжении, второй вход которого соединен с выходом второго регулируемого источника 6 опорного напряжения.Вход 7 теста нагрузки соединен с первым входом логического преобразователя 8 и с первым входом блока 9 нагрузки. Второй и третий входы логического преобразователя 8 соединены соответственно с прямым и инверсным выходами блока 3 сравнения напряжеццй, а четвертый вход логического преобразователя 8 подключен к второму мдходу блока 9 нагрузки. Щуп 4 соединен через резистор 10 с выходом первого электронного ключа 11, непосредственно подключен к первому выводу резистора 12 ц к входу второго электронного ключа 13, выход которого через резистор 14 соединен с вторым выводом резистора 12, с входом первого электронного ключа 11,с первым выходом блока 9 пагруэки, второй вход которого подключен к входу управления первого электроццого ключа 1 и к первому выходулогцческого преобразователя 8Третий вход блока 9 нагрузки соединен с входом управления второго электронного ключ 13 и с вторым выходом логического преобразователя 8, Вход второго электронного ключа 13 соединен с первым входом блока 15 сравнения напряжений, второй вход которого через резистор 16 подключен к первому выходу блока 9 нагрузки, и через резистор 17 - к первому входу блока 3 сравнения напряжений, который в свою очередь через резистор 18 подключен к шцце питания, а через резистор 19 соединен с общей шиной. Выход8759 10 15 20 25 30 35 40 45 50 55 блока 15 сравнения напряжений соединен с первым входом логического преобразователя 20, четвертый вход которого подключен к входу 7 теста нагрузки, второй вход соединен с выходом 5 лока 2 сравнения напряжений, а третий вход подключен к выходу блока 5 сравнения напряжений, Выходы логического преобразователя 20 соединены с входами индикатора 21 и с логическими выходами 22 зонда.На фиг.2 представлен один из возможных вариантов блока 9 нагрузки, выполняющий операции, требующиеся для работы устройства. Блок 9 нагруэк состоит из нести резисторов, диода, транзистора и инвертора с открытым коллектором 23, входом соединенного с первым входом блока 9 нагрузки, а выходом подключенного к второму выходу блока 9 нагрузки непосредственно, а через резистор 24 - к первому выходу блока 9 нагрузки и к коллектору транзистора 25, база которого через резистор 26 соединена с третьим входом блока 9 нагрузки. Эмиттер транзистора 25 через резистор 27 соединен с шиной питания, которая через резистор 28 подключена к первому вы- ходу блока 9 нагрузки, который, в свою очередь, через резистор 29 подключен к общей шине, а непосредственно соединен с анодом диода 30, катод которого через резистор 31 соединен с вторым входом блока 9 нагрузки.На фиг.3 представлен пример реализации логического преобразователя 8, состоящего из элемента И-НЕ 32, первым входом соединенного с четвертым входом логического преобразователя 8, вторым входом подключенного к второму входу логического преобразователя 8, а выходом соединенного с первым выходом логического преобразователя 8, и элемента И-НЕ 33, первым входом соединенного с первым входом логического преобразователя 8, вторым входом подключенного к третьему входу логического преобразователя 8, а выходом соединенного с вторым выходом логического преобразователя 8,В качестве электронных ключей 11 и 13 могут быть использованы, например, транзисторы р-п-р типа, при этом коллектор транзистора 34 (фиг.4) соединен с выходом электронного ключа 11, эмиттер подключен к входу электронного ключа 11, а база через базовый ре 3 13 зистор 35 соединена с входом управления электронного ключа 22, эмиттер транзистора 36 (фиг.5) соединен с входом электронного ключа 13, коллектор подключен к выходу электронного ключа 13, а база через базовый резистор 27 соединена с входом управления электронного ключа 13.В качестве логического преобразователя 20 может быть использовано, например, ПЗУ, выполняющее роль преобразователя кода - реакции зонда на входное воздействие в код, удобный для визуализации индикатором 21 и для регистрации информации с логических выходов 22.Регулируемые источники 1 и 6 опорного напряжения регулируются следующим образом. Регулируемый источник 1 опорного напряжения регулируется так, чтобы напряжение на его выходе равнялось максимально допустимому верхне,е му значению логич.ского нуля С . Регулируемый источник 6 опорного напряжения регулируется так, чтобы напряжение на его выходе равнялось минимально допустимому нижнему значению логической единицы П.На вход 7 теста нагрузки подают псевдослучайные тесты синхронно с подачей на входы объекта диагностирования многоразрядных кодовых наборов. На вход 7 теста нагрузки могут подаваться и детерминированные воздействия, подобраннь 1 е в соответствии с ожидаемыми реакциями объекта диагностирования.Работу зонда для проверки сигналов цифровых микросхем рассмотрим на примере ТТЛ элементов.На фиг.6 изображен выходной каскад элемента ТТЛ. В состоянии логического нуля транзистор 38 закрыт, транзистор 39 открыт. В состоянии логической единицы транзистор 38 открыл, транзистор 39 закрыт. В высокоимпедапсном состоянии транзисторы 38 и 39 закрыты.В предлагаемом устройстве оценку логического нуля по уровню напряжения производит блок 2 сравнения напряжений, на первьп вход которого подают верхнее допустимое значение напряжесния логического нуля Паксф а на Второй вход - сигнал с проверяемого выхода объекта диагностирования. Оценку логической единицы по уровню напряжения про 11 зводит блок 5 сравнения48759напряжений, на второй вход которогоподают нижнее допустимое значение напряжения логической единицы Б, а 5 10 15 20 25 30 35 40 45 50 55 на первый вход - сигнал с проверяемого выхода объекта диагностирования.Сравнение сопротивления проверяемого выхода в высокоимпедансном состоянии с минимально допустимой величиной производится блоком 15 сравнения напряжений с помощью сравнения падений напряжений на резисторах 12 и 16 при закрытых электронных ключах 11 и 13. Резисторы 16-19 представляют собой эталонный безынерционный целитель напряжения, Значения сопротивлений этих резисторов выбирают так, чтобы отношение сопротивления резистора 12 к минимально допустимому сопротивлению выхода в высокоимпедансном состоянии относительно общей шины равнялось отношению сопротивления резистора 16 к сумме сопротивлений резисторов 17 и 19, а отношение сопротивления резистора 12 к минимально допустимому сопротивлению выходав высокоимпедансном состоянии относительно шины питания равнялось отношению сопротивления резистора 16 к сумме сопротивлений резисторов 17 и 18.Оценку сопротивления выхода в высокоимпедансном состоянии относительно общей шины проводят при высоком значении напряжения нагрузки. При этомво внимание принимаются две параллельные цепочки, одну из которых составляет резистор 12 и закрытый транзистор 39 проверяемого выходного каскада, а вторую - резистор 16 и последовательно соединенные резисторы 17 и 19. При сопротивлении закрытоготранзистора 39, превышающем минимально допустимое значение, потенциал щупа 4 будет выше потенциала первого входа блока 15, что будет зафиксировано блоком 15 сравнения напряжений. Недостаточно высокое сопротивление закрытого транзистора 39 приведет ктому, что потенциал щупа 4 будет нижепотенциала первого входа блока 15. Оценку сопротивления выхода в высокоимпедансном состоянии относительно шины питания производят при низком значении напряжения нагрузки, При этом во внимание пр 1 пп 1 маются две параллельные цепочки, одну из которых составляют резистор 12 и закрытыйтранзистор 38 проверяемого выходногокаскада, а вторую - резистор 16 и по 1348759следовлтельно соединенные резисто ры 17 и 18, При сопротивлении закрытого трлцэистоол 38, превышающем минимально допустимое значение, потен 5 нилл пгупл 4 будет ниже потенциала первого входа блока 15, что будет зафиксировано блоком 15 сравнения напряжений, Недост;гточно высокое сопротивление закрытого транзистора 381 О приведет к тому, что потенциал щупа 4 будет выше потенциала первого входа блока 15.Р существующих устройствах точность измерения сопротивления высокогмпедацсггого состояния находится в противоречии с быстродействием. При фиксированной чувствительности блока 15 сравнения напряжений повысить точность измерения можно увеличением до некоторой степени сопротивления резистора 12, цо при этом затрудняется перезаряд паразитных емкостей выходного каскада объекта диагностирования, что приводит к понижению быстро,цействия. Для уменьшения упомянутого противоречия приняты меры по форсированному перезаряду паразитных емкостей, которые осуществляются с помощью блока 3 сравнения напряжений, логического преобразователя 8, блока 9 нагрузки, резисторов 10, 14 и 17, электронных ключей 11 и 13.Предположим в исходном состоянии проверяемый выход находится в высоко 35 импедацсном состоянии, при котором транзисторы 38 и 39 закрыты, а блок 9 цлгрузки выдает гнгзкий уровень напряжения цл выходе (фиг.7). Допустим в момент временина входы объекта диагностирования подают многоразрядный когьэвый набор, реакцией проверяемого вьгходл ца который также является высокоимпендлнсцое состояние. Одцоцремеггно цл вход 7 теста нагрузки подают воздействие, которое создаст гга выходе олокл 9 нагрузки высокий уровень напряжения, В течение интервала времени с, -г., блок 9 нагрузки обраблтывлет входное воздействие и50 после злвершенггя переходных процессов к моменту времени С выдает высокий уровень цлпряжения на выходе (крггвля 40 цл фпг.7), При отсутствии формирующих цепей, которые составляют55 резисторы 10 и 14 и электронные ключи 11 и 13, ерезаряд паразитных емкостей проверяемого вг,хода объектадиагнсстцроц,.цця происходит через резистор 12 с постоянной времени, определяемой величиной этого резистора и собственггыми цепями разряда (кривые 4 и 42 для исправного и неисправного высокоимпедансного состояния соответственно).Работа форсирующих цепей происходит следующим образом. Одновременно с переходными процессами на выходе блока 9 нагрузки, завершаются переходные процессы на резисторе 17 безь;нерционного эталона высокоимпедансного состояния. В момент времени устанавливается критический потенциал г, на первом выводе резистора 7. На несколько процентов ниже устанавливается потенциал (р на втором выводе резистора 17. При незавершенных г:,ереходных процессах на проверяемом выходе объекта диагностирования потенциал щупа 4 ниже потенциала второго вывода резистора 17, отчего блок 3 сравнения напряжений с прямого выхода выдает логическую единицу на второй вход логического преобразовате-ля 8, которая совместно с логической единицей на четвертом входе логического преобразователя 8 создает на первом выходе логический ноль, который по входу управления открывает электронный ключ 11. Одновременно по второму входу блока 9 нагрузки логическггй ноль обеспечивает ток через резистор 28, диод 30, резистор 31, шуцтирующее действие которого снижает нл заданную величину высокий уровень напряжения на первом выходе блока нагрузки. Снижение высокого уровня напряжения на выходе блока 9 нагрузки происходит до такой степени, чтобы при минимально допустимом значении сопротивления высокоимпедансного состояния и открытом электронномключе 11 ца щупе установился потенцилл, приближающийся, но не достигающий критического потенциала первого вывода резистора 17. При этом происходит форсированный перезаряд паразитцых емкостей проверяемого выхода объекта диагностирования с постоянной времени, определяемой сопротивлением резистора 12, параллельно подключенному ему резистора 10 с открытым электронным ключем 1 и собственными цепями разряда (кривая 43 на фиг.7). В момент времени с потенциал щупа 4 сравнивается с потенциалом второго вывода резистора 17 и затем начинаетего превосходить. Блок 3 сравнения напряжений логическую единицу на прямом выходе изменяет на ноль, вследствие чего логической единицей с пер 5 вого выхода логического преобразоателя 8 закрывается электронньп ключ 11 и одновременно повышается напряжение на выходе блока 9 нагрузки. Отрезок времени Т 4 - равен времени срабаты вания блока 3 сравнения напряжений, логического преобразователя 8, блока 9 нагрузки и электронного ключа 1. После момента времени 5 начинается завершающая стадия переходного 15 процесса с постоянной времени, определяемой величиной сопротивления резистора 12 ц собственными цепями разряда выходного каскада. Кривая 44 ха- . рактеризует переходной процесс ис правцого высокоимпедансного состояния, а кривая 45 - неисправного (фиг.7). В момент времени д регистрируют результат анализа зондом состояния проверяемого выхода. Выше рас смотрена работа форсирующих цепей при оценке сопротивления высокоимпедансного состояния относительно общей шины. Аналогично происходит работа цепей форсирования переходных про цессов,при оценке сопротивления высокоимпедансного состояния относительно шины питания (фиг.8).Проверка логического нуля, Предположим в исходный момент времени проверяемьп выход объекта диагностирования находится в состоянии логического нуля, а блок нагрузки выдает низкий уровень напряжения.Допустим в момент времеци О (фиг . 9) на входы объек та дна гно с тирования подают многоразрядный кодовый набор, которьп создаст на прогеряе - мом вьходе состояние логического нуля. Одновременно на вход 7 теста .а грузки подают воздействие, которое создаст на выходе блока 9 цагрузки высокий уровень цапряже и. Б течение интервала времени С -Г блок нагрузки обрабатывает поступившее воздействие и после завершения переходных процессов к моменту времени выдает высокое значение напряжения нагрузки, при котором открытый транзистор 39 (фг.б) проверяемого выходного каскада нагружает-я максимально допустимым током по цепи: первый выход блока 9 нагрузки, открытый электронньп ключ 11, резистор 1 О, частичцо через резистор 12, щу 4, открытый транзистор 39, обшая шина. Б данной ситуации электроццый ключ 11 открыт логическим нулем с выхода первого логического преобразователя 8, В момент времени С ца щупе прцсутствует низкий уровень напряжения, вызванный логическим нулем ца проверяемом выходе, а ца втором выводе резистора 7 имеет место высокий потенциал, вызвацньп высоким уровнем напряжения на выходе блока 9 нагрузки. Такое сочетание рассматривается блоком 3 сравнения напряжений и логическим преобразователем 8 как цезавершенцьп переходньп процесс, которые принимают меры для форсированного перезаряда паразитных емкостей. НО в данном случае это состояние стабильно и упомянутые выше меры нагружают выходной каскад максимально разрешенным током. В момент времени г. под воздействием максимальной нагрузки уровень сигнала проверяемого выхода несколько повышается, но для исправного выхода он неодолжен превышать 0 , что определяет блок 2 сравнения напряжений. На втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствовать кодовый набор 1100 соответственно, что депнфрнруеся как качественный логический ноль, проверенный под нагрузкой и регистрируется в момент времениПроверка логической единицы. Предположим в исходньп момент времени проверяемьп выход объекта диагностирования находится в состоянии логической едиз а блок 9 нагрузки выдает высокий уровень цапряжеш.Допустим в момент времени ,ц (фиг.10) на входы объекта диагностироваеия подают мцогоряз рядъп кодовый набор, который создаст ца проверяемом выходе состояце логической единицы. Одновременно на вход 7 тест нагрузки подают воздействие, которое создаст на выходе блока 9 нагрузки низкий уровень напряжения. В течение ицгервала времени С-С блок нагрузки обрабатьпзает входное воздестве и после завершеия переходцх процессов к моменту времени 1, выдает низкое значение напрлжецягрузки,при котором открытьп транзистор 38 проверяемого выходного каскад нагружается максимально разрешенм током по цепи: источник питагпя Объекта ди50 агностиронания, открытый транзистор 38, выход объекта диагностирования, щуп 4, открытый электронный .ключ 13, резистор 14, частично через5резистор 12, выход блока нагрузки,общая шина. В момент времени С, нащупе присутствует высокий уровень напряжения, вызванный логической единицей на проверяемом выходе, а навтором выводе резистора 17 имеет место низкий потенциал, вызванный низким уровнем напряжения на выходе блока 9 нагрузки. Такое сочетание потенциалов рассматривается блоком 3 сравнения напряжений и логическим преоб- фразователем 8 как незавершенный переходный процесс, н результате чего напервом и втором выходах логическогопреобразователя 8 присутствует код 10,20который открынает электронный ключ 13и закрывает электронный ключ 11. Вмомент времени С под воздействиеммаксимально допустимого тока нагрузки уровень сигнала проверяемого выхода несколько понижается, но для исправного выхода он не должен опуститься ниже 11 , т.е. ниже уровня, который регистрирует блок 5 сравнения напряжений. На втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствоватькод 0011, что дешифрируется как качественная логическая единица, проверенная под нагрузкой, и регистрируется в момент времени С .,Проверка сопротивления выхода ввысокоимпедансном состоянии относительно общей шины. Предположим н исходный момент времени проверяемый вы. 40ход находится н состоянии логическогонуля, при котором транзистор 38 закрыт, а транзистор 39 открыт (фиг.б),блок нагрузки выдает низкий уровеньнапряжения (фиг.11). Допустим н момент времени й, на входы объекта диагностирования подают многоразрядныйкодовый набор, который создаст напроверяемом выходе высокоимпедансноесостояние. Одновременно на вход 7теста нагрузки подают воздействие,которое создаст на выходе блока нагрузки высокий уровень напряжения.В течение интервала времениблок нагрузки обрабатывает поданноевоздействие и после завершения переходных процессов к моменту времениС выдает высокий уровень напряженияна выходе. Переход иэ состояния логического нуля н нысокоимпедансное состояние заключается в том,что транзистор 39 (Фиг.б) из открытого состояния переходит н закрытое состояние, а транзистор 38 остается закрытым. В течение интервала времени 1 -С,в идет обработка поданного на входы объекта диагностирования многоразрядного кодового набора и в момент времени Сщ проверяемый выход начинает переходить в высокоимпедансное состояние. При этом прекращается поступление тока в базу транзистора 39. Быстрому перезаряду емкости база-эмиттер транзистора 39 способствует ток нагрузки коллектор-эмиттер транзистора 39 от блока нагрузки с высоким уровнем напряжения на выходе. Этим достигается быстрый переход транзистора 39 в закрытое состояние и, как следствие, повьппение быстродействия при проверке выходов с тремя устойчивыми состояниями. После завершения переходных процессов потенциал щупа 4 при исправном высокоимпедансном состоянии будет вьппе потенциала первого вывода резистора 17, что фиксирует блок 15 сравнения напряжений. На втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствовать код 0010 соответственно, что дешифрируется как качественное сопротивление нысокоимпе-, дансного состояния относительно общей шины и регистрируется в момент времени Т, . При некачественном высокоимпедансном состоянии на входах логического преобразователя 20 будет код 1010.Проверка сопротивления выхода н высокоимпедансном состоянии относительно шины питания. Предположим в исходном состоянии проверяемый выход находится н логической единице, при которой транзистор 38 (фиг.б) открыт, транзистор 39 закрыт, а блок 9 нагрузки выдает на выходе высокий уровень напряжения (фиг.12).Допустим в момент временина входы объекта диагностирования подают многоразрядный кодовый набор, который создаст на проверяемом выходе высокоимпедансное состояние. Одновременно на вход 7 теста нагрузки подают ноздействие,которое создаст на выходе блока 9 нагрузки низкий уровень напряжения. В течение интервала времени с,-с, блок 9 нагрузки обрабатыва2 48759 11 13 ет входное ноздействие и после завершения переходных процессон к моменту времени С выдает низкий уровень напряжения на выходе. Переход из состояния логической единицы в высокоимпедансное состояние заключается в том, что транзистор 38 (фиг.б) выходного каскада иэ открытого состояния переходит н закрытое состояние, а транзистор 39 остается закрытым. В течение интервала времени С -1,идет обработка поданного на входы объекта диагностирования многоразрядного кодового набора, в момент времени проверяемый выход начинает переходить в высокоимпедансное состояние. При этом прекращается поступление тока в базу транзистора 38, Быстрому переэаряду паразитной емкости база-эмиттер транзистора 38 способствует ток нагрузки коллектор-эмиттер транзистора 38 на выход блока нагрузки с низким уровнем напряжения. В момент времени С,выходной каскад переходит в высокоимпедансное состояние. Оценку сопротивления выхода в высокоимпедансном состоянии относительно шины питания проводят при низком значениинапряжения выхода блока 9 нагрузки.При этом во внимание принимаются днепараллельные цепочки, одну из которыхсоставляют резистор 12 и закрытыйтранзистор 38 выходного каскада в вы 1сокоимпедансном состоянии, а вторую -резистор 16 и последовательно соединенные резисторы 17 и 18. При сопротивлении закрытого транзистора 38,превышающем минимально установленнуюнорму, потенциал щупа 4 будет нижепотенциала первого вывода резистора 17. Недостаточно высокое сопротивление закрытого транзистора 38 приведет к превьппению потенциала щупа 4над потенциалом первого вынода резистора 17, что будет зафиксировано блоком 15 сравнения напряжений. При исправном высокоимпедансном состояниина втором, третьем, четвертом и первом входах логического преобразователя 20 будет присутствовать код 1001соответственно, который дешифрируетсякак качественное сопротивление высокоимпедансного состояния относитель -но шины питания и регистрируется вмомент времени с , При некачестнен 5ном высокоимпедансном состоянии навходах логического преобразователя 20будет код 0001,5 1 О 15 20 25 30 39 40 Описанные сочетания состояний проверяемого выхода и уровней напряжения на выходе блока нагрузки обеспечивают проверку логических уровней под нагрузкой и динамичную проверку высокоимпедансного состояния относительно общей шины и шины питания. Другие сочетания упомянутых событий не обеспечивают полноценной проверки состояний выходов, но и не дают результатов, отличающихся от результатов проверки эталонного устройства.Рассмотрим некоторые такие случаи.Переход проверяемого выхода в состояние логической единицы при высоком уровне напряжения на выходе блока 9 нагрузки. В этом случае зонд ведет себя так же, как при проверке сопротивления высокоимпедансного состояния относительно общей шины. Малое сопротивление открытого транзистора 38 ( фиг,б) определяет быстрое завершение переходных процессов.Переход проверяемого выхода из логической единицы в высокоимпедансное состояние при высоком значении напряжения на выходе блока 9 нагрузки. Зонд ведет себя так же, как при проверке сопротивления высокоимпедансного состояния относительно общей шины. Переходный процесс не форсируется. Незавершенность переходного процесса на проверяемом выходе объекта диагностирования создает для зонда эффект пре-. вьппения сопротивлением высокоимпедансного состояния минимально допустимой нормы, т.е. не искажает результаты проверки эталонного устройства.Переход проверяемого выхода в состояние логического нуля при низком уровне напряжения на выходе блока 9 нагрузки. Логический ноль под нагрузкой не проверяется, Малое сопротивление открытого транзистора 39 (фиг, б)вызывает быстрое завершение переходных процессов на проверяемом выходе объекта диагностирования.Переход проверяемого выхода из логического нуля в нысокоимпедансное состояние при низком значении напряжения на выходе блока 9 нагрузки.Зонд ведет себя так же, как при проверке, сопротивления высокоимпедансного состояния относительно шийы питания, но переходньй процесс не форсируется и состояние блока 2 сравнения напряжений зависит от степени завершенности переходного процесса. Для1 О 2 С устранения неоднозначности реакциизонда предназначено соединение входа 7 теста нагрузки с первым входомлогического преобразователя 20, которое блокирует в преобразователе 20сигнал блока 2 сравнения напряженийпри низком значении напряжения на выходе блока 9 нагрузки. Незавершенность переходного процесса на проверяемом выходе объекта диагностирования создает для зонда эффект превышения сопротивлением высокоимпедансного состояния минимально допустимойнормы, т.е. не искажает результатыпроверки эталонного устройства. Формула изобретения Зонд для проверки сигналов цифровых микросхем, содержащий первый резистор, индикатор, щуп, первьп логический преобразователь, три блока сравнения напряжений, два регулируемык источника опорного напряжения, первый из которых соединен выходом с первым входом первого блока сравнения напряжений, второй вход которого соединен со щупом и первым входом второго блока сравнения напряжений, с первым входом третьего блока сравнения напряжений, второй вход которого соединен с выходом второго регилуремого источника опорного напряжения, первый вывод первого резистора соединен с клеммой для подключения источника напряжения, первый логический преобразователь соединен первым входом с выходом второго блока сравнения напряженир, вторым входом - с выходом первого блока сравнения напряжений, третьим входом - с выходом третьего блока сравнения напряжений, выходы первого логического преобразователя соединены с входами индикатора, о т л и ч а ю щ и й с я тем, что, с целью расширения функциональных возможностей и повышения быстродействия, в него введены второй, третий, чет 2 с 30 35 4 45 вертый, пятьй, шестой и седьмой резисторы, два электронных ключа, блокнагрузки, четвертьп блок сравнениянапряжений, второй логический преобразователь, вход теста нагрузки зонда, соединенный с первым входом второго логического преобразователя,счетвертым входом первого логическогопреобразователя, с первым входом блока нагрузки, первый выход которогосоединен с входом первого электронно. гс ключа, с первым выводом второгорезистора, с первым выводом третьего резистора, с первым выводом четверто. гс резистора, второй вывод третьегорезистора соединен с вторым входомвторого блока сравнения напряженийи с первым выводом пятого резистора,второй вывод которого через шестойрезистор соединен с общей шиной, через первый резистор соединен с шиной питания, а непосредственно соединенс первым входом четвертого блока г сравнения напряжений, второй вход которого соединен со щупом, а прямой и инверсный выходы соединены соответственно с вторым и третьим входамивторого логического преобразователя,четвертьп вход которого соединен с вторым выходом блока нагрузки, второй вход которого соединен с первымвыходом второго логического преобразователя и с входом управления первого электронного ключа, третий входблока нагрузки соединен с вторым выходом второго логического преобразователя и с входом управления второгоэлектронного ключа, выход которогосоединен с вторым выводом четвертого резистора, вход второго электронногоключа через седьмой резистор соединен с выходом первого электронногоключа, а непосредственно соединен с первым входом второго блока сравнения напряжений, логические выходы зондасоединены с выходами первого логического преобразователя, второй выводвторого резистора соединен со щупом.

СмотретьЗаявка

4080120, 19.06.1986

ХАРЬКОВСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. ЛЕНИНА

КОРДЮМОВ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G01R 31/28, G01R 31/3177

Метки: зонд, микросхем, проверки, сигналов, цифровых

Опубликовано: 30.10.1987

Код ссылки

<a href="https://patents.su/12-1348759-zond-dlya-proverki-signalov-cifrovykh-mikroskhem.html" target="_blank" rel="follow" title="База патентов СССР">Зонд для проверки сигналов цифровых микросхем</a>

Предыдущий патент: Устройство для контроля и диагностики многоканальной цифровой аппаратуры

Следующий патент: Устройство для измерения напряженности магнитного поля

Случайный патент: Фотометр