Устройство для контроля тестопригодных программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

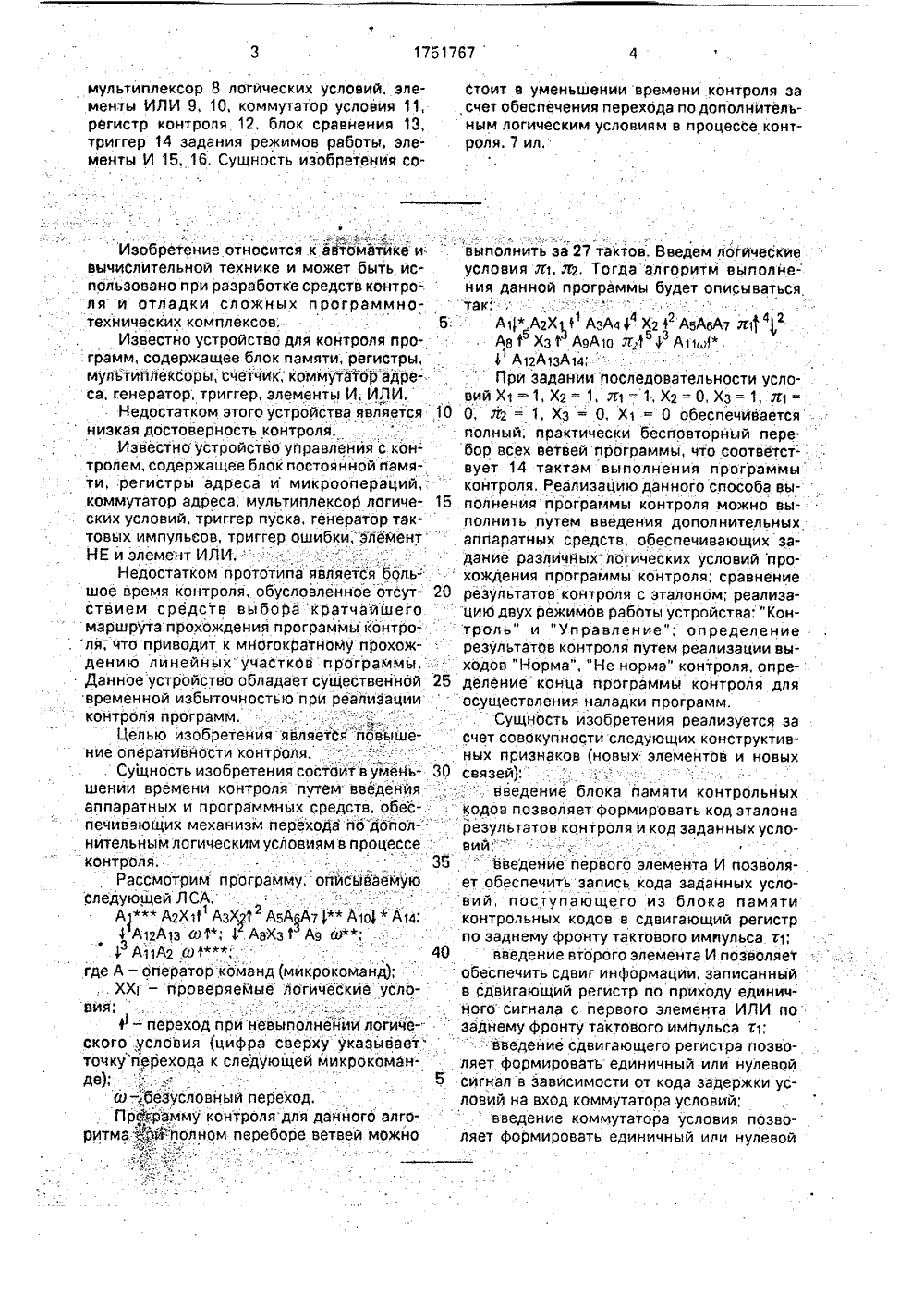

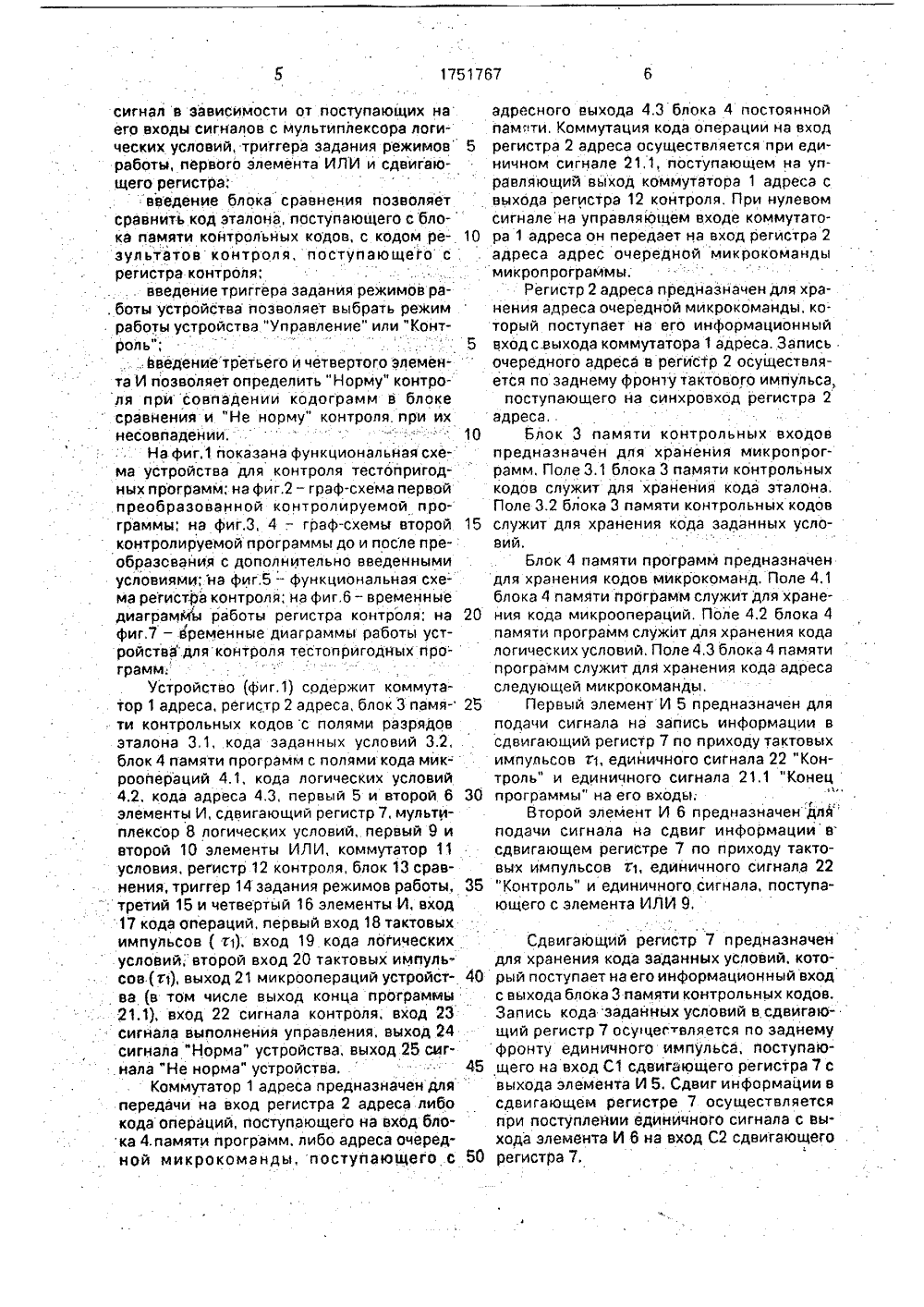

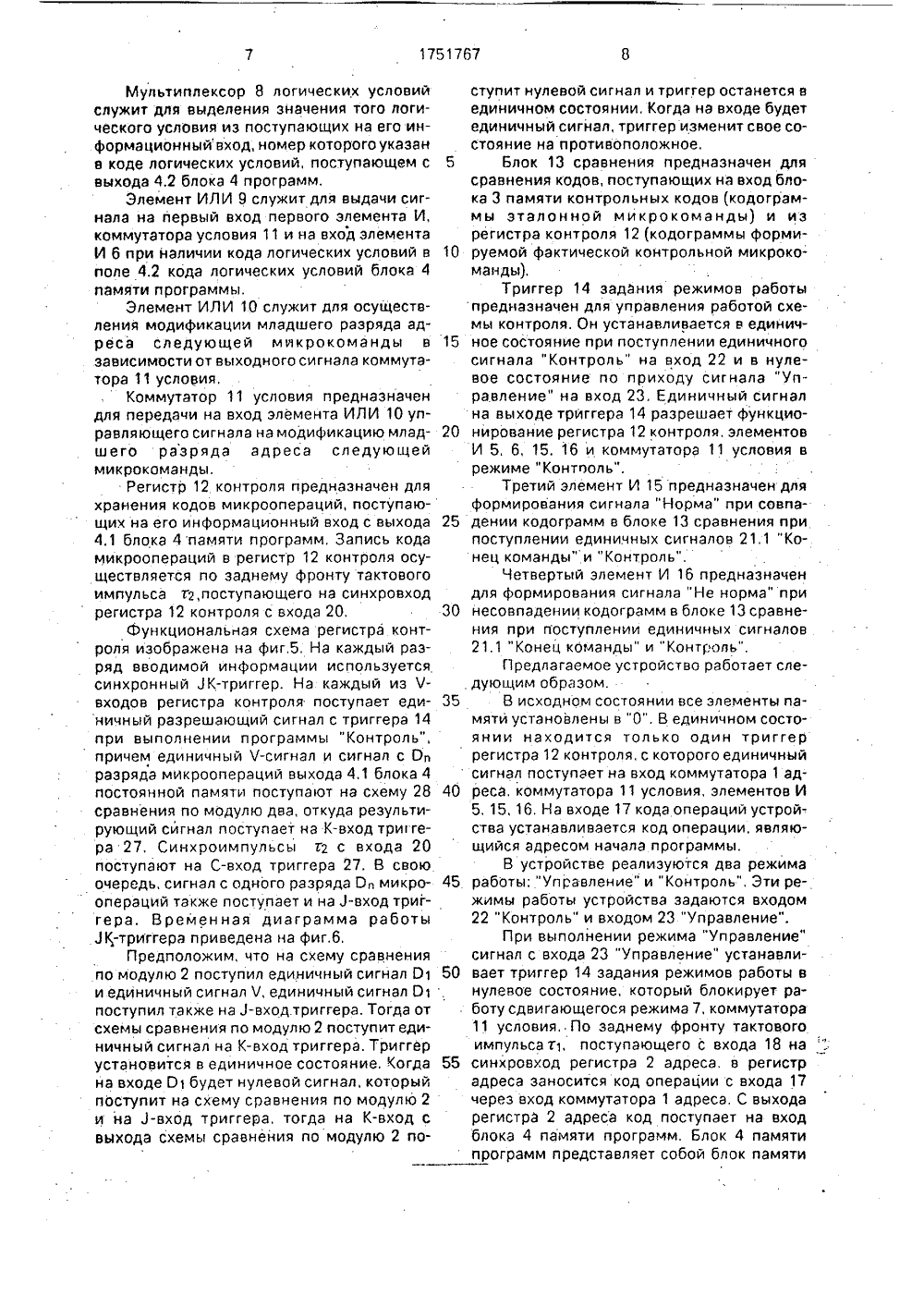

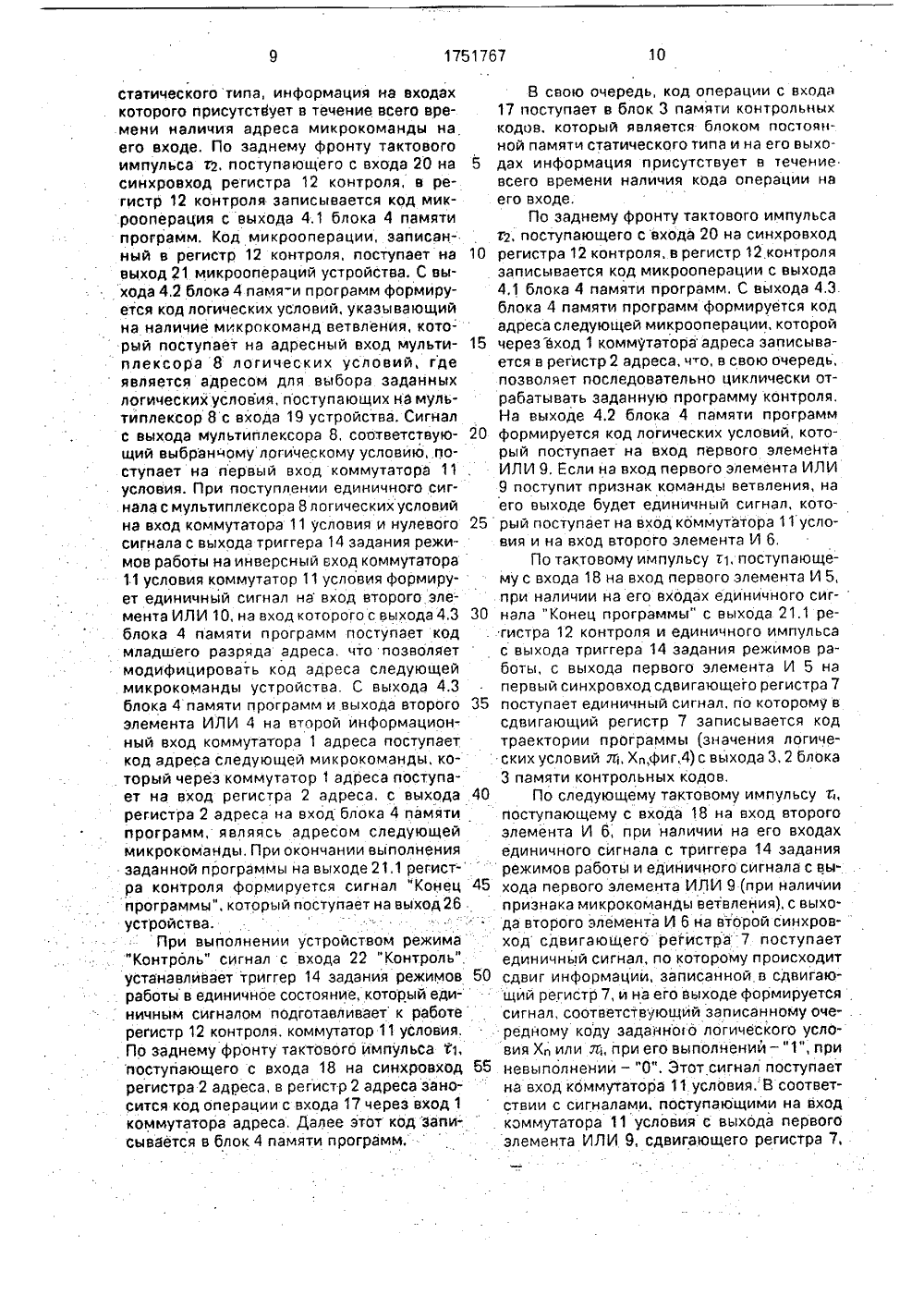

)5 006 Г 11/ ИЕ ИЗОБРЕТЕНИЯСВИДЕТЕЛЬСТВУ ПИСА К АВТО 2, 2 ОСУДАРСТВЕ ННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР 1(71) Конструкторское бюро элстроения(54) УСТРОЙСТВО ДЛЯКОНТРОЛЯ ТЕСТОПРИГОДНЬЗХ ПРОГРАММ(57) Изобретение относится к области вычислительной техники и может быть использовано при разработке средств контроля и отладки программно-технических комплексов, Цель - повышение оперативности контроля, Устройство содержит коммутатор адреса 1, регистр адреса 2, блок памяти 3 контрольных кодов, блок памяти 4 программ, элементы И 5, 6, регистр сдвига 7,1751767 Сос Тех Корректор С; Либай Редакт к издательский комбинат "Лат г. Ужгород, уМХагерина, 101 роизводствен рЗаказ. 2693ВНИИПИ итель Н СедыхМ.Моргейтай Тираж : - ,. .,., Подписноетвенного койитетв по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж-ЭЬ, Раушская наб., 4/б .сигнал в зависимости от поступающих наего входы сигналов с мультиплексора логических условий, триггера задания режимов 5 работы, первого элемента ИЛИ и сдвигающего регистра; введение блока сравнения позволяет сравнить код эталона, поступающего сблока памяти койтрольных кодов, с кодом ре зультатов контроля, поступающего срегистра контроля;введение триггера задания режимов работы устройства позволяет выбрать режим.: введениетретьего и четвертого элемента И позволяет определить "Норму" контроля при совпадении кодограмм в блоке сравнения и "Не норму" контроля, при их несовпадении, " . " - 10На фиг.1 показана функциональйая схема устройства для контроля тестопригодных программ; на фиг,2 - граф-схема первой преобразованной контролируемой программы; на фиг,3, 4 - . граф-схемы второй 15контролируемой программы до и после преобразования с дополнительно введенными условиями;на фиг,5 - функциональная схема регистра контроля; на фиг,6 - временные диаграмйы работы регистра контроля; на 20 фиг.7 - временные диаграммы работы устройствадля контроля тестопригодных и ро- грамм.Устройство (фиг.1) содержит коммута. тор 1 адреса. регистр 2 адреса, блок 3 памя ти контрольных кодов с полями разрядов эталона 3,1, кода заданных условий 3.2, блок 4 памяти программ с полями кода микроопераций 4.1, кода логических условий 4.2, кода адреса 4,3, первый 5 и второй 6 элементы И, сдвигающий регистр 7, мультиплексор 8 логических условий, первый 9 и 30 второй 10 элементы ИЛИ, коммутатор 11 условия, регистр 12 контроля, блок 13 сравусловий второй вход 20 тактовых импульсов (т 1), выход 21 микроопераций устройст ва (в том числе выход конца программы 21.1), вход 22 сигнала контроля; вход 23 сигнала выполнения управления, выход 24 сигнала "Норма" устройства, выход 25 сигнала "Не норма" устройства, 45 Коммутатор 1 адреса предназначен для передачи на вход регистра 2 адреса либо кода операций, поступающего на вход блока 4.памяти программ, либо адреса очередной микрокоманды, поступающего с нения, триггер 14 задания режимов работы, 35 : третий 15 и четвертый 16 элементы И, вход 17 кода апераций, первый вход 18 тактовых импульсов ( т). вход 19 кода логических адресного выхода 4.3 блока 4 постоянной памяти, Коммутация кода операции на вход регистра 2 адреса осуществляется при единичном сигнале 21,1, поступающем на управляющий выход коммутатора 1 адреса с выхода регистра 12 контроля, При нулевом сигнале на управляющем входе коммутатора 1 адреса он передает на вход регистра 2 адреса адрес очередной микрокоманды микропрограммы.Регистр 2 адреса предназначен для хранения адреса очередной микрокоманды, который поступает на его информационныйвход с.выхода коммутатора 1 адреса. Запись очередного адреса в регистр 2 осуществляется по заднему фронту тактового импульса, поступающего на синхровход регистра 2 адреса, .Блок 3 памяти контрольных входов предназначен для хранения микропрограмм, Поле 3.1 блока 3 памяти контрольных кодов служит для храйения кода эталона, Поле 3.2 блока 3 памяти контрольных кодов служит для хранения кода заданных условий.Блок 4 памяти программ предназначен для хранения кодов микрокоманд. Поле 4.1блока 4 памяти программ служит для хранения кода микроопераций, Поле 4,2 блока 4 памяти программ служит для хранения кода логических условий. Поле 4,3 блока 4 памяти программ служит для хранения кода адреса следующей микрокоманды,Первый элемент И 5 предназначен для подачи сигнала на запись информации в сдвигающий регистр 7 по приходу тактовых импульсов х 1, единичного сигнала 22 "Контроль" и единичного сигнала 21,1 "Конецпрограммы" на его входы;Второй элемент И 6 предназначен для" подачи сигнала на сдвиг информациив сдвигающем регистре 7 по приходу тактовых импульсов т 1, единичного сигнала 22 "Контроль" и единичного сигнала, поступающего с элемента ИЛИ 9,Сдвигающий регистр 7 предназначен для хранения кода заданных условий, который поступает на его информационный вход с выхода блока 3 памяти контрольных кодов. Запись кода заданных условий в сдвигающий регистр 7 осущегтвляется по заднему фронту единичного импульса, поступающего на вход С 1 сдвигающего регистра 7 с выхода элемента И 5. Сдвиг информации в сдвигающем регистре 7 осуществляется при поступлении единичного сигнала с выхода элемента И 6 на вход С 2 сдвигающего регистра 7.Мультиплексор 8 логических условий служит для выделения значения того логического условия из поступающих на его информационныйвход, номер которого указан в коде логических условий, поступающем с выхода 4.2 блока 4 программ.Элемент ИЛИ 9 служит для выдачи сигнала на первый вход первого элемента И, коммутатора условия 11 и на вход элемента И 6 при наличии кода логических условий в поле 4.2 кода логических условий блока 4 памяти программы,Элемент ИЛИ 10 служит для осуществления модификации младшего разряда адреса следующей мякрокоманды в зависимости от выходного сигнала коммутатора 11 условия,Коммутатор 11 условия предназначен для передачи на вход элемента ИЛИ 10 управляющего сигнала на модификацию младшего разряда адреса следующей микрокомэнды,Регистр 12 контроля предназначен для хранения кодов микроопераций, поступающих на его информационный вход с выхода 4,1 блока 4 памяти программ, Запись кода микроопераций в регистр 12 контроля осуществляется по заднему фронту тактового импульса т,поступающего нэ синхровход регистра 12 контроля с входа 20,Функциональная схема регистра контроля изображена на фиг,5, На каждый разряд вводимой информации используется синхронный ЛК-триггер. Нэ каждый из Ч- входов регистра контроля поступает единичный разрешающий сигнал с триггера 14 при выполнении программы "Контроль", причем единичный Ч-сигнал и сигнал с Ол разряда микрооперэций выхода 4,1 блока 4 постоянной памяти поступают на схему 28 сравнения по модулю два, откуда результирующий сигнал поступает на К-вход триггера 27, Синхроимпульсы г 2 с входа 20 поступают на С-вход триггера 27. В свою очередь, сигнал с одного разряда О микро- операций также поступает и на 3-вход триггера. Временная диаграмма работы ЗК-триггера приведена на фиг,б,Предположим, что на схему сравнения по модулю 2 поступил единичный сигнал О 1 и единичный сигнал Ч, единичный сигнал О 1 поступил также на 3-вход. триггера. Тогда от схемы сравнения по модулю 2 поступит единичный сигнал на К-вход триггера. Триггер установится в единичное состояние, Когда на входе О 1 будет нулевой сигнал, который поступит на схему сравнения по модулю 2 и на 3-вход триггера, тогда на К-вход с выхода схемы сравнения по модулю 2 по 10 20 25 дении кодограмм в блоке 13 сравнения при 30 35 40 50 55 ступит нулевой сигнал и триггер останется в единичном состоянии. Когда на входе будет единичный сигнал, триггер изменит свое состояние на противоположное,Блок 13 сравнения предназначен для сравнения кодов, поступающих на вход блока 3 памяти контрольных кодов (кодограммы эталонной микрокоманды) и из регистра контроля 12 (кодограммы формируемой фактической контрольной микрокоманды),Триггер 14 задания режимов работы предназначен для управления работой схемы контроля. Он устанавливается в единичное состояние при поступлении единичного сигнала "Контроль" на вход 22 и в нулевое состояние по приходу сигнала "Управление" на вход 23. Единичный сигнал на выходе триггера 14 разрешает функционирование регистра 12 контроля, элементов И 5, 6, 15, 16 и коммутатора 11 условия в режиме "Контполь",Третий элемент И 15 предназначен для формирования сигнала "Норма" при совпапоступлении единичных сигналов 21,1 "Конец команды" и "Контроль",Четвертый элемент И 16 предназначен для формирования сигнала "Не норма" при несовпадении кодограмм в блоке 13 сравнения при поступлении единичных сигналов 21,1 "Конец команды" и "Контроль",Предлагаемое устройство работает следующим образом,В исходном состоянии все элементы памяти установлены в "0". В единичном состоянии находится только один триггер регистра 12 контроля, с которого единичный сигнал поступает на вход коммутатора 1 адреса, коммутатора 11 условия, элементов И 5, 15, 16, Нэ входе 17 кода операций устройства устанавливается код операции, являющийся адресом начала программы.В устройстве реализуются два режима работы: "Управление" и "Контроль", Эти режимы работы устройства задаются входом 22 "Контроль" и входом 23 "Управление".При выполнении режима "Управление" сигнал с входа 23 "Управление" устанавливает триггер 14 задания режимов работы в нулевое состояние, который блокирует работу сдвигающегося режима 7, коммутатора 11 условия, По заднему фронту тактового импульсэт 1, поступающего с входа 18 на ".: синхровход регистра 2 адреса. в регистр адреса заносится код операции с входа 17 через вход коммутатора 1 адреса, С выхода регистрэ 2 адреса код поступает на вход блока 4 памяти программ, Блок 4 памяти программ представляет собой блок памяти10 его выходе будет единичный сигнал, кото 25 рый поступает на вход коммутатора 11 усло 30 35 40 50 статического типа, информация на входахкоторого присутствует в течение всего времени наличия адреса микрокоманды наего входе. По заднему фронту тактовогоимпульса т 2, поступающего с входа 20 насинхровход регистра 12 контроля, в регистр 12 контроля записывается код микрооперация с выхода 4,1 блока 4 памятипрограмм. Код микрооперации, записанный в регистр 12 контроля, поступает навыход 21 микроопераций устройства. С выхода 4,2 блока 4 памя-и программ формируется код логических условий, указывающийна наличие микрокоманд ветвления, который поступает на адресный вход мультиплексора 8 логических условий, гдеявляется адресом для выбора заданныхлогических условия, поступающих на мультйплексор 8 с входа 19 устройства. Сигналс выхода мультиплексора 8, соответствующий выбранчому логическому условию, поступает на первый вход коммутатора 11условия. При поступлении единичного сигнала с мультиплексора 8 логических условийна вход коммутатора 11 условия и нулевогосигнала с выхода триггера 14 задания режимов работы на инверсный вход коммутатора11 условия коммутатор 11 условия формирует единичный сигнал на вход второго элемента ИЛИ 10, на вход которого с выхода 4.3блока 4 памяти программ поступает кодмладшего разряда адреса, что позволяетмодифицировать код адреса следующеймикрокоманды устройства. С выхода 4.3блока 4 памяти программ и выхода второгоэлемента ИЛИ 4 на второй информационный вход коммутатора 1 адреса поступаеткод адреса следующей микрокоманды. который через коммутатор 1 адреса поступает на вход регистра 2 адреса, с выходарегистра 2 адреса на вход блока 4 памятипрограмм, являясь адресом следующеймикрокоманды, При окончании выполнениязаданной программы на выходе 21,1 регистра контроля формируется сигнал "Конец 4программы", который поступает на выход 26устройства,При выполнении устройством режима. работы в единичное состояние, который еди. ничным сигналом подготавливает к работерегистр 12 контроля, коммутатор 11 условия.По заднему фронту тактового импульса Ф 1,поступающего с входа 18 на синхровход 5регистра 2 адреса, в регистр 2 адреса заносится код операции с входа 17 через вход 1коммутатора адреса. Далее этот код запи-.сывается в блок 4 памяти программ,В свою очередь, код операции с входа 17 поступает в блок 3 памяти контрольных кодов, который является блоком постоянной памяти статического типа и на его выходах информация присутствует в течение всего времени наличия кода операции наего входе,По заднему фронту тактового импульсат 2, поступающего с входа 20 на синхровход регистра 12 контроля, в регистр 12 контроля записывается код микрооперации с выхода 4,1 блока 4 памяти программ, С выхода 4,3. блока 4 памяти программ формируется код адреса следующей микрооперации, которой через вход 1 коммутатора адреса записывается в регистр 2 адреса, ч о, в свою очередь,позволяет последовательно циклически отрабатывать заданную программу контроля. На выходе 4.2 блока 4 памяти программ формируется код логических условий, который поступает на вход первого элемента ИЛИ 9. Если на вход первого элемента ИЛИ 9 поступит признак команды ветвления, на вия и на вход второго элемента И 6, По тактовому импульсу т 1, поступающему с входа 18 на вход первого элемента И 5,при наличии на его входах единичного сигнала "Конец программы" с выхода 21,1 регистра 12 контроля и единичного импульса с выхода триггера 14 задания режимов работы, с выхода первого элемента И 5 на первый синхровход сдвигающего регистра 7 поступает единичный сигнал, по которому в сдвигающий регистр 7 записывается код траектории программы значения логических условий л), Хп,фиг,4) с выхода 3, 2 блока3 памяти контрольных кодов,По следующему тактовому импульсу %,поступающему с входа 18 на вход второго элемента И 6; при наличии нэ его входах единичного сигнала с триггера 14 задания режимов работы и единичного сигнала с выхода первого элемента ИЛИ 9 (при наличии признака микрокоманды ветвления), с выхода второго элемента И б на второй синхровход сдвигающего регистра 7 поступает единичный сигнал, по которому происходит сдвиг информации, записанной в сдвигающий регистр 7, и на его выходе формируется сигнал, соответствующйй записанному очередному коду задайноо логического условия Х или л;, при его выполнении - "1", при невыполнении - "0", Этот сигнал поступает на вход коммутатора 11 условия.В соответствии с сигналами, поступающими на вход коммутатора 11 условия с выхода первого элемента ИЛИ 9, сдвигающего регистра 7,триггера 14 задания режимов работы, с выхода коммутатора условия 11 формируется сигнал на входе второго элемента ИЛИ 10, куда также поступает код младшего разряда адреса следующей микрокоманды с выхода 4.3 блока 4 памяти программ для модификации младшего разряда кода адреса следующей микрокоманды. Модифицируемый младший разряд кода адреса следующей микрокоманды с выхода второго элемента ИЛИ 10 поступает на вход коммутатора 1 адреса в составе кода адреса следующей микрокоманды,По заднему фронту тактового импульса т,поступающего с входа 20 на синхровход регистра 12 контроля, по поступлении на его Ч-вход единичногосигнала с выхода триггера 14 задания режимов работы, на информационный вход регистра 12 контроля поступает информация с выхода 4,1 блока 4 памяти программ, На выходе регистра контроля формируется признак контроля, онможет определяться например по формуле КП =К(фиг.5, 6). С выхода регистра1 =11 М12 контроля кодограмма результата контроля поступает на выход 21 устройства, а также на вход блока 13 сравнения, где сравнивается с кодом эталона, который поступает на вход блока 13 сравнения с выхода 3.1 блока 3 памяти контрольных кодов. С выхода блока 13 сравнения формируется сигнал, который поступает на третий 15, четвертый 16 элементы И. При поступлении на вХОд третьего элемента И 15 единичного сигнала с триггера 14 задания условий работыи единичного сигнала с блока 13 сравнения при совпадении кодограмм по приходу единичного сигнала "Конец программ" с выхода 21.1 регистра 12 контроля (фиг.7) третий элемент И 15 формирует сигнал на выход 24 устройства "Норма" контроля, При несовпадении кодограмм в блоке 13 сравнения четвертый элемент И 16 формирует сигнал на выходе 25 устройства "Не норма" контроля,Выход 26 устройства является выходом сигнала "Конец программы", поступающего с последнего триггера регистра 12 контроля.Зададим произвольную программу контроля, структура которой изображена на фиг,З. В данной программе указаны длины линейных участков (с 31, дг, ., бзо), которые будут пройдены за время ( т 1, тг газо), заданы логические условия (Х 1. Х 2, , Х 11) прохождения программы. Рассмотрим маршруты, при которых обеспечивается минимально возможное повторное прохождениеотдельных участков при выполнении программы контроля: Н: Х 1 Х 2 К; Н. Х 1 Х 2 Хз К, 5 Н:Х 1 Х 2 ХЗХ 4 Х 5 Х 6 К; Н; Х 1 Х 4 Х 5 Х 6 Х 10 К; Н Х 1 Х 4 Х 5 Х 9 Х 0 Х 11 К Н; Х 1 Х 4 Х 7 Хв Х 9 Х 11 К; Н, Х 1 Х 4 Х 7 Хв Х 9 Х 11 К; 10 где Н - начало маршрута контроля; К - кОнец маршрута контроля, Хл - если выполняется условие соответствующей ветви программы, будет равХ- ным единице; 15 Хл - если не выполняется условие соответствующей ветви программы, Хл будет равным нулюДля минимально возможных повторений при прохождении участков программы 20 контроля введем дополнительные условия, которые обозначим льПри введении дополнительных переходов (фиг.4) последовательность значений условий будет выглядеть следующим обра зом: Н; Х 1 Хг лг лз лв л 1 Хг Хз лг Хз Х 1 Х 4 Х 5 Хв лз Х 4 л 4 Х 7 Хв Х 5 л 4 Х 7 Хв л 5 Х 9 Х 10 лв Хв Х 10 Х 11 Х 9 Х 11 К: Данный алгоритм контроля реализует ся в предлагаемом устройстве благодаря введению соответствующих технических средств, .Время выполнения программы контроля, реализованной предлагаемым устройст вом при т =т, = 1,30 уменьшается в 2,34раза. Формула изобретения Устройство для контроля тестопригод ных программ, содержащее блок памятипрограмм, регистр адреса, коммутатор адреса, мультиплексор логических условий, регистр контроля, первый элемент ИЛИ, причем вход кода операций устройства и "5 выход конца команды регистра контроля соединены соответственно с первым информационным и инверсным управляющим входами коммутатора адреса, выход которого соединен с информационным входом регистра адреса; выход которого соединен с входом блока памяти программ, выходы разрядов адреса, кода логических условий и микроопераций блока памяти программ соединены соответственно с вторым ин формационным входом коммутатора адреса, с адресным входом мультиплексора логических условий и с информационным входом регистра контроля, выход которого является выходом микроопераций устройства, вход логических условий устройства соединен с информационным входом мультиплексора логических условий, о т л и ч а ющ е е с я тем, что, с целью повышенияоперативности контроля. в устройство введены,блок памяти контрольных кодов сдвигающий регистр; блок сравнения,коммутатор условия, триггер режима работы, с первого по четвертый элементы И, второй элемент ИЛИ, причем вход кода 10операций устройства соединен с входомблока памяти контрольных кодов; выходыразрядов эталона и кода заданных условийблока памяти контрольных кодов соединены соответственно с первым информационным входом блока сравнения и синформационйым входом сдвигающего регистра, входы устройства "Контроль" и "Уп- .равление" соединены соответственно впервым и вторым входами триггера режима 20работы, выход которого соединен с первыми входами с первого по четвертый элементов И, прямым и инверсным уйравляющимивходами коммутатора условия, с разрешающим входом регистра контроля, выход мультиплексора логических условий соедийен спервым информационным входом коммутатора условий, выход первого элемента ИЛИсоединен с вторым информационным вхо- "дом коммутатора условия, первый тактовый ЗОвход устройства соединен с вторыми входами первого и второго элементов И, третийвход первого элемента И соединен с вцхо дом конца команды регистра контролч,ретий вход второго элемента И соединен с выходом первого элемента ИЛИ, выход первого элемента И соединен с входом записи сдвигающего регистра, выход второго элемента И соединен с входом сдвига сдвигаю- щего регистра, выход сдвигающего регистра соединен с вторым информационным входом коммутатора условия, выход коммутатора условия соединен с первым входом второго элемента ИЛИ, второй тактовый вход устройства соединен с синхровходом регистра контроля, выход которого является выходом микроопераций устройства и сбединен с вторым входом блокасравнения, выход которого соединен с вторым входом третьего элемента И и с вторым инверсным входом четвертого элемента И, выход последнего разряда регистра контроля соединен с третьими входами третьего и четвертого элементов И и является выходом "Конец программы" устройства, выход третьего элемента И является выходом "Норма" устройства, выход четвертого элемента И является выходом "Не норма" устройства, выход кода "логических условий блока памяти программ соединен с группой входов первого элемента ИЛИ, модифицируемый разряд блока памяти программ соединен с вторым входом второго элемента ИЛИ, выход которого соединен с разрядом второго информационного входа коммутаторч адреса.

СмотретьЗаявка

4861969, 21.08.1990

КОНСТРУКТОРСКОЕ БЮРО ЭЛЕКТРОПРИБОРОСТРОЕНИЯ

БЕК АЛЕКСАНДР ВЛАДИМИРОВИЧ, ЧЕРНЫШОВ МИХАИЛ АНАТОЛЬЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, СЕДЫХ НИКОЛАЙ ВЛАДИМИРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: программ, тестопригодных

Опубликовано: 30.07.1992

Код ссылки

<a href="https://patents.su/11-1751767-ustrojjstvo-dlya-kontrolya-testoprigodnykh-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля тестопригодных программ</a>

Предыдущий патент: Мажоритарно-резервированный интерфейс памяти

Следующий патент: Устройство для коррекции программ

Случайный патент: Способ получения 2-