Устройство для измерения сопротивления и емкости электрических и сигнальных сетей относительно земли

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1370611

Авторы: Брызгало, Карпиловский, Матвеев, Шуляев

Текст

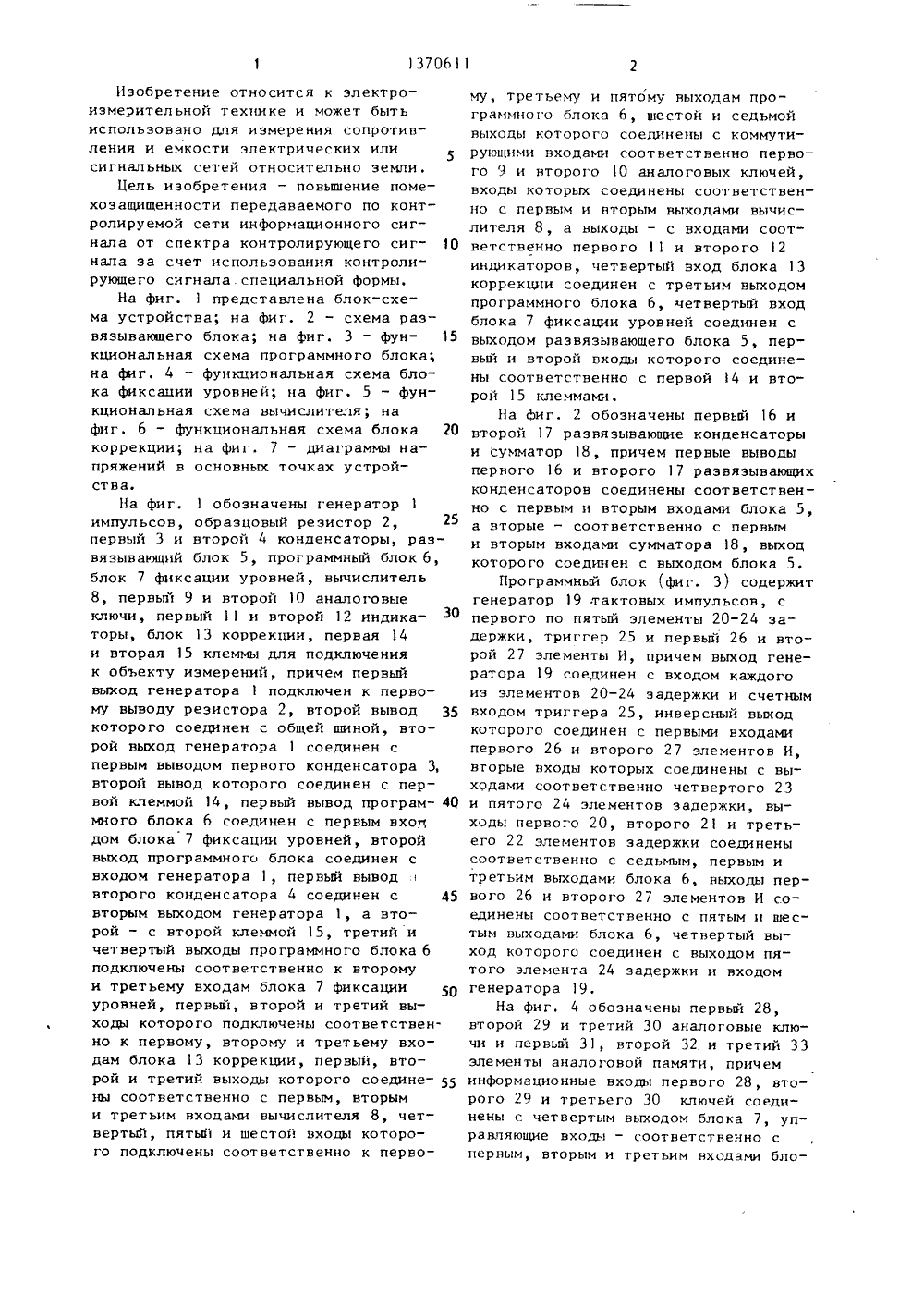

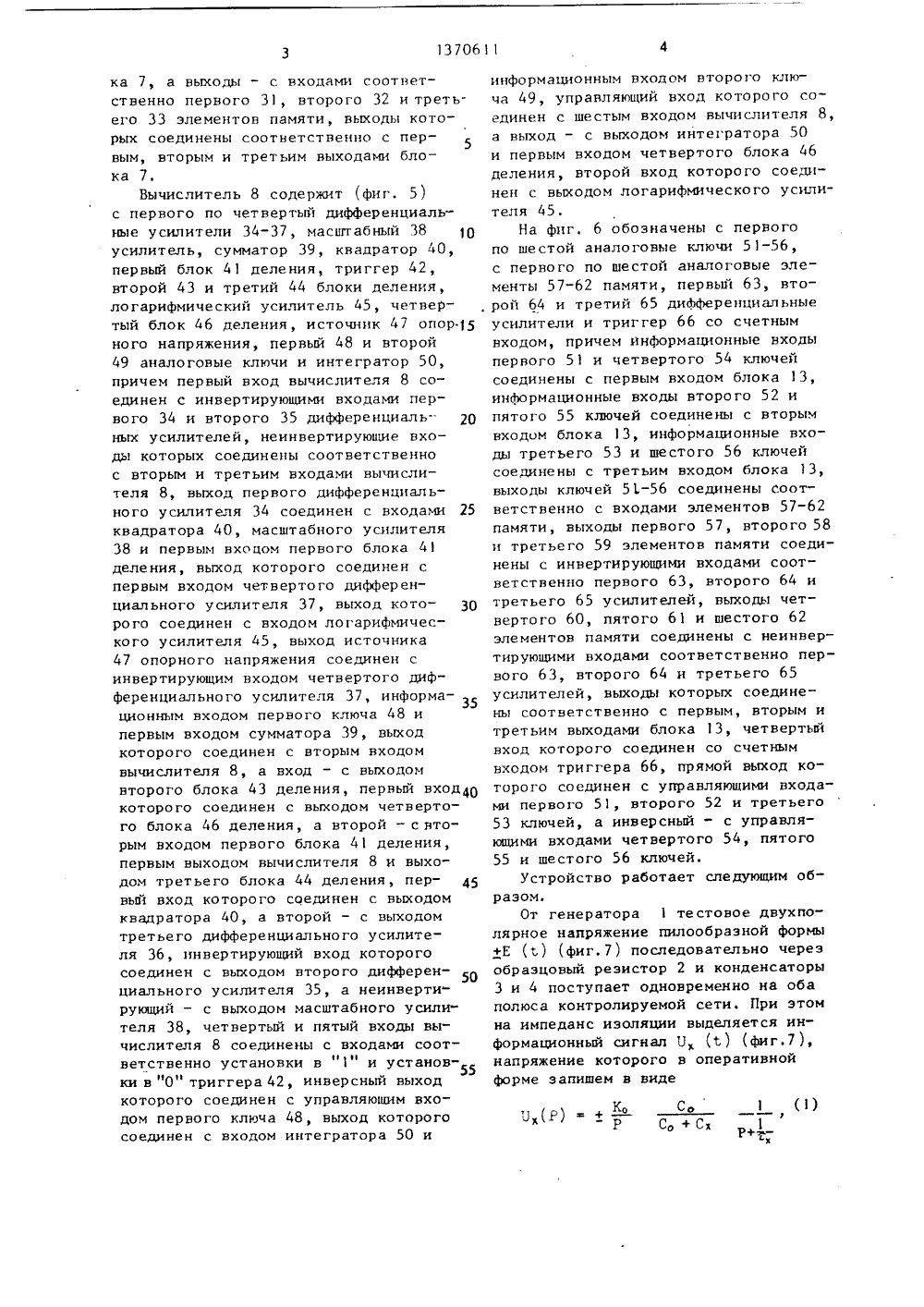

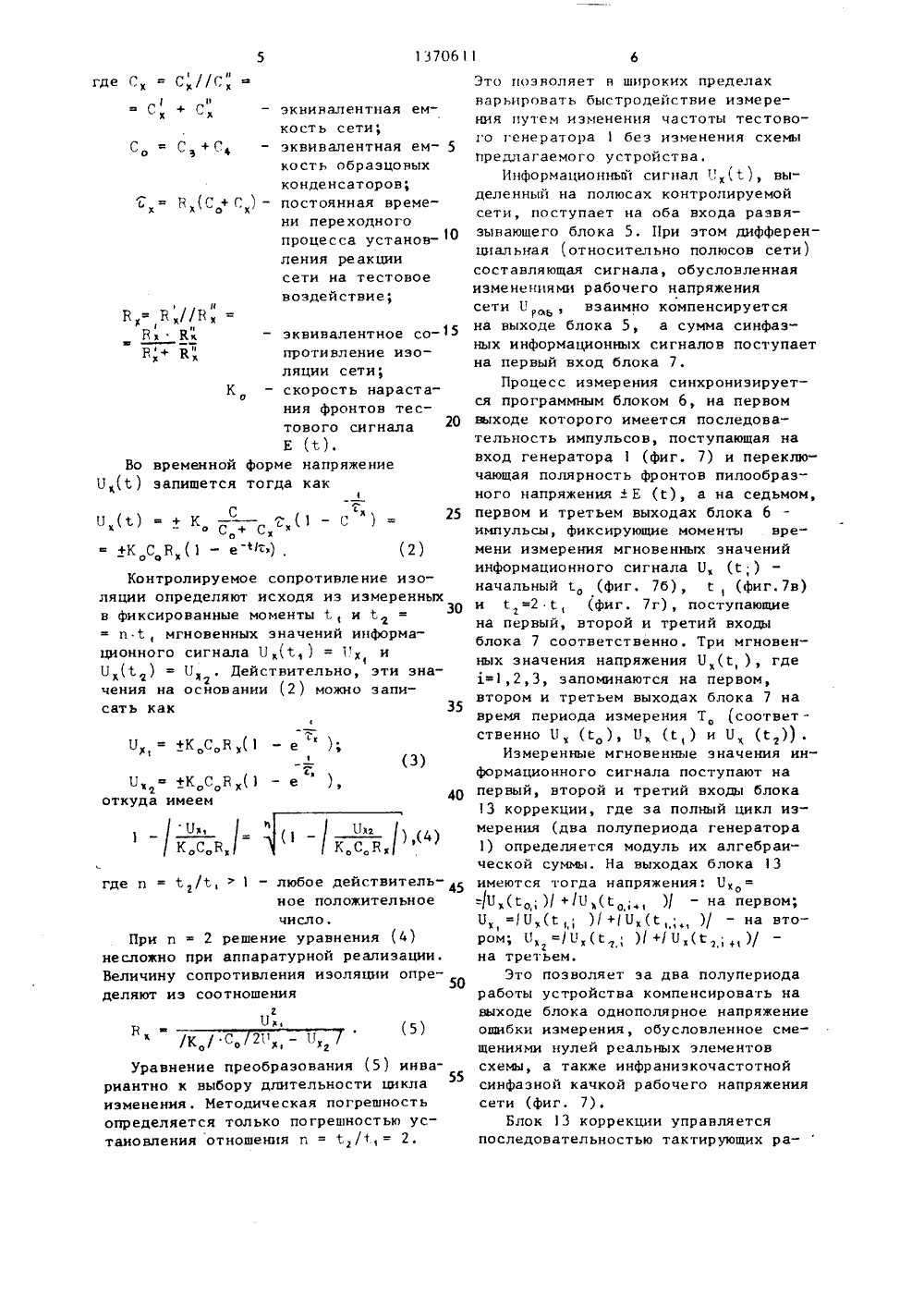

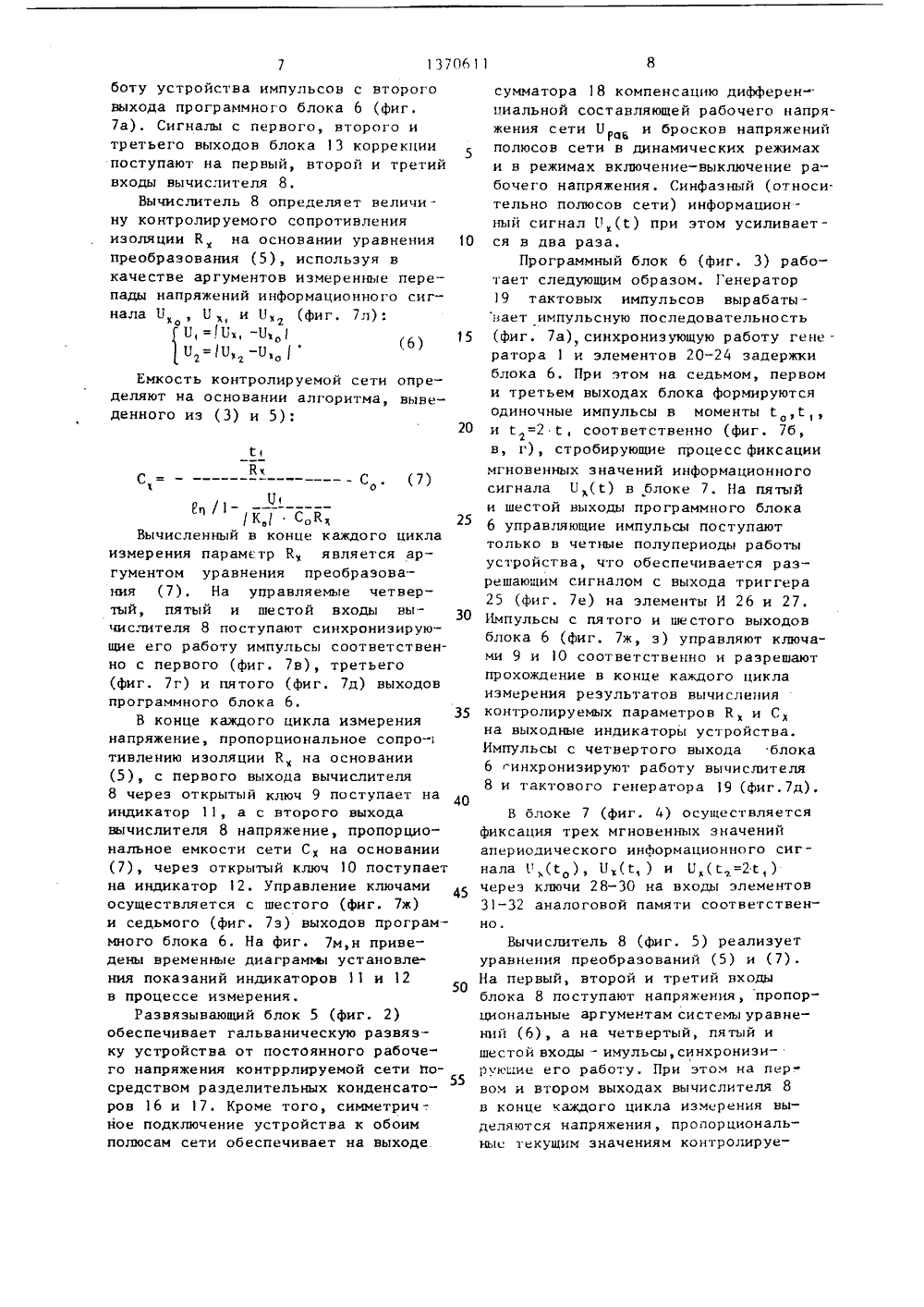

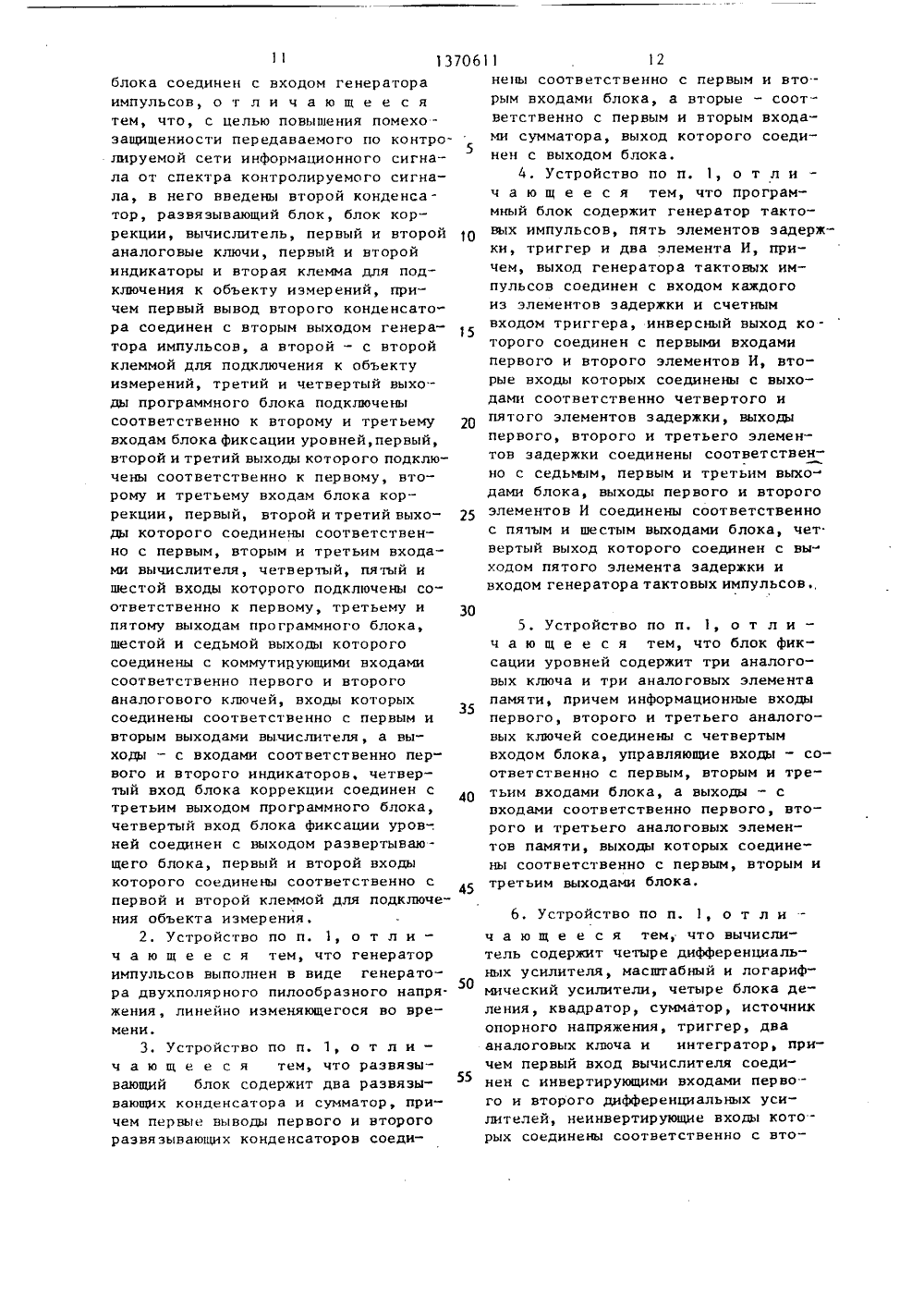

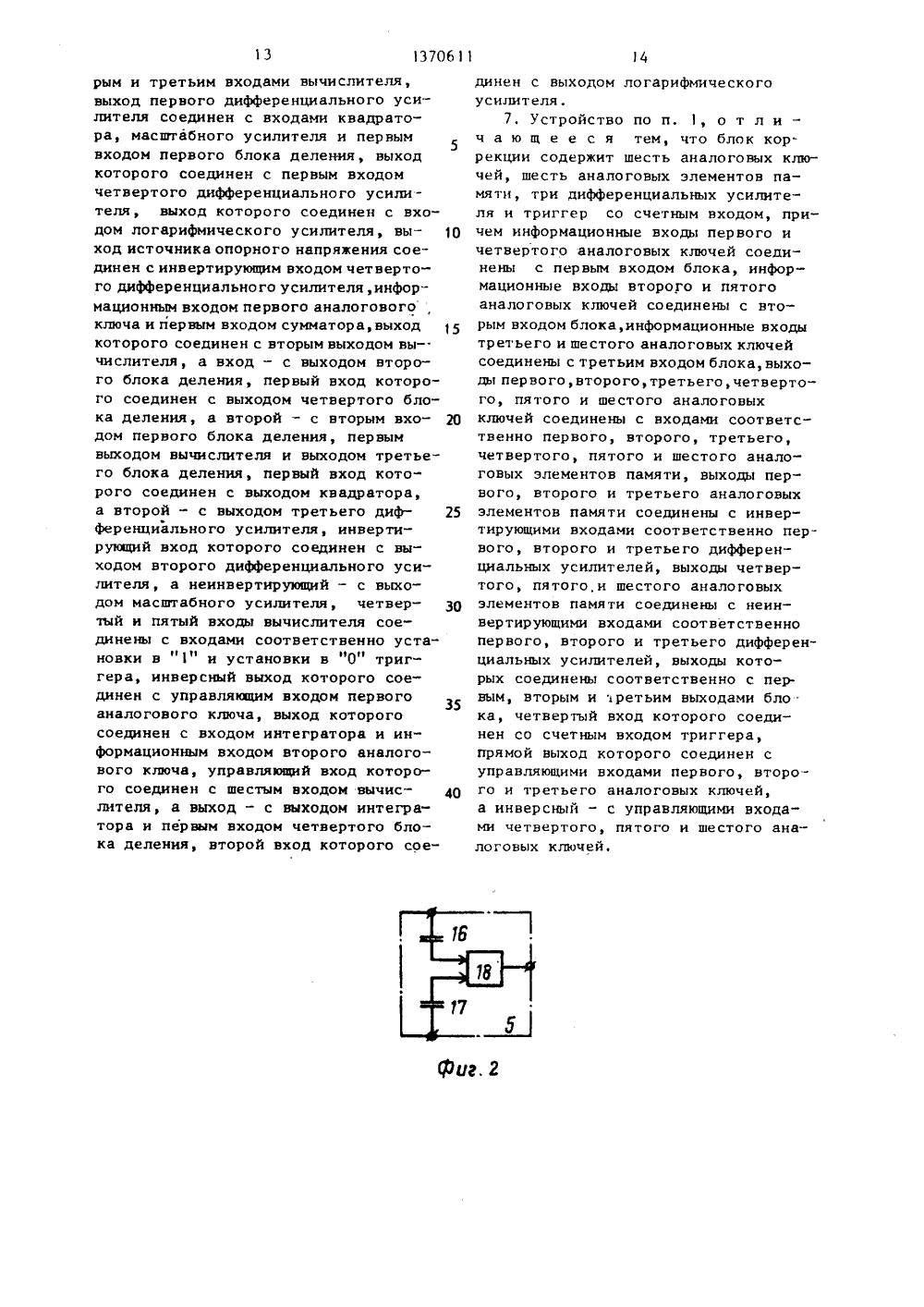

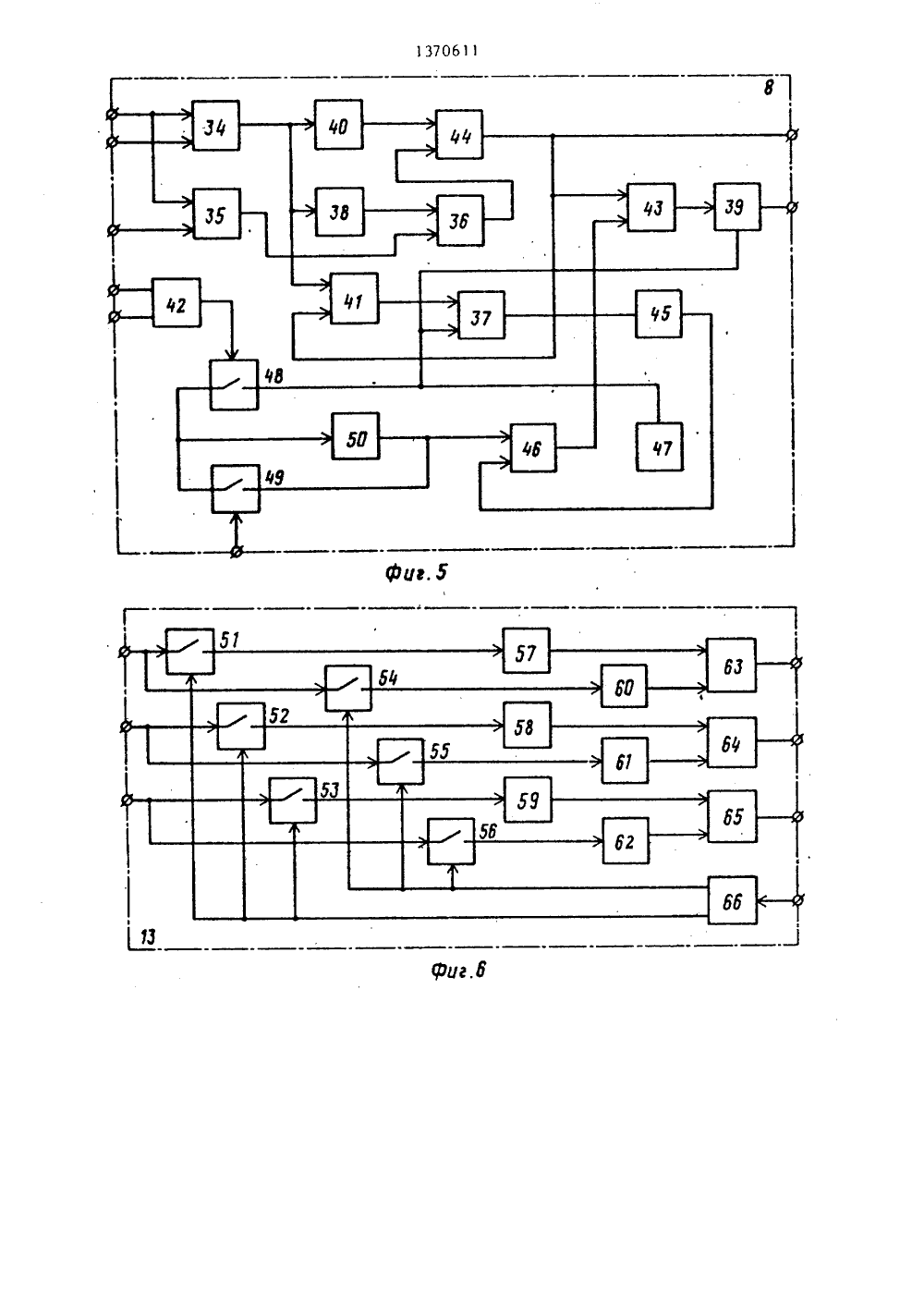

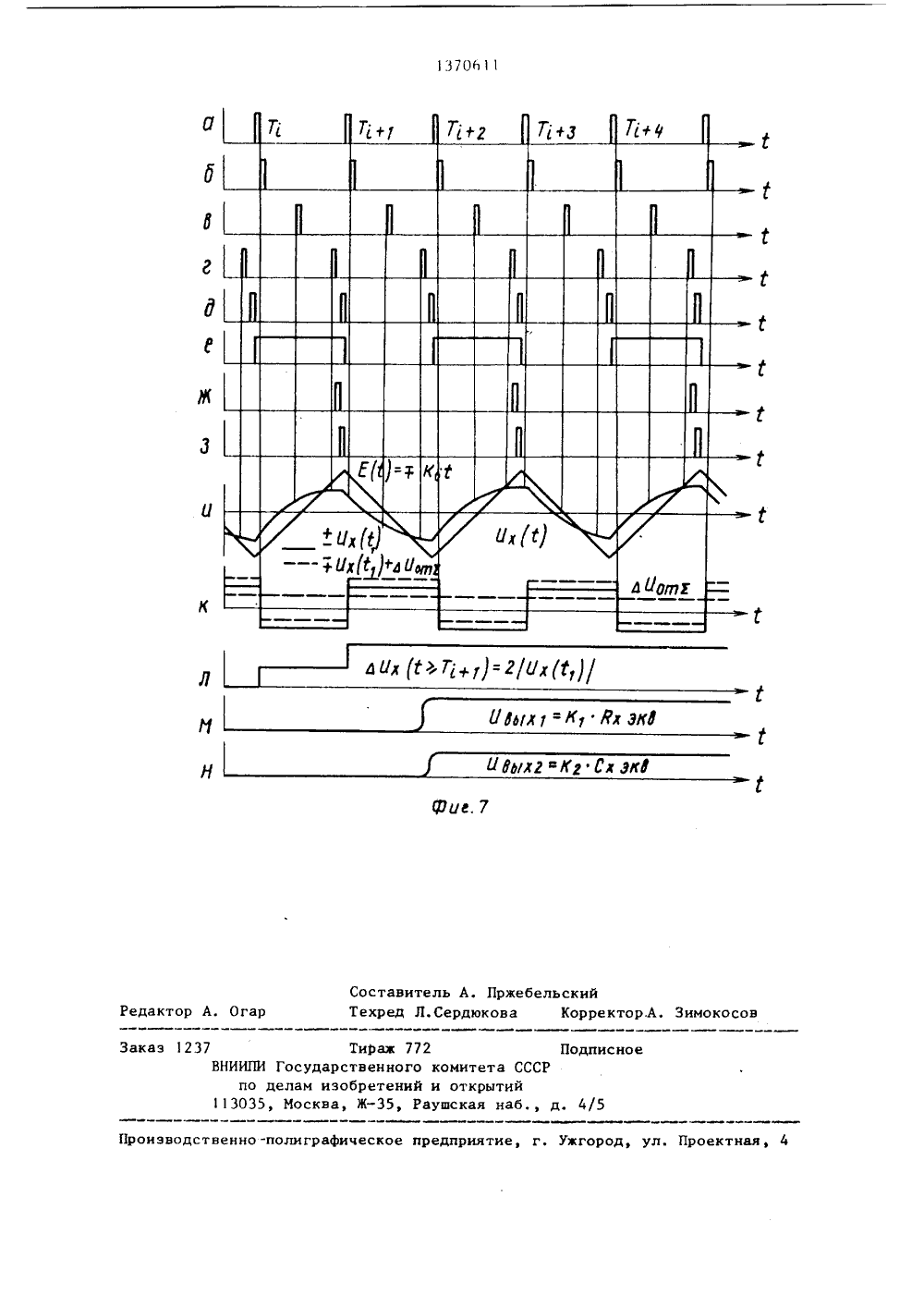

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК1370611 ииЯ 01 К 27/18 ПИСАНИЕ ИЗОБРЕТЕН эволяет ис сигнал сп приведены тора 1 им ка 5, про фиксации у ка 13 корр польэовациальнойпримерыульсо в,рам 1 ногоровней,екции. 6 раэвязывающего блоблока 6, блока 7вычислителя 8 и бло з.п.ф-лы, 7 ил,ОСУДАРСТВЕНИЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ТОРСКОМУ СВИДЕТЕЛЬСТВУ 21) 4059074/24-21 22) 18.04,86 (46) 30,01.88. Бюп, У 4 (71) Витебское областное производственно-техническое управление связи и Витебское производственное объединение "Электроизмеритель (72) В.Н. Брызгало, Л.Н. Карпиловский, И.М. Матвеев и В.Ф. Шуляен (53) 621.317.735(088.8) (56) Авторское свидетельство СССР У 978073, кл. С 01 К 27/18, 1980.Авторское свидетельстно СССР У 1118939, кл. С 01 К 27/18, 1983. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЯ И ЕМКОСТИ ЭЛЕКТРИЧЕСКИХ И СИГНАЛЬНЫХ СЕТЕЙ ОТНОСИТЕЛЬНО ЗЕМЛИ (57) Изобретение относится к электроиэмерительной технике и служит для3 повышения помехоэнаемого по контролмационного сигналролирующего сигналдержит генераторцовый резистор 2,граммный блок 6,уровней. Введениеразняэывающего бланалоговых ключей11 и 12, блока 13ванне новых функц щищенности передаируемой сети инфорот спектра конта. Устройство соимпульсов, образконденсатор 3, пролок 7 фиксацииконденсатора 4,ка 5, вычислителя 8,9 и 10, индикаторовкоррекции и образоональных связей поть контролирующийформы. В описанииреализации генера 1 370611(х 7 =Рх ЬИ 3 2 Кр Сх УУ е.7 Составитель А. ПржебельскийТехред Л.Сердюкова Корректор,А. Зимоко едактор А. 0 772 Заказ 1237 аб., д. 4/5 шска водственно -полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 НИИПИ Госуд по делам 13035, Москственн обретеЖо комитет й и откры ПодписноСССРИзобретение относится к электро- измерительной технике и может быть использовано для измерения сопротивления и емкости электрических или 5 сигнальных сетей относительно земли.Цель изобретения - повышение помехоэащищенности передаваемого по контролируемой сети информационного сигнала от спектра контролирующего сиг- О нала эа счет использования контролирующего сигнала. специальной формы.На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема развязывающего блока; на фиг. 3 - фун кциональная схема программного блока; на фиг. 4 - функциональная схема блока фиксации уровней; на фиг. 5 - функциональная схема вычислителя; на фиг. 6 - функциональная схема блока 20 коррекции; на фиг. 7 - диаграммы напряжений в основных точках устройства.На фиг. 1 обозначены генератор 1 импульсов, образцовый резистор 2, 25 первый 3 и второй 4 конденсаторы, развязывающий блок 5, программный блок 6, блок 7 фиксации уровней, вычислитель 8, первый 9 и второй 10 аналоговые ключи, первый 11 и второй 12 индикаторы, блок 13 коррекции, первая 14 и вторая 15 клеммы для подключения к объекту измерений, причем первый выход генератора 1 подключен к первому выводу резистора 2, второй вывод 35 которого соединен с общей шиной, второй выход генератора 1 соединен с первым выводом первого конденсатора 3, второй вывод которого соединен с первой клеммой 14, первый вывод програм много блока 6 соединен с первым вхот дом блока 7 фиксации уровней, второй выход программного блока соединен с входом генератора 1, первый вывод второго конденсатора 4 соединен с 45 вторым выходом генератора 1, а второй - с второй клеммой 15, третий и четвертый выходы программного блока 6 подключены соответственно к второму и третьему входам блока 7 фиксации уровней, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам блока 13 коррекции, первый, второй и третий выходы которого соедине ны соответственно с первым, вторым и третьим входами вычислителя 8, четвертый, пятый и шестой входы которого подключены соответственно к первому, третьему и пятому выходам программного блока 6, шестой и седьмой выходы которого соединены с коммутирующими входами соответственно первого 9 и второго 1 О аналоговых ключей, входы которых соединены соответственно с первым и вторым выходами вычислителя 8, а выходы - с входами соответственно первого 11 и второго 12 индикаторов, четвертый вход блока 13 коррекции соединен с третьим выходом программного блока 6, четвертый вход блока 7 фиксации уровней соединен с выходом раэвязывающего блока 5, первый и второй входы которого соединены соответственно с первой 14 и второй 15 клеммами.На Фиг. 2 обозначены первый 16 и второй 17 развязывающие конденсаторы и сумматор 18, причем первые выводы первого 16 и второго 17 развязывающих конденсаторов соединены соответственно с первым и вторым входами блока 5, а вторые - соответственно с первым и вторым входами сумматора 18, выход которого соединен с выходом блока 5,Программный блок (фиг. 3) содержит генератор 19 тактовых импульсов, с первого по пятый элементы 20-24 задержки, триггер 25 и первый 26 и второй 27 элементы И, причем выход генератора 19 соединен с входом каждого из элементов 20-24 задержки и счетным входом триггера 25, инверсный выход которого соединен с первыми входами первого 26 и второго 27 элементов И, вторые входы которых соединены с выходами соответственно четвертого 23 и пятого 24 элементов задержки, выходы первого 20, второго 21 и третьего 22 элементов задержки соединены соответственно с седьмым, первым и третьим выходами блока 6, выходы первого 26 и второго 27 элементов И соединены соответственно с пятым н шестым выходами блока 6, четвертый выход которого соединен с выходом пятого элемента 24 задержки и входом генератора 19.На фиг. 4 обозначены первый 28, второй 29 и третий 30 аналоговые ключи и первый 31, второй 32 и третий 33 элементы аналоговой памяти, причем информационные входы первого 28, второго 29 и третьего 30 ключей соединены с четвертым выходом блока 7, управляющие входы - соответственно с первым, вторым и третьим входами блока 7, а выходы - с входами соответственно первого 31, второго 32 и третьего 33 элементов памяти, выходы которых соединены соответственно с пер 5 вым, вторым и третьим выходами бло - ка 7.Вычислитель 8 содержит (фиг. 5) с первого по четвертый дифференциальные усилители 34-37, масштабный 38усилитель, сумматор 39, квадратор 40, первый блок 41 деления, триггер 42, второй 43 и третий 44 блоки деления, логарифмический усилитель 45, четвертый блок 46 деления, источник 47 опорного напряжения, первый 48 и второй 49 аналоговые ключи и интегратор 50, причем первый вход вычислителя 8 соединен с инвертирующими входами первого 34 и второго 35 дифференциаль ных усилителей, неинвертирующие входы которых соединены соответственно с вторым и третьим входами вычислителя 8, выход первого дифференциального усилителя 34 соединен с входами 25 квадратора 40, масштабного усилителя 38 и первым входом первого блока 4 деления, выход которого соединен с первым входом четвертого дифференциального усилителя 37, ВыхОд кОтОрого соединен с входом логарифмического усилителя 45, выход источника 47 опорного напряжения соединен с инвертирующим входом четвертого дифференциального усилителя 37, информационным входом первого ключа 48 и первым входом сумматора 39, выход которого соединен с вторым входом вычислителя 8, а вход - с выходом второго блока 43 деления, первый вход 40 которого соединен с выходом четвертого блока 46 деления, а второй - с Вторым входом первого блока 41 деления, первым выходом вычислителя 8 и выходом третьего блока 44 деления, пер вый вход которого соединен с выходом квадратора 40, а второй - с выходом третьего дифференциального усилителя 36, инвертирующий вход которого соединен с выходом второго дифференциального усилителя 35, а неинвертирующий - с выходом масштабного усилителя 38, четвертый и пятый входы вычислителя 8 соединены с входами соответственно установки в "1" и установки в "0" триггера 42, инверсный выход которого соединен с управляющим входом первого ключа 48, выход которого соединен с входом интегратора 50 и информационным входом второго ключа 49, управляющий вход которого соединен с шестым входом вычислителя 8,а выход - с выходом интегратора 50и первым входом четвертого блока 46деления, второй вход которого соединен с выходом логарифмического усилителя 45,На фиг. 6 обозначены с первогопо шестой аналоговые ключи 51-56,с первого по шестой аналоговые элементы 57-62 памяти, первый 63, вто, рой 64 и третий 65 дифференциальныеусилители и триггер 66 со счетнымвходом, причем Информационные входыпервого 51 и четвертого 54 ключейсоединены с первым входом блока 13,информационные входы второго 52 ипятого 55 ключей соединены с вторымвходом блока 13, информационные входы третьего 53 и шестого 56 ключейсоединены с третьим входом блока 13,выходы ключей 51-56 соединены соответственно с входами элементов 57-62памяти, выходы первого 57, второго 58и третьего 59 элементов памяти соединены с инвертирующими входами соответственно первого 63, второго 64 итретьего 65 усилителей, выходы четвертого 60, пятого 61 и шестого 62элементов памяти соединены с неинвертирующими входами соответственно первого 63, второго 64 и третьего 65усилителей, выходы которых соединены соответственно с первым, вторым итретьим выходами блока 13, четвертыйвход которого соединен со счетнымвходом триггера 66, прямой выход которого соединен с управляющими входами первого 51, второго 52 и третьего53 ключей, а инверсный - с управляющими входами четвертого 54, пятого55 и шестого 56 ключей.Устройство работает следующим образом.От генератора 1 тестовое двухполярное напряжение пилообразной формы+Е (С) (фиг,7) последовательно черезобразцовый резистор 2 и конденсаторы3 и 4 поступает одновременно на обаполюса контролируемой сети. При этомна импеданс изоляции выделяется информационный сигнал 1 (С ) (фиг.7 ),напряжение которого в оперативнойформе запишем в видеС//С- о + С где Сд Сх эквивалентная емкость сети;эквивалентная емкость образцовыхконденсаторов;постоянная времени переходногопроцесса устанонления реакциисети на тестовоевоздействие; С +Г з Х//11РХ+ КХ эквивалентное со протинление изоляции сети;К - скорость нарастаония фронтов тестового сигналаЕ (С).Во временной форме напряжение 11(С ) запишется тогда какСк( ) - о С + С х(о Х(4 и =С /С,1-любое7ное по иствительжител ьн ое сло ения (4)реализации При и 2 несложно при Величину соп ешение уранппаратурнойтивления изношения ляции апре еляют из се преобразован ыбору длительн Методическая и я только погре отношения и я (5) инвасти цикла55 грешност ь ностью ус- ,/С, = 2. Контролируемое сопротивление изоляции определяют исходя иэ измеренных30 н фиксированные моменты С, и С 7и С, мгновенных значений информационного сигнала ц,(С, ) = Пи(С 7) = 11, Действительно, эти зна- Х 7 7чения на основании (2) можно запиЭто поэволяет в широких пределахварьировать быстродействие измерения путем изменения частоты тестового генераторабез изменения схемыпредлагаемого устройства.Информационный сигнал 1 х(С) выделенный на полюсах контролируемойсети, поступает на оба входа раэвязывающего блока 5, При этом дифференциальная (относительно полюсов сети)составляющая сигнала, обуслонленнаяизменениями рабочего напряжениясети Ц аьвзаимно компенсируетсяна выходе блока 5, а сумма синфаэных информационных сигналов поступаетна первый вход блока 7,Процесс измерения синхронизируется программным блоком 6, на первомныходе которого имеется последовательность импульсов, поступающая навход генератора 1 (фиг. 7) и переключающая полярность фронтов пилообразного напряжения ф Е (С) а на седьмом,первом и третьем выходах блока 6импульсы, фиксирующие моменты времени измерения мгновенных значенийинформационного сигнала 11 х (С;)начальный С (фиг. 7 б), С, (фиг.7 в)и С =2 С, (фиг. 7 г), поступающиена первый, нторой и третий входЫблока 7 соответственно. Три мгновенных значения напряжения 11 х(С, ), гдедщ 123 запоминаются на первом,втором и третьем выходах блока 7 навремя периода измерения Т, (соответственно 11 (С) Пх (Т) " "х (С 7Измеренные мгновенные значения информационного сигнала поступают напервый, нторой и третий входы блока13 коррекции, где за полный цикл измерения (два полупериода генератора1) определяется модуль их алгебраической суммы. На выходах блока 13имеются тогда напряжения:=ПХ(С, )+Ах(С )/ - на втона третьем.Это позволяет эа дна полупериодаработы устройства компенсировать навыходе блока однополярное напряжениеошибки измерения, обусловленное смещениями нулей реальных элементовсхемы, а также инфранизкочастотнойсинфазной качкой рабочего напряжениясети (фиг. 7).Блок 13 коррекции управляетсяпоследовательностью тактирующих ра-С . (7) но.Вычислитель 8 (фиг, 5) реализуетуравнения преобразований (5) и (7).На первый, второй и третий входы 50блока 8 поступают напряжения, пропорциональные аргументам системы уравнений (6), а на четвертый пятый ишестой входы - имульсы,синхронизирующие его работу. При этом на первом и втором выходах вычислителя 8в конце каждого цикла измерения выделяются напряжения, пропорциональныс текущим значениям контролируеб оту устройства импульсов с второговыхода программного блока 6 (фиг.7 а). Сигналы с первого, второго и третьего выходов блока 13 коррекции поступают на первый, второй и третий входы вычислителя 8.Вычислитель 8 определяет величи - ну контролируемого сопротивления изоляции К на основании уравнения преобразования (5), используя в качестве аргументов измеренные перепады напряжений информационного сигнала П , Б , и П (фиг. 7 л):Емкость контролируемой сети определяют на основании алгоритма, выведенного из (3) и 5): 1Е /1- (К, . С.КВычисленный в конце каждого цикла измерения параметр К является аргументом уравнения преобразования (7). На управляемые четвертый, пятый и шестой входы вычислителя 8 поступают синхронизирующие его работу импульсы соответственно с первого (фиг. 7 в), третьего (фиг, 7 г) и пятого (фиг. 7 д) выходов программного блока 6.В конце каждого цикла измерения напряжение, пропорциональное сопро-. тивлению изоляции К на основании (5), с первого выхода вычислителя 8 через открытый ключ 9 поступает на индикатор 11, а с второго выхода вычислителя 8 напряжение, пропорциональное емкости сети С на основании (7), через открытый ключ 10 поступает на индикатор 12, Управление ключами осуществляется с шестого (фиг. 7 ж) и седьмого (фиг. 7 з) выходов программного блока 6. На фиг. 7 м,н приведены временные диаграммы установления показаний индикаторов 11 и 12 в процессе измерения.Развяэывающий блок 5 (фиг. 2) обеспечивает гальваническую развязку устройства от постоянного рабочего напряжения контррлируемой сети ггосредством разделительных конденсаторов 16 и 17. Кроме того, симметрич-, ное подключение устройства к обоим полюсам сети обеспечивает на выходе сумматора 18 компенсацию дифференггиальной составляющей рабочего напряжения сети П и бросков напряженийполюсов сети в динамических режимахи в режимах включение-выключение рабочего напряжения. Синфазный (относи.тельно полюсов сети) информационный сигнал П(Т) при этом усиливает - 1 О ся в два раза.Программный блок 6 (фиг. 3) работает следующим образом. Генератор19 тактовых импульсов вырабаты -нает импульсную последовательность 15 (фиг. 7 а), синхронизующую работу генератора 1 и элементов 20-24 задержкиблока 6. При этом на седьмом, первоми третьем выходах блока формируютсяодиночные импульсы в моменты ТС 20 и Т=2 С, соответственно (фиг. 7 б,в, г), стробирующие процесс фиксациимгновенных значений информационногосигнала 13 в блоке 7, На пятыйи шестой выходы программного блока6 управляющие импульсы поступаюттолько в четные полупериоды работыустройства, что обеспечивается разрешающим сигналом с выхода триггера25 (фиг. 7 е) на элементы И 26 и 27.Импульсы с пятого и шестого выходовблока 6 (фиг, 7 ж, э) управляют ключами 9 и 10 соответственно и разрешаютпрохождение в конце каждого циклаизмерения результатов вычисления 35 контролируемых параметров Ки Сна выходные индикаторы устройства.Импульсы с четвертого выхода блока6 синхронизируют работу вычислителя8 и тактового генератора 19 (фиг.7 д).40В блоке 7 (фиг. 4) осуществляетсяфиксация трех мгновенных значенийапериодического информационного сигнала Гл(со), П(т, ) и Бк(сг.=2) 45 чр ключи 28 30 на входы элементов31-32 аналоговой памяти соответствен 1370611 10Блок 13 коррекции (фиг. Ь) предназначен для компенсации напряжения ошибки 11 (фиг, 7 и) измерения уровней информационного сигнала 0(й), вызванного процессом медлен 55 мых сопротивления изоляции Ки емкости сети С соответственно,Вычислитель 8 работает следующимобразом. Напряжения 11, и 11, являютщиеся аргументами уравнения преобразования (5), определяются на выходах первого 34 и второго 35 дифференциальных усилителей. Напряжение,пропорциональное искомому сопротивлению изоляции К , имеется на выходе системы решающих блоков: квадратора 40, масштабного усилителя 38,третьего дифференциального усилителя 36 и третьего блока 44 деленияреализующих алгоритмы преобразова.ния (5),Емкость сети С определяется навтором выходе вычислителя 8 в видепропорционального ей напряжения на 20основании алгоритма (7), При этомзнаменатель уравнения преобразования (7) определяется на выходе системы решающих блоков: первого блока41 деления, четвертого дифференциаль ного усилителя 37 и логарифмирующегоусилителя 45. Аргументами системыблоков являются напряжение П напряжение - результат вычисления эквивалентной изоляции Ксети с первого выхода блока 8 и опорное напряжение 11 с выхода источника 47.ооЗначение числителя уравнения( 7)имеется на выходе интегратора 50,подключенного к источнику 47 опорного напряжения в течение интервалаТ С -й .Это обеспечивается управинтоляемым ключом 48 и триггером 42 сустановочными входами, управляемымсинхроимпульсами с первого и третьего выходов программного блока 6(фиг. 7 б, в). Окончательно алгоритмпреобразования (7) реализуется навыходе системы решающих блоков: четвертого 46 и второго 43 блоков деления и сумматора 39. В конце каждого полупериода измерения интегратор50 сбрасывается в нулевое состояниепосредством ключа 49, управляемогосинхроимпульсом с четвертого выходапрограммного блока 6 (фиг.7 д). Этонеобходимо для подготовки интегратора 50 к новому полупериоду измерения,но протекающего перераспределения рабочего напряжения сети между полюсами в динамических режимах коммутации потребителей с несимметричной изоляцией полюсов и дрейфом нулей реальных усилительных элементов схемы. Коррекция осуществляется за два полупериода работы схемы, причем в четные полупериоды открыты ключи 51-53 блока 13 и мгновенные значения информационного сигнала Бх(Г ),О,1 11 х (Т,) и 11(й=2 ,) запоминаются элементами 57-59 аналоговой памятисоответственно, а в нечетные значенйя 11 х(с ),11( 1) и Бх(Ег 2)че рез ключи 54-56 запоминаются элементами 60-62 аналоговой памяти. Управление ключами осуществляется с противофазных выходов триггера 66 со счетным входом, переключающегося син. хроимпульсами с второго выхода программного блока 6 (фиг. 7 а). При этом запомненные информационные сигналы с выходов первой и второй группы элементов 57-59 и 60-62 аналоговой памяти поступают на дифференциальные входл соответствующих усилителей 63-65 в противофазе. Это обеспечивает удвоение уровня информационных сигналов в соответствующие моменты С, С т =2 С измеренные в четные и нечетные полупериоды работы устройства, а также компенсирует на выходах дифференциальных усилителей 63-65 синфазное напряжение ошибки 11 ол, (фиг. 7 к).формула изобретения1. Устройство для измерения сопротивления и емкости электрических и сигнальных сетей относительно земли, содержащее генератор импульсов, образцовый резистор, первый конденсатор, программный блок, блок фиксации уровней, первую клемму для подключения к объекту измерения, первый выход генератора импульсов соединен с первым выводом образцового резистора, второй вывод которого соединен с общей юыной, второй выход генератора импульсов соединен с первым выводом первого конденсатора, второй вывод которого соединен с первой клеммой для подключения к объекту измерения, первый выход программного блока соединен с первым входом блока фиксации уровней, второй выход программного30 35 40 45 50 55 блока соединен с входом генератораимпульсов, отличающеесятем, что, с целью повышения помехозащищениости передаваемого по контролируемой сети информационного сигнала от спектра контролируемого сигнала, в него введены второй конденсатор, развязывающий блок, блок коррекции, вычислитель, первый и второйаналоговые ключи, первый и второйиндикаторы и вторая клемма для подключения к объекту измерений, причем первый вывод второго конденсатора соединен с вторым выходом генератора импульсов, а второй - с второйклеммой для подключения к объектуизмерений, третий и четвертый выходы программного блока подключенысоответственно к второму и третьемувходам блокафиксации уровней, первый,второй и третий выходы которого подключены соответственно к первому, второму и третьему входам блока коррекции, первый, второй и третий выходы которого соединены соответственно с первым, вторым и третьим входами вычислителя, четвертый, пятый ишестой входы которого подключены соответственно к первому, третьему ипятому выходам программного блока,шестой и седьмой выходы которогосоединены с коммутирующими входамисоответственно первого и второгоаналогового ключей, входы которыхсоединены соответственно с первым и вторым выходами вычислителя, а выходы - с входами соответственно первого и второго индикаторов, четвертый вход блока коррекции соединен с третьим выходом программного блока, четвертый вход блока фиксации уров-. ней соединен с выходом развертывающего блока, первый и второй входы которого соединены соответственно с первой и второй клеммой для подключения объекта измерения.2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что генератор импульсов выполнен в виде генератора двухполярного пилообразного напря. жения, линейно изменяющегося во времени.3. Устройство по и, 1, о т л и - ч а ю щ е е с я тем, что развязывающий блок содержит два развязывающих конденсатора и сумматор, причем первые выводы первого и второго развязывающих конденсаторов соеди 5 10 15 20 25 иены соответственно с первым и вторым входами блока, а вторые - соответственно с первым и вторым входами сумматора, выход которого соединен с выходом блока.4, Устройство по и. 1, о т л и ч а ю щ е е с я тем, что программный блок содержит генератор тактовых импульсов, пять элементов задержки, триггер и два элемента И, причем, выход генератора тактовых импульсов соединен с входом каждого из элементов задержки и счетным входом триггера, инверсный выход ко . торого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены с выходами соответственно четвертого и пятого элементов задержки, выходы первого, второго и третьего элементов задержки соединены соответственно с седьмым, первым и третьим выходами блока, выходы первого и второго элементов И соединены соответственно с пятым и шестым выходами блока, чет. вертый выход которого соединен с выходом пятого элемента задержки и входом генератора тактовых импульсов.,5. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что блок фиксации уровней содержит три аналоговых ключа и три аналоговых элемента памяти, причем информационные входы первого, второго и третьего аналоговых ключей соединены с четвертым входом блока, управляющие входы - соответственно с первым, вторым и третьим входами блока, а выходы - с входами соответственно первого, второго и третьего аналоговых элементов памяти, выходы которых соединены соответственно с первым, вторым и третьим выходами блока. 6. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что вычислитель содержит четыре дифференциальных усилителя, масштабный и логарифмический усилители, четыре блока деления, квадратор, сумматор, источникопорного напряжения, триггер, двааналоговых ключа и интегратор, причем первый вход вычислителя соединен с инвертирующими входами первого и второго дифференциальных усилителей, неинвертирующие входы которых соединены соответственно с вто 13137061114рым и третьим входами вычислителя, выход первого дифференциального усилителя соединен с входами квадратора, масштабного усилителя и первым5 входом первого блока деления, выход которого соединен с первым входом четвертого дифференциального усилителя, выход которого соединен с входом логарифмического усилителя, вы ход источника опорного напряжения соединен с инвертирующим входом четвертого дифференциального усилителя,информационным входом первого аналогового ключа и первым входом сумматора, выход которого соединен с вторым выходом вы-. числителя, а вход - с выходом второго блока деления, первый вход которого соединен с выходом четвертого блока деления, а второй - с вторым вхо дом первого блока деления, первым выходом вычислителя и выходом третьего блока деления, первый вход которого соединен с выходом квадратора, а второй - с выходом третьего диф ференциального усилителя, инвертирующий вход которого соединен с выходом второго дифференциального усилителя, а неинвертирующий - с выходом масштабного усилителя, четвер- ЗО тый и пятый входы вычислителя соединены с входами соответственно установки в " 1" и установки в "О" триггера, инверсный выход которого соединен с управляющим входом первого аналогового ключа, выход которого соединен с входом интегратора и информационным входом второго аналогового ключа, управляющий вход которого соединен с шестым входом зычис лителя, а выход - с выходом интегратора и первым входом четвертого блока деления, второй вход которого соединен с выходом логарифмическогоусилителя,7, Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок коррекции содержит шесть аналоговых ключей, шесть аналоговых элементов памяти, три дифференциальных усилителя и триггер со счетным входом, причем информационные входы первого ичетвертого аналоговых ключей соединены с первым входом блока, информационные входы второго и пятогоаналоговых ключей соединены с вторым входом блока, информационные входытретьего и шестого аналоговых ключейсоединены с третьим входом блока, выходы первого, второго, третьего,четвертого, пятого и шестого аналоговыхключей соединены с входами соответственно первого, второго, третьего,четвертого, пятого и шестого аналоговых элементов памяти, выходы первого, второго и третьего аналоговыхэлементов памяти соединены с инвертирующими входами соответственно первого, второго и третьего дифференциальных усилителей, выходы четвертого, пятого,и шестого аналоговыхэлементов памяти соединены с неинвертирующими входами соответственнопервого, второго и третьего дифференциальных усилителей, выходы которых соединены соответственно с первым, вторым и третьим выходами бло -ка, четвертый вход которого соединен со счетным входом триггера,прямой выход которого соединен суправляющими входами первого, второго и третьего аналоговых ключей,а инверсный - с управляющими входами четвертого, пятого и шестого аналоговых ключей.

СмотретьЗаявка

4059074, 18.04.1986

ВИТЕБСКОЕ ОБЛАСТНОЕ ПРОИЗВОДСТВЕННО-ТЕХНИЧЕСКОЕ УПРАВЛЕНИЕ СВЯЗИ, ВИТЕБСКОЕ ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ЭЛЕКТРОИЗМЕРИТЕЛЬ"

БРЫЗГАЛО ВЛАДИМИР НИКОЛАЕВИЧ, КАРПИЛОВСКИЙ ЛЕОНИД НАУМОВИЧ, МАТВЕЕВ ИГОРЬ МИХАЙЛОВИЧ, ШУЛЯЕВ ВЛАДИМИР ФЕДОРОВИЧ

МПК / Метки

МПК: G01R 27/18

Метки: емкости, земли, относительно, сетей, сигнальных, сопротивления, электрических

Опубликовано: 30.01.1988

Код ссылки

<a href="https://patents.su/11-1370611-ustrojjstvo-dlya-izmereniya-soprotivleniya-i-emkosti-ehlektricheskikh-i-signalnykh-setejj-otnositelno-zemli.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для измерения сопротивления и емкости электрических и сигнальных сетей относительно земли</a>

Предыдущий патент: Датчик мощности и коэффициента стоячей волны

Следующий патент: Датчик пульсаций электропроводности жидкости

Случайный патент: Установка для нанесения покрытия на изделия формы тел вращения