Декодирующее устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

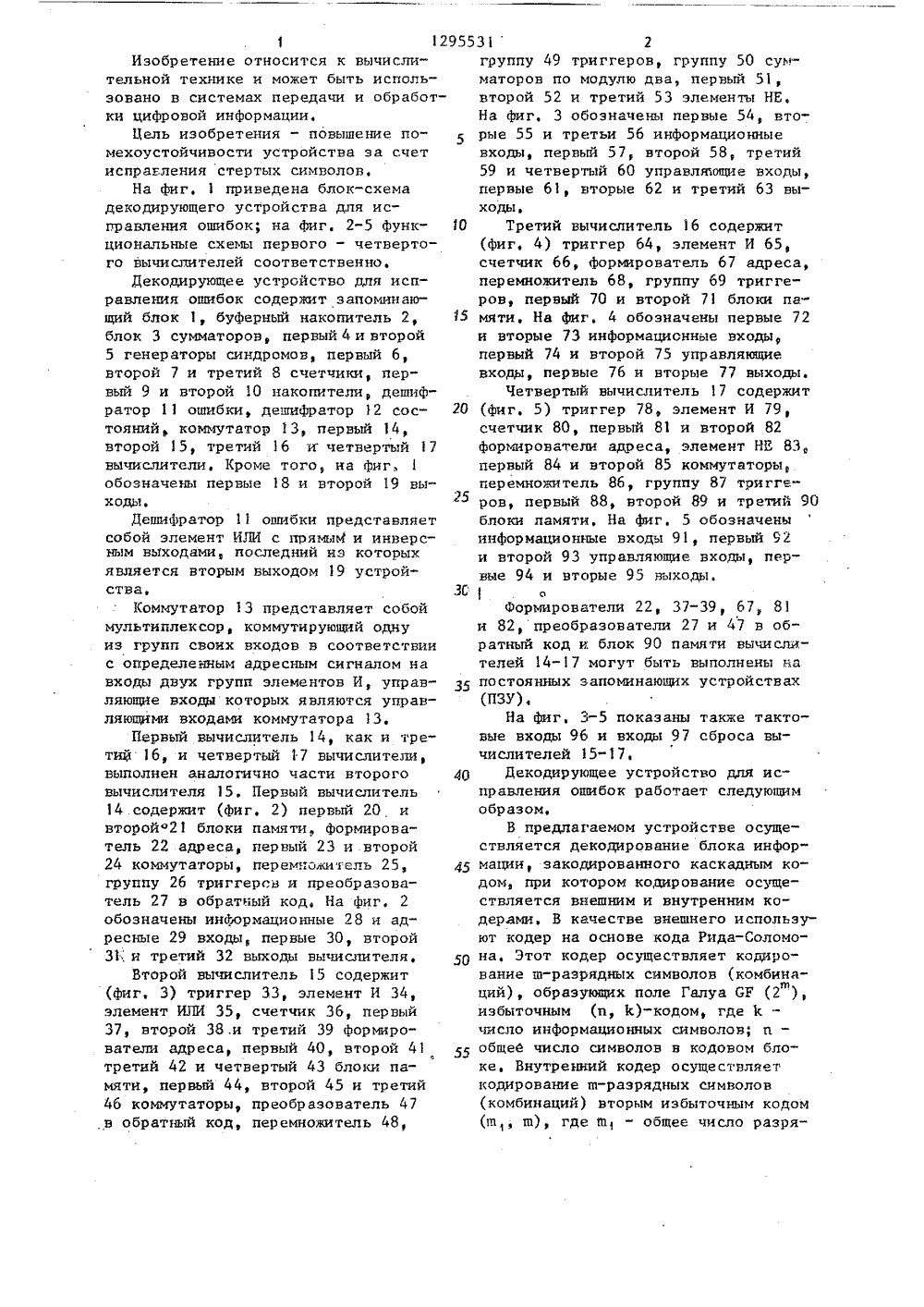

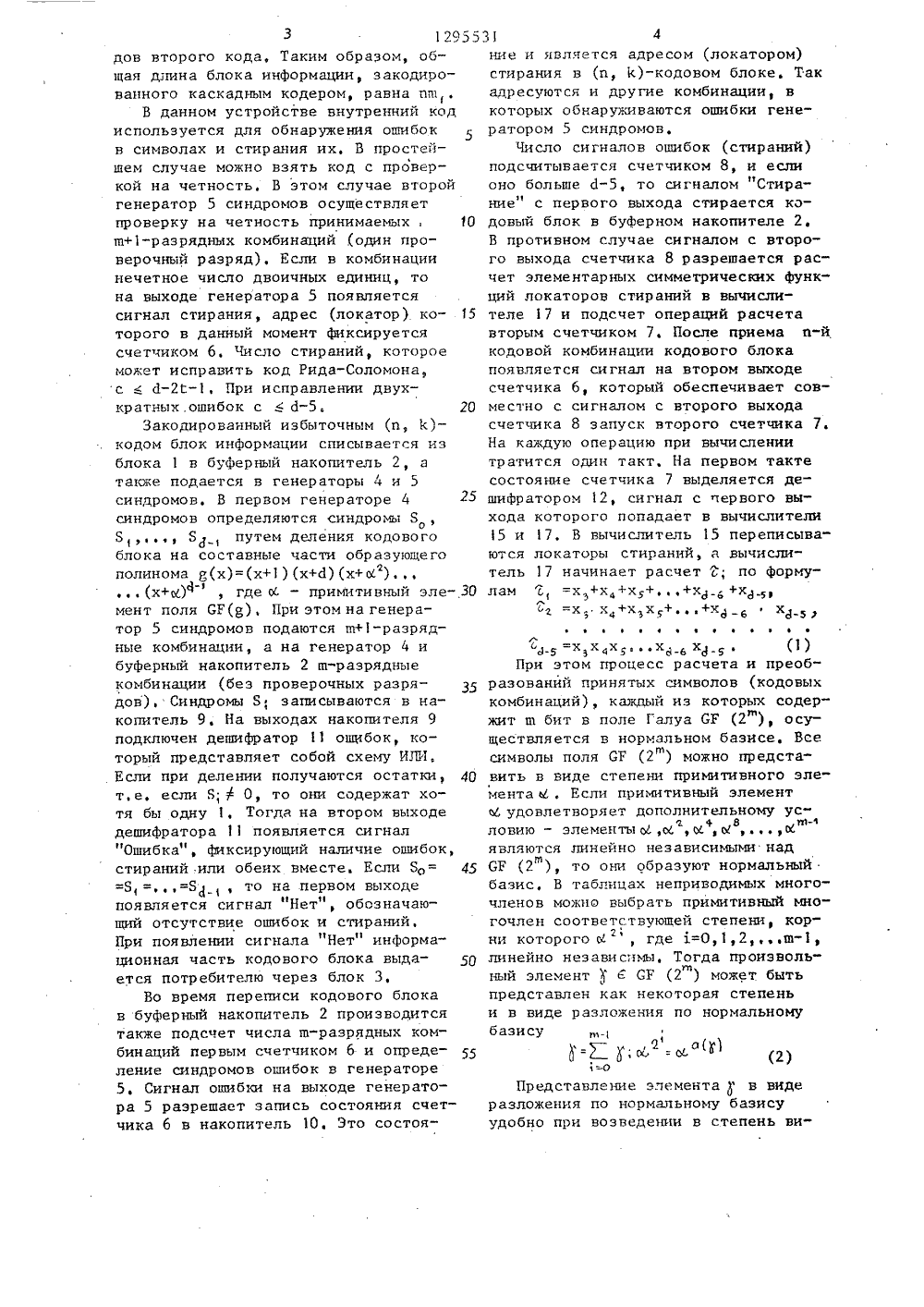

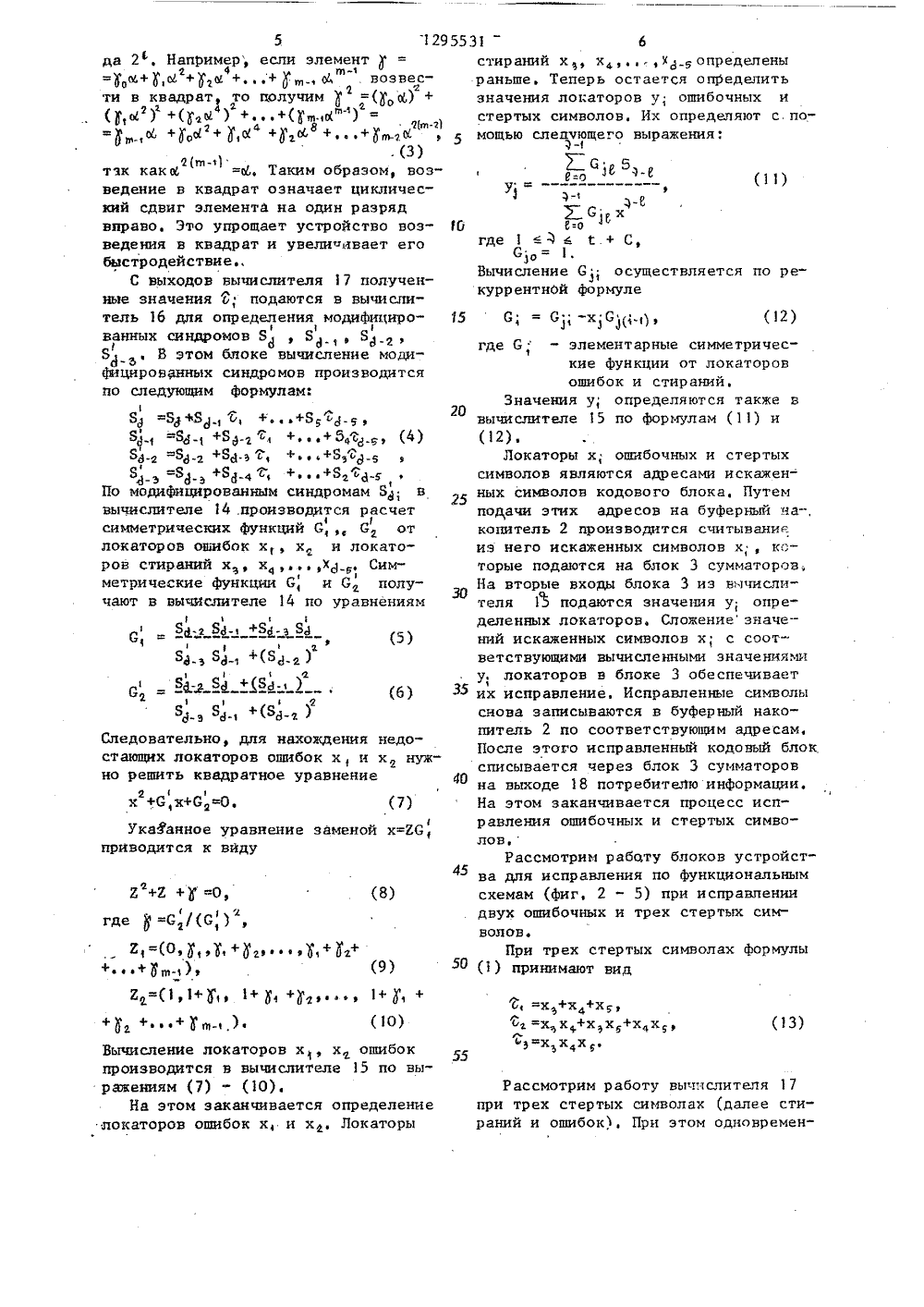

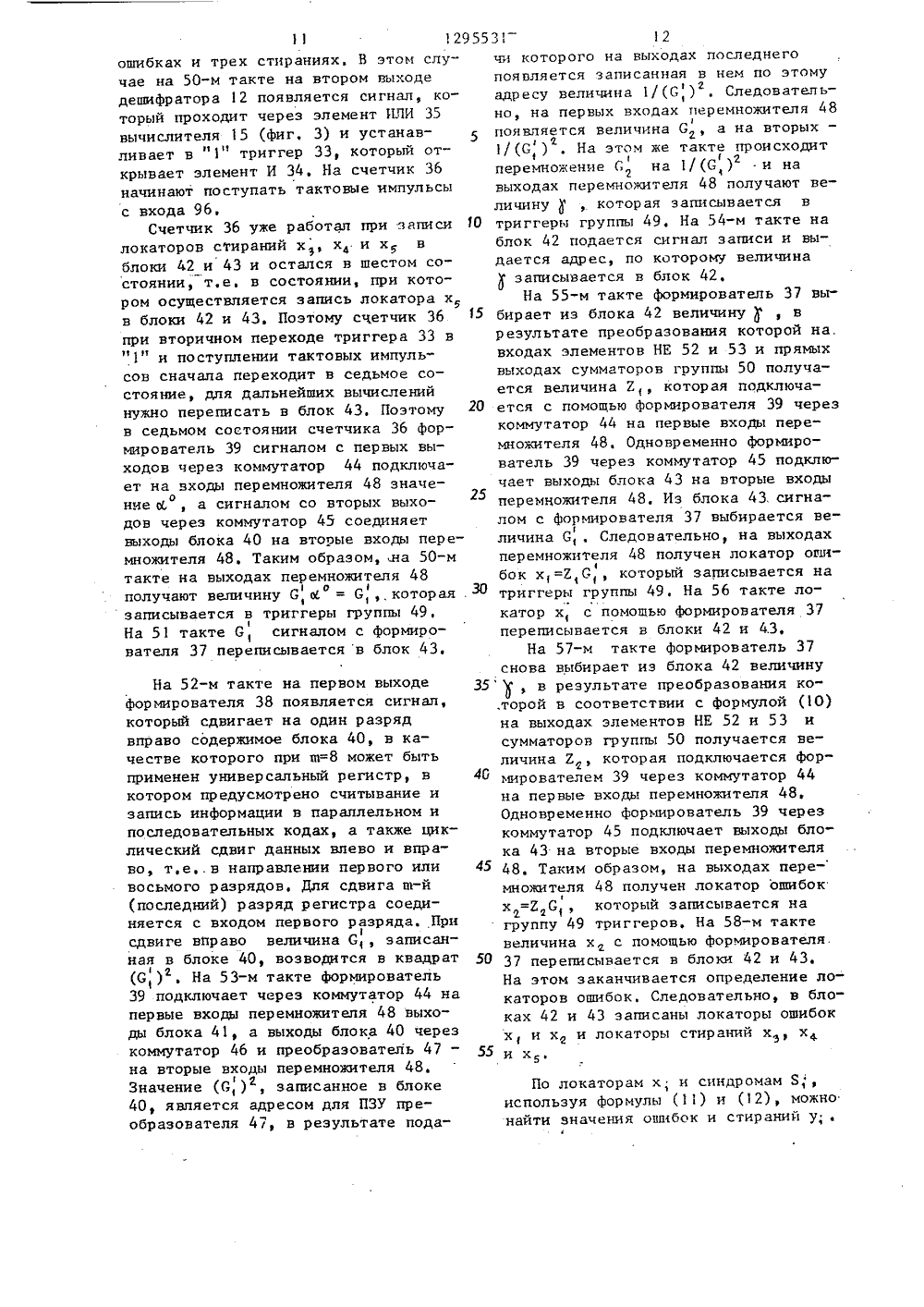

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК О 1 ДЯД М 13/ОО Н 03 ОПИСАНИЕ ИЗОБРЕТЕНИЯ АВТОРСКОМУ СВИДЕТЕПЫЮВУ в В,. В, Зябл М. Додунеков Г, И, Битков ) 4142174,1982.тельство СССР3 11 13/00,УЮЩЕЕ УСТРОЙСТВО ДЛЯШИБОКние относится к вычислике. Его использование ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(57) Изобрететельной техни в системах передачи и обработки циф" ровой информации обеспечивает повышение помехоустойчивости устройстваза счет исправления стертых символов, Цекодирующее устройство содержит за" поминающий блок 1, буферный накопитель 2, блок 3 сумматоров, первый генератор 4 синдромов, первый накопитель 9, дешифратор 11 ошибки, вычислители 14, 15. Введение второго генератора 5 синдромов, счетчиков 6-8, второго накопителя 10, дешифратора 12 состояний и вычислителей 16, 17 позволяет определять положение стертых символов и их исправление наряду с исправлением ошибок при работе в кодах Рида-Соломона, 5 ил.1295531 ектор Т. К Тираж 902арственного комитета СССРизобретений и открытийЖ"35, Раушская наб., д. Подписи 8/62ВНИИПИ Г Заказ делам Москва, 4/ полиграфическое предприяти Проектная, 4 Произ жгород тве Составитель О, Ревинскийедактор Н, Тупица Техред Л;Сердокова Ко1 12955Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки цифровой информации,Дель изобретения - повышение помехоустойчивости устройства за счетисправления стертых символов,На Фнг, 1 приведена блок-схемадекодирующего устройства для исправления ошибок; на Фиг. 2-5 функ Оциональные схемы первого - четвертого вычислителей соответственно.Декодирующее устройство для исправления ошибок содержит запоминающий блок 1, буФерный накопитель 2, 15блок 3 сумматоров, первый 4 и второй5 генераторы синдромов, первый 6,второй 7 и третий 8 счетчики, пер"вый 9 и второй 10 накопители, дешиф"ратор 11 ошибки, дешиФратор 12 состояний, коммутатор 13, первыйвторой 15, третий 16 и четвертый 17вычислители. Кроме того, на фиг 1обозначены первые 18 и второй 19 выходы.25Дешифратор 11 ошибки представляетсобой элемент ИЛИ с прямыМ и инверсным выходами, последний из которыхявляется вторым выходом 19 устройства. ЗСКоммутатор 13 представляет собоймультиплексор, коммутирующий однуиз групп своих входов в соответствиис определенным адресным сигналом навходы двух групп элементов И, управляющие входы которых являются управляннцими входами коммутатора 13.Первый вычислитель 14, как и трети 9 16, и четвертый 17 вычислители,выполнен аналогично части второго 40вычислителя 15, Первый вычислитель14.содержит (Фиг. 2) первый 20 ивторой 2 блоки памяти формирователь 22 адреса, первый 23 и второй24 коммутаторы, перемножитель 25,группу 26 триггеров и преобразователь 27 в обратный код, На фиг, 2обозначены информационные 28 и адресные 29 входы, первые 30, второй31, и третий 32 выхода вычислителя, 50Второй вычислитель 15 содержит(Фиг, 3) триггер 33, элемент И 34,элемент ИЛИ 35, счетчик 36, первый37, второй 38,и третий 39 формирователи адреса, первый 40, второй 41третий 42 и четвертый 43 блоки па"мяти, первый 44, второй 45 и третий46 коммутаторы, преобразователь 47в обратный код, перемножитель 48,31 2группу 49 триггеров, группу 50 сумматоров по модулю два, первый 51,второй 52 и третий 53 элементы НЕ.На фиг. 3 обозначены первые 54, вторые 55 и третьи 56 информационныевходы, первый 57, второй 58, третий59 и четвертый 60 управлвощие входы,первые 61, вторые 62 и третий 63 выхода,Третий вычислитель 16 содержит(фиг. 5) триггер 78, элемент И 79,счетчик 80, первый 81 и второй 82формирователи адреса, элемент НЕ 83первый 84 и второй 85 коммутаторы,перемножитель 86, группу 87 тригге"ров, первый 88, второй 89 и трегий 90блоки памяти, На фиг. 5 обозначеныинформационные входы 91, первый 92и второй 93 управляющие входы, первые 94 и вторые 95 выходы.оФормирователи 22, 37-39, 67 81и 82, преобразователи 27 и 47 в обратный код и блок 90 памяти вычислителей 14-17 могут быть выполнены напостоянных запоминающих устройствах(ПЗУ),На Фиг, 3-5 показаны также тактовые входы 96 и входы 97 сброса вычислителей 15-17,Декодирующее устройство для исправления опыбок работает следующимобразом.В предлагаемом устройстве осуществляется декодирование блока информации, закодированного каскадным кодом, при котором кодирование осуществляется внешним и внутренним кодерами, В качестве внешнего используют кодер на основе кода Рида-Соломона, Этот кодер осуществляет копирование ш-разрядных символов (комбинаЩций), образующих поле Галуа СР (2 ),избыточным (и, Е)-кодом, где К -число информационных символов; и -общей число символов в кодовом блоке, Внутренний кодер осуществляегкодирование ш-разрядных символов(комбинаций) вторым избыточным кодом(ш ш), где й - общее число разря 3 1 2955дов второго кода, Таким образом, общая длина блока информации, закодированного каскадным кодером, равна пшВ данном устройстве внутренний кодиспользуется для обнаружения ошибокв символах и стирания их. В простейшем случае можно взять код с проверкой на четность, В этом случае второйгенератор 5 синдромов осуществляетпроверку на четность принимаемых, 10ш+1-разрядных комбинаций (один проверочный разряд), Если в комбинациинечетное число двоичных единиц, тона выходе генератора 5 появляетсясигнал стирания, адрес (локатор) которого в данный момент фиксируетсясчетчиком 6, Число стираний, котороеможет исправить код Рида-Соломона,сйС, При исправлении двухкратных. ошибок с ( Й. 20Закодированный избыточным (п, Е) -кодом блок информации списывается изблока 1 в буферный накопитель 2, атакже подается в генераторы 4 и 5синдромов, В первом генераторе 4 25синдромов определяются синдромы ЯофЯ Я,1, путем деления кодовогоблока на составные части образующегополинома Е(х)=(х+1)(х+Й)(х+сс )(х+сД 1, где с - примитивный элемент поля СР(8), При этом на генератор 5 синдромов подаются ш+1-разрядные комбинации, а на генератор 4 ибуферный накопитель 2 ш-разрядныекомбинации (без проверочных разрядов), Синдромы Я; записываются в накопитель 9, На выходах накопителя 9подключен дешифратор 11 ошибок, который представляет собой схему ИЛИ,Если при делении получаются остатки, 10т,е. если Я; Ф О, то они содержат хотя бы одну 1, Тогда на втором выходедешифратора 11 появляется сигнал=Я ==Я,1 , то на .первом выходепоявляется сигнал "Нет", обозначающий отсутствие ошибок и стираний,При появлении сигнала "Нет" информационная часть кодового блока выдается потребителю через блок 3,Во время переписи кодового блокав буферный накопитель 2 производитсятакже подсчет числа ш-разрядных комбинаций первым счетчиком 6 и определение синдромов ошибок в генераторе5, Сигнал ошибки на выходе генератора 5 разрешает запись состояния счетчика 6 в накопитель 10. Это состоя 31 4ние и является адресом (локатором)стирания в (и, 1 с)-кодовом блоке, Такадресуются и другие комбинации, вкоторых обнаруживаются ошибки генератором 5 синдромов,Число сигналов ошибок (стираний)подсчитывается счетчиком 8, и еслионо больше д, то сигналом "Стирание" с первого выхода стирается кодовый блок в буферном накопителе 2.В противном случае сигналом с второго выхода счетчика 8 разрешается расчет элементарных симметрических функций локаторов стираний в вычислителе 17 и подсчет операций расчетавторым счетчиком 7. После приема и-йкодовой комбинации кодового блокапоявляется сигнал на втором выходесчетчика 6, который обеспечивает совместно с сигналом с второго выходасчетчика 8 запуск второго счетчика 7.На каждую операцию при вычислениитратится один такт, На первом тактесостояние счетчика 7 выделяется дешифратором 12, сигнал с первого выхода которого попадает в вычислители15 и 17, В вычислитель 15 переписываются локаторы стираний, а вычислитель 17 начинает расчет 3, по формулам с, =х +х,+хх+х 1л=х. х, +хх+. +х 1 6х 1Фс4 Я ф ф ф д3-5 ф (1)При этом процесс расчета и преобразований принятых символов (кодовыхкомбинаций), каждый из которых содержит т бит в поле Галуа СР (2 ), осуществляется в нормальном базисе, Всесимволы поля СУ (2 ) можно представить в виде степени примитивного элемента Ы, Если примитивный элементМ, удовлетворяет дополнительному ус 4 8 Ю 1ловию - элементы с,с, М, М ссявляются линейно независимыми надСР (2), то они образуют нормальныйбазис, В таблицах неприводимых многочленов можно выбрать примитивный многочлен соответствующей степени, корни которого М , где 1.=0,1,2,ш,линейно независимы, Тогда произвольный элементЕ СР (2 ) может бытьпредставлен как некоторая степеньи в виде разложения по нормальномубазису ос-1(2)1=ОПредставление элементав видеразложения по нормальному базисуудобно при возведении в степень ви. (3)а 1 в тэк какЖ =Ы. Таким образом, возведение в квадрат означает циклический сдвиг элемента на один разрядвправо. Это упрощает устройство возведения в квадрат и увели)ивает егобыстродействие.,С выходов вычислителя 17 полученные значения о; подаются в вычиспитель 16 для определения модифицированных синдромов Я, Я Я 1 г )Б) ь, В этом блоке вычисление модиФицировДиных синдромов производитсяпо следующим Формулам:/Я,1 =БД ьЯ,1, (, +, ,+Я ,1Б,- +Яд-а . +ф е+аа-р) (Я-г Ъ-а +Бд-э+ф ф ф+Б) "с 3-з )ЯД- ЯД Яг д )По модифицированным синдромам Б 1 ввычислителе 14 .производится расчетсимметрических Функций С, Са отлокаторов оиибок х х, н локаторов стирании х ) х ))хДСимметрические Функции С, и С получают в вычислителе 14 по уравнениям1ЯДБ- +Б 2.-Яд(6)гБ Б +(Б, )Следовательно, для нахождения недостающих локаторов ошибок х, и хг нужно решить квадратное уравнениех +С,х+С =О. (7)Указанное уравнение заменой х=ЕС,приводится к вйду Е +Е + =О,(8)где 1 Сг(С, ) )Е =(О+2) е) )+ г+ ++ш,)е (1 О) Вычисление локаторов х) хг ошибок производится в вычислителе 15 по выражениям (7) - (10),На этом заканчивается определение локаторов ошибок х, и хг. Локаторы 5531 6стираний х ) х 4) , ) хопределеныраньше. Теперь остаетСя Определитьзначения локаторов у, ошибочных истертых символов, Их определяют с.помощью следующего выражения:;У Се х10 3=огде 1 " 1 й й.+ С,оВычисление С осуществляется по рекуррентной Формуле 15С = С; -хС (.) ) (12)где С - элементарные симметрические Функции от локаторовошибок и стираний.Значения у; определяются также в 20вычислителе 15 но Формулам (11) и(12).Локаторы х; ошибочных и стертыхсимволов являются адресами искаженных символов кодового блока. Путемподачи этих адресов на буферный на-,копитель 2 производится считыванииз него искаженных символов х; ) которые подаются на блок 3 сумматоров ЗОНа вторые входы блока 3 из вычислителя 15 подаются значения у; определенных локаторов. Сложение значений искаженных символов х; с соответствующими вычисленными значениямиу. локаторов в блоке 3 обеспечивает 35 их исправление, Исправленные символыснова записываются в буферный накопитель 2 по соответствующим адресам,После этого исправленный кодовый блоксписывается через блок 3 сумматоровна выходе 18 потребитеЛю информации.На этом заканчивается процесс исправления ошибочных и стертых символов,Рассмотрни работу блоков устройст ва для исправления по Функциональнымсхемам (Фиг. 2 - 5) при исправлениидвух ошибочных и трех стертых символов.При трех стертых символах формулы 5 О (1) принимают вид Рассмотрим работу вычислителя 17 при трех стертых символах (далее стираний и ошибок), При этом одновремен 12955но происходит запись локаторов стираний х, х и х . в вычислитель 15,На первом такте после приема кодового блока расстояние счетчика 7 выделяется дешифратором 2, сигнал с первого выхода которого попадает в вь 1 числители 15 и 17, В вычислителе 17 сигнал попадает на С-входтриггера 78, на Р-вход которого подан ранее сигнал со счетчика 8, Триггер О 78 устанавливается в "1" и открывает элемент И 79, через который начинают поступать тактовые импульсы, Аналогично в вычислителе 15 сигналом с дешифратора 12 устанавливается в 5 1" триггер 33, ,сигнал с выхода которого разрешает прохождение тактовых импульсов через элемент И 34В результате начинают работать счетчики 80 (фиг. 5) и 36 (фиг, 3), После довательные состояния счетчика 80 являются адресами для формирователей 8 и 82 и блока 90 памяти, Аналогично последовательнье состояния счетчика 36 являются адресами для формирователя 37, по которым в них занесеныадреса элементов поля Галуа СР (2 ),записываемых вблоки 42 и 43.На первом такте на выходы блока90 в накопитель 10 выдается сигнал .30считывания и адрес локатора стираний х , формирователь 82 подключаетна первые входы перемножителя 86 через коммутатор 84 выход элементаНЕ 83, а через коммутатор 85 на вторые входы перемножителя 86 сигнал свыходов накопителя 10. В вычислителе 15 аналогично формирователь 39подключает выход элемента НЕ 51 черезкоммутатор 44 на первые входы перемножителя 48, а выходы накопителя 10через коммутатор 45 - на вторые входы перемножителя 48,Таким образом, на входы обоих перемножителей подключаются оь =1 и х . 45ОзФПроизведение М х =хэ записывается натриггеры группы 87 и группы 49 и вблок 88. На втором такте локатор .стираний хо переписывается с группы 49триггеров в блоки 42 и 43. 50На третьем такте аналогично изнакопителя 10 выбирается хо и умножается на ь, . Результат, т,е, х 4,записывается в блок 88, складываетсяс содержанием (х) группы 87 триггеров и записывается на триггеры груп-пы 49, На четвертом такте переписывается локатор стираний х в блоки42 и 43,3 8Таким же образом, ца пятом такте осушествляется выборка х. и умножение ь. . Резульгат, т.е, х , складывается с х+х 4 на триггерах группы 87 и записывается на группу 49триг геров.На шестом такте величина с, стриггеров группы 87 записывается вблок 89, а локатор х переписываетсяс группы 49 в блоки 42 и 43, На этомзакан пгвается запись локаторов стираний в вычислитель 15,С седьмого такта начинается вычисление , При этом формирователь82 подключает через коммутатор 84на первые входы перемножителя 86 выходы блока 88, Выходы накопителя 10остаются подключенными на вторые входы перемножителя 86. Из накопителя10 выбирается величина х., а из блока 88 - локатор стираний х,1, Произведение х х записывается на триггеры группы 87. На восьмом такте хзхзаписывается блок 89, На девятомтакте х из накопителя 1 д и х, изблока 88 перемножаются на перемножителе 86 и произведение х х складывается с х х 1 на триггерах группы 87.Произведение хх получают на десятомтакте и складывают на тех же триггерах с ххо ьх,х,1Полученная величина о записывается на одиннадцатом такте в блок 8".Для расчета гз используют произведение х х, записанное в блоке 89, выходы которого подключены на вторые входы перемнолжтеля 86, На первые входы перемножителя 86 из блока 88 подается локатор х, На двенадцатом такте величина ь =х х х записывается на триггеры группы 87, с которых на 13-м такте переписывается вблок 89.Для дальнешпих расчетов неЬбходи,омо записать ь .=1 в блок 89. Это производится на 14-м такте путем подключения через коммутаторы 84 и 85 навходы перемножителя 86 выхода элемента НЕ 83. Таким образом, в перемножителе 86 производится перемножениео о,оЫ. М =ж и результат вначале записывается на триггеры группы 87, а на15-м такте - в блок 89,На 16-м такте появляется сигнална третьем выходе дешифратора 12,который подается в вычислитель 16 свхода 74 на С-вход триггера 64(фиг. 4). До этого с дешифратора 11с входа 75 на Р-вход триггера 64подан сигнал "Ошибка", поэтому тригсс ссгер 6 4 устанавливается в " 1 и р азрешается работа вычислителя 1 6 , Приэтом через элемент И 65 н а счетчик66 начинают поступать тактовые импульсы с , Состояния счетчика 6 6 свыходов 7 7 попадают н а адресные входы коммутатора 1 3, Число цепей А ; ввыходах 7 7 определяется количествомвычисляемых синдромов Б;, Вычислениеосуществляется по формулам (4), которые при исправлении двух ошибок итрех стираний принимают вид:БГ84 с 7 Бзс 38:Б .+8 г +Бо, +8 тсс. з8 Бр , +Б,Бс) эНа 16-м такте счетчик 66 переходит в первое состояние. В данномслучае в вычислении участвуют семьсиндромов, поэтому на адресные входыкоммутатора 13 со счетчика 66 подхо-.дят три цепи, которые обеспечиваютполучение восьми адресов. сВ первомсостоянии счетчика 66 коммутатор 13подключает синдром Б, который попадает через открытый сигналом "Ошиб"ка" блок элементов И коммутатора 13на вторые входы 73 перемножителя 68,В это время на первые входы 72 перемножителя 68 из блока 89 списываетНа выходах перемножителя 68 поолучают произведением. Б =Б , которое записывается на триггеры группы69. Аналогично получают произведение80, которое складывается с Б натриггерах группы 69. ПроизведенияБ , Б оз также складываются на4 2 ) Этесх жефтриггерах. Полученная сумма8 на 20-м такте переписывается аБраллельно в блоки 70 и 71,Аналогично получают в соответствии с формулами (12) и записываютв блоки 70 и 71 модифицированныессиндромы 85 ) 84Бэ) на что тратится 15 тактов, Таким образом, работа вычислителя 16 заканчиваетсяна 35-м такте.Расчет симметрических Функций С,и С от локаторов ошибок и стира2.ний производят в вычислителе 14,Вычисление производят по выражениям(5) и 6), которые при исправлениидвух ошибок и трех стираний прини.,мают вид: Вычисление начинается с 36-готакта, на котором формирователь 22 10 адреса открывает коммутаторы 23 и24 по их первым входам, Поэтому напервые и вторые входы перемножителя25 подключаются соответственно выходы блоков 70 и 71. Величины Б и Б 15 подаются на входы перемножителя 25сПроизведение ББ записывается втриггеры группы 26, Аналогично на37 такте получают произведение Б Бкоторое складывается с ЯЯнатрнг герах группы 26, Результат сложениязаписывается в блок 20 на 38-м такте.Аналогично на 39-м такте вычисляют знаменатель выражения (15), т,е,88+(Я )=а, который на 41-м такте 25 записывается в блок 21. На 42-м такте числитель выражения (15) умножа-ют на величину 1 1Г;а Б Б +(Б)Величину 1/а получают в преобразователе 27, в котором по адресуББ+(Я )записана величина 1 а. Таким образом, здесь операция деления 35 заменяется операцией умножения, Дляумножения выход блока 30 подключается через коммутатор 23 на первыевходы перемножителя 25, а выходы преобразователя 27 - на его вторые вхо ды, Полученная величина С, записывается в триггеры группы 26, а на 43-итакте сигналом 3(" Запись 2") свыхода 31 переписывается в вычислитель 15 на блок 40 фиг, 3).45 Аналогично вычисляют С по формуле (16) на 44 - 48-м тактах. Поскольку знаменатели в формулах (15)и (16) одинаковы, вторично знаменатель не вычисляют, а используют его 50 значение, записанное в блоке 21, На49-м такте величина С с помощьюсигнала 3, (" Запись" ) с выхода 32переписывается на блок 41,Недостающие локаторы ошибок х, и 55 х, определяются по формулам (7)(10) в вычислителе 15, где также вычисляются значения ошибок и стиранийпо формулам (11) и (12), Работу вычислителя 15 рассмотоим при двух11 12ошибках и трех стираниях, В этом случае на 50-м такте на втором выходедешифратора 2 появляется сигнал, который проходит через элемент ИЛИ 35вычислителя 15 (фиг, 3) и устанавливает в "1" триггер 33, который открывает элемент И 34, На счетчик 36начинают поступать тактовые импульсыс входа 96,Счетчик 36 уже работал при записилокаторов стираний х , хд и х вблоки 42 и 43 и остался в шестом состоянии, т.е, в состоянии, при котором осуществляется запись локатора хв блоки 42 и 43. Поэтому счетчик 36при вторичном переходе триггера 33 в"1" и поступлении тактовых импульсов сначала переходит в седьмое состояние, для дальнейших вычисленийнужно переписать в блок 43, Поэтомув седьмом состоянии счетчика 36 формирователь 39 сигналом с первых выходов через коммутатор 44 подключает на входы перемножителя 48 значеоние сС , а сигналом со вторых выходов через коммутатор 45 соединяетвыходы блока 40 на вторые входы перемножителя 48. Таким образом, на 50-мтакте на выходах перемножителя 48ополучают величину С,= С которая .записывается в триггеры группы 49,На 51 такте С, сигналом с формирователя 37 переписывается в блок 43. На 52-м такте на первом выходе формирователя 38 появляется сигнал, который сдвигает на один разряд вправо содержимое блока 40, в качестве которого при а=8 может быть применен универсальный регистр, в котором предусмотрено считывание и запись информации в параллельном и последовательных кодах, а также циклический сдвиг данных влево и вправо, т,е,. в направлении первого или восьмого разрядов, Для сдвига ш-й (последний) разряд регистра соединяется с входом первого разряда. При сдвиге вправо величина С, записанная в блоке 40, возводится в квадратг(С,), На 53-м такте формирователь 39 подключает через коммутатор 44 на первые входы перемножителя 48 выходы блока 41, а выходы блока 40 через коммутатор 46 и преобразователь 47 - на вторые входы перемножителя 48. Значение (С, ), записанное в блокег40, является адресом для ПЗУ преобразователя 47, в результате пода 9553112чи которого на выходах последнегопоявляется записанная в нем по этомуадресу величина 1/(С, ) . Следовательно, на первых входах неремножителя 48появляется величина С, а на вторых -1/(С, ), На этом же такте происходитгперемножение Сг на 1/(С,) и навыходах перемнажителя 48 получают величину, которая записывается в Ю триггеры группы 49. На 54-м такте наблок 42 подается сигнал записи и выдается адрес, по которому величиназаписывается в блок 42.На 55-м такте формирователь 37 вы бирает из блока 42 величину, врезультате преобразования которой на.входах элементов НЕ 52 и 53 и прямыхвыходах сумматоров группы 50 получается величина Е которая подключа ется с помощью Формирователя 39 черезкоммутатор 44 на первые входы перемножителя 48. Одновременно формирователь 39 через коммутатор 45 подключает выходы блока 43 на вторые входыперемножителя 48, Из блока 43. сигналом с Формирователя 37 выбирается ве 1личина С, . Следовательно, на выходахпер емножителя 48 получен локатор оши 1бок х, =Е, С, который записывается натриггеры группы 49, На 56 такте локатор х, с помощью Формирователя 37переписывается в блоки 42 и 43.На 57-м такте формирователь 37снова выбирает иэ блока 42 величину 35 , в результате преобразования ко.торой в соответствии с формулой (10)на выходах элементов НЕ 52 и 53 исумматоров группы 50 получается величина Е , которая подключается фор" мирователем 39 через коммутатор 44на первые входы перемножителя 48,Одновременно формирователь 39 черезкоммутатор 45 подключает выходы блока 43 на вторые входы перемножителя 45 48. Таким образом, на выходах перемножителя 48 получен локатор ошибокх =ЕС который записывается нагруппу 49 три г гер о в, На 58-м тактевеличина хг с помощью формирователя.3 переписывается в блоки 42 и 43.На этом заканчивается определение локаторов ошибокСледовательно, в блоках 42 и 43 записаны локаторы ошибокх и хг и локаторы стираний хэ, х 55 и хПо локаторам х, и синдромам Яиспользуя Формулы (11) и (12), можнонайти значения ошибок и стираний у; .13 1295531 14 Процедуру нахождения значений у; опишем при возникновении двух ошибок итрех стираний. В этом случае выражения (11) и (12) лри вычислении принимают вид: С 84 +С 18 + С 282 +С 1 Я 1 +С 48 О а э С х +С х +С х +С х 1+С 14 х(19)Вначале определяют С С, Сз, С 4 по формулам (19). При этом локаторы х, - х записаны в блоках 42 и 43. Вычисление С происходит с 59-го такта так: формирователь 39 подключает с помощью коммутатора 44 выходы блока 42 на первые входы пере- множителя 48. Формирователь 37 задает адрес, по которому в блок 42 записан локатор ошибок х, в результате с выхода блока 42 величина х, подается на первые входы перемножителя 48, Формирователь 39 подключает выход элемента НЕ 51 через коммутатор 45 на вторые входы перемножителя 48, в результате на него подается с = 1. Результат умножения х х 4озаписывается в триггеры группы 49. Аналогично происходит выбор из блока 42 и умножение на К локатора х 4, Результат складывается по модулю два с х на триггерах группы 49. На следующем, 61-м такте необходимо выбрать из блока 42 локатор стираний хэ и сложить его с х, +х . Адрес для выбора хз из блока 42 задает формирователь 37. При этом выходы блока 42 через коммутатор 44 подключаются на первые входы перемножителя 48, на вторые входы снова подключается М. , Таким образом, происходит умножение х 2 наЫ и сложение результата с х+х на триггерах группы 49. Аналогично производится сложение Х 4 и х. Результат сложения, т.е. С записывается в блок 42 на 64-м такте.1 Также производится вычисление СС 4 и С 4, которые записываются вблок 42. 5 1 О 15 20 25 30 35 40 45 50 55 Расчет С 1 С, С и С 4 производится по формулам (18) с лоомощью формирователей 37 и 39, а также коммутаторов 44 и 45, Результаты расчетовзаписываются с триггеров группы 49в блок 42.После этого приступают к определению у при этом вначале определяют числитель, а затем знаменательвыражения (17). Для нахождения чисснндромы 8 1 88- через коммутатор 13 считываются сигналами со счетчика 66 вычислителя 16,которые задают адреса для мультиплексора в коммутаторе 13, подключающего Б, Я 8,1на входы перемножителя 68 по сигналу с выходатриггера 33 (выход 63), Значение числителя записывается в блок 42, азначение знаменателя остается натриггерах группы 49. Теперь числитель необходимо разделить на знаменатель. Значение числителя из блока32 через коммутатор 44 подается напервые входы перемножителя 48, азначение знаменателя через коммута-тор 46, преобразователь 47 и коммутатор 45 - на вторые входы перемножителя 48, Если значение знаменателя обозначить через а , то на выходепреобразователя 47 получают величину 1/д, которая и умножается на числитель. В результате на выходах перемножителя 48 получают значение у,Величина у записывается в триггерыгруппы 49, а затем в блок 43,Остальные значения у; получают изаписывают в блок 42 аналогично,Таким образом, локаторы х; записаны в блоке 42, а значения ошибоки стираний у, записаны в блоке 43.Далее величина х, являющаяся ад"ресом искаженного элемента, с помощью формирователя 37 списывается сблока 42 и подается на буферный накопитель 2, В результате разряды искаженного элемента с адресом х, подаются на блок 3 сумматоров, на вторс.е входы которых формирователь 37списывает из блока 43 у, при сложении разрядов искаженного элемента су, происходит исправление и исправленный элемент записывается в буферный накопитель 2 по тому же адресу.Аналогично происходит исправлениеостальных искаженных элементов кодово го блока.Таким образом, предлагаемое устройство позволяет исправлять до двухДекодирующее устройство для исправления ошибок, содержащее запоминающий блок, первые выходы которого подключены к соответствующим входам 10 первого генератора синдромов и первым информационным. входам буферного накопителя, выходы которого соединены с соответствующими первыми входами блока сумматоров, выходы которого 15 подключены к соответствующим вторым информационным входам буферного накопителя и являются первыми выходами устройства, выходы первого генератора синдромов соединены с соответст вующими входами первого накопителя, выходы которого подключены к соответствуювдм входам дешифратора ошибки, первый выход которого соединен с первым управляющим входом буферного накопителя и является вторым выходом устройства, первый вычислитель, первые, второй и третий выходы которого подключены соответственно к первым информационным, первому и второму управляюшкм входам второго вычислителя, первые и вторые выходы которого соединены соответственно с третьими информационными входами буферного накопителя и вторыми 35 входами блока сумматоров, о т л и - ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости устройства за счет исправления стертых символов, в устройство введены первый, 4 второй и третий счетчики, второй генератор синдрома, второй накопитель, третий и четвертый вычислители, дешифратор состояний и коммутатор, первые и вторые выходы запоминающегоблока подключены к входам соответственно первого счетчика и второгогенератора синдромов, выход которо" 1 15 12955 ошибок и до Йстираний, т,е, обеспечивает существенное повышение достоверности исправленной информации Формула изобретения 31 16го соединен с первым управляющимвходом второго накопителя и входомтретьего счетчика, первый и второйвыходы которого подключены соответственно к второму управляющему входубуферного накопителя и первому управляющему входу четвертого вычислителяи управляющему входу второго счетчика, первый и второй выходы первогосчетчика соединены с информационными входами соответственно второго накопителя и второго счетчика, выходыкоторых подключены к входам дешифратора состояний, первый выход которого соединен с вторым управляющимвходом четвертого вычислителя итретьим управляющим входом второговычислителя, второй и третий выходыдешифратора состояний соединены соответственно с четвертым управляющимвходом второго вычислителя и первымуправляющим входом третьего вычислителя, первые выходы которого подклю-,чены к информационным входам первоговычислителя, выходы первого накопителя подключены к соответствующиминформационным входам коммутатора,первые и вторые выходы которого соединены соответственно с первыми инФормационными входаьы третьего вычислителя и вторьми информационнымивходами второго вычислителя, третийвыход которого соединен с первым управляющим входом коммутатора, второйвыход дешифратора ошибок соединен суправляющими входами коммутатора итретьего вычислителя, вторые выходыкоторого подключены к адресным входам коммутатора и первого вычислитея, первые и вторые выходы четвертого вычислителя подключены соответственно к вторым информационным входам третьего вычислителя и адреснымвходам второго накопителя, выходыкоторого подключены к информационнымвходам четвертого и третьим информационным входам второго вычислителей,

СмотретьЗаявка

3837857, 04.01.1985

ПРЕДПРИЯТИЕ ПЯ В-2867, ИНСТИТУТ ПРОБЛЕМ ПЕРЕДАЧИ ИНФОРМАЦИИ АН СССР, ПЕНЗЕНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ЗИНОВЬЕВ ВИКТОР АЛЕКСАНДРОВИЧ, ЗЯБЛОВ ВИКТОР ВАСИЛЬЕВИЧ, САВЕЛЬЕВ БОРИС АЛЕКСАНДРОВИЧ, ДОДУНЕКОВ СТЕФАН МАНЕВ, ГЕОРГИЕВА ВАЛЕНТИНА МАРКОВА, ЖИТКОВ ГЕННАДИЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 13/05

Метки: декодирующее, исправления, ошибок

Опубликовано: 07.03.1987

Код ссылки

<a href="https://patents.su/11-1295531-dekodiruyushhee-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Декодирующее устройство для исправления ошибок</a>

Предыдущий патент: Двунаправленный преобразователь кодов

Следующий патент: Вычислитель ошибок помехоустойчивого декодера

Случайный патент: Среда для изготовления постоянных микропрепаратов из биологических объектов