Адаптивное микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

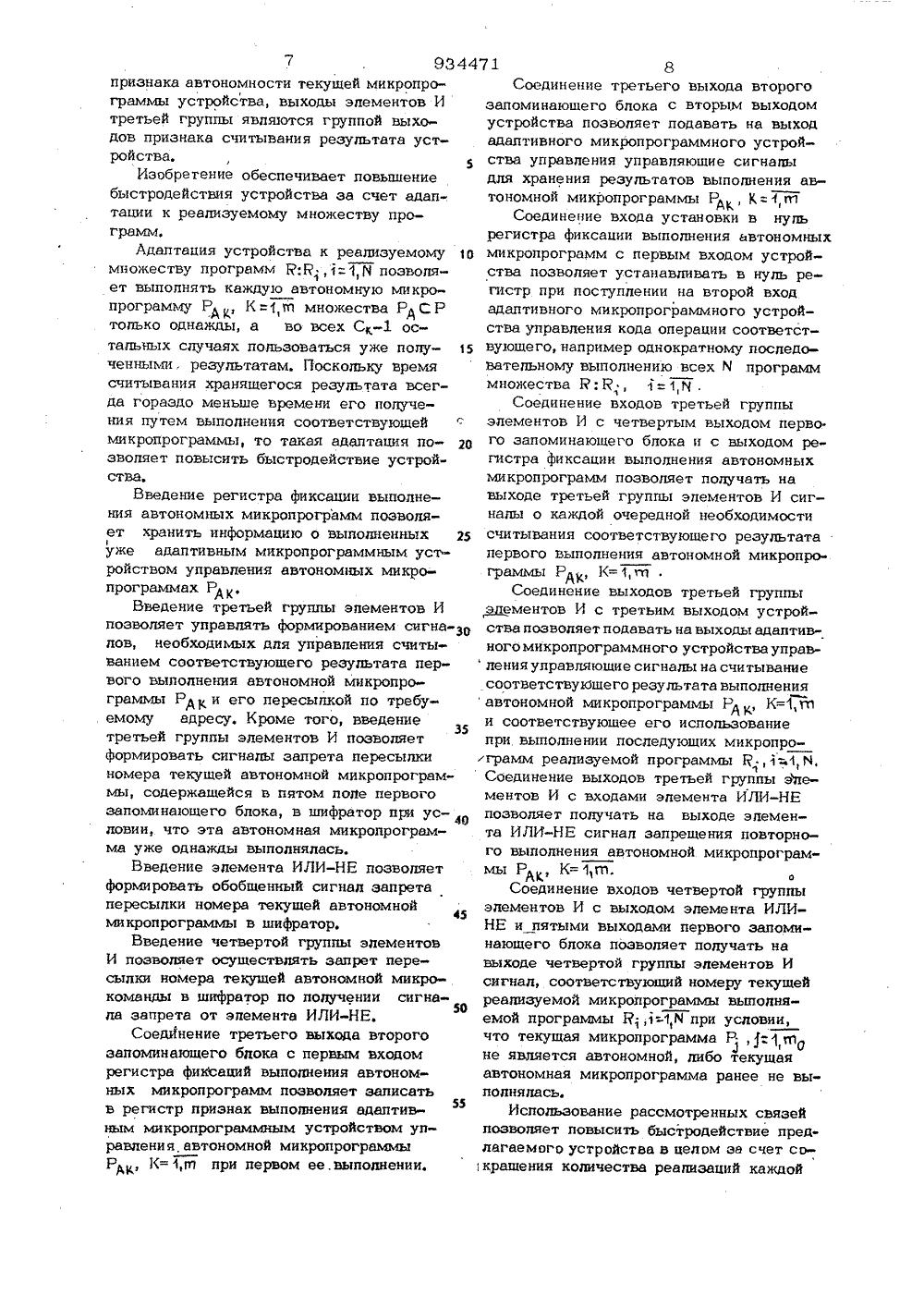

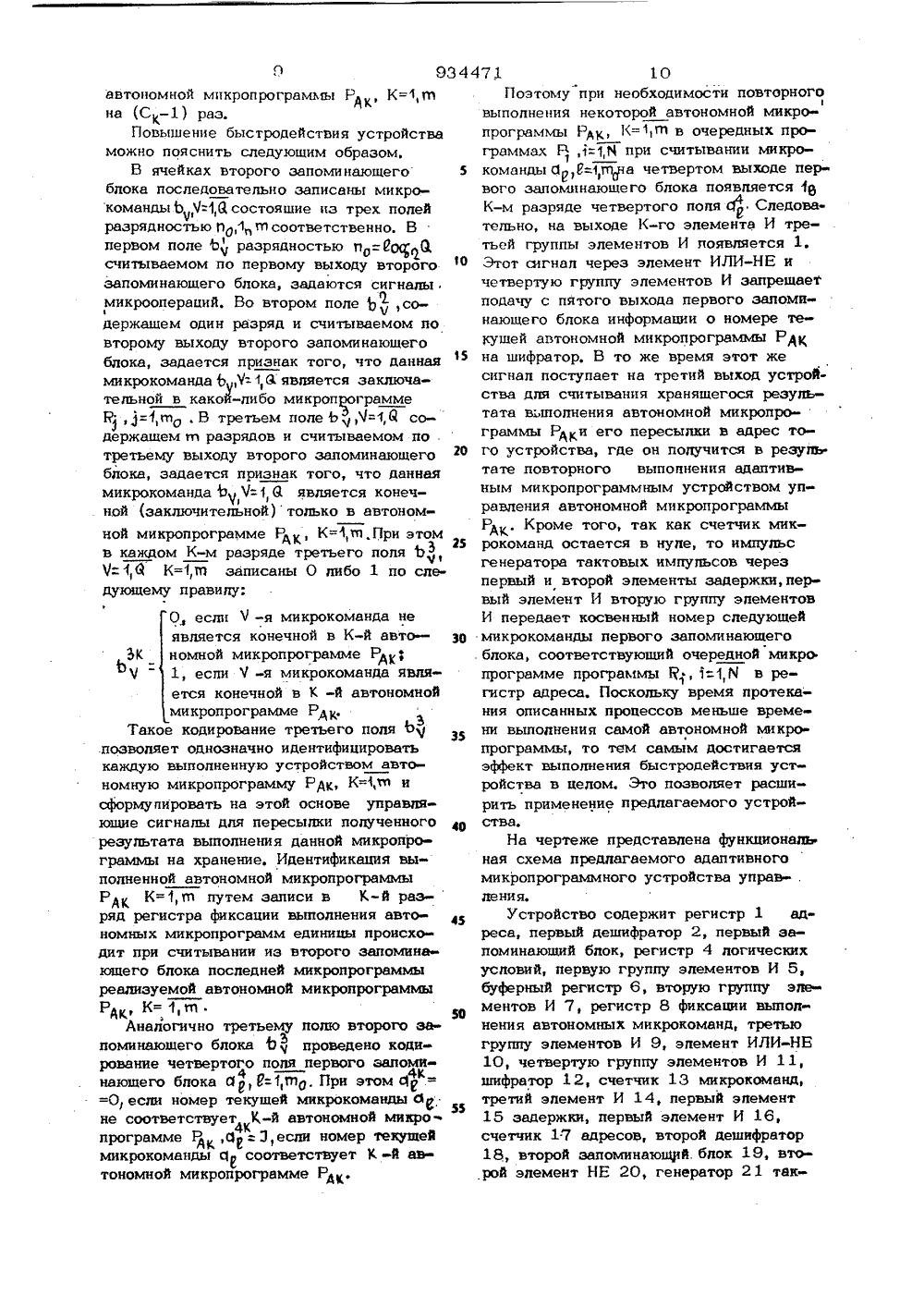

Союз СоветскинСоциапистическикРеспублик ОП ИСАЙ ИЕИЗОБРЕТЕНИЯк двтовскомю свидитюльствю п 934471( 06 Р 9/22 с присоединением заявки йЪ Госурэрстеацвй комитет СССР(23) Приоритет но делам нзебретеннй н открытей(54) АВАПТИВНОЕ МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ Изобретение относится к автоматикеи вычислительной технике и может бытьиспользовано в качестве управляющегоустройства ЭВМ, применяемых дпя управления сложными системами,Известно микропрограммное устройство управления, содержащее два запоминающих блока, регистры, логические элементы И и НЕ, элементы задержки, счетчики, дешифраторы и генератор тактовыхимпульсов 1,Недостатком этого устройства является низкое быстродействие,Наиболее близким к предлагаемомуявляется микропрограммное устройствоуправления, Это устройство содержит ре 15гистр адреса, первый и второй дешифраторы, первый и второй запоминающие бло.ки, регистр логических условий, первую.и вторую группы элементов И, буферный26регистр, шифратор, счетчик микрокоманд,первый, второй, третий и четвертый элементы И, первый и второй элементы задержки, счетчик адресов, первый и второй элементы НЕ и генератор тактовыхимпульсов, причем адресный вход регистра адреса является первым входомустройства, выход регистра адреса соединен с первым входом первого дешифратора, а выход - с входом первого запоминаюшего блока, первый, второй и третий выходы которого соединены соответственно с входом адреса буферного регистра, входом установки в нуль регистра. адреса и информационным входом регистра логических условий, выходы которого соединены с первыми входами элементов И первой группы, вторые входыкоторых подключены к второй группе входов устройства, а выходы соединены сгруппой входов логических условий буферного регистра, выходы которого соедииены с,первыми входами элементов Ивторой группы, вторые входы и выходыкоторых соединены соответственно с выходом первого элемента И и группойвходов косвенного адреса регистра адреса, первый выход шифратора соединен с37/45 Тир ВНИИПИ Госу по делам 113035, Мосаж 732 Подписноедарственного комитета СССРизобретений и открытийква, Ж, Раушская набд. 4/ филиал ППП "Патент", г; Ужгород,.ул, Проектная,Составитель В, Латышев Редактор Н. Ковалева Техреа И.Гайду Корректор Ю. Макаренко5 9344В связи с этим при последовательномвыпопнении М программ множества Ксодержащих автономные микропрограммыподмножества Г , каждая автономная микропрограмма РдК, К=1, 1 выполняетсяМК . Краз. В то же время результа 1=1сты выполнения микропрограммы РАК вовсех Ск ее реализациях одни и те же.Таким образом, микропрограммное уст0ройство управления для получения результата выполнения каждой автономной микропрограммы РК= 1,в затрачивает вревремя в СК раз больше, чем требуетсядпя ее однократной реализации. Это при 15водит к дополнительным временным затратам на последовательную реализациюмножества К, а следоватепьно, к снижению быстродействия устройства управления в целом, что сужает применение предпагаемого устройства,Цель изобретения - повышение быстродействия устройства.Поставленная цепь достигается тем,что в адаптивное микропрограммное устройство управления, содержащее регистрадреса, первый и второй дешифраторы,первый.и второй запоминающие блоки, ре-гистр логических условий, первую и вторую группы элементов И, буферный ре- З 0гистр, шифратор, счетчик микрокоманд,первый, второй, третий и четвертый элементы И первый и второй элементы задержки, счетчик адресов, первый и второй элементы НЕ и генератор тактовых з 5импульсов, причем адресный вход регистра адреса подкшочен к первому входуустройства, выход регистра адреса соединен с первым входом первого дешифратора, а выход - с входом первого задоминаюшего блока, первый, второй и третий выходы которого соединены соответственно с входом адреса буферного регистра, входом установки в нуль регистра адреса и информационным входом регистра когических условий, выходы которого соединены с первыми входами элементов И первой группы эпементов И,вторые входы которых подкпючены к второй группе входов устройства, а выходысоединены с группой входов погическихусловий буферного регистра, выходы которого соединены с первыми входами элементов И второй группы. вторые входы ивыходы которых соединены соответственно с выходом первого элемента И и группой входов косвенного адреса регистраадреса, первый выход шифратора соединенс первым входом счетчика микрокоманд, . 71 6первый и второй входы второго элементаИ соединены соответственно с выходомгенератора тактовых импульсов и выходомпервого элемента НЕ вход которого соединен с выходом третьего элемента И ипервым входом четвертого элемента И,второй вход которого соединен с входомпервого и выходом второго элементов задержки, первый и второй входы первогоэлемента задержки соединены соответственно с выходами первого элемента эадер.жки и третьего элемента И, вход второгоэлемента задержки соединен с выходомгенератора тактовых импульсов, выходчетвертого элемента И соединен с вторымвходом первого дешифратора, входами установки в нуль регистра логических усповий и буферного регистра и первым вхо-.дом счетчика адресов, второй и третийвходы и выход которого соединены соответственно с входом второго элементаНЕ, вторым выходом шифратора и первымвходом второго дешифратора, второй входи выход которого соединены соответственно с выходом второго элемента И и входом второго запоминающего блока, группа выходов кода микрооперации которогоявляется групповым выходом кода микрооперации устройства, а выход адресногопризнака соединен с входом второго эпемента НЕ, выход которого соединен свторым входом счетчика микрокоманд,выходы которого соединены со входами,третьего эпемента И введены регистрфиксации выполнения автономных микропрограмм, третья и четвертая группыэлементов И и элемент ИЛИ-НЕ, причемгруппа информационных входов, вход установки в нуль и выходы регистра фик-.сации выполнения автономных микропрограмм соединены соответственно с группой выходов признака автономности микропрограммй второго запоминающего блока, первым входом регистра адреса ипервыми входами элементов И третьей .группы, вторые входы и выходы которыхсоединены соответственно с группой выходов признака автономности текущеймикропрограммы первого запоминающегобпока и входами элементов ИЛИ-НЕ, выход которого соединен с первыми входами элементов И четвертой группы, вторыевходы и выходы которых соединены соответственно с группой выходов номера текущей микропрограммы первого эапоминаншего блока и входами шифратора группа выходов признака автономности текущей микропрограммы второго запоминающего бпока является групповым выходом7 9344признака автономности текущей микропрограммы устройства, выходы элементов Итретьей группы являются группой выходов признака считывания результата устройства.5Изобретение обеспечивает повьпцениебыстродействия устройства за счет адаптации к реализуемому множеству программ,Адаптация устройства к реализуемому 1 Омножеству программ Б,Б, :1,8 позволяет выполнять каждую автономную микропрограмму РА , К =1, ю множества РА С Ртолько однажды, а во всех Ск. остальных случаях пользоваться уже попученными, результатам, Поскольку времясчитывания хранящегося результата всегда гораздо меньше времени его получения путем выполнения соответствующеймикропрограммы, то такая адаптация позволяет повысить быстродействие устройства,Введение регистра фиксации выполнения автономных микропрограмм позволяет хранить информацию о выполненных 25уже адаптивным микропрограммным устройством управления автономных микропрограммах РАВведение третьей группы элементов Ипозволяет управлять формированием сигна-Золов, необходимых дпя управления считыванием соответствующего результата первого выполнения автономной микропрограммы Рд 1 и его пересылкой по требуемому адресу. Кроме того, введениетретьей группы элементов И позволяетформировать сигналы запрета пересылкиномера текущей автономной микропрограммы, содержащейся в пятом попе первогозапоминающего блока, в шифратор при усОповии, что эта автономная микропрограмма уже однажды выполнялась.Введение элемента ИЛИ-НЕ позволяетформировать обобщенный сигнал запретапересылки номера текущей автономноймикропрограммы в шифратор.Введение четвертой группы элементовИ позволяет осуществлять запрет пересылки номера текущей автономной микрокоманды в шифратор по получении сигна 50ла запрета от элемента ИЛИ-НЕ,Соединение третьего выхода второгозапоминаюшего блока с первым входомрегистра фиксаций выполнения автономных микропрограмм позволяет записатьв регистр признак выполнения адаптив 55ным микропрограммным устройством управления автономной микропрограммыРАк, К=1,п при первом ее.выполнении,Соединение третьего выхода второго запоминаюшего блока с вторым выходом устройства позволяет подавать на выход адаптивного микропрограммного устройства управления управляющие сигналы дпя хранения результатов выполнения автономной микропрограммы РА, К:1,пСоединение входа установки в нуль регистра фиксации выполнения автономных микропрограмм с первым входом устройства позволяет устанавливать в нуль регистр при поступлении на второй вход адаптивного микропрограммного устройства управления кода операции соответствующего, например однократному носледовательному выполнению всех М программ множества Р: К;, 1" 1, ИСоединение входов третьей группы элементов И с четвертым выходом перво. го эапоминаюшего блока и с выходом регистра фиксации выполнения автономных микропрограмм позволяет получать на выходе третьей группы элементов И сигналы о каждой очередной необходимости считывания соответствующего результата первого выполнения автономной микропрогРаммы РдК, К= 1, 1Соединение выходов третьей группы ,.-цементов И с третьим выходом устройства позволяет подавать на выходы адаптивного микропрограммного устройства управ ления управляюшие сигналы на считывание соответствующего результата выполненияавтономной микропрограммы РА К=1,тй и соответствующее его использование при. выполнении последующих микропро"грамм реализуемой программы К., =1, М, Соединение выходов третьей группы элементов И с входами элемента ИЛИ-НЕ позволяет получать на выходе элемента ИЛИ-НЕ сигнал запрешения повторного выполнения автономной микропрограмЬКСоединение входов четвертой группы элементов И с выходом элемента ИЛИНЕ и пятыми выходами первого заломинаюшего блока позволяет получать на выходе четвертой группы элементов И сигнал, соответствукший номеру текущей реализуемой микропрограммы выполняемой программы й;=1,И при условии, что текущая микропрограмма Р,:1,л 1 не является автономной, либо текушая автономная микропрограмма ранее не выполнялась.Использование рассмотренных связей позволяет повысить быстродействие предлагаемого устройства в целом зе счет со-крашения количества реализаций каждой11 9344товых импульсов, второй элемент 22 задержки, четвертый элемент И 23, первыйэлемент НЕ 24, второй элемент И 25.Символом 26 обозначен первый входустройства 27-31 - первый, второй, третий, четвертый и пятый выходы первогозапоминающего блока соответственно,32 - второй вход устройства, ЗЗ - третий выход устройства, 34 - первый выход второго запоминающего блока, являюшийся одновременно первым выходомустройства, 35 - второй вход второгозапоминающего блока, 36 - третий выход второго запоминающего блока, являющийся одновременно вторым выходом 15устройства.В первом запоминающем блоке 3 хранятся микрокоманды 4 0=1,п 1 осостоящиеиэ пяти полей, каждая иэ которых соответствует микропрограмме Р,р 1 П 10,. В 20первом поле Ор 0 с 1,ЮОразрядаостью с 1 Г == 001 п 1 считываемом по первому выходу 27, содержится косвенный адрес номера следующей микропрограммы. Вовтором попе б 0=1,Ф 0 состоящем из одного разряда й считываемом по второмувыходу 28, задается сигнап сброса регистра 1 адреса. В третьем попе 4 8:1,т 0,3содержащем д, разрядов и считываемомпо третьему выходу 29, хранится код, З 0проверяемых логических условий.В четвертом поле с 1 Е,6=1,п 10 разряд 4.ностью т считываемом по четвертомувыходу 30, задается признак (идентификатор) автономности текщей микропрограммы. В пятом попе 6, 0=1110 содержащем д разрядов и считываемом попятому выходу 31 хранится номер текущей микропрограммы.Регистр фиксации выполнения автономных микропрограмм 8 предназначен даяхранения информации о выполненных ужеадаптивным микропрограммным устройством управления автономных микропрограмЯК 45Третья группа элементов И 9 управляет формированием сигналов, необходимыхдля управления считыванием соответствующего результата первого выполненияавтономной микропрограммы Р 1, К=1 Ри его пересылкой по требуемому адресу,Элемент ИЛИ-НЕ обеспечивает выдачу на четвертую группу элементов И 11сигнала запрещающего пересылку номератекущей автономной микропрограммы, содержащего в пятом поле первого запоминающего блоке б в шифратор 12 при8условии что эта автономная микропрограмма уже однажды выпоцняпась,71 12Во втором запоминающем блоке 19 записаны микрокоманды Ь ,Ф 1 Я из которых формируются все микропрограммы Р =1 мо состоящие иэ некоторых линейных последовательностей микрокоманд, количество которых соответствует текущему номеру микропрограммы, задаваемому в пятом поле С, М,п 1 первого запоминаю 5щего блока 3, Каждая микрокоманда ЬЧ, Ф 1,Я состоит из трех попей разрядностью 1 1 и т соответственно. В первом. лопе Ьсчитываемом по первому выходу 34, задаются сигналы микроопераций, Сигнал со второго поля Ь считываемыйЧпо второму выходу 35, осуществляет прибавление единицы к содержимому счетчика 17 адреса, а в случае, когдаЬЧ:О, кроме того, вычитание единицы из содержимого счетчика микрокоманд 13. В третьем попе ЬФ 1,Я считываемом по тре 3тьему выходу 36, записывается единица, если данная микрокоманда принадлежит автономной микрокоманде Р,ц, К=1, и является в ней последней.Устройство работает следующим образом.В исходном состоянии все элементы памяти находятся в нулевом состоянии.Код операции через первый вход 26 устройства поступает на регистр 1 адреса, задавая адрес соответствующей ячейке в первом запоминающем блоке 3.Генератор 21 тактовых импульсов через второй элемент 22 задержки и чет- вертый элемент И 23 при получении сигнала разрешения с выхода третьего элемента И 14, соответствующего нулевому содержимому счетчика 13 микрокоманд, производит установку в нуль счетчика 17 адреса, регистра 4 логических условий и буферного регистра 6, а также осуществляет пуск первого дешифратора 2. По сигналу дешифратора 2 с перо вого запоминающего бпока 3 считывается микрокоманда О= 0=1,П 1, соответствующая первой выпопняемой микропрограмме Р,:1,ПО первой реализуемой программы К 1= 1 М, С выхода 27 первого запоминающего блока 3 в буферный регистр 6 записывается косвенный адрес номера следующей микропрограммы. Сигнал с выхода 28 устанавливает регистр 1 адреса в исходное состояние. С выхода 29 в регистр 4 логических условий записывается код проверяемых логических условий, Одновременно сигнал, соответствующий номеру текущей микропрограммы, с выхода 31 поступает через четвертую группу элементов И 11,3 9344открытую разрешающим сигналом с выхода элементов ИЛИ-НЕ вследствие нулевого состояния всех выходов третьей группы элементов И 9, на вход шифратора12, Нулевое состояние всех выходов третьей группы элементов И 9 обусловленов этой ситуации нулевым содержаниемвсех т разрядов регистра 8 фиксациивыполнения автономных микропрограмм.С выходов шифратора 12 в счетчик 13 10микрокоманд записывается признак длины текущей микропрограммы, а в счетчик 17 адреса - адрес первой микрокоманды Ь 1=1,Я текущей микропрограммы,3"- 1,т;,5После считывания информации из первого запоминающего блока 3 импульс 21генератора через элементы 22 и 15задержки первый элемент И 16 открывает вторую группу элементов И 7 и разрешает перезапись информации с регистра 6 на регистр 1.После считывания микрокоманд из первого запоминающего блока 3 и записив счетчик 13 микрокоманд кода длины 25текущей микропрограммы его показанияотличны от нуля,Поэтому сигнал на выходе третьегоэлемента И 14 принимает нулевое значение и через первый элемент НЕ 24 от З 0крывает второй элемент И 25, через который следующий тактовый импульс генератора 21 запускает второй дешифратор .18, Далее по каждому тактовому импульсу генератора 21 в соответствии с адресом, записанном в счетчике 17 адреса,из запоминающего блока 19 считываются микрокоманды Ь,Ы 1,Я,.С выхода 34второго запоминающего блока считываются сигналы микроопераций, с выхода 35- 40сигналы, увеличивающие на единицу содержимое счетчика 17 адресов и уменьшающее при Ъ= 1 на единицу содержимоесчетчика 13 микрокоманд, При показаниисчетчика 13 микрокоманд, отличных отнуля, следующий тактовый импульс аналогично описанному осуществляет считывание микрокоманд из второго запоминающего блока 19,В процессе работы адаптивного микропрограймного устройства управления приполучении на первом входе устройства32 соответствующего сигнала с выходовэлементов И первой группы 5 возможноизменение показаний буферного регист 55ра 6 еЕсли показание счетчика 13 микрокоманд равно нулю, то импульс генераторе21 через элементы 22 и 15 задержки,71 14 первый элемент И 16 и вторую группуэлементов И 7 передает адрес номераследующей микрокоманды, соответствующий следующей микропрограмме реализуемой программы К;, :1,М с буферного регистра 6 на регистр 1 адреса.Следующий импульс генератора 21через второй элемент 22 задержки и чет-.вертый элемент И 23 устанавливает висходное состояние счетчик 18 адреса,регистр 4 логических условий н буферный регистр 6. Кроме того, осуществляется запуск дешифратора 2, считываетсямикрокоманда с 1,1=1 р, из первого запоми.нающего блока 3 и работа устройстваосуществляется аналогично описанномувыше.В счучае считывания из первого запо.минающего блока 3 микрокоманды, соответствующей первой автономной микрокоманде Р, К=1,т выходов 30 на К-йсэлементИтретьей группы элементов И9 поступает единичный сигнал. Однаковыходы третьей группы элементов И 9по-прежнему сохраняют нулевое состояние, так как все п разрядов регистрафиксации выполнения автономных микропрограмм 8 находятся в нулевом состоянии, Поэтому работа устройства осушест.вляется аналогично описанному выше дотех пор, пока из второго запоминающего блока 19 не будет считана последняямикрокоманда 13,М= ,й автономной микропрограммы РАК, К=1,т.При этом на третьих выходах 36 второго запоминающегоблока 19 снимается сигнал, в -м разряде которого записана единица, Зготсигнал подается на второй выход устройства для управления пересылкой получаемого в результате выполнения автономной микропрограммы Р , К - 1,т результата на хранение, с целью его дальнейшего использования при реализации других программ, содержащих автономнуюКроме того, этот же сигнал подаетсяна вход регистра 8 фиксации выполненияавтономных микропрограмм для записи вего К -м разряде единицы,Пусть теперь в процессе дальнейшейработы при реализации некоторой другойпрограммы потребуется выполнить автономную микропрограмму Рх, К=1,п,которая уже раз выполнялась адаптивныммикропрограммным устройством управления, В этом случае при считывании микрокоманды, соответствующей требуемой автономной микропрограмме Рд К 1,т 1на четвертом выходе 30 в К -м разряде15 9344 появится единичный сигнал, который поступит на К -й элемент третьей группы элементов И 9. Этот элемент открыт, поскольку в К -м разряде регистра фикса ции выполнения автономных микропрограмм 8 записана единица.В результате на выходе элемента ИЛИНЕ 10 формируется сигнал, запрещающий передачу через четвертую группу элементов И 11 текущего номера микрокоман о ды 4 Е =1 во соответствующего данной автономной микрокомандне Р, К=1,ю с пятого выхода 31 первого запоминающего блока 3 на вход шифратора 12. Одновременно с третьего выхода 33 устройства подается управляющий сигнал на считывание хранящегося результата выпол нения автономной. микропрограммы.Так как в этой ситуации счетчик 13 микрокоманд остается в нулевом состоянии, то импульс генератора 21 через элементы 22 и 15 задержки, первый элемент И 16 и вторую группу элементов И 7 передает косвенный номер спедующей микрокоманды Я, := 1 що первого 25 запоминающего блока 3 .в регистр 1 адреса, Иальше устройство работает аналогично описанному вышеВ случае необходимости выполнения рассматриваемой автономной микропрограммы РА, К=1 е в третий, четвертый, , Сраэ устройство работает точно так же, как и при вторичном ее выполнении.При реализации любой другой автономной микрокоманды из подмножества РА работа адаптивного микропрограммного устройства управления отличается только распопожением единиц в считываемых ко- жха 4 Е,Р:т 1,Ъ ЪМЪ Ч=,аПри поступлении на вход 26 нового кода операции после выполнения набора программ, кроме записи его в регистр 1 адреса, осуществляется установка в нуль регистра 8 фиксации выполнения автоном- . ных микропрограмм.Таким образом, соединение третьего выхода .36 второго запоминающего блока 19 с вторым выходом устройства и первым входом регистра 8 фиксации выполнения автономных микропрограмм, вход установки в нуль которого соединен с первым входом 26 устройства, а выход соединен с первыми входами элементов И третьей группы элементов И 9, вторые входы которых подкаочены к четвертому55 выходу 30 первого запоминающего бпока, 3, а выходы соединены с третьим выходом ЗЗ устройства и входами элемента 71 16 10 ИЛИ-НЕ, выход котороо соединен с первыми входами эпементов И четвертой группы элементов И 11, вторые входы которых соединены с пятыми выходами 31 первого запоминающего блока 3, а выход соединен с входом шифратора 12, позволяет повысить быстродействие устройства в целом.Это следует из того, что при последовательной реализации всехпрограмм множества Р: Й,1:1 Й каждая автономная микропрограмма Р, К=1,щ подмножества Рс Р выпоцняется адаптивным микропрограммным устройством управления нейС =1 Я раз как это делается в известном, а только однажды, Если автономная микропрограмма РА К=1,т выполняется эа время 1 К то за счет отсутствия повторной реализации одной микропрограммы выигривается времяМ"к= К "К 1Следовательно, при последовательной реализации всего подмножества РА,РАк, К=1,п величину выигрыша времени (повышения быстродействия) можно определить по формуле щ щ М ЬТ=СЬТК=С ЕРКК .К К 1 К 1 формула изобретения Адаптивное микропрограммное устройство управления, содержащее регистр адреса, первый и второй дешифраторы, первый и второй запоминающие блоки, регистр погических условий, перую и вторую группы элементов И, буферный регистр, шифратор, счетчик микрокоманд, первый, второй, третий и четвертый элементы И, первый и второй элемент задержки, счетчик адресов, первый и вто рой элементы НЕ и генератор тактовых импульсов, причем адресный вход регист ра адреса подключен к первому входу устройства, выход регистра адреса соединен с первым входом первого дешифратора, а выход - с входом первого запоми минающего блока, первый второй и третий выходы котопого соединены соответственно с входом адреса буферного регистра, входом установки в нуль регистра адреса и информационным входом регистра логических условий, выходы кото17 9344 рого соединены с первыми входами элементов И первой группы, вторые входы которых подключены к второй группе вхо. дов устройства, а выходы соединены с группой входов логических условий буферного регистра, выходы которого соединены с первыми входами элементов И второй группы, вторые входы и выходы которых соединены соответственно с выходом первого элемента И и группой входов 1 О косвенного адреса регистра адреса, первый выход шифратора соединен с первым входом счетчика микрокоманд, первый и второй входы второго элемента И соединены соответственно с выходом ге З нератора тактовых импульсов и выходом первого элемента НЕ, вход которого соединен с выходом третьего элемента И и первым входом четвертого элемента И, второй вход которого соединен с входом 2 й первого и выходом второго элементов задержки, первый и второй входы первого элемента задержки соединены соответственно с выходами первого элемента задержки и третьего элемента И, вход вто З рого элемента задержки соединен с выходом генератора тактовых импульсов, выход четвертого элемента И соединен с вторым входом первого дешифратора, вхо-. дами установки в нуль регистра логичес- Зй ких условий и буферного регистра и первым входом счетчика адресов, второй и третий входы и выход которого соединены соответственно с входом второго элемента НЕ, вторым выходом шифратора и первым входом второго дешифрагора, второй вход и выход которого соединены соответственно с выходом второго элемента И и входом второго запоминающего блока, группа выходов кода микро- й операции которого является групповым выходом кода микрооперации устройства, в выход адресного признака соединеН с 71 18входом второго элемента НЕ, выход которого соединен с вторым входом счетчикамикрокоманд, выходы которого соединеныс входами третьего элемента И о т л ич а ю щ е е с я тем, что, с целью повышения быстродействия, в него введенырегистр фиксации выполнения автономныхмикропрограмм, третья и четвертая группы элементов И и элемент ИЛИ-НЕ, при"чем группа информационных входов, входустановки в нуль и выходы регистра фиксации выполнения автономных микропрограмм соединены соответственно с группой выходов признака автономности микропрограммы второго запоминающего блока, первым входом регистра адреса ипервымн входами элементов И третьейгруппы, вторые входы и выходы которых, соединены соответственно с группой выходов признака автономности текущеймикропрограммы первого запоминающегоблока и входами элемента ИЛИ-НЕ, выход которого соединен с первыми входами элементов И четвертой группы, вторые входы и выходы которых соединенысоответственно с группой выходов номера текущей микропрограммы первого запоминающего блока и входами шифратора, группа выходов признака автономности текущей микропрограммы второго запоминающего блока является групповымвыходом признака автономности текущеймикропрограммы устройства, выходы элементов И третьей группы являются группой выходов признака считывания результата устройства.Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССРИ 9 646333, кл. С 06 Г 9/16, 1979,2. Авторское свидетельство СССР позаявке % 2633719/18-24,л. С 06 Г 9/16, 1978 (прототип).

СмотретьЗаявка

2917653, 25.04.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

БАРБАШ ИВАН ПАНКРАТОВИЧ, СИДОРЕНКО ВАЛЕНТИН ИВАНОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: адаптивное, микропрограммное

Опубликовано: 07.06.1982

Код ссылки

<a href="https://patents.su/10-934471-adaptivnoe-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Адаптивное микропрограммное устройство управления</a>

Предыдущий патент: Устройство для деления чисел, представленных число импульсным кодом

Следующий патент: Микропрограммное устройство управления

Случайный патент: Устройство для подвески съемочных камер круговой панорамы к вертолету