Устройство для коррекции ошибок вычислительного процесса

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1807487

Авторы: Зенин, Литвиненко, Терещенков, Тимонькин, Ткаченко, Харченко

Текст

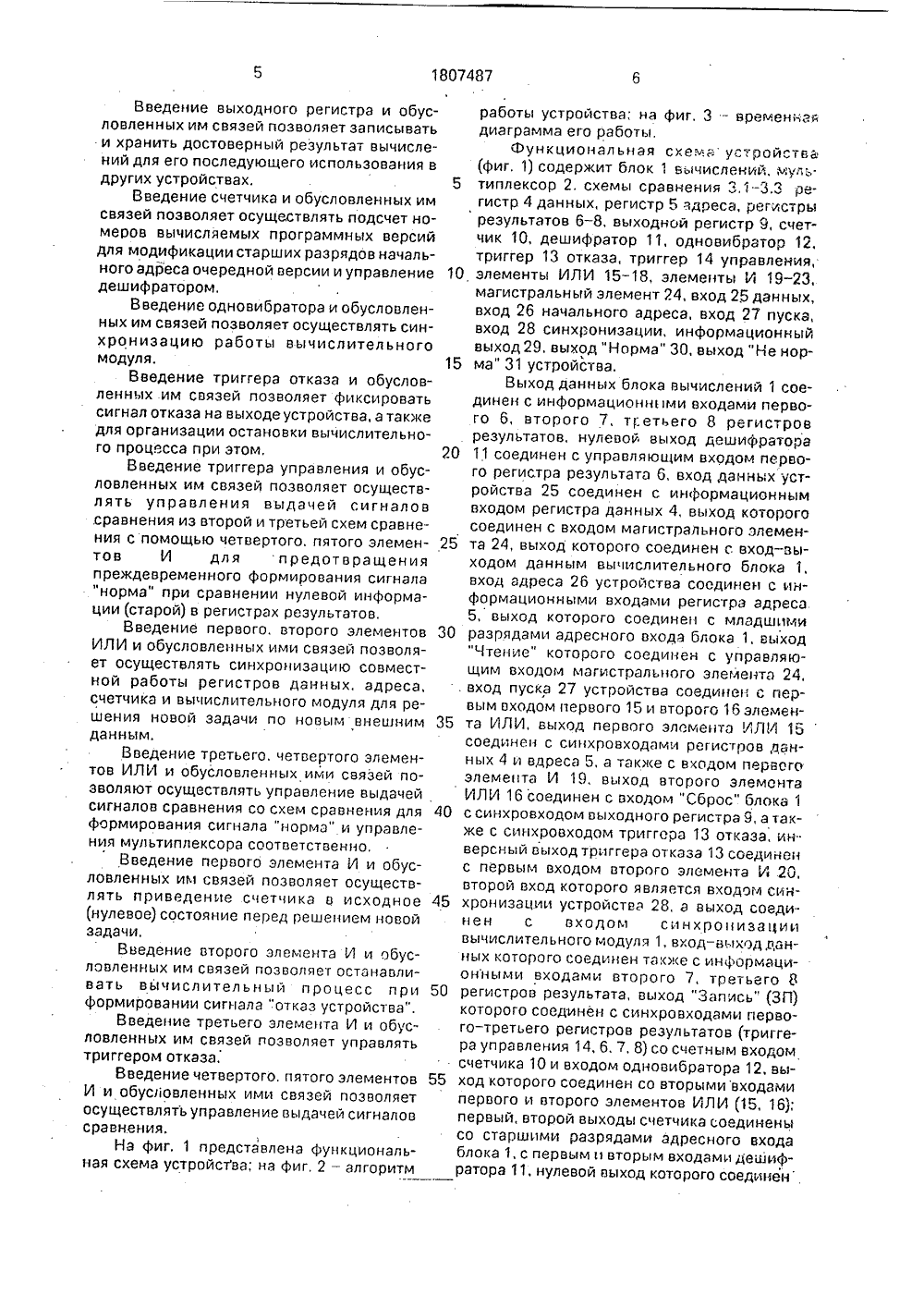

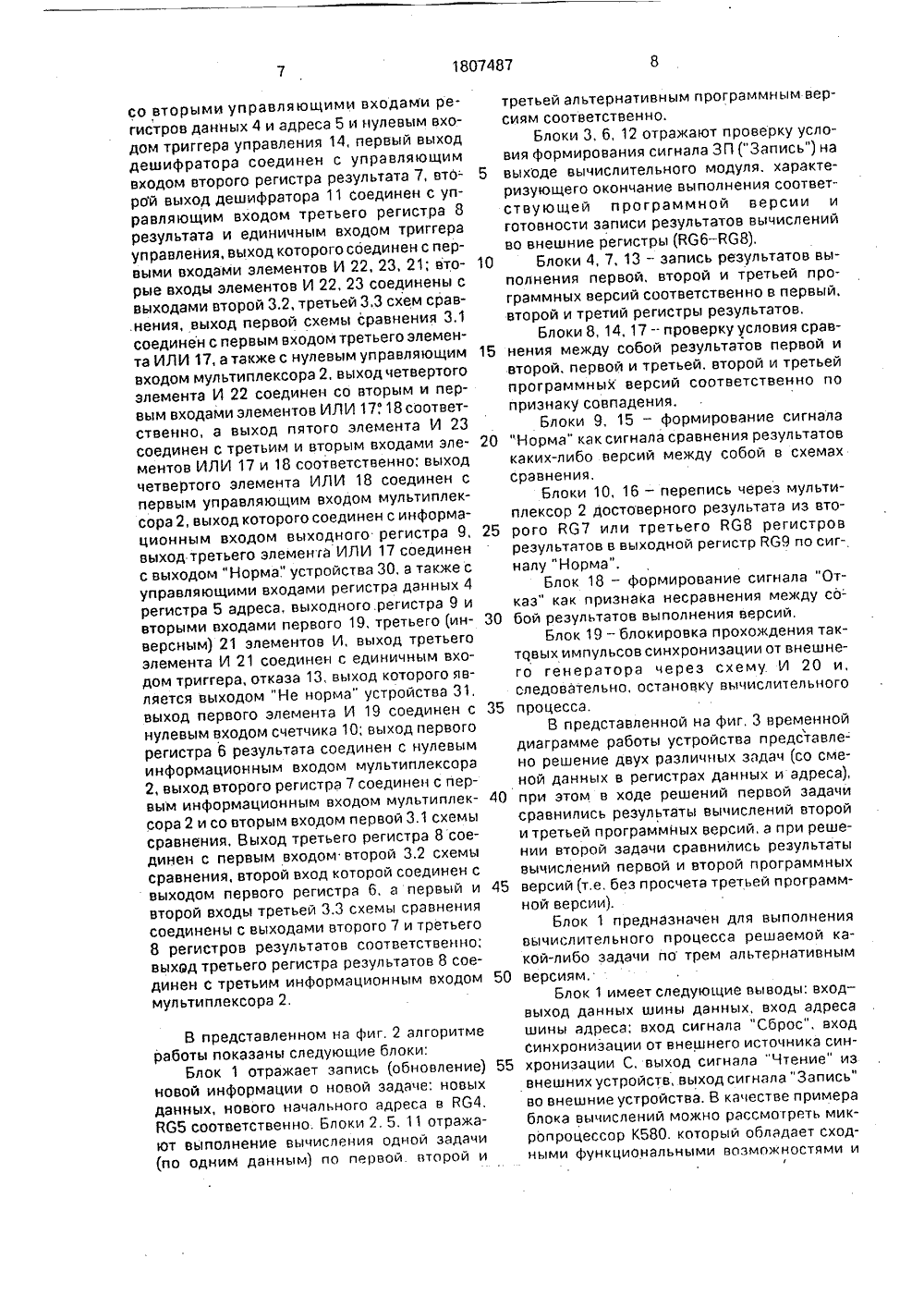

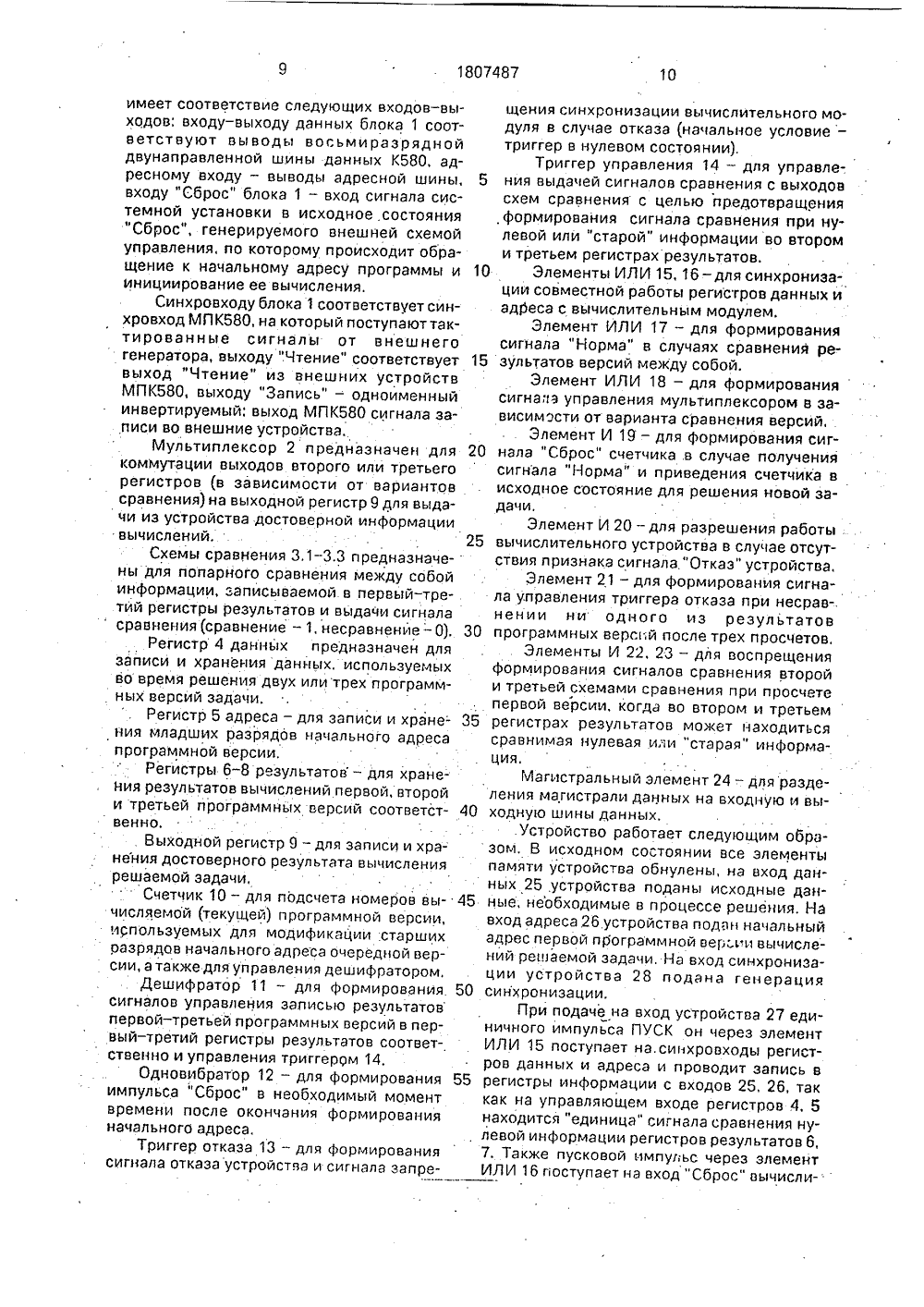

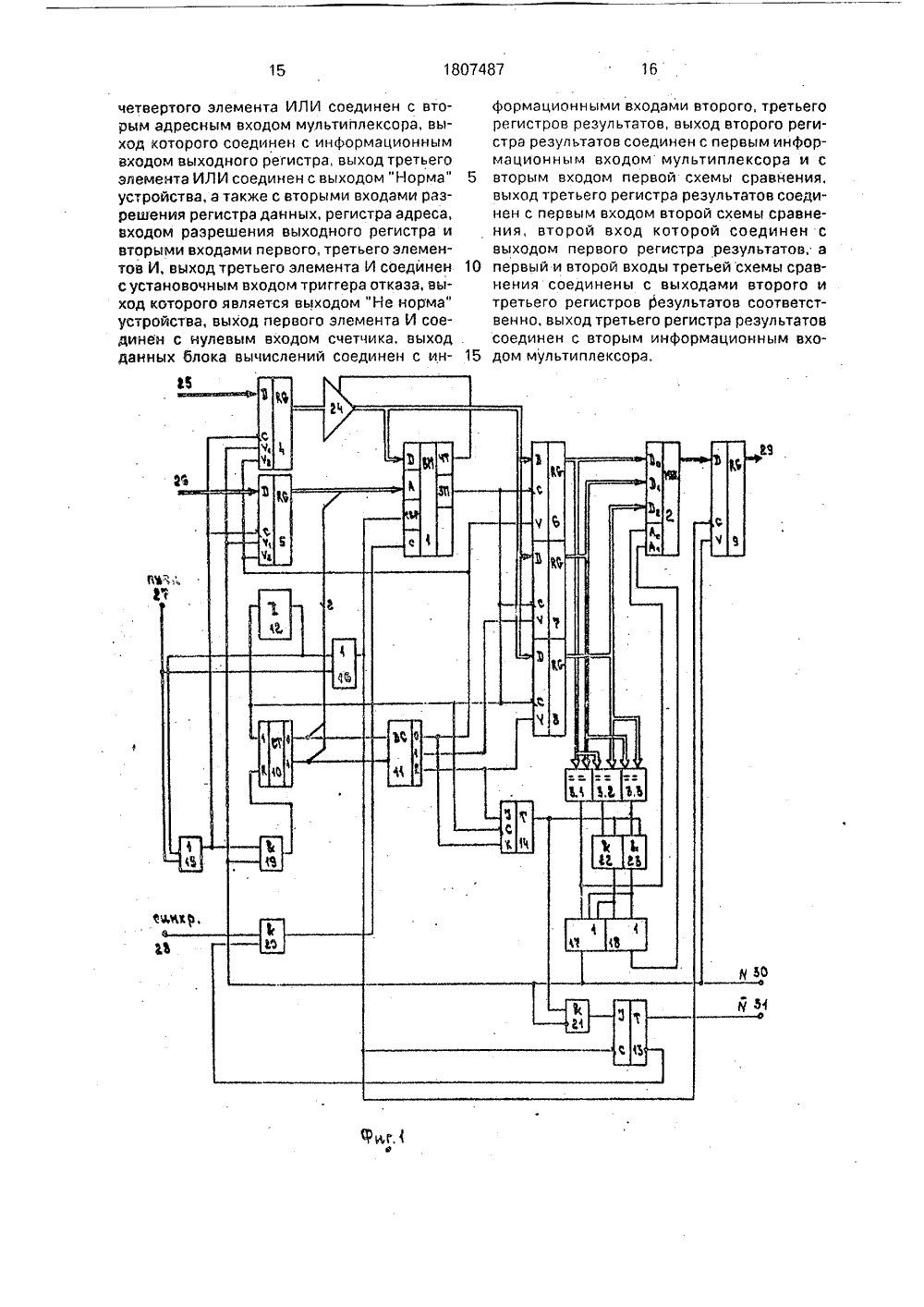

1807487 СООЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХ ЕСПУБЛИК ТЕНТНОЕ ГОСУДАРСТВЕННО ВЕДОМСТВО ССС (ГОСПАТЕНТ СССР к,д 3.9 1 1 М И(56) Авторское свидетельство СССРМ 1390612, кл, 6 06 Р 11/16, 1988.Микропрограммные управляющие устройства и системы / Под ред, Г, Н.Тимонькина. Ч, 2. - Харьков, 1982. С, 154,(54) УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК ВЫЧИСЛИТЕЛЬНОГО ПРОЦЕССА(57) Изобретение относится к вычислительной технике и может быть использовано ввысоконадежных вычислительных устройствах, Цель изобретения - повышение достоверности выходной информациивычислительного модуля, Она достигаетсявведением регистра данных, регистра адреса, второго и трегьего регистров результата,Предлагаемое устройство относится к области автоматики и вычислительной техники и может быть использовано в высоко- надежных вычислительных устройствах,Цель изобретения - повышение достоверности выходной информации вычислительного модуля.Поставленная цель достигается тем, что в устройство для коррекции ошибок вычислительного модуля, содержащее вычислительный модуль, первый регистр результата, дешифратор, первую схему сравнения, мультиплексор, - причем выход данных вычислительного модуля соединен с информационным входом первого регистра выходного регистра, второи и третьеи схем сравнения, триггера отказа, триггера управления, счетчика, одновибратора, с первого по четвертый элементов ИЛИ, с первого по пятый элементов И, магистральногоэлемента, Сущность изобретения состоит в увели.чении вероятности правильного функционирования устройства и в увеличении достоверности выдаваемой информации путем коррекции ошибок вычислительного процесса, вызываемых сбоями и ошибками, в том числе программного обеспечения методом двух- или трехкратного решения одной задачи по двум (трем) различным альтернативным программным версиям, разнесенным последовательно по времени, с последующим сравнением между собой полученных ре. зультатов. Достоверны считается результат, сравниваемый в двух программных версиях, 3 ил. результата, выход которого соединен с ну левым информационным входом мульти- фь, плексора, а также с первым входом первой (ф схемы сравнения, кроме того, нулевой выход дешифратора соединен с управляющим входом первого регистра результата, дополнительно введены регистр данных, регистр адреса, второй и третий регистры результатов, выходной регистр, вторая и третья схемы сравнения, триггер отказа. триггер управления, счетчик, одновибратор, с первого по четвертый элементы ИЛИ, с первого по пятый элементы И, блок магистральных элементов. причем вход данных устройства соединен с информационным входом реги1807487 юУъ сцции дм сичм юрса реева йф алгачи ФМ рсщйнмс носааЬ оставитель В,Харченкоехред М,Моргентал Корректор А.Козориз Редакто Производ но издательский комбинат "Патент", г, Ужгород, ул,Гагарина. 1 Заказ В381 Тираж ИПИ Государственного ко 113035, МоПодписноеитета по изобретениям и открытиям при ГКква, Ж, Раушская наб 4/5мы сравнения соединен с первым входом третьего элемента ИЛИ. а также с нулевым управляющим входом мультиплексора, выход четвертого элемента И соединен со вторым и первым входами третьего и четверого элементов ИЛИ соответственно, а выход пятого элемента И - с третьим и вторым входами третьего и четвертого элементов ИЛИ соответственно, выход четвертого элемента ИЛИ соединен с первым управляющим входом мультиплексора, выход которого соединен с информационнымвходом выходного регистра, выход третьего 50 стра данных, выход которого соединен с входом магистрального элемента, выход ко. торого соединен с входом - выходом вычислительного модуля, вход адреса устройства соединен с информационным входом реги стра адреса, выход которого соединен с младшими разрядами адресного входа вычислительного модуля, выход "Чтение" которого соединен с управляющим входом магистрального элемента; вход пуска уст ройства соединен с первым входом первого и второго элемента ИЛИ, выход первого элемента ИЛИ соединен с синхровходами регистров данных и адреса, а также с входом первого элемента И, выход второго элемен та ИЛИ соединен с входом "Сброс" вычислительного модуля, синхровходом выходного регистра, а также ссинхровхо- .дом триггера отказа, инверсный выход триггера отказа соединен с первым входом 20 второго элемента И, второй вход которого является входом синхронизации устройства, а выход соединен с входом синхронизации вычислительного модуля, выход "Запись" которого соединен с синхровхода ми первого - третьего регистров результатов, триггера управления, счетным входом счетчика и входом одновибратора, выход которого соединен со вторыми входами первого и второго элементов ИЛИ, первый и З 0 второй выходы счетчика соединены со стар- шими разрядами адресного входа вычислительного модуля, первым и вторым входами дешифратора, нулевой выход которого также соединен с нулевым входом триггера уп- З 5 равления и со вторыми управляющими входами регистров данных и адреса., первый выход дешифратора соединен с управляющим входом второго регистра результата.второй выход дешифратора соединен с уп равляющими входом третьего регистра результата и единичным входом триггера управления, выход которого соединен с первыми входами третьего - пятого элементов И, вторые входы четвертого и пятого элементов И соединены с выходами второй и третьей схем сравнения, выход первой схеГ элемента ИЛИ соединен с выходом "Норма" устройства, а также с управляющими входами данных регистра адреса, выходного регистра и вторыми входами первого и третьего элементов И, выход третьего элемента И соединен с единичным входомтриггера отказа, выход которого является выходом сигнала "Не норма" устройства. выход первого элемента И соединен с нулевым одо счетчика, вод да вычислительного модуля соединен с информационными входами второго и третьего регистров результатов, выход второго регистра результатов соединен с первым информационным входом мультиплексора и вторым входом первой схемы сравнения, выход третьего регистра результата соединен с первым входом второй схемы сравнения, второй вход которой соединен с выходом первого регистра результата, а первый и второй входы третьей схемы сравнения соединены с выходами второго и третьего регистров результатов соответственно, выход третьего регистра результатов соединен с вторым информационным входом мультиплексора.Сущность изобретения состоит в увеличении надежности устройства, достоверности выдаваемой информации путем коррекции ошибок вычислительного процесса, вызванных сбоями и ошибками, в том числе программного обеспечения, методом двух- или трехкратного решения одной задачи по двум (трем) различным альтернативным программным версиям,.разнесенным последовательно во времени, с последующим сравнением между собой полученных результатов, Достоверным считается результат, сравнимый в двух программных версиях.Изобретение реализуется путем введения следующих новых элементов и связей,Введение двух дополнительных (второй и третьей) схем сравнения и обусловленных ими связей позволяет реализовать сравнение между собой трех результатов вычислений в различных сочетаниях для определения достоверного результата.Введение регистра данных и регистра адреса и обусловленных ими связей позволяет запомнить исходные данные и начальный адрес микропрограммы для двух-, трехкратной ее реализации.Введение дополнительно .второго и третьего регистров результатов позволяет записывать и хранить результаты вычислений альтернативных программных версий для последующей организации их сравнения и выдачи сравнимого результата.10 20 25 30 40 50 55 Введение выходного регистра и обусловленных им связей позволяет записывать и хранить достоверный результат вычислений для его последующего использования в других устройствах.Введение счетчика и обусловленных им связей позволяет осуществлять подсчет номеров вычисляемых программных версий для модификации старших разрядов начального адреса очередной версии и управление дешиф ратором,Введение одновибратора и обусловленных им связей позволяет осуществлять синхронизацию работы вычислительного модуля.Введение триггера отказа и обусловленных им связей позволяет фиксировать сигнал отказа на выходеустройства, а также для организации остановки вычислительного процесса при этом,Введение триггера управления и обусловленных им связей позволяет осуществлять управления выдачей сигналов сравнения из второй и третьей схем сравнения с помощью четвертого, пятого элементов И для предотвращения преждевременного формирования сигнала "норма" при сравнении нулевой информации (старой) в регистрах результатов.Введение первого, второго элементов ИЛИ и обусловленных ими связей позволяет осуществлять синхронизацию совместной работы регистров данных, адреса, счетчика и вычислительного модуля для решения новой задачи по новым внешним данным.Введение третьего, четвертого элементов ИЛИ и обусловленных ими связей позволяют осуществлять управление выдачей сигналов сравнения со схем сравнения для формирования сигнала "норма" и управления мультиплексора соответственно.Введение первого элемента И и обусловленных им связей позволяет осуществлять приведение счетчика в исходное (нулевое) состояние перед решением новой задачи,Введение второго элемента И и обусловленных им связей позволяет останавливать вычислительный процесс при формировании сигнала "отказ устройства".Введение третьего элемента И и обусловленных им связей позволяет управлять триггером отказа.Введение четвертого, пятого элементов И и обусловленных или связей позволяет осуществлять управление выдачей сигналов сравнения,На фиг. 1 представлена функциональная схема устройства; на фиг, 2 - алгоритм работы устройства; на фиг. 3 - временная диаграмма его работы,Функциональная схема ус,ройства фиг, 1) содержит блок 1 вычислений, муль типлексор 2. схемы сравнения 3,1-3.3 регистр 4 данных, регистр 5 адреса, регистры результатов 6 - 8, выходной регистр 9, счетчик 10, дешифратор 11, одновибратор 12, триггер 13 отказа, триггер 14 управления,элементы ИЛИ 15-18, элементы И 19 - 23,магистральный элемент 24, вход 25 данных, вход 26 начального адреса, вход 27 пуска, вход 28 синхронизации, информационный выход 29, выход "Норма" 30, выход "Не норма" 31 устройства. Выход данных блока вычислений 1 соединен с информационн или входами первого б, второго 7, третьего 8 регистров результатов, нулевой выход дешифратора 11 соединен с управляющим входом первого регистра результата б, вход данных устройства 25 соединен с информационным входом регистра данных 4, выход которого соединен с входам магистрального элемента 24, выход которого соединен с вход - выходом данныл вычислительного блокавход адреса 26 устройства соединен с информационными входами регистра адреса5, выход которого соединен с младшими разрядами адресного входа блока 1, выход"Чтение" которого соединен с управляющим входом магистрального элемента 24,вход пуска 27 устройства соединен с первым входом первого 15 и второго 16 элемента ИЛИ, выход первого элемента ИЛИ 15 соединен с синхровходами регистров данных 4 и адреса 5, а также с входом первого элемента И 19, выход второго элемента ИЛИ 16 соединен с входом "Сброс" блока 1 с синхровходом выходного регистра 9, э также с синхровходом триггера 13 отказа, инверсный выход триггера отказа 13 соединен с первым входом второго элемента И 20, второй вход которого является входом синхронизации устройства 28, а выход соединен с входом синхронизации вычислительного модуля 1, вход - выход данных которого соединен также с информационными входами второго 7, третьего 8 регистров результата, выход "Запись" ЗП) которого соединен с синхровходэми первого-третьего регистров резул ьтато в (триггера управления 14, б, 7, 8) со счетным входом счетчика 10 и входом одновибрэтора 12, выход которого соединен со вторымивходами первого и второго элементов ИЛИ 15, 16); первый, второй выходы счетчика соединены со старшими разрядами адресного входа блока 1. с первым и вторым входами дешифратора 11, нулевой выход которого соединенсо вторыми управляющими входами регистров данных 4 и адреса 5 и нулевым входом триггера управления 14, первый выход дешифратора соединен с управляющим входом второго регистра результата 7, второй выход дешифратора 11 соединен с управляющим входом третьего регистра 8 результата и единичным входом триггера управления, выход которого соединен с первыми входами элементов И 22, 23, 21; вторые входы элементов И 22, 23 соединены с выходами второй 3.2, третьей 3,3 схем срав.нения, выход первой схемы сравнения 3.1 соединен с первым входом третьего элемента ИЛИ 17, а также с нулевым управляющим входом мультиплексора 2. выход четвертого элемента И 22 соединен со вторым и первым входами элементов ИЛИ 1718 соответственно, а выход пятого элемента И 23 соединен с третьим и вторым входами элементов ИЛИ 17 и 18 соответственно; выход четвертого элемента ИЛИ 18 соединен с первым управляющим входом мультиплексора 2, выход которого соединен с информационным входом выходного регистра 9, выход третьего элемен га ИЛИ 17 соединен с выходом "Норма." устройства 30, а также с управляющими входами регистра данных 4 регистра 5 адреса, выходного. регистра 9 и вторыми входами первого 19, третьего (инверсным) 21 элементов И, выход третьего элемента И 21 соединен с единичным входом триггера, отказа 13, выход которого является выходом "Не норма" устройства 31, выход первого элемента И 19 соединен с нулевым входом счетчика 10; выход первого регистра 6 результата соединен с нулевым информационным входом мультиплексора 2, выход второго регистра 7 соединен с первым информационным входом мультиплексора 2 и со вторым входом первой 3,1 схемы сравнения, Выход третьего регистра 8 соединен с первым входом второй 3.2 схемы сравнения, второй вход которой соединен с выходом первого регистра 6, а первый и второй входы третьей 3.3 схемы сравнения соединены с выходами второго 7 и третьего 8 регистров результатов соответственно; выход третьего регистра результатов 8 соединен с третьим информационным входом мультиплексора 2. В представленном на фиг, 2 алгоритме работы показаны следующие блоки:Блок 1 отражает запись (обновление) новой информации о новой задаче: новых данных, нового начального адреса в 864, В 65 соответственно. Блоки 2, 5, 11 отражают выполнение вычисления Одной задачи (по одним данным) по первой второй и третьей альтернативным программным версиям соответственно.Блоки 3, б, 12 отражают проверку условия формирования сигнала ЗП (" Запись" ) на5 выходе вычислительного модуля, характеризующего окончание выполнения соответствующей программной версии иготовности записи результатов вычисленийво внешние регистры (В 66 - 868),10 Блоки 4, 7, 13 - запись результатов выполнения первой, второй и третьей программных версий соответственно в первый,второй и третий регистры результатов.Блоки 8, 14, 17 - проверку условия срав 15 нения между собой результатов первой ивторой, первой и третьей, второй и третьейпрограммных версий соответственно попризнаку совпадения.Блоки 9, 15 - формирование сигнала20 "Норма" как сигнала сравнения результатовкаких-либо версий между собой в схемахсравнения.Блоки 10, 16 - перепись через мультиплексор 2 достоверного результата из вто 25 рого 867 или третьего 868 регистроврезультатов в выходной регистр 869 по сигналу "Норма".Блок 18 - формирование сигнала "Отказ" как признака несравнения между со 30 бой результатов выполнения версий,Блок 19 - блокировка прохождения тактовых импульсов синхронизации от внешнего генератора через схему. И 20 и,следовательно, остановку вычислительного35 процесса.В представленной на фиг, 3 временнойдиаграмме работы устройства представлено решение двух различных задач (со сменой данных в регистрах данных и адреса),40 при этом в ходе решений первой задачисравнились результаты вычислений второйи третьей программных версий, а при решении второй задачи сравнились результатывычислений первой и второй программных45 версий (т.е, без просчета третьей программной версии).Блок 1 предназначен для выполнениявычислительного процесса решаемой какой-либо задачи по трем альтернативным50 версиям,Блок 1 имеет следующие выводы: вход -выход данных шины данных, вход адресашины адреса; вход сигнала "Сброс", входсинхронизации от внешнего источника син 55 хронизации С, выход сигнала "Чтение" извнешних устройств, выход сигнала "Запись"во внешние устройства. В качестве примераблока вычислений можно рассмотреть микропроцессор К 580. который обладает сходными функциональными возможностями иГения синхронизации вычислительного моуля в случае отказа (начальное условие - риггер в нулевом состоянии).Триггер управления 14 - для управлеия выдачей сигналов сравнения с выходов хем сравнения с целью предотвращения ормирования сигнала сравнения при нуевой или "старой" информации во втором третьем регистрах результатов.Элементы ИЛИ 15, 16 - для синхронизаии совместной работы регистров данных и дреса с вычислительным модулем.Элемент ИЛИ 17 - для формирования игнала "Норма" в случаях сравнения реультатов версий мекду собой.Элемент ИЛИ 18 - для формирования игнала управления мультиплексором в заисимости от варианта сравнения версий,Элемент И 19 - для Формирования сигала "Сброс" счетчика .в случае получения игнала "Норма" и приведения счетчика в сходное состояние для решения новой заачи.Элемент И 20 - для разрешения работы ычислительного устройства в случае отсуттвия признака сигнала."Отказ" устройства.Элемент 21 - для формирования сигнаа управления триггера отказа при несравении ни одного из результатов рограммных версий после трех просчетов,Элементы И 22, 23 - для воспрещения ормирования сигналов сравнения второй третьей схемами сравнения при просчете ервой версии, когда во втором и третьем егистрах результатов может находиться авнимая нулевая и;1 и "старая" информаия.Магистральный элемент 24 - для раздения магистрали данных на входную и выдную шины данных..Устройство работает следующим обрам, В исходном состоянии все элементы мяти устройства обнулены, на вход даных 25 устройства поданы исходные даные, необходимые в процессе решения. На од адреса 26 устройства подан начальный рес первой программной версии вычислей решаемой задачи. На вход синхронизаии устройства 28 подана генерация нхронизации.При подаче на вход устройства 27 едичного импульса ПУСК он через элемент ЛИ 15 поступает на,синхровходы региств данных и адреса и проводит запись в гистры информации с входов 25, 26, так к на управляющем входе регистров 4, 5 ходится "единица" сигнала сравнения нувой информации регистров результатов 6, Также пусковой импульс через элемент И 16 поступает на вход "Сброс" вычислиимеет соответствие следующих входов - вы- щ ходов; входу-выходу данных блока 1 соот- д ветствуют выводы восьмиразрядной т двунаправленной шины данных К 580, адресному входу - выводы адресной шины, 5 н входу "Сброс" блока 1 - вход сигнала сис- с темной установки в исходное, состояния ф "Сброс", генерируемого внешней схемой л управления, по которому происходит обра- и щение к начальному адресу программы и 10 инициирование ее вычисления, цСинхровходу блока 1 соответствует син- а хровход МПК 580, на который поступаюттактированные сигналы от внешнего с генератора, выходу ".Чтение" соответствует 15 з выход "Чтение" из внешних устройств МПК 580, выходу "Запись" - одноименный с инвертируемый: выход МПК 580 сигнала за- в писи во внешние устройства.Мультиплексор 2 предназначен для 20 н коммутации выходов второго или третьего с регистров (в зависимости от вариантов и сравнения) на выходной регистр 9 для выда- д чи из устройства достоверной информации вычислений, 25 вСхемы сравнения 3.1-3,3 предназначе- с ны для попарного сравнения между собой информации, записываемой в первый-тре- л тйй регистры результатов и выдачи сигнала нсравнения(сравнение - 1,несравнение -О). 30 иРегистр 4 данных предназначен для записи и хранения данных, используемых ф во время решения двух или трех программ- и ных версий задачи. иРегистр 5 адреса - для записи и хране р ния младших разрядов начального адреса ср программной версии, . цРегистры б - 8 результатов - для хранения результатов вычислений первой, второй ле и третьей программнйх версий соответст хо венно,Выходной регистр 9 - для записи и хра- зо нения достоверного результата вычисления па решаемой задачи,нСчетчик 10 - для подсчета номеров вы н числяемой (текущей) программной версии, вх используемых для модификации .старших ад оазрядов начального адреса очередной вер- ни сии,атакжедляуправлениядешифратором, цДешифратор 11 - для Формирования 50 си сигналов управления записью результатов первой - третьей программных версий в пер- ни вый-третий регистры результатов соответ- И ственно и управления триггером 14, роОдновибратор 12 - для формирования 55 реимпульса "Сброс" в необходимый момент ка времени после окончания формирования на начального адреса, леТриггер отказа 13 - для формирования 7.сигнала отказа устройства и сигнала запре- ИЛтельного модуля, по которому иницируется вычислительный процесс и происходит считывание информации из внешних регистров-регистра 4 и регистра 5 по сигналу "Чтение", поступающего с выхода ЧТ на магистральный элемент 24 и формирующего направленную входную шину данных, По сигналу системного сброса оычислительного модуля происходит обращение к перной ячейке памяти, куда уже записан начальный адрес программы первой версии, а затем происходит инициирование вычислительного процесса по программе первой версии.При формирования на выходе шины данных блока 1 "информации о результатах вычислений" на выходе ЗП формируется сигнал записи но внешние устройства, Ст-. сутствующий при этом сигнал ЧТ обусловливает высокоимпедансное состояние магистрального элемента и коммутирует выход шины данных нэ информационные входы первого-третьего регистра результатов, По сигналу "ЗП", поступающего на синхровхода первого - третьего регистров результатов, происходит запись результатоо вычислений первой версии в первый регистр б, так как исходное состояние дешифратора 11 формирует нэ. нулевом выходе дешифратора сигнал, поступающий на управляющий вход только первого регистра : результата В 66.Одновременно сигнал "ЗП" с выхода блока 1 поступает на счетный вход счетчика 10, на выходах которого формируется код 10), разряды которого поступают о качестве модифйкэции старших разрядов начального адреса на адресный вход блока 1, задавая новый начальный адрес, а также на вход дешифратора, формируя единичный сигнал нэ его первол выходе, выдавая сигнал разрешения записи на регистр результата 7, Кроме того, сигнал "ЗП" поступает на вход одновибратора 12, формируя на его выходе импульс с параметрами, необходимыми для оконцэния переходных процессов по формированию оного начального адрсса блока 1, окончания записи информации из МП н выходные регистры и формирования сигнала системного сброса блока 1. инициирую- щего нацало вычисления по нторой программной версии,. Так кэк нэ выходах регистров б, 7 различная информация, то на выходе регистра 17 формируется нулевой потенциал, который запрещает перезапись информации о регистры 4, 5,Данные результатов вычисления второйверсии по сигналу "ЗП" запишутся оо второй регистр результатон В 67), так кэк только на управляющем входе второго регистра результата будет присутствовать единица с10 вибратор импульс системного сброса блока 1 и инициирование вычисления по третьей Фсхеме сравнения иэ первого и второго реги 20 состояние 9; 45 страх 4, 5 в течение одной задачи в случае и, следовательно, формирования единично 50 го сигнала сравнения правильного нулевого 30 35 первого оыхода дешифратора, Аналогично нышерассмотренному алгоритму взаимодействия элементов сигнал "ЗП" с выхода блока 1 переведет счетчик 10 в новое состояние 0,1), цто произведет модификацию старших разрядов начального адреса для формирования начального адреса третьей версии, переведет выходы дешифратора в состояние 00.1), сформирует через одноверсии, При сравнении информации в первой стров результатов первой и второй версии на первом выходе схем сравнения сформируется единичный сигнал, который;- переведет упраоляющий код мультиплексора н состояние 1,0), что подключит выход второго регистра результата к входу выходного регистра;- через элемент ИЛИ 17 сформирует сигнал "Норма" сравнения, который разрешит запись сравнимой, а значит, достоверной, информации н выходной регистр; разрешит перезапись информации в регистрах данных и адреса разрешит через элемент И 19 сброс счетчика в исходное- сформирует на выходе устройства 30 сигнал "Норма" решения задачи, При этом сформированный сигналом "ЗП" с выхода блока 1 выходной импульс одновибратора 12 приведет счетчик со старшими разрядами начального адреса и дешифратор в исходное состояние для новой задачи и запишет новые данные, адрес новой задачи в регистры В 64, В 65, а о выходной регистр 9 - достоверный результат уже решенной задачи, а также инициирует оычислительный процесс новой задачи по новым данн ьол,Для предотвращения преждевременной смены входных данных и адреса в региполучения запись в регисгр 6) правильного результата вычисления первой программной версии, но в виде нулевой информации,результата и исходного нулевого состояния второго регистра 7 нулевой выходдешифратора 11 также соединен со вторыми управляющими входами регистров 4, 5, В случае несраонения результатов первой и второй версий происходит вычисление и запись результатов третьей программной версии в третий регистр результатов аналогично описанному выше алгоритму, При наличии результатов 1 рех версий в трех регистрах В 65 10 15 20 25 яние, чем сформирует на выходе 31 сигнал"Отказ" и через элемент И 20 запретит прохождение импульсов синхронизации из 6, 7, 8 происходит сравнение результатов первой и третьей версий во второй схеме сравнения и результатов второй и третьей версий в третьей схеме сравнения.При сравнении любых двух значений с выходов регистра 6 - 8 на выходе элемента ИЛИ 18 - 15 формируется код управления мультиплексора 2 для подключения выхода третьего регистра результатов к входу выходного регистра, а на выходе элемента ИЛИ 17 сформируется сигнал "Норма", так как триггер 14 управления, переведенный в единичное состояние, единичным сигналом с второго выхода дешифратора разрешит прохождение сигналов сравнения через элементы И 22, 23,Сигнал "Норма", поступив на выход 30устройства, аналогично вышеописанному алгоритму переведет схему устройства в исходное состояние для решения новой задачи с новыми данными, Результат решенной задачи при этом будет храниться в выходном регистре.В случае несравнения между собой всех трех результатов через схему И 21 с инвер.- сным входом по выходам схем сравнения триггер отказа перейдет в единичное состовнешнего генератора. Вычислительный процесс блока 1 остановится для дальнейшего выяснения, является ли признак отказа следствием некорректно поставленной задачи; отказа элементов схемы устройства или других причин, но в данном устройстве процесс диагностирования нерассматривается.Формула изобретения Устройство для коррекции ошибок вычислительного процесса, содержащее первый регистр результатов, дешифратор; первую схему сравнения, блок вычислений, мультиплексор, причем выход данных блока вычислений соединен с информационным входом первого регистра результатов. выход которого соединен с первым информационным входом мультиплексора и с первым входом первой схемы сравнения, первый выход дешифратора соединен с входом разрешения записи первого регистра результатов, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности вычислений, в устройство дополнительно введены регистр данных, регистр адреса, второй и третий регистры результатов, выходной регистр, вторая и третья схемы сравнения, триггер отказа, триггер управления, счетчик, одновибратор, с первого по четвертый 35 40 45 50 55 элементы ИЛИ, с первого по пятый элементы И, магистральный элемент, причем информационный вход устройства соединен с информационным входом регистра данных, выход которого соединен с входом магистрального элемента. выход которого соединен с входом данных блока вычислений, вход начального адреса устройства соединен с информационным входом регистра адреса, выход которого соединен с младшими разрядами адресного входа блока вычислений, выход "Чтение" которого соединен с управляющим входом магистрального элемента, вход пуска устройства соединен с первыми входами первого и второго элементов ИЛИ, выход первого элемента ИЛИ соединен с синхровходами регистров данных и адреса и с первым входом первого элемента И, выход второго элемента ИЛИ соединен с входом "Сброс" блока вычислений, с синхровходом выходного регистра и с синхровходом триггера отказа, инверсный выход триггера отказа соединен с первым входом второго элемента И, второй вход которого является входом синхронизации устройства, а выход второго элемента И соединен с входом синхронизации блока вычислений, выход "Запись" которого соединен с синхровходами первого, второго, третьего регистров результатов и триггера управления и со счетным входом счетчика и входом одновибратора, выход которого соединен с вторыми входами первого и второго элементов ИЛИ, первый и второй выходы разрядов счетчика соединены со старшими разрядами адресного входа блока вычислений и с первым и вторым входами дешифратора, первый выход которого соединен с нулевым входом триггера управления, с первыми входами разрешения регистров данных и адреса, второй выход дешифратора соединен с входом разрешения второго регистра результатов, третий выход дешифратора соединен с входом разрешения третьего регистра результатов и единичным входом триггера управления. выход которого соединен с первыми входами третьего, четвертого, пятого элементов И, вторые входы четвертого, пятого элементов И соединены с выходами второй и третьей схем сравнения соответственно, выход первой схемы сравнения соединен с первым входом третьего элемента ИЛИ и с первым адресным входом мультиплексора, выход четвертого элемента И соединен с вторым входом третьего и первым входом четвертого элементов ИЛИ соответственно, выход пятого элемента И соединен с третьим входом третьего и вторым входом четвертого элементов ИЛИ соответственно, выходчетвертого элемента ИЛИ соединен с вторым адресным входом мультиплексора, выход которого соединен с информационным входом выходного регистра, выход третьего элемента ИЛИ соединен с выходом "Норма" устройства, а также с вторыми входами разревения регистра данных, регистра адреса, входом разрешения выходного регистра и вторыми входами первого, третьего элементов И, выход третьего элемента И соединен с установочным входом триггера отказа, выход которого является выходом "Не норма" устройства, выход первого элемента И соединен с нулевым входом счетчика, выход данных блока вычислений соединен с информационными входами второго, третьего регистров результатов, выход второго регистра результатов соединен с первым информационным входом мультиплексора и с 5 вторым входом первой схемы сравнения.выход третьего регистра результатов соединен с первым входом второй схемы сравнения, второй вход которой соединен с выходом первого регистра результатов, а 10 первый и второй входы третьей схемы сравнения соединены с выходами второго и третьего регистров результатов соответственно, выход третьего регистра результатов соединен с вторым информационным вхо дом мультиплексора.

СмотретьЗаявка

4949207, 24.06.1991

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ЗЕНИН АНДРЕЙ ПЕТРОВИЧ, ЛИТВИНЕНКО ВАДИМ ГЕОРГИЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТЕРЕЩЕНКОВ СЕРГЕЙ ВЛАДИМИРОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/16

Метки: вычислительного, коррекции, ошибок, процесса

Опубликовано: 07.04.1993

Код ссылки

<a href="https://patents.su/10-1807487-ustrojjstvo-dlya-korrekcii-oshibok-vychislitelnogo-processa.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции ошибок вычислительного процесса</a>

Предыдущий патент: Устройство для контроля распределителя импульсов

Следующий патент: Устройство для мажоритарного выбора сигналов

Случайный патент: Способ получения окислительных белевых вытравок