Резервированная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1785087

Автор: Родин

Текст

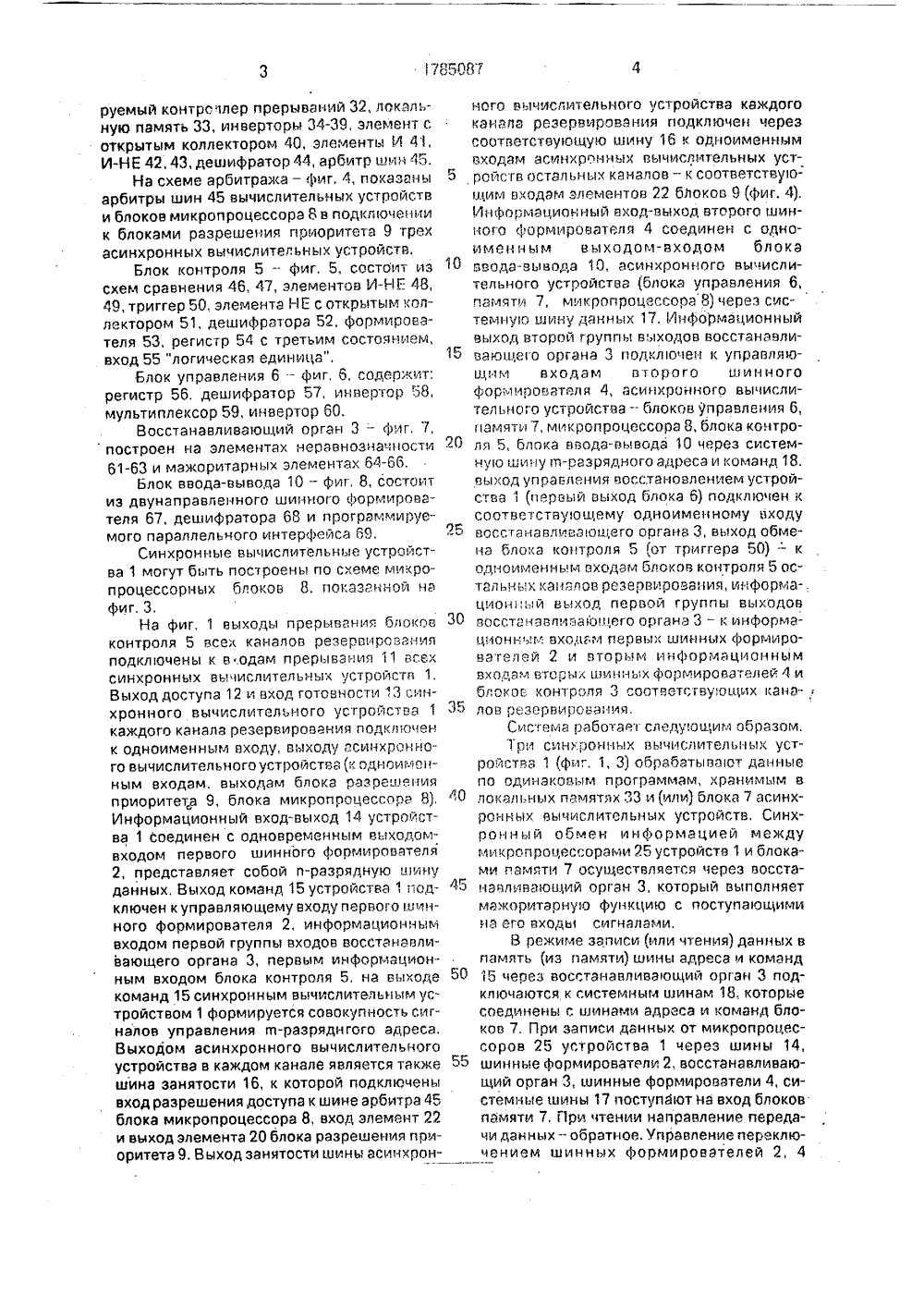

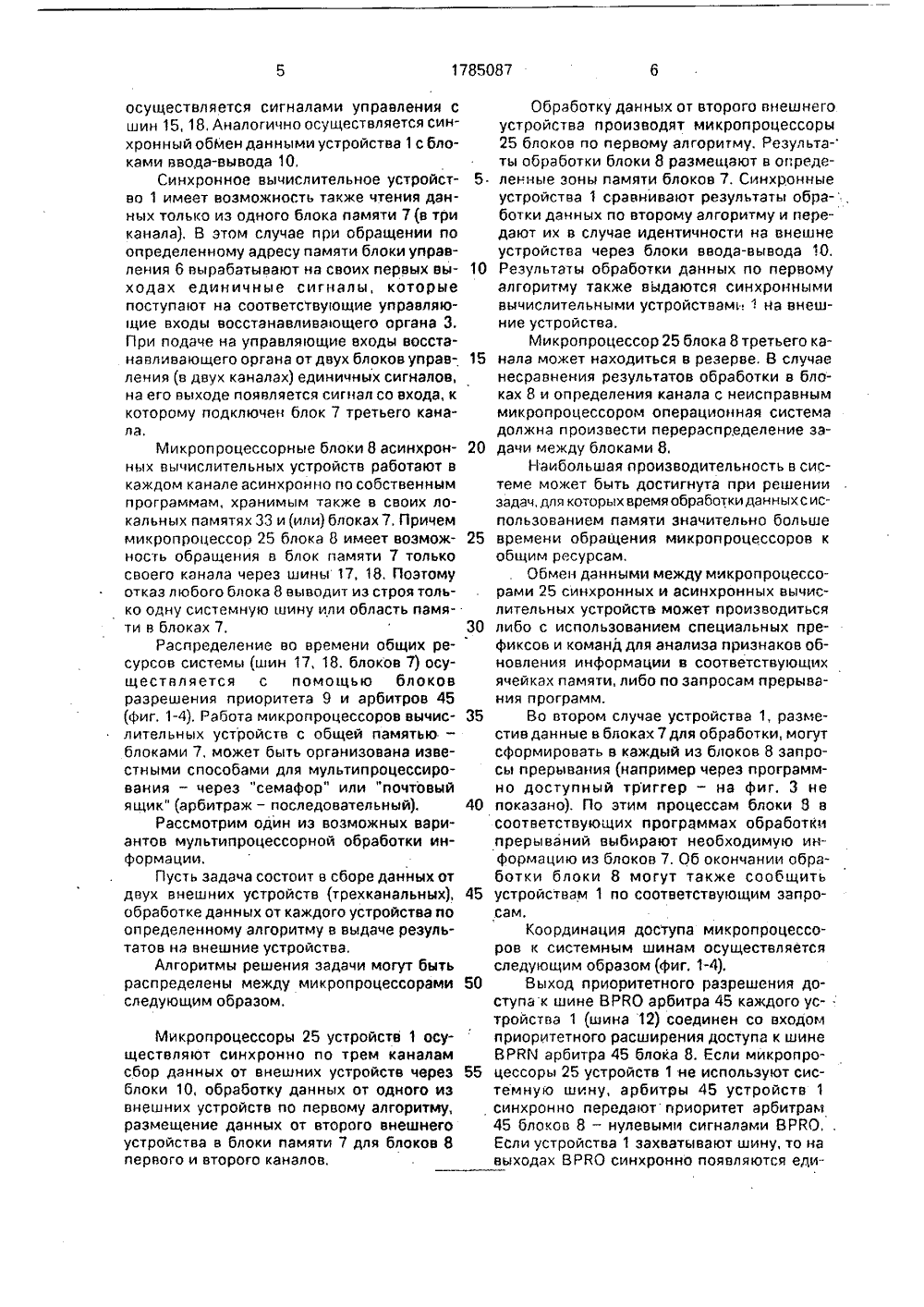

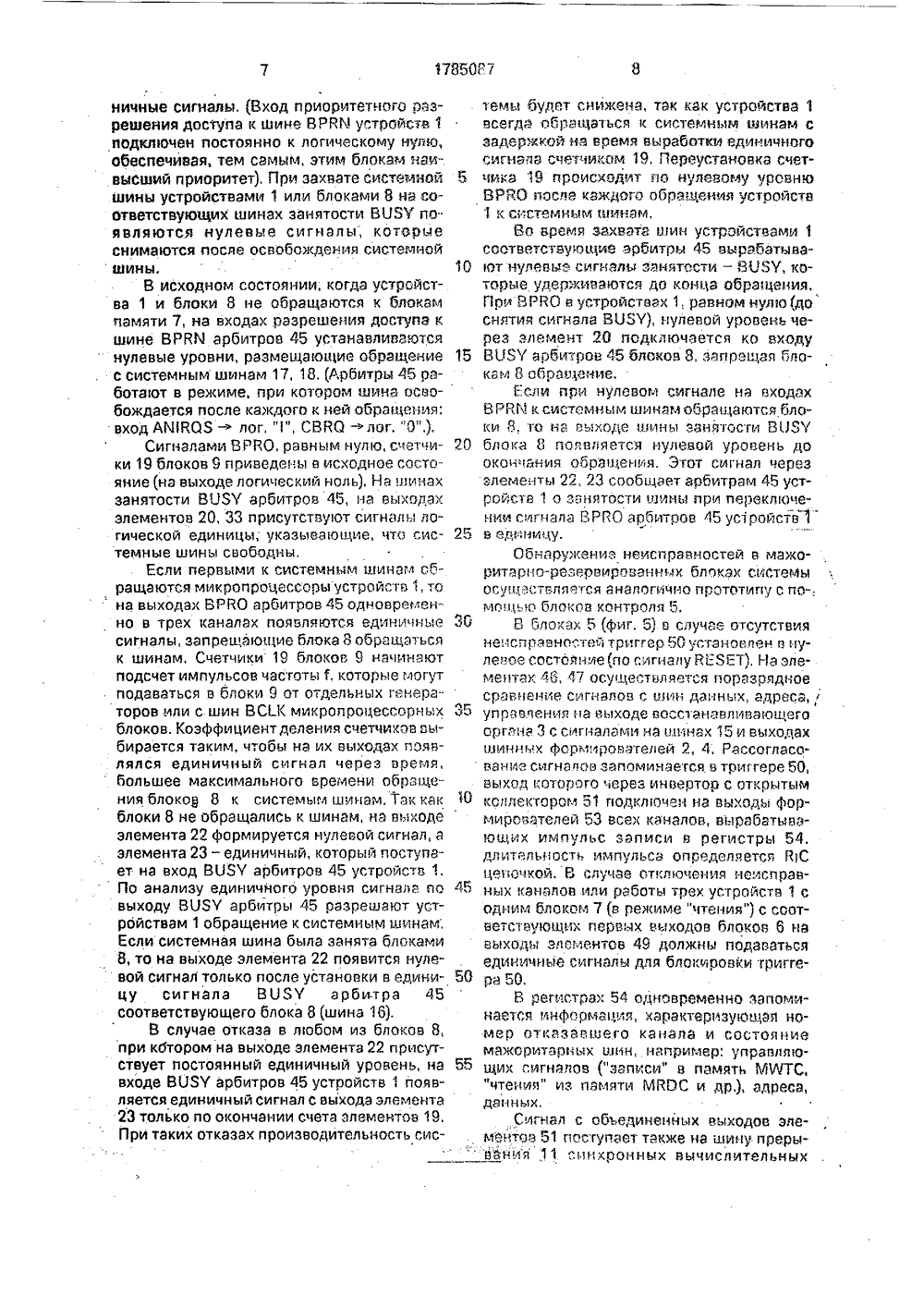

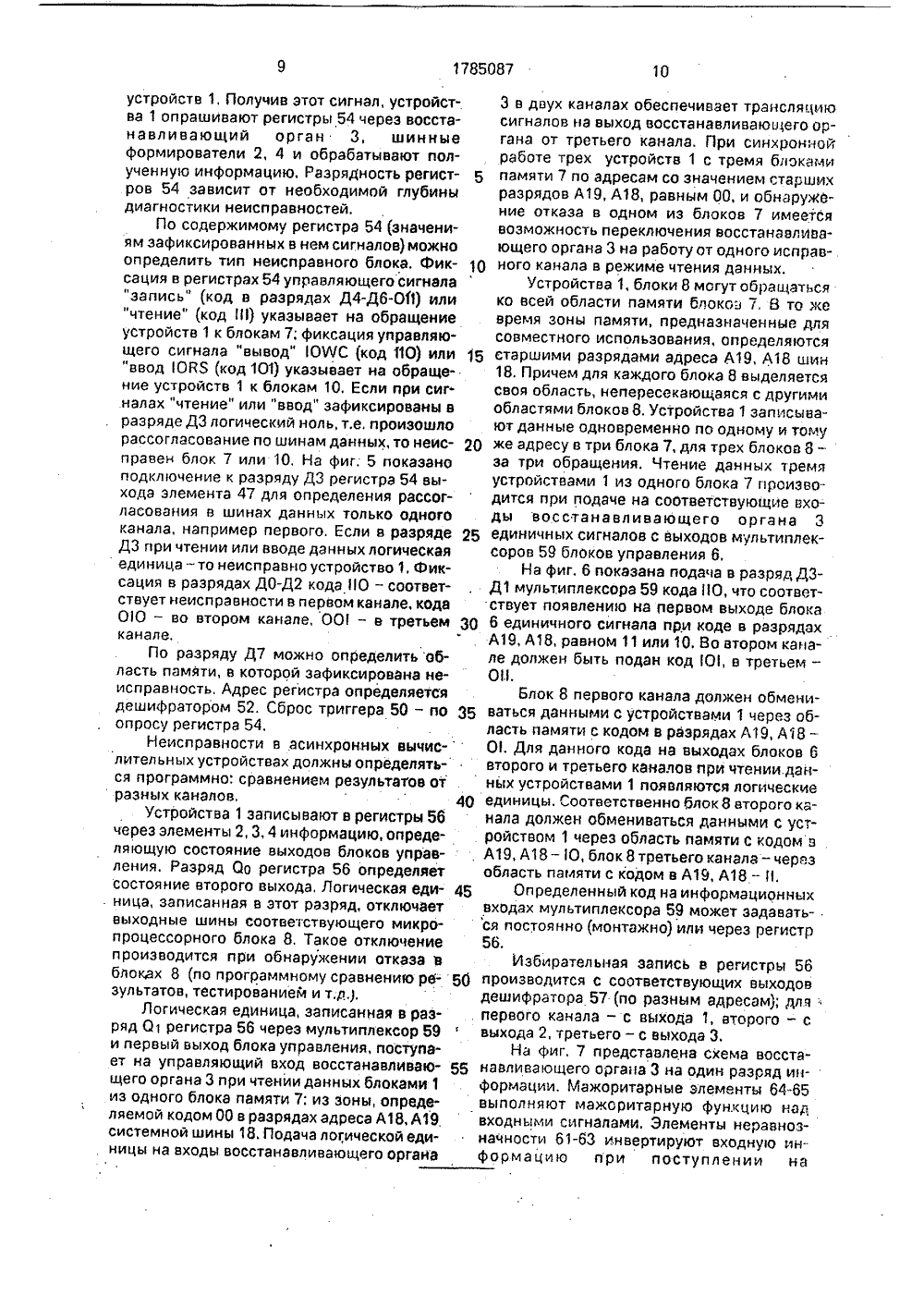

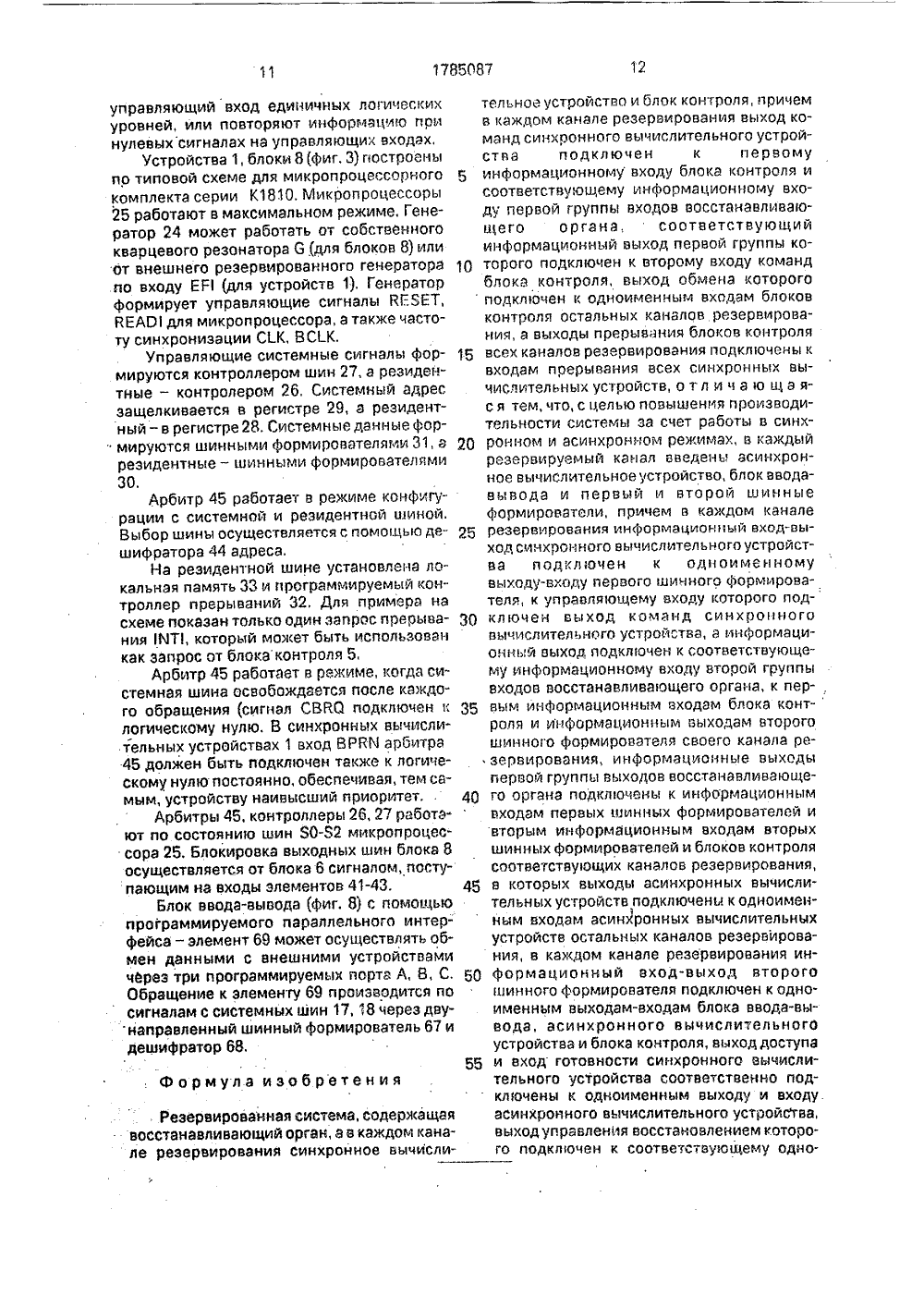

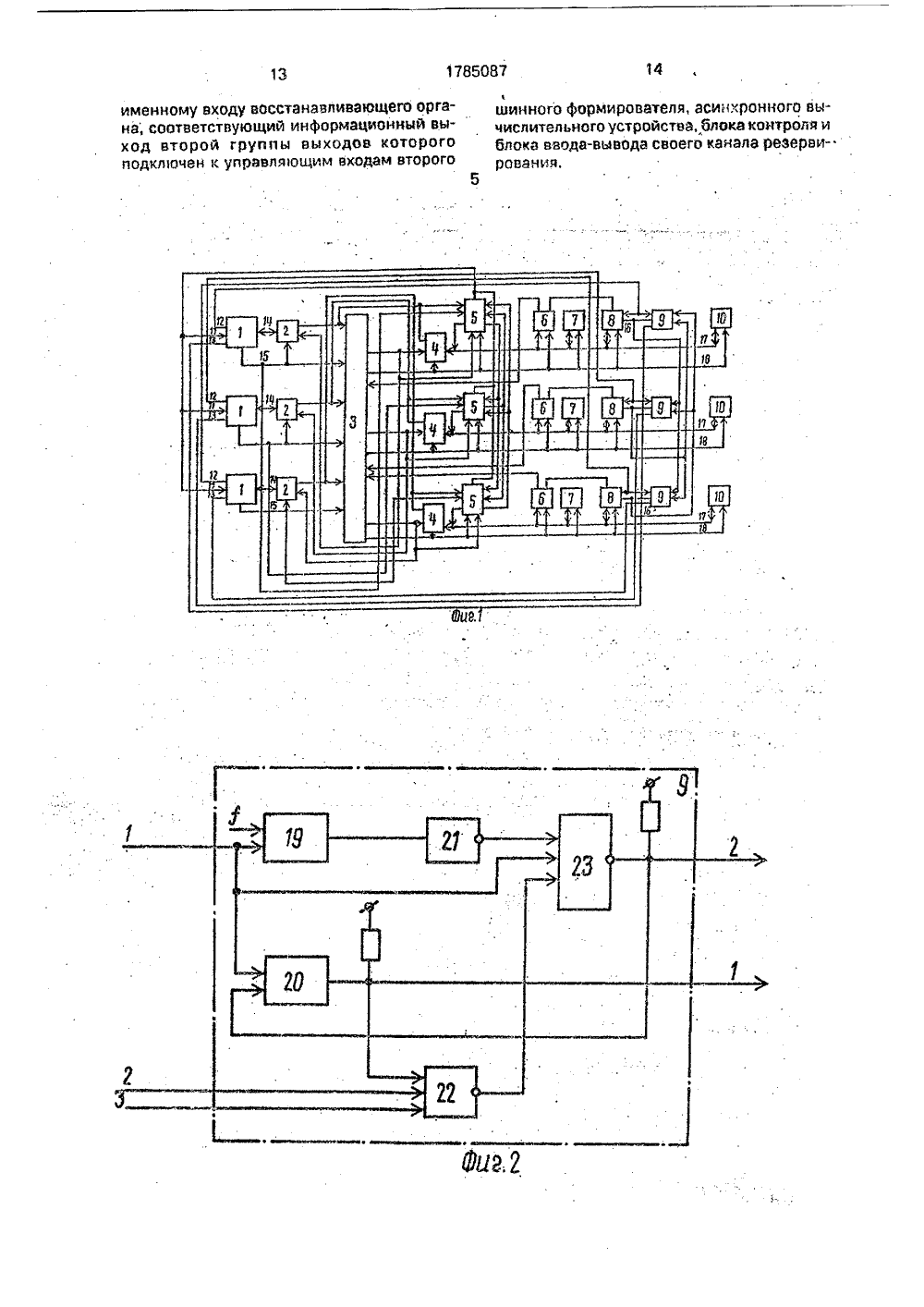

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 087 А 9 КСАН АВТО венныи комплекс ого научно-произия "Электронмаш" ство СССР/18, Н 05 К 10/00; ГОСУДАР СТ В Е ННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР(56) Авторское свидетельМ. 1309788, кл. О 06 Г 11Авторское свидетельМ 1101827, кл, 6 06 Г 111982,Авторское свидетельМ 1584137, кл, О 06 Е 111088,Изобретение относится к области вычислительной техники и может быть использовано при проектировании вычислительных систем и устройств повышенной надежности и производительности.Цель изобретения - повышение производительности системы за счет работы в синхронном и асинхронном режиме.На фиг. 1 показана функциональная схема резервированной системы, на фиг, 2 - блока разрешения приоритета; на фиг; 3 - вариант реализации блока микропроцессора; на фиг, 4 - схема арбитража; на фиг. 5 - вариант реализации блока контроля; на фиг, 6 - блока управления; на фиг. 7 - восстанавливающегооргана на 1 разрядинформации; на фиг. 8 - блока авода-вывода,Резервированная система (фиг. 1) состоит из трех каналов резервирования, в каждый из которых входят синхронное вычислительное устройство 1, первые 2 и вторые 4 шинные формирователи, блок контроля 5, блок ввода-вывода 10,асинхронное 11 Н 05 К 10/ОО, 6 06 Е 11/18(54) РЕЗЕРВИРОВАННАЯ СИСТЕМА (57) Сущность изобретения: система содержит три канала резервирования, в каждь 1 й из который входят одно синхронное вычислительное,устройство, два шинных формирователя, блок контроля, блок ввода-вывода. асинхронное вычислительное устройство, состоящее из блока управления, блока памяти, блока микропроцессора, блок разрешения приоритета, а также общий для канала резервирования восстанавливающий орган. 8 ил. вычислительное устройство, состоящее из блока управления 6, блока памяти 7, блока микропроцессора 8, блока разрешения приоритета 9, Система содержит также общий для резервируемых каналов восстанавливающий орган 3.На фиг. 1 обозначены: вход прерывания 11, выход доступа 12, вход готовности 13, информационный вход-выход 14, выход команд 15 синхронного вычислительного устройства 1, шина занятости 16, системная шина данных 17, системная вина адреса и ксманд 18Блок разрешения приоритета 9 - фиг, 2, состоит из счетчика 19, двухвходового элемента ИЛИ с открытым коллектором 20, инвертора 21, первого трехвходового элемента И-НЕ 22, второго трехвходового . элемента И-НЕ с открытым коллектором 23,Блок микропроцессора 8- фиг, 3, содержит генератор 24, микропроцессор 25, контроллеры шин 26, 27, регистры 28, 29 шинные формирователи 30, 31, программиктор М, Керецман Редактор Н. Егоро роизводственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина.аэ 1759ВНИИПИ Составитель В, Родин Текред М. Моргентал Тираж Подписноеарственного комитета по изобретениям и открытиям,при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5руемый контроллер прерываний 32, локэльнуа память 33, инвертсры 34-39, элемент с открытым коллектором 40, элементы И 41, И-НЕ 42,43, дешифратор 44, арбитр шин 45,На схеме арбитрахса - фиг, 4, показаны арбитры шин 45 вычислительных устройств и блоков микропроцессора 8 в подклочении к блоками разрешения приоритета 9 трех асинхронных вычислительных устройств,Блок контроля 5 - фиг. 5, состоит из схем сравнения 46, 47, элементов И-НЕ 48, 49, триггер 50, элемента НЕ с открытым коллектором 51, дешифратора 52, формирователя 53, регистр 54 с третьим состоянием, вход 55 "логическая единица",Блок управления 6 - фиг, 6, содержит; регистр 56, дешифратор 57, инвертор 58, мультиплексор 59, инвертср 60.Восстанавливающий орган 3 - флг, 7, построен на элементах неравнозначнссти 61-63 и мажоритарных элементах 64-66,Блок ввода-вывода 10 - флг, 8, состоит иэ двунаправленного шинного формирователя 67, дещифратора 68 и программируемого параллельного интерфейса 69,Синхронные вычислительные устоойства 1 могут бь 1 ть построень 1 по схеме микропроцессорных блоков 8, пОказэннсй нэ фиг. 3,На фиг, 1 выхсдь 1 прерывания блоков контроля 5 всех каналов резервирсвэния подклочены к в одам прерывания 11 всех синхронньх вычислительных устройств 1, Выход доступа 12 и вхсД ГотовнОсти 13 синхронного вычислительного устройства каждого канала резервированля подкл 1 счен к одноименным входу, выходу асинхронного вычислительного устройства (к одноименным входам, выходам блока разрешения приоритета 9, блока микропроцессора 8), Информационный вход-выход 14 устройства 1 соединен с одновременным выходом- входом первого шинного формирователя 2, представляет собой и-разрядную шину данных, Выход команд 15 устройства 1 подключен к управляющему входу первого ше 4- ного формирователя 2, информационным входом первой группы входов восстанавливающего органа 3, первым информационным входом блока контроля 5, на выходе команд 15 синхронным вьЧислительным устройством 1 формируется совокупность сигналов управления гп-разряднгого адреса, Выходом асинхронного вычислительного устройства в каждом канале является также шина занятости 16, к которой подключенывход разрешения доступа к шине арбитра 45 блока микропроцессора 8, вход элемент 22 и выход элемента 20 блока разрешения приоритета 9. Выход занятости шины асинхрон ного вцчлслительного устройства каждого канала резервирования подключен через соответствующую шину 16 к одноименнымвходам асинхронных Вь 1 числительных уст 5 ройств остальных каналов - к соответствуощим входам элементов 22 бЛоков 9 фиг, 4),Информационный вход-выход второго шинного фОрмирсвателя 4 ссеДинен с ОднО- именным выходом-входом блока ввода-вывода 10, асинхронного вычислительного устройства (блока управления 6, памяти 7, млкрспроцессоса 8) через системную шину данных 17, Информационныйвыход второй группы выходов Восстанавливающего органа 3 подклсче 14 к управляющим входам второго шинного формирователя 4, асинхссннОГО Вычислительного устройства - блоков управления 6,20 25 30 35 40 45 50 памяти 7, микропроцессора 8, блока контроля 5, блока ввода-вывода 10 через системнус шину и,-разрядного адреса и команд 18. выход упрэгления восстановлением устройства 1 (первый Выход блока 6) подключен к соответствующему Одноименному входу Восстанавливающего органа 3, вьход обмена блока контроля 5 (ст триггера 50) -к одноименнь м входам блоков контроля 5 остальных каналов резервирования, информа-. цисн 1 ый выход первой Группы ВыхОдОВ восстанавливающего органа 3 - к информэцнонньм входам первых шинных фсрмирователей 2 и вторьм информационнымвхслэм вторых шиннь х формирователей 4 и блоков контроля 3 соответствующих кана.лов резервирсва 41 ля.Сисгема работает следусщим образом, 1 ри синхрон 14 ьх вычислительных устрсйтяа 1 фи" 1 3) сбрабатываст данныепо одинаковым программам, хранимым в локэльнцх памятях 33 и или) блока 7 асинхронных вычислительных устройств, Синхрон н ы й обмен и н формацией между микропроцессорами 25 устройств 1 и блоками памяти 7 осуществляется через вссстанэвливасщий орган 3, который выполняет мажоритарную функцию с поступаощими нэ его входи сигналами,В режиме записи или чтения) данных в память (из памятл) шины адреса и команд 5 чеоез восстанавливаощий орган 3 подключаются к системным шинам 18 которые соединены с шинами адреса и команд блоков 7, При записи данных от микропроцессоров 25 устройства 1 через шины 14,щиннье Формирователи 2. восстанавливающий орган 3, шинные формирователи 4, системные щинц 17 поступйот на вход блоковпамяти 7, При чтении направление передачи данных - обратное. Управление переключением шинных формирователей2, 4осуществляется сигналами управления сшин 15, 18, Аналогично осуществляется синхронный обмен данными устройства 1 с блоками ввода-вывода 10,Синхронное вычислительное устройство 1 имеет воэможность также чтения данных только из одного блока памяти 7(в триканала), В этом случае при обращении поопределенному адресу памяти блоки управления 6 вырабатывают на своих первых выходах единичные сигналы, которыепоступают на соответствующие управляющие входы восстанавливающего органа 3.При подаче на управляющие входы восстанавливающего органа от двух блоков управления (в двух каналах) единичных сигналов,на его выходе появляется сигнал со входа, ккоторому подключен блок 7 третьего канала,Микропроцессорные блоки 8 асинхронных вычислительных устройств работают вкаждом канале асинхронно по собственнымпрограммам, хранимым также в своих локальных памятях 33 и (или) блоках 7, Причеммикропроцессор 25 блока 8 имеет возможность обращения в блок памяти 7 толькосвоего канала через шины 17, 18. Поэтомуотказ любого блока 8 выводит из строя только одну системную шину или область памяти в блоках 7. 30Распределение во времени общих ресурсов системы (шин 17, 18. блоков 7) осуществляется с помощью блоковразрешения приоритета 9 и арбитров 45(фиг, 1-4). Работа микропроцессоров вычислительных устройств с общей памятью -блоками 7, может быть организована известными способами для мультипроцессирования - через "семафор" или "почтовыйящик" (арбитраж - последовательный), 40Рассмотрим один из возможных вариантов мультипроцессорной обработки информации.Пусть задача состоит в сборе данных отдвух внешних устройств (трехканальных), 45обработке данных от каждого устройства поопределенному алгоритму в выдаче результатов на внешние устройства,Алгоритмы решения задачи могут бытьраспределены между микропроцессорами 50следующим образом,Микропроцессоры 25 устройств 1 осуществляют синхронно по трем каналам сбор данных от внешних устройств через блоки 10, обработку данных от одного из внешних устройств по первому алгоритму, размещение данных от второго внешнего устройства в блоки памяти 7 для блоков 8 первого и второго каналов,Обработку данных от второго внешнегоустройства производят микропроцессоры25 блоков по первому алгоритму. Результа-ты обработки блоки 8 размещают в определенные зоны памяти блоков 7. Синхронныеустройства 1 сравнивают результаты обра-,ботки данных по второму алгоритму и передают их в случае идентичности на внешнеустройства через блоки ввода-вывода 10.Результаты обработки данных по первомуалгоритму также выдаются синхроннымивычислительными устройствами 1 на внешние устройства,Микропроцессор 25 блока 8 третьего канала может находиться в резерве. В случаенесравнения результатов обработки в блоках 8 и определения канала с неисправныммикропроцессором операционная системадолжна произвести перераспределение задачи между блоками 8,Наибольшая производительность в системе может быть достигнута при решениизадач, для которых время обработки данных с использованием памяти значительно большевремени обращения микропроцессоров кобщим ресурсам.Обмен данными между микропроцессорами 25 синхронных и асинхронных вычислительных устройств может производитьсялибо с использованием специальных префиксов и команд для анализа признаков обновления информации в соответствующихячейках памяти, либо по запросам прерывания программ.Во втором случае устройства 1, разместивданные в блоках 7 для обработки, могутсформировать в каждый иэ блоков 8 запросы прерывания (например через программно доступный триггер - на фиг. 3 непоказано, По этим процессам блоки 8 всоответствующих программах обработкипрерываний выбирают необходимую информацию из блоков 7. Об окончании обработки блоки 8 могут также сообщитьустройствам 1 по соответствующим запросам.Координация доступа микропроцессоров к системным шинам осуществляетсяследующим образом (фиг. 1-4).Выход приоритетного разрешения доступак шине ВРВО арбитра 45 каждого устройства 1 (шина 12) соединен со входомприоритетного расширения доступа к шинеВРЯД арбитра 45 блока 8. Если микропроцессоры 25 устройств 1 не используют системную шину, арбитры 45 устройств 1синхронно передают приоритет арбитрам45 блоков 8 - нулевыми сигналами ВРРО, .Если устройства 1 захватывают шину, то навыходах ВРВО синхронно появляются единичные сигналы. (Вход приоритетного разрешения доступа к шине ВРОЙ устройств 1 ПОДКЛЮЧЕН ПОСтОяннО к лОгичЕСкОму нув, обеспечивая, тем самым, этим блокам наи-. высший приоритет). При захвате системной шины устройствами 1 или блоками 8 на соответствующих шинах занятости ВОЗУ появляются нулевые сигналы, которые снимаются после освобождения системной шины.В исодном сосоии; ОГда устройства 1 и блоки 8 не Обращаются к блокам памяти 7, на входах разрешения доступа к шине ВРЯД арбитров 45 устанавливаются нулевье уровни, размещающие обращение с системным шинам 17, 18, (Арбитры 45 работают в режиме, при котором шина освобождается после каждого к ней обращения; вход АКВОЯ - лог, "Г, СВВО -в лог, "О",),Сигналами В РВО, равным нулю, счетчики 19 блоков 9 приведены в исходное состояние (на выходе логический ноль), На шинах занятости ВОЗУ арбитров 45, на выходах элементов 20, 33 присутствуют сигналы логической единицы; указывающие, что системные шины свободны,Если первыми к системным шинам Обращаются микропроцессоры устройсгв 1, тона выходас ВРИО арбитров 45 одновременно в трех каналах появляются единичные сигналы, запрещающие блока 8 обращаться к шинам. Счетчики 19 блоков 9 начинают подсчет импульсов частоты т, которь 18 могут пОДаваться В блоки 9 От Отд 8 льных Генераторов или с шин ВСс.К микропроцессорных блОкОВ, КоэффициентДеления счетчиков выбирается таким, чтобы на их выходах появлялся единичный сигнал через Время, большее максимального времени обращения блоков 8 к системым шинам, Так как блоки 8 не обращались к шинам, на Выходе элемента 22 формируется нулевой сигнал, а элемента 23 - единичный, который поступает на вход ВОЯУ арбитров 45 устройств 1.По анализу единичного уровня сигнала по выходу ВОЯУ арбитры 45 Оазрешают усгрбйствам 1 обращение к системным шинам; Если системная шина была занята блоками В, то на выходе элемента 22 появится нулевой сигнал только после установки в единицу сигнала ВОЗУ арбитра 45 соответствующего блока 8 (шина 16),В случае отказа в любом из блоков 8,при кбтором на выходе элемента 22 присутствует постоянный единичный уровень, на входе ВОЗУ арбитров 45 устройств 1 появляется единичный сигнал С выхода элемента 23 только по окончании счета элементов 19.При таких отказах производительность системи будет снижена, так как устройства 1всегда Обращаться к системным шинам сзадерккой на время Вьработки единичнОГОсигнала счетчиком 19, Переустановка счет 5 чика 19 происходит по нулевому уровнюВРЯО после каждого обращения устройств1 к системным шинам,ВО Время захвата шин устройстВами 1соответствующие арбитры 45 вырабатывавот Нуяввие СИГНВЛЫ ЭаняТОСТИ - ВОЯУ 1 СОторые удерживаются до конца обращения,При ВРВО В устройствах 1 равном нулю(доснятия сигнала ВОЗУ), нулевой уровень через элемент 2 О подключается ко входу15 ВОЗУ арбитров 45 блоков 8, запрещая блоКам 8 Обращевние,Если при чулевом сигнале на ВходахВРРИ к системным шинам Обращаются блоки 8, то на выходе шины занятости ВОЯУ2 О блока 8 появляется нулеВОЙ уровень ДООкончания Обоащения, Этот сиГнал черезэлементы 22, 23 сообщает арбитрам 45 устройств 1 о занятости шины при переключении сигнала ВРИО арбитров 45 ус 1 ройств 125 В 8 Диницу,Обнарукение неисправностей В мажоритарнс-резервированных блскас системыОСУЩВСТВЛЯетсй анаЛОГИЧНО ПРОТОТИПУ С ПО-;мощью блоков контроля 5.3 б В блоках 5 (фиг, 5) о случае отсутствиянеисправностей триггер 50 установлен В нулевое состояние (по сигналу РЕЯЕТ), На элементах 46, 47 осущетвляется поразрядноесравненс 8 сигналов с шин данных, адрес",о г-в УПОВВЛ 8 НИЯ На ВЫХОД 8 ВОССТаНВВЛИВаЮЩЕГООрГана 3 с сигналами на шинах 15 и Выходахшинных фсрмирователей 2, 4, РассогласоВание сигналов запоминается в триггере 50,ВЫХОД КОТОРОГО ЧВРеэ ИНВ 8 РТОО С ОТКРЫТЫМф коллектором 51 подклочен на Выходы формирователей 53 всес каналов, вырабатывающих импульс записи В регистры 54.длительность импульса определяется ЯСЦегизчкой, В случа 8 Отключения неисправных каналов или работы трех устройсв 1 содним блоксм 7 (в режиме "чтения" ) с соотВетстВующих первых Выходов блоков 6 наВыходы элементов 49 должны подаватьсяединичные сигналы для блокиоовки тригге 5 О ра 50,В регистрах 54 Одновременно запоминается информация, характеризующая номер отказавшего канала и состояниемажоритарных шин, например; управляюЩих сиГналов (" записи" В память МКТС"чтения" из памяти МЯОС и др,), адреса,ДВННЫХ,Сигнал с объединенных Выходов элементов 51 поступает также на шину прерыВВЙия 11 синхронных вычислительных3 в двух каналах обеспечивает трансляцию сигналов на выход восстанавливающего органа от третьего канала, При синхронной работе трех устройств 1 с тремя блоками памяти 7 по адресам со значением старших разрядов А 19, А 18, равным 00, и обнаружвние отказа в одном из блоков 7 имеется возможность переключения восстанавливающего органа 3 на работу от одного исправного канала в режиме чтения данных.Устройства 1, блоки 8 могут обращаться ко всей области памяти блоков 7, В то же время зоны памяти, предназначенные для совместного использования, определяются старшими разрядами адреса А 19, А 18 шин 18. Причем для каждого блока 8 выделяется своя область, непересекающаяся с другими областями блоков 8, Устройства 1 записывают данные одновременно по одному и тому же адресу в три блока 7, для трех блоков 8 - за три обращения. Чтение данных тремя устройствами 1 из одного блока 7 производится при подаче на соответствующие входы восстанавливающего органа 3 единичных сигналов с выходов мультиплексоров 59 блоков управления 6.На фиг, 6 показана подача в разряд ДЗД 1 мультиплексора 59 кодаО, что соответствует появлению на первом выходе блока 6 единичного сигнала при коде в разрядах А 19, А 18, равном 11 или 10. Во втором канале должен быть подан код О, в третьем - О,Блок 8 первого канала должен обмениваться данными с устройствами 1 через область памяти с кодом в разрядах А 19, А 18 - О. Для данного кода на выходах блоков 6 второго и третьего каналов при чтении данных устройствами 1 появляются логические единицы. Соответственно блок 8 второго канала должен обмениваться данными с устройством 1 через область памяти с кодом в А 19, А 18 - О, блок 8 третьего канала - через область памяти с кодом в А 19, А 18 - .Определенный код на информационных входах мультиплексора 59 может задаваться постоянно монтажно) или через регистр 56.Избирательная запись в регистры 56 производится с соответствующих выходов дешифратора 57 (по разным адресам); для первого канала - с выхода 1, второго - с выхода 2, третьего - с выхода 3.На фиг, 7 представлена схема восстанавливающего органа 3 на один разряд информации. Мажоритарные элементы 64-65 выполняют мажоритарную функцию над входными сигналами. Элементы неравнозачности 61-63 инвертируют входную инормацию при поступлении на устройств 1, Получив этот сигнал, устройст-.ва 1 опрашивают регистры 54 через восстанавливающий орган 3, шинные формирователи 2, 4 и обрабатывают полученную информацию, РазряДность регист ров 54 зависит от необходимой глубины диагностики неисправностей.По содержимому регистра 54 (значениям зафиксированных в нем сигналов) можно определить тип неисправного блока. Фик сация в регистрах 54 управляющего сигнала "запись" (код в разрядах Д 4-Д 6-ОЙ) или "чтение" (код ) указывает на обращение устройств 1 к блокам 7; фиксация управляющего сигнала "вывод" ОУЧС код 110) или 15 "ввод 083 код 1 О 1) указывает на обращение устройств 1 к блокам 10, Если при сигналах "чтение" или "ввод" зафиксированы в разряде ДЗ логический ноль, т.е, произошло рассогласование по шинам данных, то неис правен блок 7 или 10, На фиг; 5 показано подключение к разряду ДЗ регистра 54 выхода элемента 47 для определения рассогласования в шинах данных только одного канала, например первого, Если в разряде 25 ДЗ при чтении или вводе данных логическая единица - то неисправно устройство 1. Фиксация в разрядах ДО-Д 2 кода О - соответствует неисправности в первом канале, кода ОО - во втором канале, ОО - в третьем 30 канале.По разряду Д 7 можно определить область памяти, в которой зафиксирована неисправность, Адрес регистра определяется дешифратором 52. Сброс триггера 50 - по 35 опросу регистра 54,Неисправности в асинхронных вычис-лительных устройствах должны определяться программно: сравнением результатов от разных каналов, 40Устройства 1 записывают в регистры 56 через элементы 2, 3, 4 информацию, определяющую состояние выходов блоков управления. Разряд О 0 регистра 56 определяет состояние второго выхода. Логическая еди . ница, записанная в этот разряд, отключает выходные шины соответствующего микропроцессорного блока 8, Такое отключение производится при обнаружении отказа в блоках 8 (по программному сравнению ре зультатов, тестированием и т;д,).Логическая единица, записанная в разряд 01 регистра 56 через мультиплексор 59 и первый выход блока управления, поступает на управляющий вход восстанавливаю щего органа 3 при чтении данных блоками 1 из одного блока памяти 7: из эоны, определяемой кодом 00 в разрядах адреса А 18, А 19 системной шины 18. Подача логической еди- н ницы на входы восстанавливающего органа фуправляющий вход единичных логическихуровней, или повторяют информацию поинулевыхсигналах на управляющих входах,Устройства 1, блоки 8 фиг, 3) построеныпо типовой схеме для микропроцессорногокомплекта серии К 1810. Микропроцессоры25 работают в максимальном режиме. Генератор 24 может работать от собственногокварцевого резонатора 8 (для блоков 8) илиОт внешнего резервированного генераторапо входу ЕЕ (для устройств 1). Генераторформирует управляющие сигналы ЕЕЯЕТ,РЕАО для микропроцессора, а также частоту синхронизации С К, ВС К.Управляющие системные сигналы формируются контроллером шин 27, а резидентные - контролером 26, Системный адресзащелкивается в регистре 29, а резидентный - в регистре 28. Системные данные фор" мируются шинными формирователями 31, арезидентные - шинными формирователями30.Арбитр 45 работает в режиме конфигурации с системной и резидентной шиной,Выбор шины осуществляется с помощью дешифратора 44 адреса,На резидентной шине установлена локальная память 33 и программируемый контроллер прерываний 32, Для примера насхеме показан только один запрос прерывания 1 ЙТ, который может быть использованкак запрос от блока контроля 5,Арбитр 45 работает в режиме, когда системная шина освобождается после каждого обращения (сигнал СВКО подключен клогическому нулю. В синхронных вычислительных устройствах 1 вход ВРЯД арбитра45 должен быть подключен также к логическому нулю постоянно, обеспечивал, тем самым, устройству наивысший приоритетАрбитры 45, контроллеры 26, 27 работа"ют по состоянию шин 80-82 микропроцессора 25. Блокировка выходных шин блока 8осуществляется от блока 6 сигналом, поступающим на входы элементов 41-43,Блок ввода-вывода (фиг. 8) с помощьюпрограммируемого параллельного интерфейса - элемент 69 может осуществлять обмен данными с внешними устройствамичерез три программируемых порта А, В, С,Обращение к элементу 69 производится посигналам с системных шин 17, 18 через двунаправленный шинный формирователь 67 идешиФратор 68.Формула изобретенияРезервированная синема, содержащаявосстанавливающий орган, а в каждом канале резервирования синхронное вычислительное устройство и блок контроля, причем в каждом канале резервирования выход команд синхронного вычислительного устройства подключен к первому информационному входу блока контроля и соответствующему информационному входу первой группы входов восстанавливающего органа., соответствующий информационный выход первой группы ко торого подключен к второму входу командблока контроля, выход обмена которого подключен к одноименным входам блоков контроля остальных каналов резервирования, а выходы прерывания блоков контроля всех каналов резеовирования подключены к входам поерывания всех синхронных вычислительных устройств, о т л и ч а ю щ а яс я тем, что, с целью повь 1 шения производительности системы за счет работы в синх ронном и асинхронном режимах, в каждыйрезервируемый канал введены асинхронное вычислительноеустройство, блок ввода- вывода и первый и второй шинные формирователи, причем в каждом канале 25 резервирования информационный вход-выход сичхронного вычислительного устройства подключен к Одноименному выходу-входу первого шинного формирователя, к управляощему ВхОду которОго под ключен Выход команд синхронноговычислительного устройства, а информационный выход подключен к соответствующему информационному входу второй группы входов восстанавливающего органа, к пер-, 35 вым информационным входам блока конт-роля и информационным выходам второго шинного формирователя своего канала резервирования, информационные выходы первой группы выходов восстанавливающе го органа подключены к информационнымвходам первых шинных формирователей и вторым информационным входам вторых шинных формирователей и блоков контроля соответствующих каналов резервирования, 45 в которых выходы асинхронных вычислительных устройств подключены к одноименным входам асинхронных вычислительных устройств остальных каналов резервирования, в каждом канале резервирования ин ФОрмационный ВхОд-ВыхОд второгошинного формирователя подключен к одноименным выходам-входам блока ввода-вывода, асинхронного вычислительного устройства и блока контроля, выход доступа 55 и вход готовности синхронного вычислительного устройства соответственно под ключены к одноименным выходу и входуасинхронного вычислительного устройства, выход управления восстановлением которого подклочен к соответствующему одноименному входу восстанавливающего органа, соответствующий информационный выход второй группы выходов которого подкл 1 очен к управляющим входам второго шинного Формирователя, асинхронного вычислительногоустройства, блокаконтроля и блока ввода-вывода своего канала резервирования,51785087 Мтсдю ЭВР"фЯем яямоБ ЬМИ ФЦФЙ с

СмотретьЗаявка

4797328, 28.02.1990

НАУЧНО-ПРОИЗВОДСТВЕННЫЙ КОМПЛЕКС "СИСТЕМА" ЛЕНИНГРАДСКОГО НАУЧНО-ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "ЭЛЕКТРОНМАШ"

РОДИН ВАЛЕРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/18, H05K 10/00

Метки: резервированная

Опубликовано: 30.12.1992

Код ссылки

<a href="https://patents.su/10-1785087-rezervirovannaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Резервированная система</a>