Декодер сверточного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1660178

Автор: Савчук

Текст

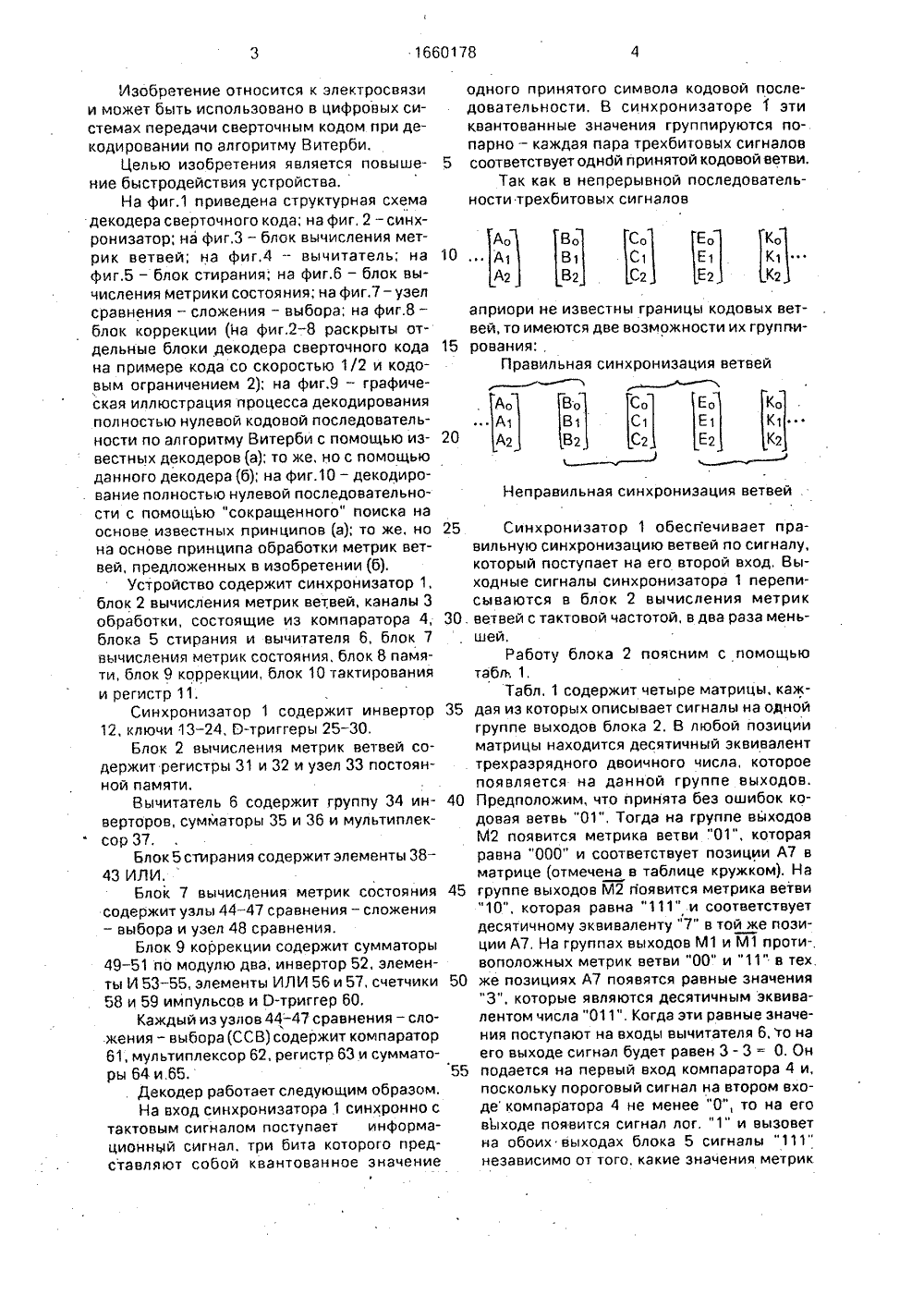

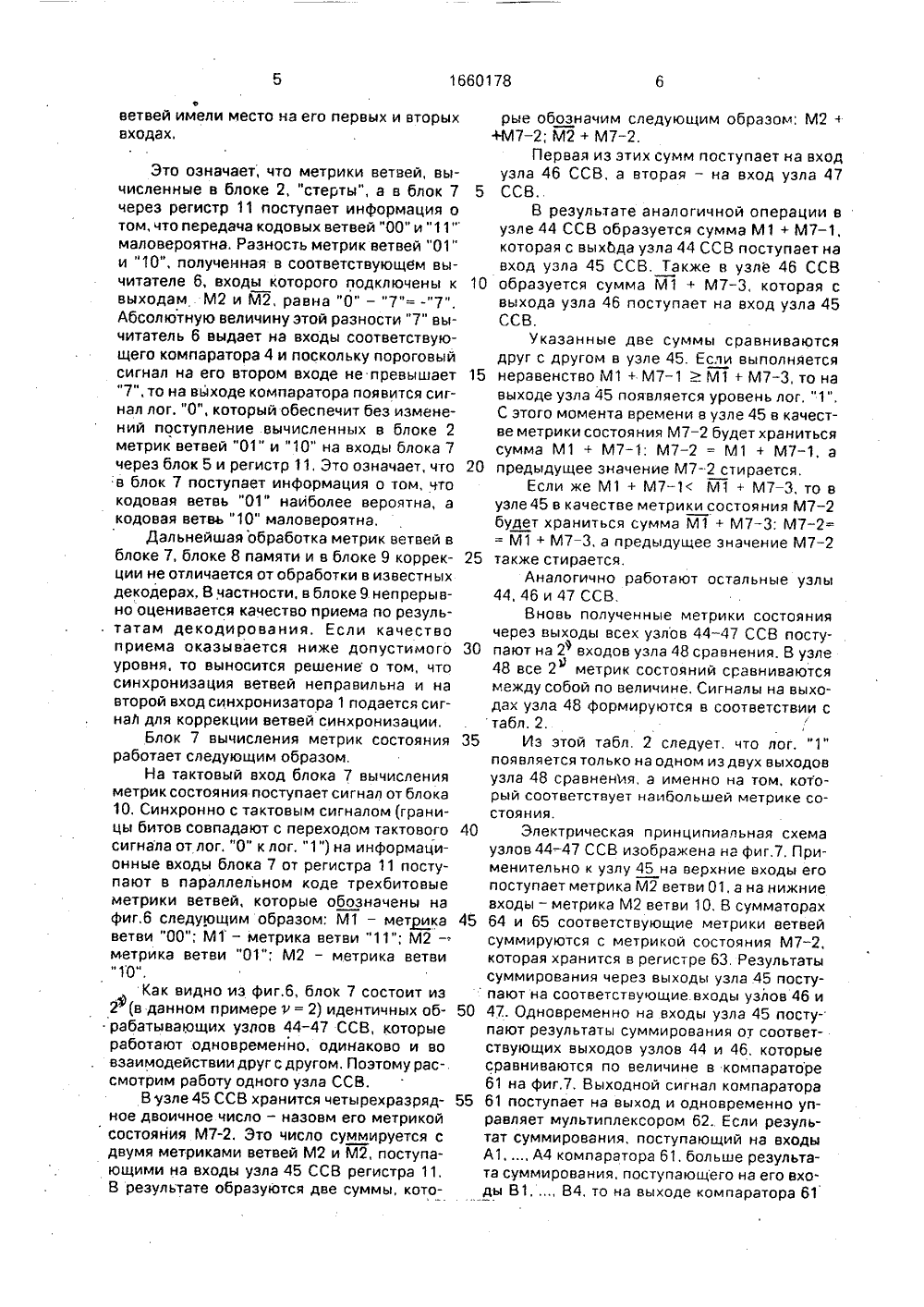

(5)5 Н 03 М 1 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТПРИ ГКНТ СССР Ф ИСАНИЕ И 306 РЕТЕНИЯ(57) Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи сверточным кодом при декодировании по алгоритму Витерби. Целью изобретения является повышение быстродействия устройства. Устройство содержит синхронизатор 1, блок 2 вычисления метрик ветвей, каналы 3 обработки. состоящие из компаратора 4, блок 5 стирания и вычитателя 6, блок 7 вычисления метрик состояния, блок 8 памяти, блок 9 коррекции, блок 10 тактирования и регистр 11, 10 ил 2 табл.) фЧ Ъь Ъс у С ТСоставитель О.Тюринаедактор Е.Копча Техред М,Моргентал КоРРектоР Т,Пали Заказ 1855 Тираж 466 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС113035, Москва, Ж, Рауйская наб 4/5изводственно-издательский комбинат "Патент". г. Ужгород, ул.Гагарина, 101660178 одного принятого символа кодовой последовательности. В синхронизаторе 1 эти квантованные значения группируются попарно - каждая пара трехбитовых сигналов 5 соответствует однбй принятой кодовой ветви.Так как в непрерывной последовательности трехбитовых сигналов ронизатор; на фиг,З - блок вычисления метрик ветвей; на фиг,4 - вычитатель; на 10,.фиг.5 - блок стирания; на фиг.6 - блок вычисления Метрики состояния; на фиг.7 - узелсравнения - сложения - выбора; на фиг.8 -блок коррекции (на фиг,2 - 8 раскрыты отдельные блоки декодера сверточного кода 15на примере кода со скоростью 1/2 и кодовым ограничением 2); на фиг.9 - графичеК 1 К 2 е известны границы ются две возможнос априори нвей, то имрования;Прави довых ветих группицесса декодированиядоной последовательтерби с помощью изто же, но с помощью ская иллюстрация прполностью нулевой кости по алгоритмувестных декодеров ( а),кодера (б); на фиг.10 - декодироностью нулевой последовательноощью "сокращенного" поиска навестных принципов (а); то же, но 2принципа обработки метрик ветоженных в изобретении (б),иство содержит синхронизатор 1,исления метрик ветвей, каналы 3, состоящие из компаратора 4, 3тирания и вычитателя 6, блок 7я метрик состояния, блок 8 памякоррекции, блок 10 тактирования11.онизатор 1 содержит инвертор 313-24, О-триггеры 25-30.2 вычисления метрик ветвей согистры 31 и 32 и узел 33 постоянданного д вание пол сти с пом основе из на основе вей, предлУстро блок 2 выч обработки блока 5 с вычислен ти, блок 9 етвей . Синхрониза 1 обеспечивает правильную синхро ию ветвей по сигналу, который поступа а его второй вход, Выходные сигналы ронизатора 1 переписываются в бл вычисления метрик ветвей с тактовой частотой, в два раза меньшей.Работу блока 2 поясним с помощью табл, 1,Табл. 1 содержит четыре матрицы, каждая из которых описывает сигналы на одной группе выходов блока 2, В любой позиции матрицы находится десятичный эквивалент трехразрядного двоичного числа, которое появляется на данной группе выходов. Предположим, что принята без ошибок кодовая ветвь "01", Тогда на группе выходов М 2 появится метрика ветви "01", которая равна "000" и соответствует позиции А 7 в матрице (отмечена в таблице кружком). На группе выходов М 2 появится метрика ветви "10", которая равна "111" и соответствует десятичному эквиваленту "7" в тои же позиции А 7, На группах выходов М 1 и М 1 противоположных метрик ветви "00" и "11" в тех же позициях А 7 появятся равные значения "3", которые являются десятичным эквивалентом числа "011". Когда эти равные значения поступают на входы вычитателя 6, то на его выходе сигнал будет равен 3 - 3 - О, Он подается на первый вход компаратора 4 и, поскольку пороговый сигнал на втором входе компаратора 4 не менее "0", то на его восходе появится сигнал лог. "1" и вызовет на обоих выходах блока 5 сигналы "111" независимо от того, какие значения метрик торнизацет н синхок 2 и регистр Синхр 12, ключи Блок держит ре ной памят Вычи верторов сор 37, и.атель 6 содержитсумматоры 35 и 3 уппу 34 инмультиплексодержит элементы 385 сгира 45 5 дэом. нно с орма- пред- чение Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи сверточным кодом при декодировании по алгоритму Витерби.Целью изобретения является повышение быстродействия устройства.На фиг.1 приведена структурная схема декодера сверточного кода; на фиг. 2 - синх 43 ИЛИ.Блок 7 вычисления метрик состояния содержит узлы 44 - 47 сравнения - сложения - выбора и узел 48 сравнения.Блок 9 коррекции содержит сумматоры 49 - 51 по модулю два, инвертор 52, элементы И 53 - 55, элементы ИЛИ 56 и 57, счетчики 58 и 59 импульсов и О-триггер 60.Каждый из узлов 44 - 47 сравнения - сложения - выбора (ССВ) содержит компаратор 61, мультиплексор 62, регистр 63 и сумматоры 64 и.65,, Декодер работает следующим обрНа вход синхронизатора 1 синхро тактовым сигналом поступает инф ционный сигнал, три бита которого ставляют собой квантованное зна ьная синхронизация ветвей еправильная синхронизация вветвей имели место на его первых и вторыхвходах. 10 20 25 30 35 40 45 50 55 Это означает, что метрики ветвей, вычисленные в блоке 2, "стерты", а в блок 7через регистр 11 поступает информация отом, что передача кодовых ветвей "00" и "11"маловероятна, Разность метрик ветвей "01"и "10", полученная в соответствующем вычитателе 6, входы которого подключены квыходам . М 2 и М 2, равна "0" - "7"= -"7".Абсолютную величину этой разности "7" вычитатель 6 выдает на входы соответствующего компаратора 4 и поскольку пороговыйсигнал на его втором входе не превышает"7", то на выходе компаратора появится сигнал лог. "О", который обеспечит без изменений поступление вычисленных в блоке 2метрик ветвей "01" и "10" на входы блока 7через блок 5 и регистр 11, Это означает, что:в блок 7 поступает информация о том, чтокодовая ветвь "01" наиболее вероятна, акодовая ветвь "10" маловероятна,Дальнейшая обработка метрик ветвей вблоке 7, блоке 8 памяти и в блоке 9 коррекции не отличается от обработки в известныхдекодерах. В,частности, в блоке 9 непрерывно оценивается качество приема по резуль, татам декодирования. Если качествоприема оказывается ниже допустимогоуровня, то выносится решение о том, чтосинхронизация ветвей неправильна и навторой вход синхронизатора 1 подается сигнал для коррекции ветвей синхронизации.Блок 7 вычисления метрик состоянияработает следующим образом,На тактовый вход блока 7 вычисленияметрик состояния поступает сигнал от блока10. Синхронно с тактовым сигналом (границы битов совпадают с переходом тактовогосигнала от лог. "0" к лог. "1") на информационные входы блока 7 от регистра 11 поступают в параллельном коде трехбитовыеметрики ветвей, которые обозначены нафиг,6 следующим образом: М 1 - метоикаветви "00"; М 1 - метрика ветви "11"; М 2 -метрика ветви "01"; М 2 - метрика ветви"10".Как видно из фиг.6, блок 7 состоит из2 (в данном примере= 2) идентичных обрабатывающих узлов 44-47 ССВ, которыеработают одновременно, одинаково и вовзаимодействии друг с другом. Поэтому рас-.смотрим работу одного узла ССВ.В узле 45 ССВ хранится четырехразрядное двоичное число - назовм его метрикойсостояния М 7-2. Это число суммируется сдвумя метриками ветвей М 2 и М 2, поступающими на входы узла 45 ССВ регистра 11.В результате образуются две суммы, которые обозначим следующим образом; М 2+М 7 - 2; М 2 + М 7-2.Первая из этих сумм поступает на вход узла 46 ССВ, а вторая - на вход узла 47 ССВ.В результате аналогичной операции в узле 44 ССВ образуется сумма М 1 + М 7 - 1, которая с выхода узла 44 ССВ поступает на вход узла 45 ССВ, Также в узле 46 ССВобразуется сумма М 1 + М 7-3, которая свыхода узла 46 поступает на вход узла 45 ССВ,указанные две суммы сравниваются друг с другом в узле 45. Если выполняется неравенство М 1+ М 7-1М 1 + М 7-3, то навыходе узла 45 появляется уровень лог, "1". С этого момента времени в узле 45 в качестве метрики состояния М 7 - 2 будет храниться сумма М 1 + М 7-1: М 7-2 = М 1 + М 7-1, а предыдущее значение М 7-2 стирается.Если же М 1 + М 7-1 М 1 + М 7 - 3, то в узле 45 в качестве метрики состояния М 7 - 2 будет храниться сумма М 1 + М 7 - 3: М 7 - 2= = М 1+ М 7 - 3, а предыдущее значение М 7-2 также стирается.Аналогично работают остальные узлы 44, 46 и 47 ССВ.Вновь полученные метрики состояния через выходы всех узлов 44 - 47 ССВ поступают на 2 ф входов узла 48 сравнения. В узле 48 все 2" метрик состояний сравниваются между собой по величине, Сигналы на выходах узла 48 формируются в соответствии с табл. 2.Из этой табл. 2 следует, что лог, "1" появляется только на одном из двух выходов узла 48 сравненИя, а именно на том, который соответствует наибольшей метрике состояния.Электрическая принципиальная схема узлов 44 - 47 ССВ изображена на фиг,7, Применительно к узлу 45 на верхние входы его поступает метрика М 2 ветви 01, а на нижние входы - метрика М 2 ветви 10. В сумматорах 64 и 65 соответствующие метрики ветвей суммируются с метрикой состояния М 7 - 2, которая хранится в регистре 63, Результаты суммирования через выходы узла 45 поступают на соответствующие входы узлов 46 и 47 Одновременно на входы узла 45 поступают результаты суммирования от соответствующих выходов узлов 44 и 46, которые сравниваются по величине в компараторе 61 на фиг.7. Выходной сигнал компаратора 61 поступает на выход и одновременно управляет мультиплексором 62, Если реэультат суммирования, поступающий на входыА 1, , А 4 компаратора 61, больше результата суммирования, поступающего на его входы В 1, В 4, то на выходе компаратора 6110 15 20 25 ЗО 35 40 45 50 55 имеет место лог. "1", В противном случаепоявляется лог, "О",В том случае, если на входе А/В мультиплексора 62 появляется лог. "1", то на еговыходы проходит четырехразрядный сигналчерез входы узла 45 ССВ, Если же на входеА/В мультиплексора 62 появляется лог, "0",то на его выходы проходит четырехразрядный сигнал через третьи выходы 4.Выходы мультиплексора 62 подключены к входам регистра 63, поэтому при изменении тактового сигнала на входе от лог, "0"к лог. "1" выходной сигнал мультиплексора62 записывается в регистр 63 в качественовой метрики состояния М 7 - 2. Далее описанный цикл повторяется,Вычитатель работает следующим образом.Пусть необходимо вычислить разностьдвух чисел; умен ьшаемое М 1 = 1(10) = 001 (2);вычитаемое М 1 = 7(10) = 111 (2).Тогда в сумматоре 35 выполняются следующие операции.Сигналы на входах АЗ, А 2, А 1, АО: 0001,Сигналы на входах ВЗ, В 2, В 1, ВО; 1000,Сигналы на входе РО:, 1,Сигналы на выходах 53, 32, Я 1, 30: 1010,В сумматоре 36 выполняются следующие операции,Сигналы на входах А 2, А 1, АО: 010,Сигналы на входах В 2, В 1, ВО; 111.Сигнал на выходах Г 2, Г 1, ЯО: 110.Сигнал 3 с выхода сумматора 35 воздействует на управляющий вход АВ мультиплексора 37 так, что при ЯЗ = 1 на его выходыпроходят сигналы 110 (2) = б (10), что, очевидно, является модулем разности двух чисел 1и 7,В случае, когда уменьшаемое большевычитаемого, то на выходе ЯЗ сумматора 35имеет место сигнал 53 = О, который воздей ствует на управляющий вход АВ мультиплексора 37 так, что на его выходы проходятсигналы Я 2, Я 1, 50 с выходов сумматора 35.Они представляют собой положительноечисло, которое является само по себе модулем разности.Для сравнительной оценки традиционного и предложенного принципов обработки метрик ветвей сделан прямой расчетпроцесса декодирования сверточного кодапри работе в двоичномсимметричном кана:ле с вероятностью ошибки 001. Результатыпредставлены в виде "решетчатой диаграммы" на фиг.9 процесса декодирования.Предполагалось, что при передаче полностью нулевой кодовой последовательности четвертая и пятая кодовые ветвиприняты с ошибками, как показано на фиг,9,где номер принятой коровой ветви совпада ет с номером шага декодирования. Из фиг,9 а, на которой графически изображен процесс декодирования на основе традиционной обработки метрик ветвей, видно, что две ошибочно принятые кодовые ветви на 4-и и 5-м шагах декодирования вызвали ошибочное событие на 4-м-м шагах декодирования, которое заключается в том, что декодированная. последовательность не совпадает с переданной (полностью нулевой последовательностью).Полужирными линиями выделены кодовые последовательности, хранящиеся в блоке 8 памяти. Помехоустойчивость декодирования тем выше, чем лучше совпадают друг с другом эти последовательности Как видно иэ фиг 9 а, вплоть до 24-го, шага декодирования, в памяти декодера хранятся три последовательности, которые расходятся друг с другом на 4-м и 8-м шагах декодирования, Следовательно, на 24-м шаге декодирования еще нельзя утверждать, что, начиная с 10-го шага декодирования, событие будет правильным, поскольку на 10-м шаге декодирования с правильной последовательностью совпадает лишь одна из тех, что хранится в памяти декодера Как видно из фиг.9 б, предложенный принцип обработки метрик ветвей приводит к значительно лучшему результату. При точно такой же ошибке в канале (4-я и 5-я ветви приняты как "11", хотя передавалась полностью нулевая последовательность) ошибочного события вообще не происходит, а, начиная с 9-го шага декодироваюия,все последовательности, которые хранятся в памяти декодера (они также выделены полужирными линиями) слились в одну правильную последовательность в ветвях 1-9. Это означает, что на 9-м шаге декодирования можно с уверенностью сказать. что эти ветви приняты правильно. В этом конкретном примере задержка декодирования, равная 14 -.3 =- 11 шагам, оказывается достаточной для исправления ошибки вканале. В то же время при традиционной обработке задержка кодирования, равна 24- 3 = 21 шагу недостаточна для надежного декодирования.Еще более значительный эффект дает предлагаемый принцип обработки метрик ветвей в случае процедуры "сокращенного поиска",основанного на алгоритме Витерби.Пример расчета для сокращенного поиска показан на фиг.10 при тех же условиях в канале передачи. Расчет показывает, что при сокращении количества вычислений в процессоре декодера в 2 раза традиционный принцип обработки ветвей может при1 О 1660178 Таблица 1 2 3 3." 2 1 0 О О 0 0 3 3 3 4 5 б 7 0 0 0 О 0 1 2 3 3 2 1 О 0 О О 0 3 2 1 О 0 О 0 О 3 2 1 0 0 О 0 0 0 0 О 0 0 1 2 3. 2 2 2 2 3 4 5 б б 5 4 3 2 2 2 2 4 3 2 0 О О а 5 4 3 2 1 1 1 1 0 0 0 0 0 1 2 3 А Б Г Д Ж 3 0 0 0 0 0 2 3 0 0 0 . 01 2 3 4 1 1 1 2 3 4 5 7 б 5 4 3 3 3 3 А Б В Г Д Е Ж 3 А Б В Г Д Е Ж 3 7 б 5 4 3 3 3 3 б 5 . 4 3 2 2 2 2 0 0 0 О О 1 2 3 3 2 1 0 0 0 0 0 0 0 0 0 0 1 2 3 3 2 1 0 0 О 0 0 0 0 0 0 1 2 3 4 0 0 0 0 0 2 3 0 0 0 0 0 1 2.3 3 2 1 О 0 0 О 0 5 4 3 2 1 1 1 1 А " Б В Г Д Е Ж 3 4 3 2 1 0 О а О 2 1 О 0 0 О О вести к так называемой "катастрофической ошибке". Как видно из фиг,10 а, она заключается в том, что ошибочное событие не заканчивается на конечной задержке кодирования: в памяти декодера не хранится ни одной декодированной последовательности, совпадающей с полностью нулевой переданной кодовой последовательностью.Если в такой "сокращенной" процедуре декодирования использовать предложенный принцип обработки метрик ветвей, то, как показано на фиг,10 б, после ошибочного события, начиная с 8-го шага декодирования, декодер начинает правильно декодировать полностью нулевую последовательность. Формула изобретения Декодер сверточного кода, содержащий синхронизатор, первый вход которого является входом декодера, и групп выходов синхронизатора (где и - число кодовых символов, образующих одну кодовую ветвь) подключены к соответствующим входам блока вычисления метрик ветвей, блок вычисления метрики состояния, выходы которого подключены к соответствующим входам блока памяти, выходы которого подключены к соОтветствующим входам блока Метрика М 1 ветви "00" Метрика М 2 ветви "01" коррекции, первый и второй выходы которого подключены соответственно к выходу декодера и второму входу синхронизатора, третий вход которого подключен к первому 5 выходу блока тактирования, второй выход которого подключен к вторым входам блока вычисления метрик ветвей, блока вычисления метрик соетояния, блока памяти и блока коррекции, о т л и ч а ю щ и й с я .тем, что, с10 целью повышения быстродействия, в него введены регистр и 2" каналов обработки, каждый из которых содержит вычитатель, компаратор и блок стирания, первые и вторые входы вычитателя и блока стирания15 каждого канала обработки попарно объединены и подключены соответственно к выходам метрик противоположных ветвей блока вычисления метрик ветвей, выходы вычитателя подключены к первым входам компара 20 тора своего канала обработки, выход компаратора подключен к третьему входу блока стирания того же канала обработки, выходы блоков стирания всех каналов подключены к соответствующим информацион 25 ным входам регистра, тактовый вход которого подключен к второму выходу блока тактирования. вторые входы компараторов подключены ксоответствующим входам задания порога,30 Метрика М 1 ветви "11" Метрика М 2 ветви "10"Фиг. 8 0 Ю Сойю О 0 4 р у 1 г 1 з и Фиг г ПРа 6 ильнаи l(йЫаЯ 0- О слоаВа- Оаи тельачюн рпРильноя к

СмотретьЗаявка

4626945, 26.12.1988

ПРЕДПРИЯТИЕ ПЯ А-1221

САВЧУК АЛЕКСАНДР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H03M 13/23

Метки: декодер, кода, сверточного

Опубликовано: 30.06.1991

Код ссылки

<a href="https://patents.su/10-1660178-dekoder-svertochnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Декодер сверточного кода</a>

Предыдущий патент: Преобразователь двоичного кода в трехпозиционный код

Следующий патент: Устройство компенсации помех, принимаемых по боковым лепесткам диаграммы направленности основной антенны

Случайный патент: Многослойное покрытие дорог и аэродромов