Устройство для контроля управляющих сигналов микропроцессора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

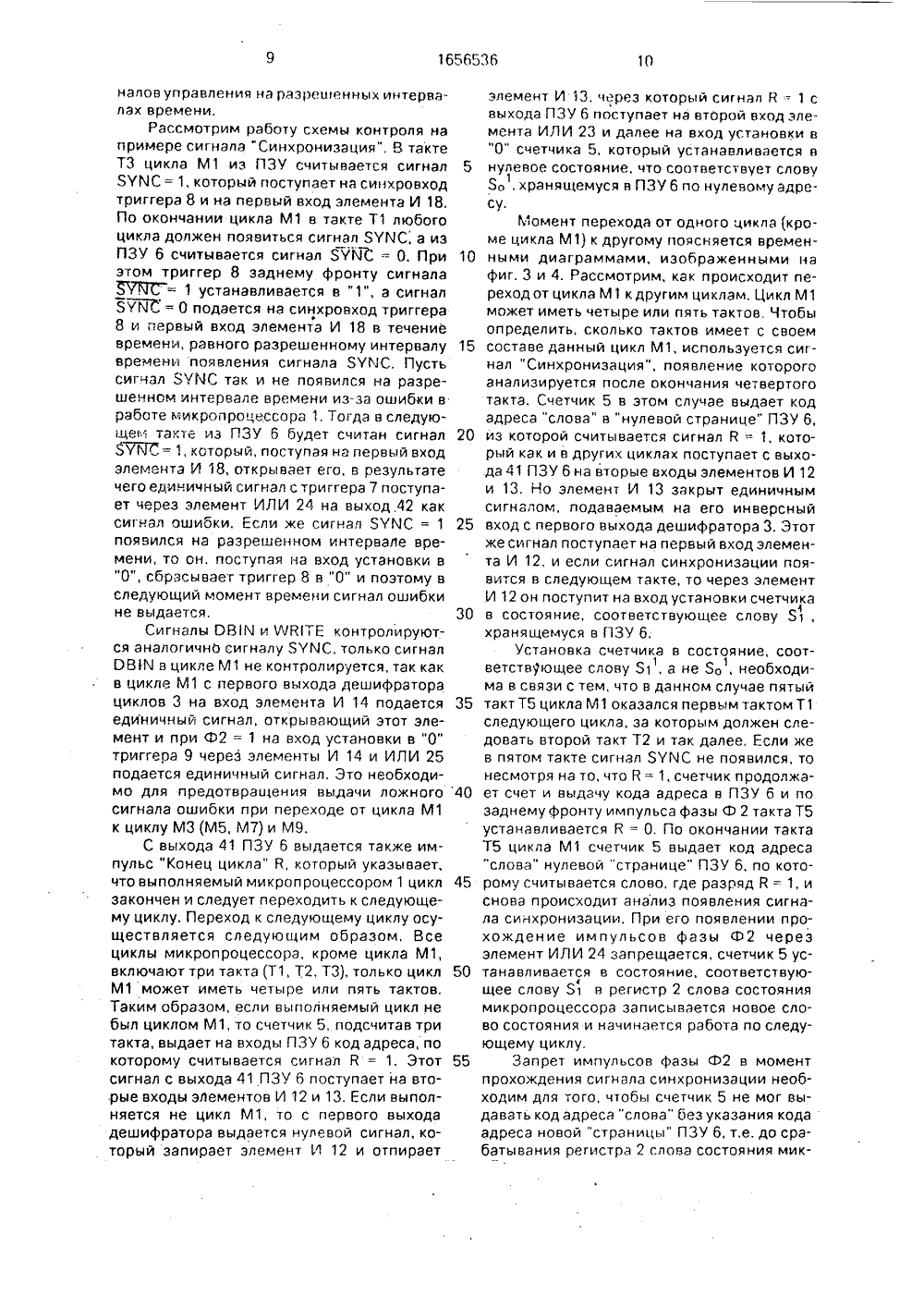

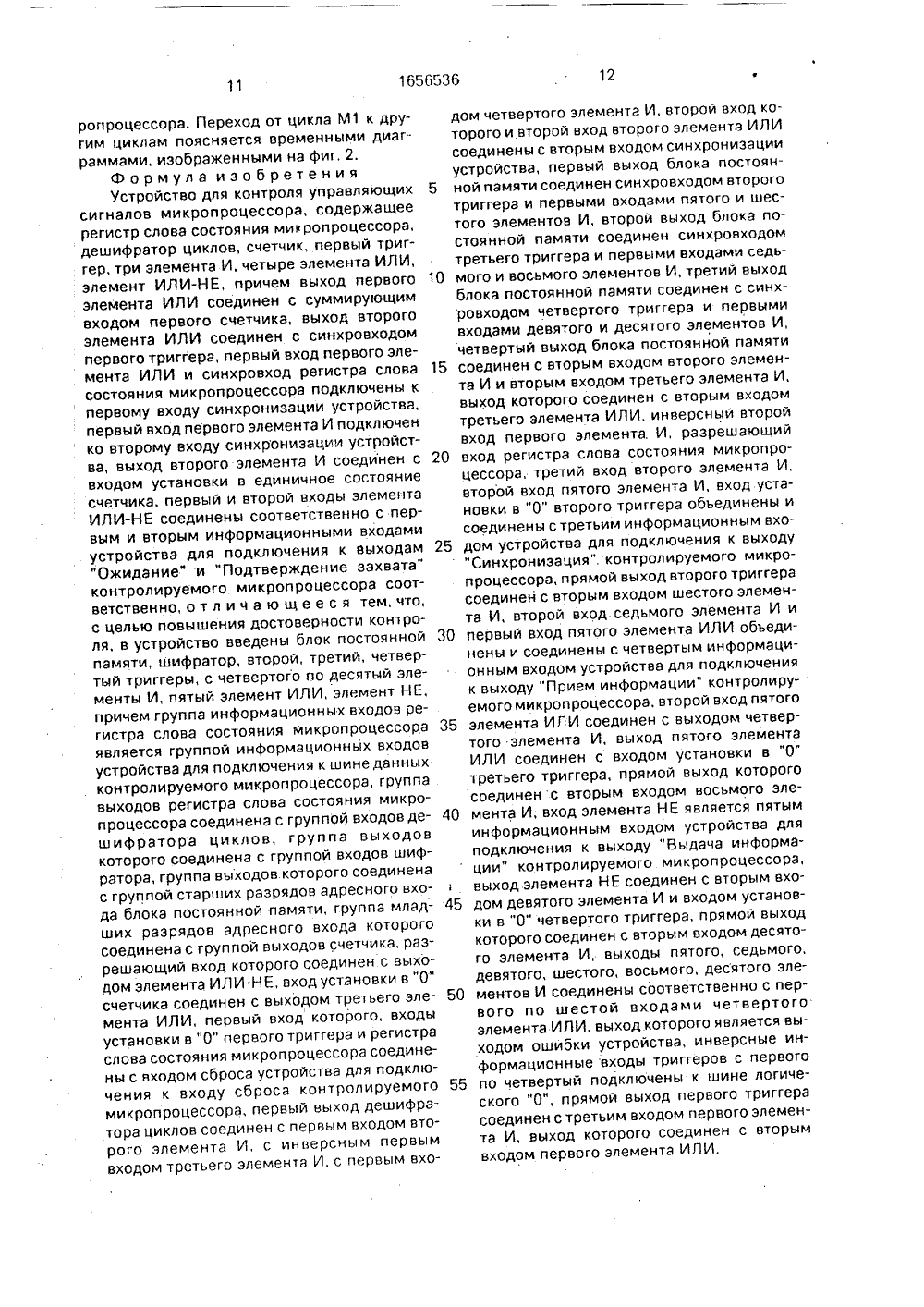

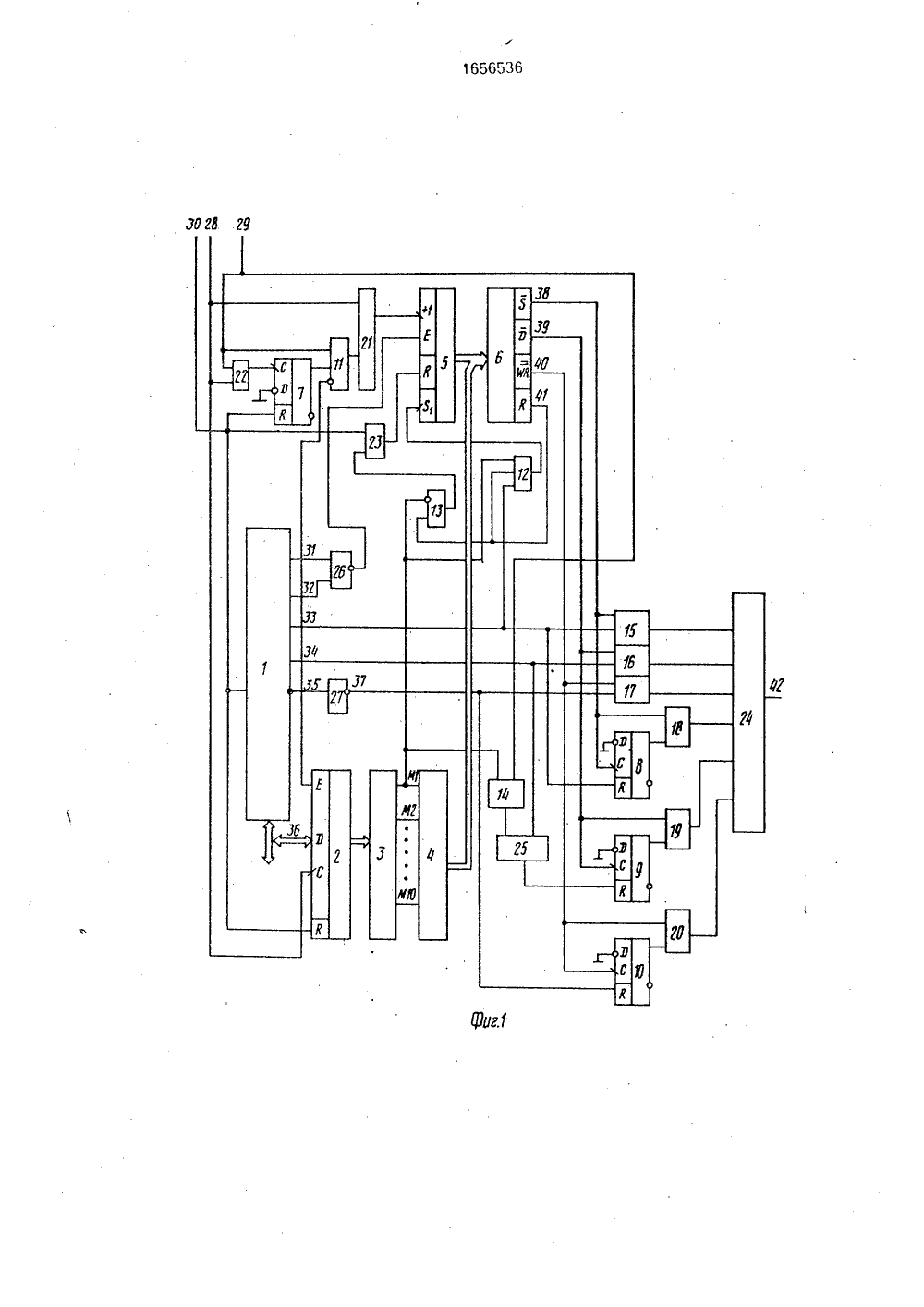

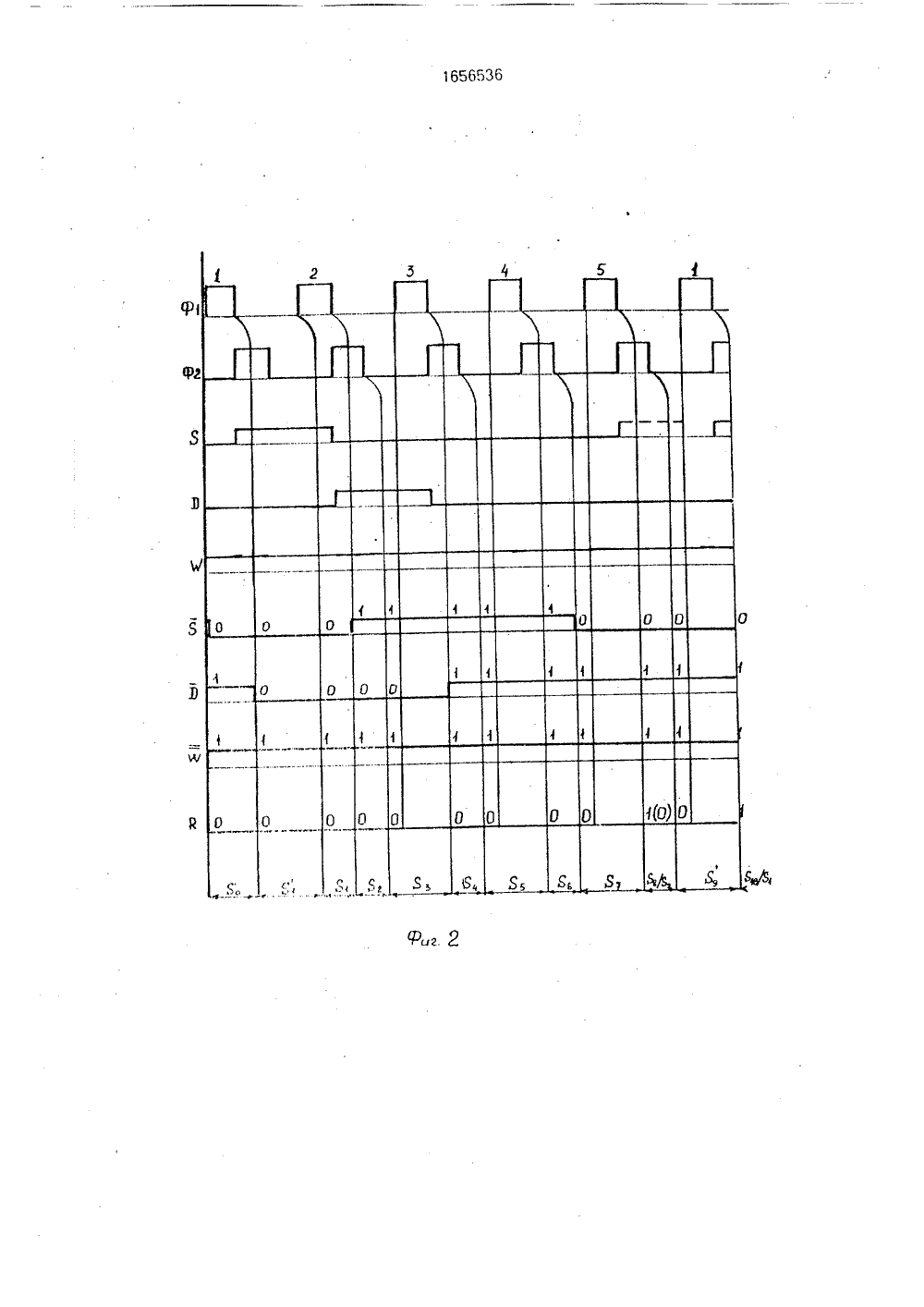

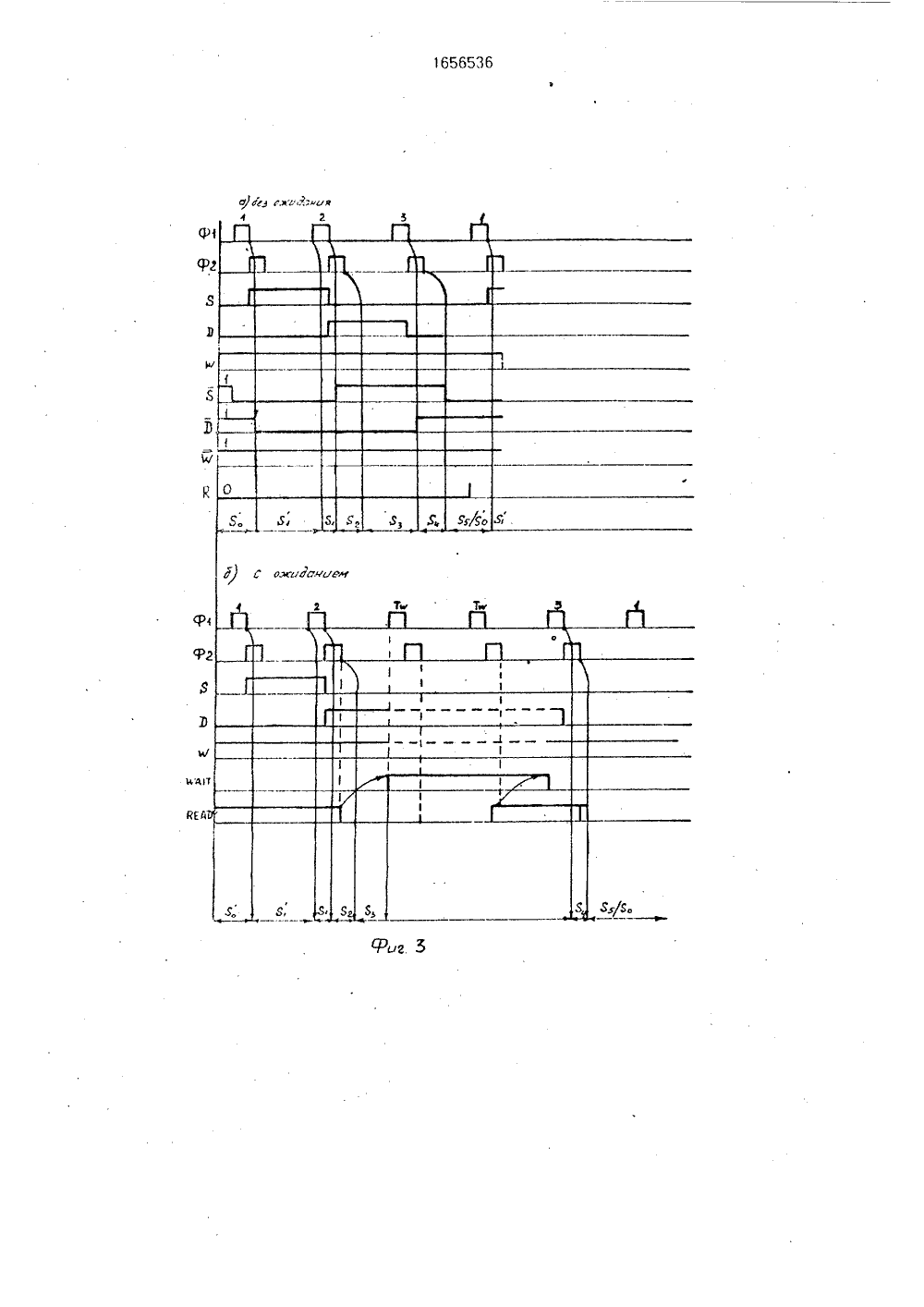

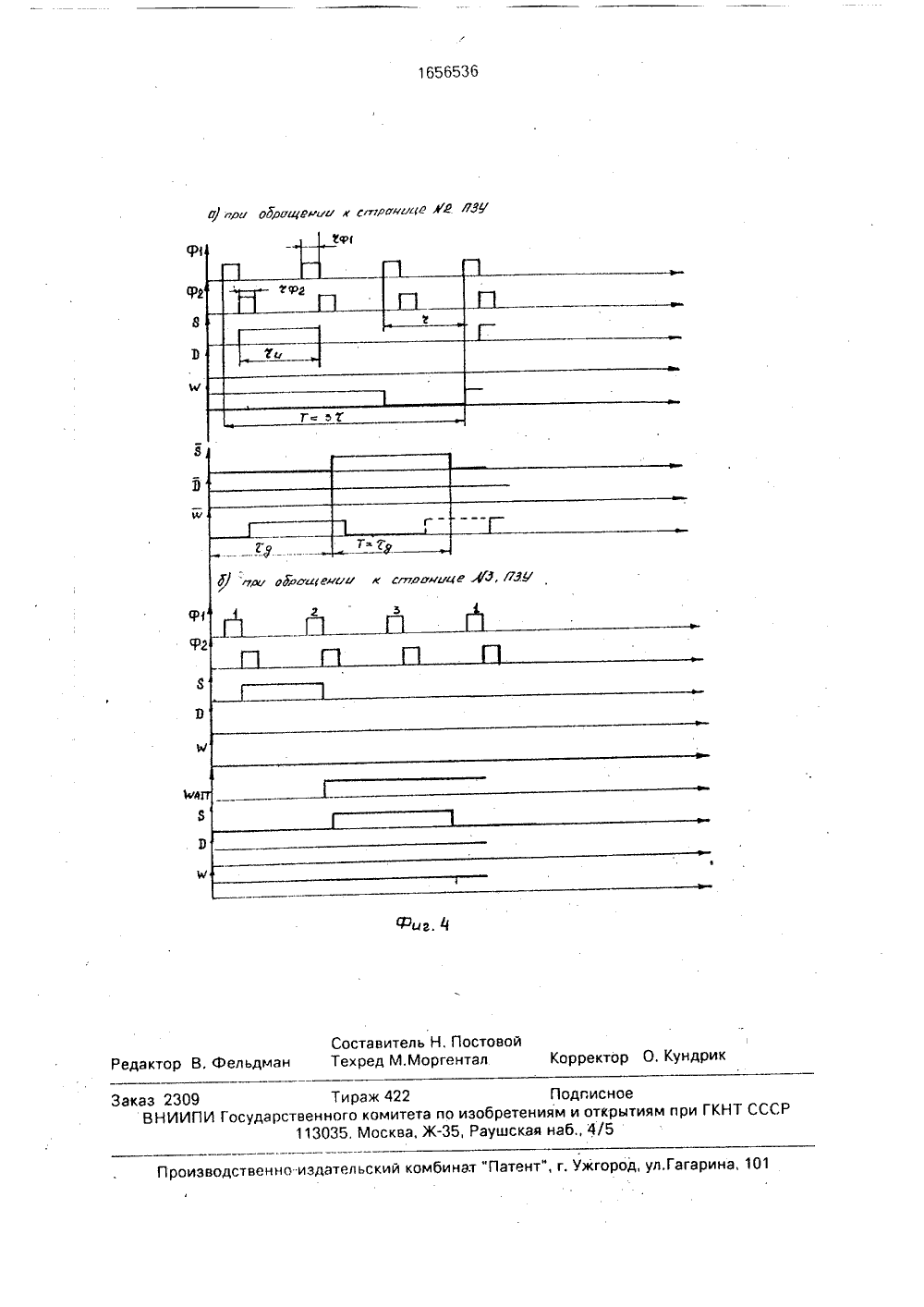

СОГОЗ СОВГТСКИХСОЦИАЛИС)ИЧЕСКИРЕСПУБЛИК 36 А 1 06 Г 11 00 ИСАНИЕ ИЗОБРЕТЕН К АВТ В.Ю,Пион ькин,Я УПРАВ- ОЦЕССОГОСУДАРСТВЕННЫИ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ.ГКНТ СССР МУ СВИДЕТЕЛЬСТВУ.(56) Авторское свидетельство СССйг 1238076, кл. 6 06 Г 11/00, 1986Авторское свидетельство СССМ 1283480, кл. 6 06 Г 11/00, 1986(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЛЯЮЩИХ СИГНАЛОВ МИКРОПР(57) Изобретение относится к цифровой вычислительной технике и может быть использовано при построении микропроцессорных Изобретениечислительной техзовано имикропроцессорнконтролем,Целью изобретения является повышение достоверности контроля управляющих сигналов микропроцессора.На фиг. 1 представлена функциональная схема устройства для контроля управляющих сигналов микропроцессора, на фиг. 2 представлены временные диаграммы работы устройства при цикле М 1 при обращении к "нулевой" странице ПЗУ; на фиг. 3 - временные диаграммы работы устройства при обращении к странице М 1 ПЗУ; на фиг, 4 а и б представлены временные диаграммы работы устройства при обращении к страницам В 2 и М 3 ПЗУ соответственно.Устройство для контроля управляющих сигналов микропроцессора содержит контотносится к цифровой вынике и может быть испольри построении ых систем и микроЭВМ с систем и микроЭВМ с контролем. Цель изобретения - повышение достоверности контроля управляющих сигналов микропроцессора, Устройство содержит контролируемый микропроцессор, регистр слова состояния микропроцессора, дешифратор циклов, шифратор, счетчик, постоянное запоминающее устройство, четыре триггера, десять элементов И, пять элементов ИЛИ, элемент ИЛИ-НЕ, элемент НЕ. Сущность изобретения состоит в повышении достоверности контроля формирования управляющих сигналов микропроцессора типа КР 580 ИК 80 А за счет ограничения временны) интервалов, в течение которых разрешена подача управляющих сигналов в разряды шины управления. 4 ил. ролируемый микропроцессор 1, регистр 2 слова состояния микропроцессора, дешифратор циклов 3, шифратор 4, счетчик 5, блок постоянной памяти постоянное запоминающее устройство (ПЗУ) б, первый 7, второй 8, третий 9 и четвертый 10 триггеры, первый 11, второй 12, третий .13, четвертый 14, пятый 15, седьмой 16, девятый 17, шестой 18, восьмой 19, десятый 20 элементы И, первый 21, второй 22, третий 23, четвертый 24, пятый 25 элементы ИЛИ, элемент ИЛИ-НЕ 26, элемент НЕ 27.Позициями 28, 29, 30 обозначены первый, второй и третий входы устройства соответственно, 31, 32, 33, 34, 35 первый, второй, третий, четвертый и пятый выходы микропроцессора соответственно, которые образуют шину управления, 36 - шина данных микропроцессора, 37 - выход элемента НЕ, 38, 39, 40, 41 - первый, второй, третий,1656536 4 пРи 03 ртцРииистраница,И лЗУ иг Составитель Н, Постовойдактор В. Фельдман Техред М.Моргентал Корректор О, Кун м при ГКНТ СССР Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина з 2309 ВНИИПИ Госуда Тираж 422венного комитета по изо 113035, Москва, Ж, Ра Подписноеетениям и открытиская наб 4/5четвертый выходы ПЗУ 6 соответственно, 42 интервале времени. Работает аналогично- выход ошибки устройства, триггеру 8.Микропроцессор 1 служит для обработ- Элемент И 11 служит для запрета выдаки поступающей на его входы информации, чи на счетный вход счетчика 5 синхросигнаПо отношению к устройству он является 5 лов с входа 29 устройства при наличии вразрядах шины управления микропроцесРегистр 2 слова состояния микропро- сора сигнала "Синхронизация".цессора служит для приема, хранения и вы- Элемент И 12 служит для установкидачи слова - состояния микропроцессора. счетчика 5 в состояние, соответствующееДешифратор 3 цикла служит для преоб слову 1 ПЗУ б, при переходе от цикла М 1 кразования кода слова состояния в код одно- другим циклам работы микропроцессора 1.го из десяти циклов работыЭлемент И 13 служит для подачи едимикропроцессора 1, ничного сигнала на вход установки в "0"Шифратор 4 служит для преобразова- счетчика 5 при переходе от одного циклания кода цикла работы микропроцессора в 15 (кроме цикла М 1) к другому циклу работыкод адреса "страницы" ПЗУ б, соответству- микропроцессора 1.ющей данному циклу. Элемент И 14 служит для подачи сигнаСчетчик 5 служит для подсчета числа ла "1" на входустановки в "0" триггера 9 приимпульсов тактовой частоты кажого цикла выполнении цикла М 1 всякий раз по прихоработы микропроцессора и выдачи этого 20 ду синхроимпульса со.входа 29 устройствачисла в качестве кода адреса "слова" "стра- Это необходимо для исключения ложногосигнала ошибки при переходе от цикла М 1ПЗУ 6 служит для хранения и выдачи к циклу МЗ(М 5, М 7) и М 9.инверсных значений управляющих сигна- Элемент И 15 служит для контроля отлов, которые образуют слова и задают гра сутствия сигнала "Синхронизация" на зани ы разрешенных интервалов времени прещенных интервалах времени. На этихдля выд уачи управляющих сигналов микро- интервалах инверсный сигнал "СинхрониП Уб аи оцессора в каждом такте каждого цикла, зация", выдаваемый с выхода 38 3 раТриггер 7 служит для организации такой вен "1" и отпирает элемент И 15, Если в этотстрогой последовательности поступления 30 момент с микропроцессора выдан сигналсинхроимпульсов со входов 28 и 29 устрой- "Синхронизация" в шину управления, то онства на счетный вход счетчика 5, когда на как сигнал ошибки пройдет через элемент Исчетчик подается сначала синхроимпульс 15 и элемент ИЛИ 24 на выход 42 ошибкипервой фазы со входа 28, а затем синхроим- устройства.35 Элемент И 16 служит для контроля отТриггер 8 служит для определения нали- сутствия сигнала "Прием информации" нач ия или отсутствия управляющего сигнала запрещенных интервалах времени. Работа 1"Синхронизация (ЯУСС)" на разрешенном ет аналогично элементу И 5.интервале времени. Так, если сигнал отсут- Элемент И 17 служит для контроля отствует, то триггер находится в единичном 40 сутствия сигнала "Выдача информации" насостоянии, если же сигнал синхронизации запрещенных интервалах времени, РаботаИ 15,обнаружен, то единичным сигналом "Синх- ет аналогично элементу И 5,ронизация", подаваемым на вход установки Элемент И 18 служит для выдачи сигнав "0" триггера 8, он сбрасывается в нулевое, ла "Ошибка" на четвертый вход элементасостояние. В единичное состояние триггер 45 ИЛИ 24 при отсутствии сигнала "Синхрони 8 устанавливается по заднему фронту им- зация" на разрешенном интервале времепульса, поступающего на его синхровход с ни.выхода 38 ПЗУ б. Элемент И 19 служит для выдачи сигнаЛИТриггер 9 служитдляопределениянали- ла "Ошибка" на пятый вход элемента Ичия или отсутствия управляющего сигнала 50 24 приотсутствиисигнала "Приеминформа"Прием информации" (ОВИч) на разрешен- ции" на разрешенном интервале времени.н ом интервале времени во всех циклах, кро- Элемент И 20 служит для выдачи сигнаме цикла М 1,. чтобы исключить ложный ла "Ошибка" на шестой входэлемента ИЛ Исигнал ошибки на выходе 40 устройства при 24 при отсутствии сигнала "Выдача инфорпереходе от цикла М 1 к циклу МЗ(М 5, М 7) и 55 мации" на разрешенном интервале времеМ 9, В остальном работает аналогично триг- ни,геру 8. Элемент ИЛИ 21 служит для приема поТриггер 10 служит для определения на- ступающих на его входы синхросигналов иличия или отсутствия сигнала "Выдача ин- выдачи их на счетный вход счетчика 5,формации" (ЧЧВТЕ) на разрешенномЭлемент ИЛИ 22 служит для появления"1" на прямом выходе триггера 7 как припоявлении синхросигнэлэ на входе 28 устройства, тэк и при появлении синхросигнала на.входе 29 устройства. 5Элемент ИЛИ 23 служит для организации обнуления содержимого счетчика 5 какобщим сигналом "Сброс" со входа 29 устройства, так и при переходе от одного цикла(кроме цикла М 1) к другому циклу работы 10микропроцессора 1.Элемент ИЛИ 24 служит для выдачиобобщающего сигнала "Ошибка" нэ выход42 ошибки устройства при неправильнойвыдаче микропроцессором 1 в разряды шины управления управляющих сигналов"Синхронизация" ЯУ 1 чС, "Прием информации" ОВ 18, "Выдача информации",Ф/В 1 ТЕ .Элемент ИЛИ 25 служит для подачи на 20вход установки в "0" триггера 9 единичногосигнэлэ кэк при цикле работы М 1, тэк и припоявлении в других циклах работы нэ разрешенных интервалах времени сигнала "Прием информации". 25Элемент ИЛИ-НЕ 26 служит для подачинэ разрешающий вход счетчика 5 единичного сигнала при отсутствии в разрядах шиныуправления сигналов "Подтверждение захвата" Н 10 А и "Ожидания" ЮА 1 Т и подачи 30на разрешающий вход счетчика 5 нулевогосигнала при наличии хотя бы одного из сигналов "Подтверждение захвата" и "Ожидание",Элемент НЕ 27 служит для получения 35неинвертированного сигнэла "Выдача информации" ЮВ 1 ТЕ для работы схемы контроля.Вход 28 устройства служит для подачитактовых импульсов первой фазы Ф 1. 40Вход 29 устройства служит для подачитактовых импульсов второй фазы Ф 2.Вход 30 устройства служит для подачисигнала "Сброс" оператором в любой момент времени для остановки контроля, 45Выход 31 микропроцессора 1 являетсяпервым выходом микропроцессора и служит для выдачи управляющего сигнала"Ожидание".Выход 32 является. вторым выходом 50микропроцессора 1 и служит для выдачиуправляющего сигнала НЮА "Подтверждение захвата".Выход 33 является третьим выходоммикропроцессора 1 и служит для выдачи 55управляющего сигнала БУМС "Синхронизация",Выход 34 является четвертым выходоммикропроцессора,1 и служит для выдачи управляющего сигнала ОВ 1 Й "Прием информации",Выход 35 является инверсным пятымвыходом микропроцессора 1 и служит длявыдачи управляющего сигнэла АНЮТЕ "Выдача информации".Выходы 31, 32, 33, 34, 35 микропроцессора 1 образуют шину управления, котораяподвергается контролю.Группа выходов 33 микропроцессора 1является шиной данных. Выход 37 являетсявыходом элемента НЕ 27,Выходы 38, 39, 40, 41 ПЗУ 6 служат длявыдачи кодов слов из ПЗУ 6,Выход 42 устройства является выходомошибки.На фиг. 2 изображены временные диаграммы работы устройства при обращении к"нулевой" странице ПЗУ.Нэ фиг. 3 изображены временные диаграммы работы устройства при обращении кпервой "странице" ПЗУ б.Нэ фиг. 4,а изображены временные диаграммы работы устройства при обращениико второй "странице" ПЗУ б,Нэ фиг. 4,6 изображены временные диаграммы работы устройства при обращениик третьей "странице" ПЗУ б.Символами 5 ообозначены "слова",хранящиеся в ПЗУ б и содержэщие коды"инверсных" значений управляющих сигналов ЯУСС, ОВ 1 М, ВIЯ 1 ТЕ, а также прямогозначения сигнала ВЕЗЕТ.Устройство работает следующим образом,Перед началом работы на вход 30 сбросэ устройстВд ПОддется сиГндл ВысокОГОуровня длительностью не менее трех периодов тактовой частоты микропроцессорэ 1,которым микропроцессор устанавливаетсяв исходное состояние. Этим же сигналом висходное нулевое состояние устанавливаются счетчик 5, регистр 2 слова состояниямикропроцессора, триггер 7. После этого вмикропроцессоре начинается такт Т 1 машинного цикла выборки команды М 1 (см,фиг, 2), Нэ первый и второй входы 28 и 29синхронизации устройства поступают неперекрывающиеся последовательности синхроимпульсов первой Ф 1 и второй Ф 2 фазсоответственноЕсли первым пришел импульс фазы Ф2, то он поступает на первый вход элементаИ 11 и через элемент ИЛИ 22 нэ синхровходтриггера 7, который по заднему фронту импульса фэзы Ф 2 устэнавливается в состояние "1" и выдэет единичный сигнал натретий вход элемента И 11. Но так как этотмомент уже заперт нулевым сигнэлом совторого входа 29 синхронизэции устройст 1656536ва, то импульс фазы Ф 2 не поступает на счетный вход счетчика 5, Если же приходит первым импульс фазы Ф 1, то он поступает на первый вход элемента ИЛИ 21, с выхода элемента ИЛИ 21 проходит на счетный вход счетчика 5, а также устанавливает триггер 7 в состояние "1", что обеспечивает прохождение импульса фазы Ф 2 при отсутствии сигнала "Синхронизация" на инверсном входе элемента И 11, поступающего с выхода 33 микропроцессора 1.В счетчике 5 при появлении на его счетном входе импульса проверяется, есть ли на его разрешающем входе единичный сигнал, который поступает при отсутствии в разрядах шин управления микропроцессора 1 сигналов "Ожидание" ЮА 1 Т и "Подтверждение захвата" НОА, Эти сигналы выдаются на разрешающий вход счетчика с выходов 31 и 32 микропроцессора 1 соответственно через элемент ИЛИ-НЕ 26. При отсутствии этих сигналов счетчик начинает подсчитывать импульсы по их заднему фронту для исключения гонок сигнала "Ожидание", который устанавливается в "1" по переднему фронту импульса фазы Ф 1 и самим импульсом фазы Ф 1, При появлении хотя бы одного из сигналов на выходах 31 и 32 микропроцессоров 1 счет останавливается и счетчик 5 запоминает свое состояние, чтобы продолжить счет при снятии этих сигналов. Каждый машинный цикл сопровождается выдачей сигнала "Синхронизация" в такте Т 1, При этом на шину данных микропроцессора выдается слово состояния микропроцессора 1, определяющее действия, которые будут выполняться в данном машинном цикле, По совпадению сигналов Ф 1 = 1 и Е = 1 слово состояние записывается в 8 - разрядный регистр 2 слова состояния микропроцессора. С группы выходов регистра 2 слово состояния поступает на группу выходов дешифратора циклов 3, который определяет, какой из циклов выполняется в данном случае, и дает эту информацию в виде единичного сигнала на один из десяти своих выходов, коорые подключены к входам шифратора 4. Шифратор 4 преобразует код цикла в код адреса "страницы" ПЗУ в соответствующей данному циклу и выдае этот код на группу сгарших разрядов адресного входа Г 13 У 6, В то же время со счетчика 5 поступает на группу младших разрядов адресного входа ПЗУ б число подсчитанных импульсов в виде кода адреса "слова и данной "страниу " 113 У б. Адресное пространство ПЗУ б разбип, на 4 страницы, каждая из которых соо ;етствует определенной группе циклов "нулевая Страница циклу М 1 (см. фи.), пе 1)ваястраница- циклам М 2, М 4, Мб, М 8, М 10(см фиг. 3, а и б), "вторая страница" - циклам МЗМ 5, М 7 (см. фиг, 4,а), "третья страница" - циклу М 9 (см. фиг, 4,б). Такое разбиение 5 адресного пространства объясняется тем,что каждой "странице" поставлены в соответствие циклы, которым соответствуют 10 15 20 25 30 35 40 45 50 55 сходные сигналы управления во время их выполнения.В случае, если с выходов шифратора не поступает код адреса "страницы", как например в такте Т 1, то обращение производится к "нулевой странице", так как цикл М 1обязателен для всех без исключения команд, а в такте Т 1 выдаются управляющие сигналы, одинаковые для всех циклов. По адресам, поступающим на входы ПЗУ б, из него извлекаются слова, которые содержат инверсные значения сигналов управления микропроцессора "Синхронизация", "Прием информации", "Выдача информации" и в прямом виде значение сигнала "Конец цикла",Значение БУМС, ОВ 1 М, О/Р 1 ТЕ сигналов БУМС, ОВ 11 ч, В/К 1 ТЕ поступают на первые входы элементов И 15, 16, 17 соответственно, на вторые входы которых поступаЮт прямые значения управляющих сигналов с выходов ЗЗ, 34 микропроцессора 1 и с выхода 37 элемента НЕ 27 соответственно, При этом проверяется отсутствие импульсов данных сигналов управления на запрещенных интервалах, Пусть в данный момент времени (например, в такте ТЗ цикла М 1) не должно быть сигнала ЯУСС "Синхронизация" см, фиг. 2). Тогда в соответствующем данному моменту слове ПЗУ б должно быть записано 5 У/Л. = 1. Этот сигнал открывает элемент И 14 и в случае, если появится ложный сигнал "Синхронизация", то этот сигнал пройдет через элемент И 14 на первый вход элемента ИЛИ 24, с выхода 42 которого будет выдан сигнал ошибки, Если же сигнал "Синхронизация" должен быть в данном такте (например, в такте Т 1 цикла М 1), то из ПЗУ б будет считан сигнал Б 7)ЧГ= О, который запирает элемент И 15 на время прохождения сигнала БУКС, Аналогичным образом работают схемы контроля сигналов ОВ 1 М "Прием информации" и О/В 1 ТЕ "Выдача информации",Инверсные значения сигналов ЯУСС, О Б 1 М, ЮК 1 ТЕ поступают также с выходов 38, 39, 40 соответственно на входы синхронизации триггеров 8, 9, 10 и на первые входы элементов И 18, 19, 20. На входы установки в "0" триггеров 8, 9, 10 подаются контролируемые значения. сигналов БУМС, ОВ 1 И, й/К 1 ТЕ соответственно в прямом виде. Здесь контролируется наличие нужных сиг 165653610 20 25 30 35 40 45 50 55 налов управления на разрешенных интервалах времени.Рассмотрим работу схемы контроля на примере сигнала "Синхронизация", В такте ТЗ цикла М 1 из ПЗУ считывается сигнал БУМС = 1, который поступает на синхровход триггера 8 и на первый вход элемента И 18, По окончании цикла М 1 в такте Т 1 любого цикла должен появиться сигнал БУКС, а из ПЗУ б считывается сигнал ЯУгЛ= О. При этом триггер 8 заднему фронту сигнала ГРГН. = 1 устанавливается в "1", а сигнал БАМ; = 0 подается на синхровход триггера 8 и первый вход элемента И 18 в течение времени, равного разрешенному интервалу времени появления сигнала БУМС. Пусть сигнал ЯУИС так и не появился на разрешенном интервале времени из-за ошибки в работе микропроцессора 1, Тогда в следующем тахте из ПЗУ б будет считан сигнал 75 Р= 1, который, поступая на первый вход элемента И 18, открывает его, в результате чего единичный сигнал с триггера 7 поступает через элемент ИЛИ 24 на выход,42 как сигнал ошибки, Если же сигнал БУМС = 1 появился на разрешенном интервале времени, то он. поступая на вход установки в "О, сбрасывает триггер 8 в "0" и поэтому в следующий момент времени сигнал ошибки не выдается,Сигналы ОВК и ЯКТЕ контролируются аналогично сигналу ВУДС, только сигнал ОВЮ в цикле М 1 не контролируется, так как в цикле М 1 с первого выхода дешифратора циклов 3 на вход элемента И 14 подается единичный сигнал, открывающий этот элемент и при Ф 2 = 1 на вход установки в "0" триггера 9 через элементы И 14 и ИЛИ 25 подается единичный сигнал. Это необходимо для предотвращения выдачи ложного сигнала ошибки при переходе от цикла М 1 к циклу МЗ М 5, М 7) и М 9,С выхода 41 ПЗУ б выдается также импульс "Конец цикла" Я, который указывает, что выполняемый микропроцессором 1 цикл закончен и следует переходить к следующему циклу. Переход к следующему циклу осуществляется следующим образом, Все циклы микропроцессора, кроме цикла М 1,включают три такта (Т 1, Т 2, ТЗ), только цикл М 1 может иметь четыре или пять тактов. Таким образом, если выполняемый цикл не был циклом М 1, то счетчик 5, подсчитав три такта, выдает на входы ПЗУ б код адреса, по которому считывается сигнал Я = 1. Этот сигнал с выхода 41 ПЗУ 6 поступает на вторые входы элементов И 12 и 13. Если выполняется не цикл М 1, то с первого выхода дешифратора выдается нулевой сигнал, который запирает элемент И 12 и отпирает элемент И 13, через который сигнал й:= 1 с выхода ПЗУ 6 поступает на второй вход элемента ИЛИ 23 и далее на вход установки в "0" счетчика 5, который устанавливается в нулевое состояние, что соответствует слову Яо, хранящемуся в ПЗУ б по нулевому адре 1су.Момент перехода от одного цикла (кроме цикла М 1) к другому поясняется временными диаграммами, изображенными на фиг, 3 и 4. Рассмотрим, как происходит переход от цикла М 1 к другим циклам, Цикл М 1 может иметь четыре или пять тактов. Чтобы определить, сколько тактов имеет с своем составе данный цикл М 1, используется сигнал "Синхронизация", появление которого анализируется после окончания четвертого такта. Счетчик 5 в этом случае выдает код адреса "слова" в "нулевой странице" ПЗУ б, из которой считывается сигнал В =- 1, который как и в других циклах поступает с выхода 41 ПЗУ б на вторые входы элементов И 12 и 13. Но элемент И 13 закрыт единичным сигналом, подаваемым на его инверсный вход с первого выхода дешифратора 3. Этот же сигнал поступает на первый вход элемента И 12, и если сигнал синхронизации появится в следующем такте, то через элемент И 12 он поступит на вход установки счетчика в состояние, соответствующее слову 51, хранящемуся в ПЗУ б,Установка счетчика в состояние, соответствующее слову Я 1, а не Яо, необходима в связи с тем, что в данном случае пятый такт Т 5 цикла М 1 оказался первым тактом Т 1 следующего цикла, за которым должен следовать второй такт Т 2 и так далее, Если же в пятом такте сигнал 5 УгчС не появился, то несмотря на то, что К = 1, счетчик продолжает счет и выдачу кода адреса в ПЗУ б и по заднему фронту импульса фазы Ф 2 такта Т 5 устанавливается К = О. По окончании такта Т 5 цикла М 1 счетчик 5 выдает код адреса "слова" нулевой "странице" ПЗУ б, по которому считывается слово, где разряд Й = 1, и снова происходит анализ появления сигнала синхронизации, При его появлении прохождение импульсов фазы Ф 2 через элемент ИЛИ 24 запрещается, счетчик 5 устанавливается в состояние, соответствующее слову Я 1 в регистр 2 слова состояния микропроцессора записывается новое слово состояния и начинается работа по следующему циклу,Запрет импульсов фазы Ф 2 в момент прохождения сигнала синхронизации необходим для того, чтобы счетчик 5 не мог выдавать код адреса "слова" без указания кода адреса новой "страницы" ПЗУ б, т,е, до срабатывания регистра 2 слова состояния мик 1656536 125 10 15 20 25 30 35 40 45 50 55 ропроцессора, Переход от цикла М 1 к другим циклам поясняется временными диаграммами, изображенными на фиг. 2.Формула изобретения Устройство для контроля управляющих сигналов микропроцессора, содержащее регистр слова состояния микропроцессора, дешифратор циклов, счетчик, первый триггер, три элемента И, четыре элемента ИЛИ, элемент ИЛИ-НЕ, причем выход первого элемента ИЛИ соединен с суммирующим входом первого счетчика, выход второго элемента ИЛИ соединен с синхровходом первого триггера, первый вход первого элемента ИЛИ и синхровход регистра слова состояния микропроцессора подключены к первому входу синхронизации устройства, первый вход первого элемента И подключен ко второму входу синхронизации устройства, выход второго элемента И соединен с входом установки в единичное состояние счетчика, первый и второй входы элемента ИЛИ-НЕ соединены соответственно с первым и вторым информационными входами устройства для подключения к выходам "Ожидание" и "Подтверждение захвата" контролируемого микропроцессора соответственно, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в устройство введены блок постоянной памяти,. шифратор, второй, третий, четвертый триггеры, с четвертого по десятый элементы И, пятый элемент ИЛИ, элемент НЕ, причем группа информационных входов регистра слова состояния микропроцессора является группой информационных входов устройства для подключения к шине данных контролируемого микропроцессора, группа выходов регистра слова состояния микропроцессора соединена с группой входов дешифратора циклов, группа выходов которого соединена с группой входов шифратора, группа выходов которого соединена с группой старших разрядов адресного входа блока постоянной памяти, группа младших разрядов адресного входа которого соединена с группой выходов счетчика, разрешающий вход которого соединен с выходом элемента ИЛИ-НЕ, вход установки в "0" счетчика соединен с выходом третьего элемента ИЛИ, первый вход которого, входы установки в "0" первого триггера и регистра слова состояния микропроцессора соединены с входом сброса устройства для подключения к входу сброса контролируемого микропроцессора, первый выход дешифратора циклов соединен с первым входом второго элемента И, с инверсным первым входом третьего элемента И, с первым входом четвертого элемента И, второй вход которого и второй вход второго элемента ИЛИ соединены с вторым входом синхронизации устройства, первый выход блока постоянной памяти соединен синхровходом второго триггера и первыми входами пятого и шестого элементов И, второй выход блока постоянной памяти соединен синхровходом третьего триггера и первыми входами седьмого и восьмого элементов И, третий выход блока постоянной памяти соединен с синхровходом четвертого триггера и первыми входами девятого и десятого элементов И, четвертый выход блока постоянной памяти соединен с вторым входом второго элемента И и вторым входом третьего элемента И,выход которого соединен с вторым входом третьего элемента ИЛИ, инверсный второй вход первого элемента. И, разрешающий вход регистра слова состояния микропроцессора, третий вход второго элемента И, второй вход пятого элемента И, вход установки в "0" второго триггера объединены и соединены с третьим информационным входом устройства для подключения к выходу"Синхронизация". контролируемого микропроцессора, прямой выход второго триггера соединен с вторым входом шестого элемента И, второй вход седьмого элемента И и первый вход пятого элемента ИЛИ объединены и соединены с четвертым информационным входом устройства для подключения к выходу "Прием информации" контролируемого микропроцессора, второй вход пятого элемента ИЛИ соединен с выходом четвертого элемента И, выход пятого элемента ИЛИ соединен с входом установки в "0" третьего триггера, прямой выход которого соединен с вторым входом восьмого элемента И, вход элемента НЕ является пятым информационным входом устройства для подключения к выходу "Выдача информации" контролируемого микропроцессора, выход элемента НЕ соединен с вторым входом девятого элемента И и входом установки в "0" четвертого триггера, прямой выход которого соединен с вторым входом десятого элемента И, выходы пятого, седьмого, девятого, шестого, восьмого, десятого элементов И соединены соответственно с перваго по шестой входами четвертого элемента ИЛИ, выход которого является выходом ошибки устройства, инверсные информационные входы триггеров с первого по четвертый подключены к шине логического "0", прямой выход первого триггера соединен с третьим входом первого элемента И, еыход которого соединен с вторымвходом первого элемента ИЛИ.

СмотретьЗаявка

4636747, 12.01.1989

ПРЕДПРИЯТИЕ ПЯ М-5156

СИДОРЕНКО НИКОЛАЙ ФЕДОРОВИЧ, ТКАЧЕВ МИХАИЛ ПАВЛОВИЧ, ПИКИН ВЛАДИМИР ЮРЬЕВИЧ, ОСТРОУМОВ БОРИС ВЛАДИМИРОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 11/00

Метки: микропроцессора, сигналов, управляющих

Опубликовано: 15.06.1991

Код ссылки

<a href="https://patents.su/10-1656536-ustrojjstvo-dlya-kontrolya-upravlyayushhikh-signalov-mikroprocessora.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля управляющих сигналов микропроцессора</a>

Предыдущий патент: Устройство для определения очередности поступления (е+1) цифровых сигналов

Следующий патент: Устройство для контроля дешифратора

Случайный патент: Способ приготовления бетонной смеси