Устройство обнаружения и исправления ошибок в кодах рида соломона

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

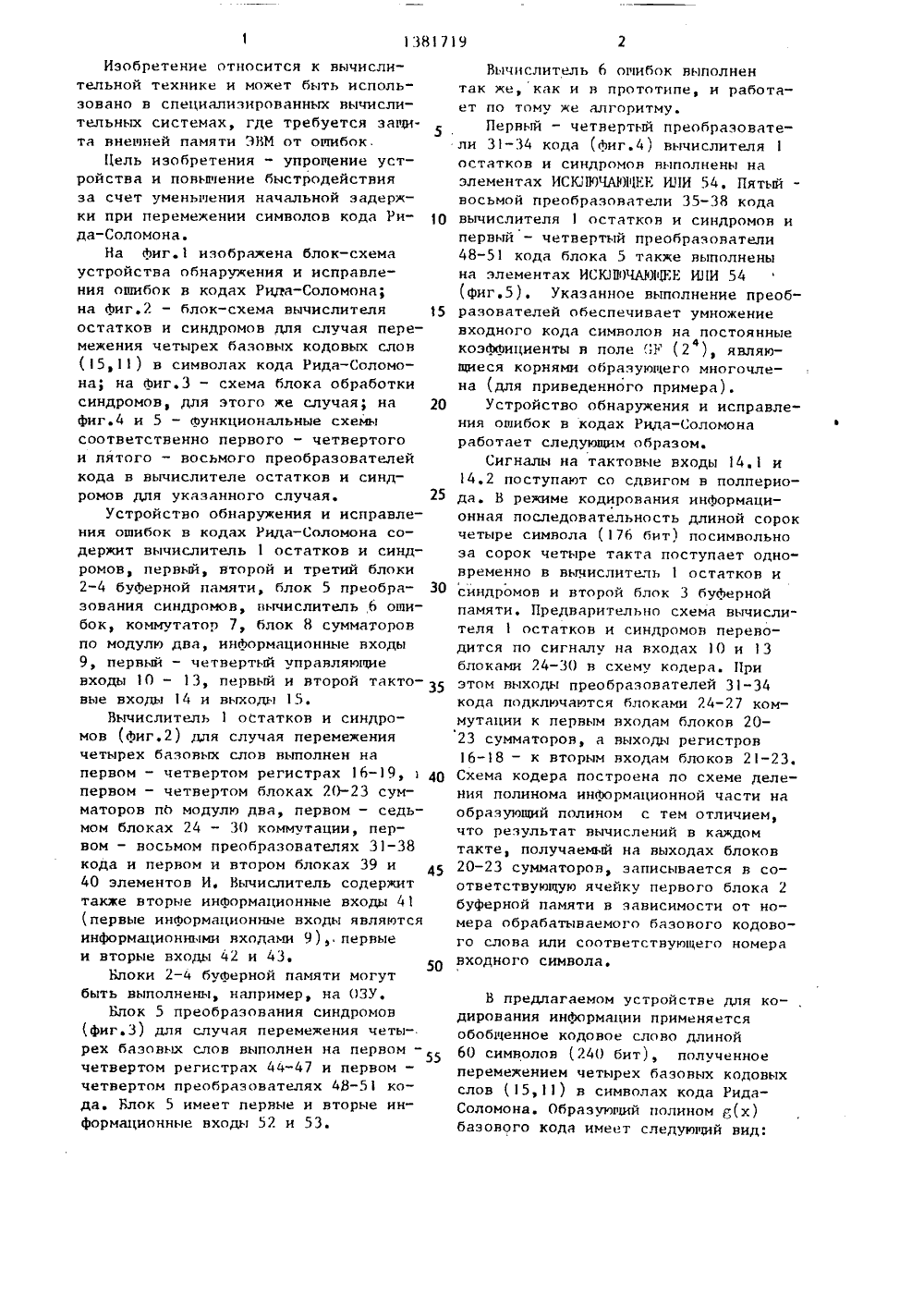

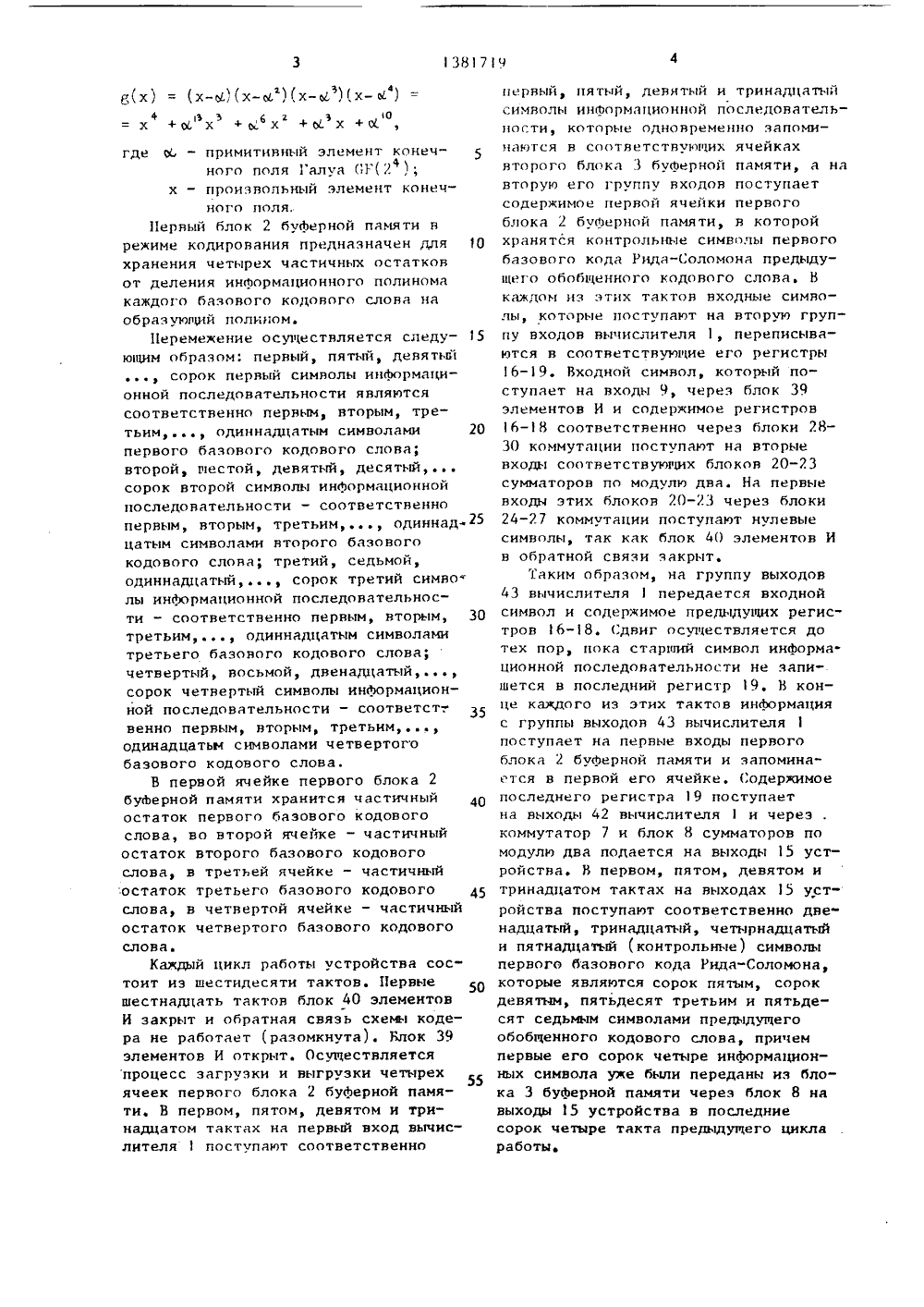

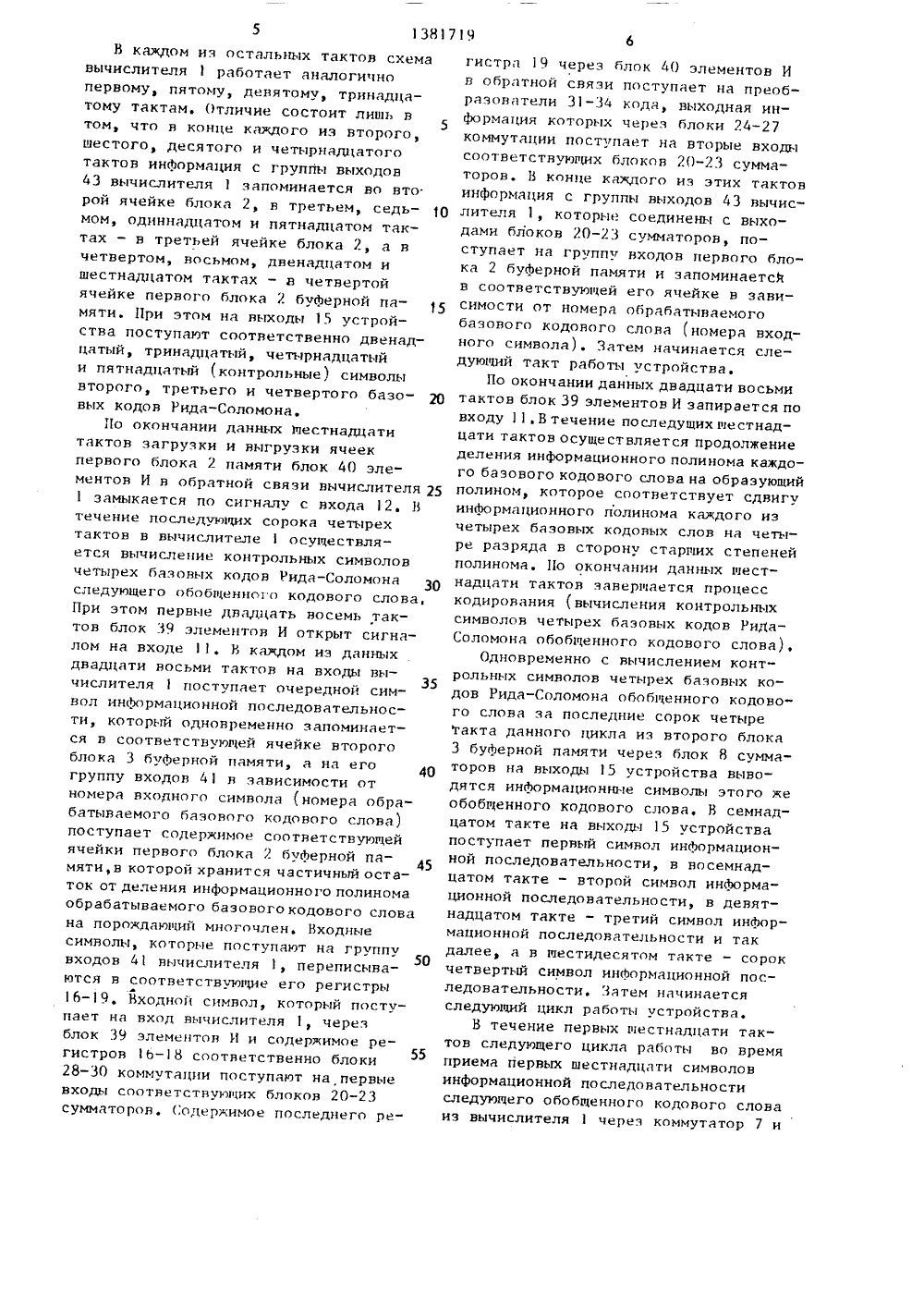

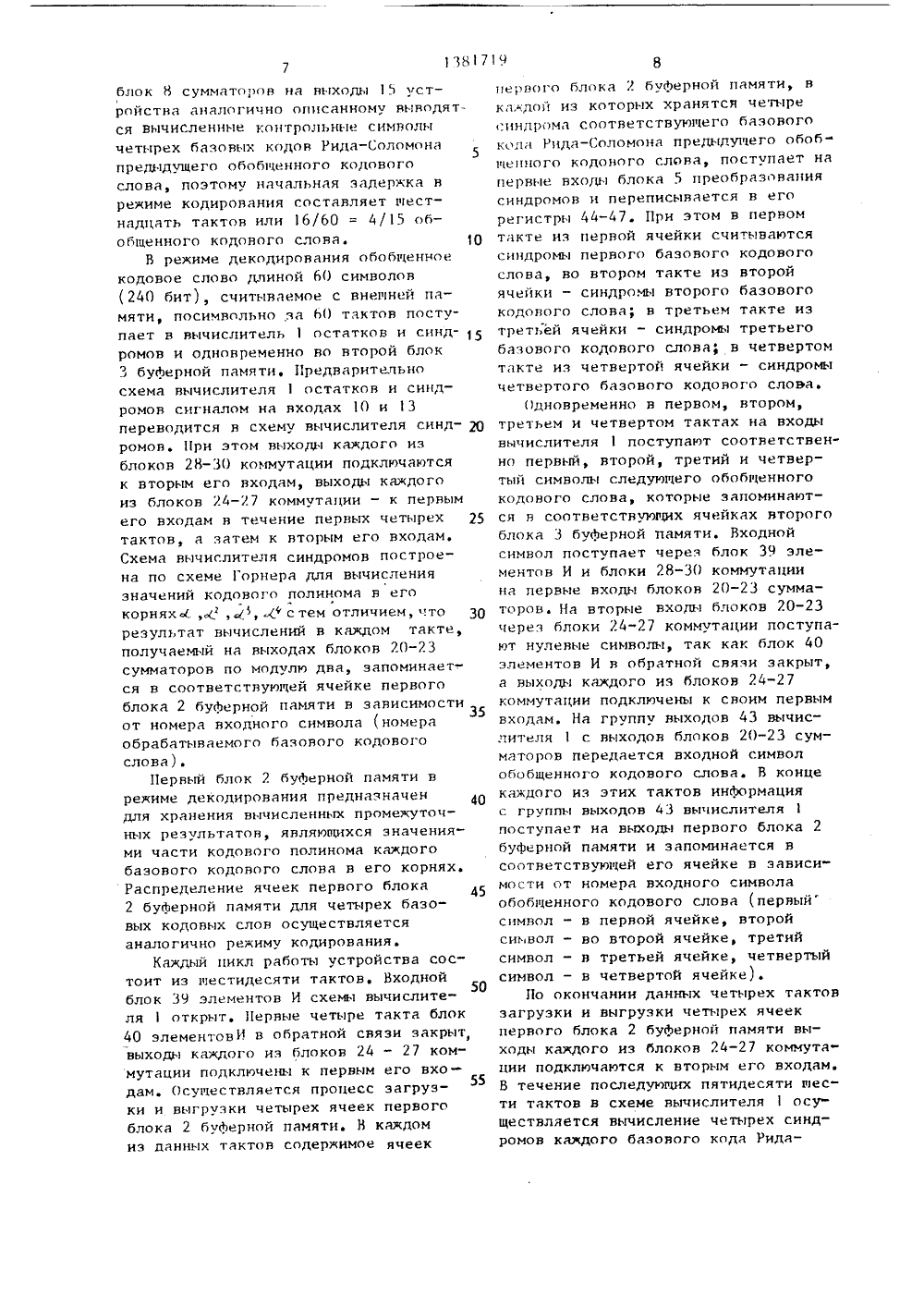

(71) Курскийтут и Институтв энергетике АН(53) 81.3(088 уетс ощиб 24 Бил.( 10олитехнический инстипроблем моделиронани УССР н, В, В.Гво 8) 1 етров опц,нее 984 ю Вь СССР), 1981. ИЯ И ИСПРАВСО,)ОЮНАк вычислиьзонание н тельных Ав У 101 (54) уемая а от ЕНИЯ57) специ 75 ГОСУДАРСТВЕННЫИ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ А 8 ТОРСКОМУ СВИДЕТЕЛЬСТВ 1 ЕЕЕ ТгапзасС).опз оп С ч.С-ЗЗ, М 2, р,178-18 ория передачи инйормац В 1964, с.32-34.торское свидетельство 8119, кл. О 06 Р 11/О( УСХРОЙСТВО ОБНАРУЖЕН011 ИБОК В КОДАХ РИДА- Изобретение относится ой технике, Его испол ализированных вычисли системах, где треб я защ ней памяти ЧВМ от ок, позволяет упростить устройство и повысить быст родействие за счет уменьшения началь ной задержки при перемежении символов кода Рида-Соломона. Устройство защиты от ошибок но внешней памяти содержит вычислитель 1 остатков и синдромов, блоки 2,3 буферной памяти блок 5 преобразования синдромон, вычислитель Ь ошибок, коммутатор 7 и блок 8 сумматоров по модули два. Благодаря введении блока 4 буферной памяти и специальному выполнении вычислителя 1 остатков и синдромов в устройстве обеспечивается треб степень перемежения для защиты пакетных ошибок, а обработка символов в режимах кодирования и декодирования осуществляется без их предварительного накопления. 5 ил.,.1 ежнин едак акая 1195/ Подписноественного комитета ССС эобретений и открыти-35, Раунская наб.,/5 оизводстецио Ь ф тираж 97.8 ВНИИ 11 И Госуд по делам 15, Москва, лиграйическое предприятие, г,ужгород, ул,ПроектнаяИзобретение относится к вычислительной технике и может бить использовано в специализированных вычислительных системах, где требуется защита внешней памяти ЭВМ от ошибок,Цель изобретения - упрощение устройства и повлпчение быстродействияза счет уменьшения начальной задержки при перемежении символов кода Рида-Соломона.На фиг.1 изображена блок-схемаустройства обнаружения и исправления ошибок в кодах Рида-Соломона;на фиг.2 - блок-схема вычислителя 15остатков и синдромов для случая перемежения четырех базових кодовых слов(1511) в символах кода Рида-Соломона; на Фиг.3 - схема блока обработкисиндромов, для этого же случая; на 20фиг,4 и 5 - йункциональные схемысоответственно первого - четвертогои пятого - восьмого преобразователейкода в вычислителе остатков и синдромов для указанного случая. 25Устройство обнаружения и исправления ошибок в кодах Рида-Соломона содержит вичислитель 1 остатков и синдромов, первый, второй и третий блоки2-4 буферной памяти, блок 5 преобразования синдромов, влиислитель 6 ошибок, коммутатор 7, блок 8 сумматоровпо модулв два, информационные входы9, первый - четвертый управлявщиевходы 10 - 13, первий и второй тактовые входы 14 и влходи 15.Вычислитель 1 остатков и синдромов (фиг.2) дпя случая перемежениячетырех базовых слов выполнен напервом - четвертом регистрах 16-19,40первом - четвертом блоках 20-23 сумматоров по модулв два, первом - седьмом блоках 24 - 30 коммутации, первом - восьмом преобразователях 31-38кода и первом и втором блоках 39 и 4540 элементов И. Вычислитель содержиттакже вторые инйормационние входы 41(первые инйормационные входы являвтсяинформационными входами 9), первыеи вторые входы 42 и 43.Блоки 2-4 буйерной памяти могутбыть выполнены, например, на 03 У.Блок 5 преобразования синдромов(фиг3) для случая перемежения четы-,рех базовых слов Выполнен на первом - 55четвертом регистрах 44-47 и первом -четвертом преобразователях 48-51 кода. Блок 5 имеет первые и вторые информационные входи 52 и 53. Вычислитель 6 ошибок выполнен так же, как и в прототипе, и работает по тому же алгоритму.Первий - четвертый преобразователи 31-34 кода (Фиг.4) вычислителя 1 остатков и синдромов выполнены на элементах ИСКЛИЧА 3)19:Е И 3 И 54. Пятый восьмой преобразователи 35-38 кода вычислителя 1 остатков и синдромов и первый - четвертый преобразователи 48-51 кода блока 5 также выполнены на элементах ИСЮР)ЧАЮ 17 Е И 1 И 54 (фиг.5). Указанное выполнение преобразователей обеспечивает умножение входного кода символов на постоянные коэфйициенты в поле (Р (2 ), являвщиеся корнями образувщего многочлена (для приведенного примера).Устройство обнаружения и исправления ошибок в кодах Рида-Соломона работает следувщим образом.Сигналы на тактовые входы 14.1 и 14.2 поступавт со сдвигом в полпериода. В режиме кодирования информационная последовательность длиной сорок четыре символа (176 бит) посимвольно эа сорок четыре такта поступает одно" временно в вляислитель 1 остатков и синдромов и второй блок 3 буферной памяти. Предварительно схема вычислителя 1 остатков и синдромов переводится по сигналу на входах 10 и 13 блоками 24-30 в схему кодераПри этом выходи преобразователей 31-34 кода подклвчавтся блоками 24-27 коммутации к первым входам блоков 20- 23 сумматоров, а виходл регистров 16-18 - к вторым входам блоков 21-23. Схема кодера построена по схеме деления полинома информационной части на образувщий полином с тем отличием, что результат вычислений в каждом такте, получаемый на выходах блоков 20-23 сумматоров, записывается в соответствувщув ячейку первого блока 2 буферной памяти в зависимости от номера обрабатываемого базового кодового слова или соответствувщего номера входного символа. В предлагаемом устройстве для кодирования информации применяется обобщенное кодовое слово длиной 60 символов (240 бит), полученное перемежением четырех базовых кодових слов (15,11) в символах кода Рида- Соломона. Образувщий полипом д(х) базового кода имеет следувщий вид:= х +О х +ь, х +М. х+с где М, - примитивный элемент конечного поля Галуа ОР(2 );х - произвольный элемент конечного поля.11 ервый блок 2 буферной памяти в режиме кодирования предназначен для О хранения четырех частичнлх остатков от деления информационного полинома каждого базового кодового слова на образующий полипом.Неремежение осуществляется следу ющим образом: первый, пятый, девятлйсорок первый символы информационной последовательности являются соответственно первым, вторым, третьим одиннадцатым символами 20 первого базового кодового слова; второй, шестой, девятый, десятый, сорок второй символы информационной последовательности - соответственно первым, вторым, третьим одиннад25 цатим символами второго базового кодового слова; третий, седьмой, одиннадцатый сорок третий символы информационной последовательности - соответственно первым, вторым, 30 третьим одиннадцатым символами третьего базового кодового слова; четвертый, восьмой, двенадцатый сорок четвертый символы информационной последовательности - соответст-. венно первым, вторым, третьим одинадцатьи символами четвертого базового кодового слова.В первой ячейке первого блока 2 буферной памяти хранится частичный 40 остаток первого базового кодового слова, во второй ячейке - частичный остаток второго базового кодового слова, в третьей ячейке - частичный остаток третьего базового кодового 45 слова, в четвертой ячейке - частичный остаток четвертого базового кодовогослова.Каждый цикл работы устройства состоит из шестидесяти тактов. Первые шестнадцать тактов блок 40 элементов И закрыт и обратная связь схемы кодера не работает (разомкнута). Блок 39 элементов И открыт. Осуществляется процесс загрузки и выгрузки четырех ячеек первого блока 2 буферной памяти. В первом, пятом, девятом и тринадцатом тактах на первый вход вычислителя 1 поступают соответственна первый, пятый, девятый и тринадцатыйсимволы инФормационной последовательности, которые одновременно запоминаются в соответствующих ячейкахвторого блока 3 буферной памяти, а навторую его группу входов поступаетсодержимое первой ячейки первогоблока 2 буферной памяти, в которойхранятся контрольные символы первогобазового кода Рида-Соломона предлдущего обобщенного кодового слова. Нкаждом из этих тактов входные символы, которле поступают на вторую группу входов вычислителя 1, переписываются в соответствующие его регистры16-19. Входной символ, который поступает на входы 9, через блок 39элементов И и содержимое регистров16-18 соответственно через блоки 2830 коммутации поступают на вторыевходы соответствующих блоков 20-23сумматоров по модулю два. На первыевходы этих блоков 20-23 через блоки24-27 коммутации поступают нулевыесимволы, так как блок 40 элементов Ив обратной связи закрыт.Таким образом, на группу выходов43 вычислителя 1 передается входнойсимвол и содержимое предыдущих регистров 16-8. Сдвиг осуществляется дотех пор, пока старший символ информационной последовательности не запишется в последний регистр 19. В конце каждого из этих тактов информацияс группы выходов 43 вычислителяпоступает на первые входы первогоблока 2 буферной памяти и запоминается в первой его ячейке. Содержимоепоследнего регистра 19 поступаетна выходы 42 вычислителя 1 и черезкоммутатор 7 и блок 8 сумматоров помодулю два подается на выходы 15 устройства. В первом, пятом, девятом итринадцатом тактах на выходах 15 устройства поступают соответственно двенадцатый, тринадцатый, четырнадцатыйи пятнадцатый (контрольные) символыпервого базового кода Рида-Соломона,которые являются сорок пятым, сорокдевятым, пятьдесят третьим и пятьдесят седьмым символами предыдущегообобщенного кодового слова, причемпервые его сорок четыре информационных символа уже бкли переданы из блока 3 буферной памяти через блок 8 навыходы 15 устройства в последниесорок четыре такта предыдущего циклаработы, 1381719В каждом из остальных тактов схема вычислителяработает аналогично первому, пятому, девятому, тринадцатому тактам. Отличие состоит лишь втом, что в конце каждого из второго,шестого, десятого и четырнадцатоготактов информация с группы выходов43 вычислителя 1 запоминается во вто.рой ячейке блока 2, в третьем, седьмом, одиннадцатом и пятнадцатом тактах - в третьей ячейке блока 2, а вчетвертом, восьмом, двенадцатом ишестнадцатом тактах - в четвертойячейке первого блока 2 буферной памяти. При этом на выходы 15 устройства поступают соответственно двенадцатый, тринадцатый, четырнадцатыйи пятнадцатый (контрольные) символывторого, третьего и четвертого базовых кодов Рида-Соломона,По окончании данных шестнадцатитактов загрузки и выгрузки ячеекпервого блока 2 памяти блок 40 элементов И в обратной связи вычислителя 251 замыкается по сигналу с входа 12. Втечение последующих сорока четырехтактов в вычислителе 1 осуществляется вычисление контрольных символовчетырех базовых кодов Рида-Соломонаследующего обобщенноо кодового слова,При этом первые двадцать восемь тактов блок 39 элементов И открыт сигналом на входе 1, В каждом из данныхдвадцати восьми тактов на входы вы 35числителя 1 поступает очередной символ информационной последовательности, который одновременно запоминается в соответствующей ячейке второгоблока 3 буферной памяти, а на его 40группу входов 41 в зависимости отномера входного символа (номера обрабатываемого базового кодового слона)поступает содержимое соответствующейячейки первого блока 2 буферной памяти,в которой хранится частичный остаток от деления информационного полиномаобрабатываемого базового кодового слована порождающий многочлен. Входныесимволы, которые поступают на группувходов 41 вычислителя 1, переписыва 50ются в соответствующие его регистрыМ16-19, Входной символ, который поступает на вход вычислителя 1, черезблок 39 элементов И и содержимое регистров 1 Ьсоответственно блоки28-30 коммутации поступают на первыевходы соответствующих блоков 20-23сумматоров. Содержимое последнего регистра 19 через блок 40 элементов И в обратной связи поступает на преобразователи 31-34 кода, выходная информация которых через блоки 24-27 коммутации поступает на вторые входы соответствующих блоков 20-23 сумматоров. В конце каждого из этих тактов информация с группы выходов 43 вычислителя 1, которые соединены с выходами блоков 20-23 сумматоров, поступает на группу входов первого блока 2 буферной памяти и запоминается в соответствующей его ячейке в зависимости от номера обрабатываемого базового кодового слова (номера входного символа). Затем начинается следующий такт работы устройства.По окончании данных двадцати восьми тактов блок 39 элементов И запирается по входу 11. В течение последущих шестнадцати тактов осуществляется продолжение деления информационного полинома каждого базового кодового слова на образующий полином, которое соответствует сдвигу информационного полинома каждого из четырех базовых кодовых слов на четыре разряда в сторону старших степеней полинома. По окончании данных шестнадцати тактов завершается процесс кодирования (вычисления контрольных символов четырех базовых кодов Рида- Соломона обобщенного кодового слова).Одновременно с вычислением контрольных символов четырех базовых кодов Рида-Соломона обобщенного кодового слова за последние сорок четыре такта данного цикла из второго блока 3 буферной памяти через блок 8 сумматоров на выходы 15 устройства выводятся информационные символы этого же обобщенного кодового слова. В семнадцатом такте на выходы 15 устройства поступает первый символ информационной последовательности, в восемнадцатом такте - второй символ информационной последовательности, в девятнадцатом такте - третий символ информационной последовательности и так далее, а в шестидесятом такте - сорок четвертый символ информационной последовательности. Затем начинается следующий цикл работы устройства.В течение первых шестнадцати тактов следующего цикла работы во время приема первых шестнадцати символов информационной последовательности следующего обобщенного кодового слона из вычислителячерез коммутатор 7 иблок Й сумматоров на выходы 15 устройства аналогично описанному выводятся вычисленные контрольные символы четырех базовых кодов Рида-Соломона предыдущего обобщенного кодового слова, поэтому начальная задержка в режиме кодирования составляет щестнадцать тактов или 16/60 = 4/15 обобщенного кодового слова. 1 ОВ режиме декодирования обобщенкое кодовое слово длиной 60 символов (240 бит), считываемое с внещней памяти, посимвольно,за 60 тактов поступает в вычислитель 1 остатков и синд ромов и одновременно во второй блок 3 буФерной памяти. Предварительно схема вычислителя 1 остатков и синдромов сигналом на входах 1 О и 13 переводится в схему вычислителя синд ромов. При этом выходы каждого из блоков 28-30 коммутации подклвчавтся к вторым его входам, выходы каждого из блоков 24-27 коммутации - к первым его входам в течение первых четырех 25 тактов, а затем к вторим его входам. Схема вычислителя синдромов построена по схеме Горнера для вычисления значений кодового полинома в его корняхК,.l, ф с тем отличием, .то 30 результат вычислений в каждом такте, получаемый на выходах блоков 20-23 сумматоров по модулв два, запоминается в соответстнувщей ячейке первого блока 2 буФерной памяти в зависимости от номера входного символа (номера обрабатываемого базового кодового слова).Первый блок 2 буФериой памяти в режиме декодирования предназначен 40 для хранения вычисленных промежуточных результатов, являвщихся значениями части кодового полинома каждого базового кодового слова в его корнях. Распределение ячеек первого блока 45 2 буФерной памяти для четырех базовых кодовых слов осуществляется аналогично режиму кодирования.Каждый цикл работы устройства состоит из щестидесяти тактов. Входной блок 39 элементов И схемы вычислителя 1 открыт, Первые четыре такта блок 40 элементовИ в обратной связи закрыт, выходи каждого из блоков 24 - 27 коммутации подклвченн к первым его вхо 55 дам. Осуществляется процесс загрузки и выгрузки четырех ячеек первого блока 2 буФерной памяти. В каждом из данных тактов содержимое ячеек ервого блока 2 буФерной памяти, в ка,дой из которых хранятся четыре синдрома соответствувщего базового кода Рида-Соломона предыдущего обобщенного кодового слова, поступает на первые входы блока 5 преобразования синдромов и переписывается в его регистры 44-47. При этом в первом такте из первой ячейки считнвавтся синдромы первого базового кодового слова, во втором такте иэ второй ячейки - синдромы второго базового кодового слова; в третьем такте из третьей ячейки - синдромы третьего базового кодового слова; в четвертом такте из четвертой ячейки - синдромы четвертого базового кодового слова.Одновременно в первом, втором, третьем и четвертом тактах на входы вычислителя 1 поступавт соответственно первый, второй, третий и четвертый символы следувщего обобщенного кодового слова, которые эапоминавтся в соответствувщих ячейках второго блока 3 буФерной памяти, Входной символ поступает через блок 39 элементов И и блоки 28-30 коммутации на первые входи блоков 20-23 сумматоров, На вторые входы блоков 20-23 через блоки 24-27 коммутации поступавт нулевые символы, так как блок 40 элементов И в обратной связи закрыт, а выходы каждого из блоков 24-27 коммутации подклвчены к своим первым входам, На группу выходов 43 вычислителя 1 с выходов блоков 20-23 сумматоров передается входной символ обобщенного кодового слова. В конце каждого из этих тактов инФормация с группы выходов 43 вычислителя 1 поступает на выходы первого блока 2 буФерной памяти и запоминается в соответствувщей его ячейке в зависимости от номера входного символа обобщенного кодового слова (перныи символ - в первой ячейкевторой символ - во второй ячейке, третий символ - и третьей ячейке, четвертый символ - в четвертой ячейке).11 о окончании данных четырех тактов загрузки и выгрузки четырех ячеек первого блока 2 буФерной памяти выходы каждого из блоков 24-27 коммутации подклвчавтся к вторым его входам. В течение последувщих пятидесяти нести тактов в схеме вычислителя 1 осуществляется вычисление четырех синдромов каждого базового кода Рида 138719 1 ОСоломона следувщего обобщенного кодового слова. В каждом из этих тактов на входи вычислителя 1 поступает очередной символ обобщенного кодовогоь слова, которий одновременно запоминается н соотнетстнувщей ячейке второго блока 3 буферной памяти, а на группу 41 входов н зависимости от номера входного символа (номера обра батынаемого базового кодового слона) поступает содержимое соответстнувщей ячейки первого блока 2 буферной памяти. Входные символы которые поступавт на группу входов 41 вычислителя 1, переписывается н соотнетствувщие его регистры 16-19Входной символ через блок 39 элементов И и через блоки 28-30 коммутации поступает на первые входи блоков 20-23 сумма торов, Содержимое каждого из регистров 16-19 поступает на соотнетствувщий преобразователь 35-38 кода. Выходная информация последних через блоки 24-27 коммутации поступает 25 на вторые входи соответствувщих блоков 20-23 сумматоров. В конце каждого из этих тактов информация с виходов ч 3 ничислителя 1 поступает на входи первого блок . 2 буферной памяти 30 и запоминается и соответствувщей его ячейке в зависимости от номера обрабатываемого базового кодового слова (номера входного символа). По окончании пятидесяти шести тактов начина 35 ется следувщий цикл работы вычислите" ля.Одновременно с работой схемы вычислителя 1 из второго блока 3 буферной памяти выводятся символы преди дущего обобщенного кодового слова, а в блоке 5 преобразования синдромов и вычислителе 6 ошибок осуществляется за один и тот же такт вычисление значения ошибки для данного ниноди мого символа. К блоке 5 преобразования синдромов осуществляется циклический сдвиг четирех синдромов каждого базового кода Рида-Соломона предыдущего обобщенного кодового слова путем умножения н блоках 48-51 этих синдромов соответственно на Ж Ы , М. , М. (корни обраэувщего2 змногочлена), В ничислителе 6 ошибок по преобразонанним синдромам в этом же такте определяется значение ошиб 55 ки для данного выводимого сцмнола.В каждом такте работи устройства из нтрдго блока 3 буферной памяти выводится очередной символ предыдущего обобщенного кодового слова, которнй поступает на первые входи блока 8 сумматорон по модулв два. Одновременно в регистры 44-47 блока 5 преобразования синдромов переписывается информация с первых его входов 52 в первых четырех тактах загрузки ячеек третьего блока 4 буферной памяти или с вторых его входов 53 в остальных пятидесяти шести тактах данного цикла работы. На вторые его входы 53 поступает содержимое соответствувщей ячейки третьего блока 4 буферной памяти в зависимости от номера обрабатываемого базового кода Рида-Соломона (номера выводимого символа) предыдущего обобщенного кодового слова. Распределение ячеек третьего блока 4 буферной памяти для четырех базовых кодовых слон осуществляется аналогично первому блоку 2 буферной памяти. Содержимое каждого из регистров 44-47 блока 5 поступает на соотнетстнувщий преобразователь .48-51 кода. Информация с виходов блока 5 поступает на входи третьего блока 4 буферной памяти и запоминается в соотнетствувщей его ячейке н зависимости от номера обрабатываемого базового кода Рида-Соломона предыдущего обобщенного кодового слова. Одновременно информация с выходов блока 5 преобразования синдромов поступает на входи вычислителя 6 ошибок, Вычисленное и вычислителе 6 значение ошибки с его виходон через коммутатор 7 поступает на вторые входи блока 8 сумматоров по модулв дна. В блоке 8 сумматоров производится исправление выводимого символа путем сложения его со значением ошибки. В первом такте на выходи 15 устройства поступает первый символ предидущего обобщенного кодового слова, но втором такте - второй, и третьем такте третий и так далее, а и сорок четвертом такте - сорок четвертый символ информационной части обобщенного кодового слова.Таким образом, начальная задержка в режиме декодирования составляет один цикл работы устройства, соотнетствувщий времени передачи одного обобщенного кодового слова.Предлагаемое устройство обнаружения и исправления ошибок н кодах Рида-Соломона позволяет гарантированноисправлять при принятой степени перемежения, равной 4, один пакет ошибок до 29 бит или два пакета ошибок по 13 бит в каждом обобщенном5 кодовом слове длиной 40 бит (количество исправляемых базовым кодом ошибок 2, длина символов 4 бита).По сравнении с известным предлагаемое устройство упрощено примерно в О 1,65 раза.Начальная задержка, вносимая предлагаемым устройством при перемежении символов базовых кодов Рида-Соломона в составе обобщенного кодового слова,5 в режиме кодирования составляют 4/15 обобщенного кодового слова, в режиме декодирования - одно обобщенное кодовое слово (в известных устройствах - два-три обобщенных кодовых слова). 20В предлагаемом устройстве без изменения его операционной части можно изменять степень перемежения символов информационной последовательности, т,е, количество базовых кодов 25 Рида-Соломона в составе обобщенного кодового слова, при этом достаточно изменить ейкости блоков 2-4 буферной памяти и количество тактов в цикле работы устройства. Например, если блоки 2-4 буферной памяти построить на интегральных схемах типа К 531 РУЯП, можно повышать степень перемежения от четырех до шестнадцати без дополнительных затрат на реализацию остальных блоков, причем при степени пере 35 межения, равной шестнадцати, предла гаемое устройство позволяет гарантированно исправлять пакет ошибок длиной 125 бит или два пакета по 6 бит в обобщенном слове длиной 960 бит. формула изобретения45Устройство обнаружения и исправления ощибок в кодах Рида-Соломона, содержащее блок преобразования синдромов, первый блок буФерной памяти, вычислитель ошибок, выходы которого соединены с соответствующими первыми информационными входами коммутатора, второй блок буферной памяти, выходы которого соединены с соответствующими Первыми входами блока сумматоров по модулю два, выходы которого являются выходами устройства, и вычислитель остатков и синдромов, включающий в себя первый - К-й регистры (К -число базовых кодовых слов), первый .(-" блоки сумматоров по модули два и первый и второй блоки элементов И, выходы первого блока элементов И соединены с соответствующими первыми входами первого блока сумматоров по модулю два, выходы К-го регистра подключены к соответствующим информационным входам второго блока элементов И и вторым информационным входам коммутатора, информационные входы первого блока элементов И объединены с соответствующими информационными входами блока буферной памяти и являются инФормационными входами устройства, тактовые входы первого и второго блоков буферной памяти объединены и являются первым тактовым входом устройства, тактовые входы блока преобразования синдромов и вычислителя ошибок и входы синхронизации первого - К-го регистров вычислителя остатков и синдромов объединены и являются вторым тактовым входом устройства, управляющий вход коммутатора и управлявщие входы первого и второго блоков элементов И вычислителя остатков и синд" ромов являются соответственно первым - третьим управлявгими входами устройства, о т л и ч а в щ е е с я тем, что, с целью упрощения устройства и повыиения быстродействия за счет уменьшения начальной задержкй1 при перемежении символов кода Рида- Соломона, в устройство введен третий блок буферной памяти, в вычислитель остатков и синдромов введены первый (2 К-)-й блоки коммутации и первый (2 К)-й преобразователи кода, выходы, (К+1)-го - (2 К)-го блоков коммутации соединены с первыми информационными входами соответственно второго К-го блоков сумматоров по модули два, выходы второго блока элементов И подключены к соответствующим входам первого - К-го преобразователей кодов, выходы которых соединены с соответствующими первыми информационными входами одноименных блоков коммутации, выходы которых соединены с соответствующими вторыми входами одноименных блоков сумматоров по модулю два, выходы первого - (К)-го регистров подключены к первым информационным входам соответственно (К+1)- го - (2 К)-го блоков коммутации и через соответственно (К+1)-й (2 К)-й преобразователи кода - к138171 Ч 14 7 с вторым информационным входам соответственно первого - (К)-го блоков коммутации, нходн и выходы (2 К)-го преобразонателя кода подключены со 5 ответственно к выходам К-го регистра и вторым инАормационным входам К-го блока коммутации, вторые входы (К+1)-го - (2 К)-го блоков коммутации соответственно объединены и подключены к выходам первого блока элементов И, упранляющие входи первого К-го блоков коммутации объединены и подключены к первому управляющему входу устройства, управляющие входы (К+1)-го - (2 К)-го блоков коммутации объединены и являются четвертым управляющим входом устройства, выходы первого - К-го блоков сумматоров по модулю два вычислителя остатков и 20 синдромон соединены с соответствующими информационными входами первого блока буферной памяти, ныходы которого подключены к соответствующим первым информационным входам блока преобразования синдромов и информационным входам первого - К-го регистровничислителя остатков и синдромов,ныходы блока преобразования синдромов подключены к соотнетствутиминформационным входам вычислителяощибок и третьего блока буферной памяти, Выходы которого соединены ссоответствующими вторыми информационными входами блока преобразованиясиндромов, выходы коммутатора подключены к соответствующим нторымнходам блока сумматоров по модулюдва, тактовый вход третьего блокабуферной памяти подключен к первомутактовому входу устройства, управляющий вход блока преобразования синдромов подклюЧен к второму управляющему входу устройства.

СмотретьЗаявка

4061423, 28.03.1986

КУРСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ, ИНСТИТУТ ПРОБЛЕМ МОДЕЛИРОВАНИЯ В ЭНЕРГЕТИКЕ АН УССР

ТИПИКИН АЛЕКСАНДР ПЕТРОВИЧ, ПЕТРОВ ВЯЧЕСЛАВ ВАСИЛЬЕВИЧ, ГОРШКОВ НИКОЛАЙ ВАСИЛЬЕВИЧ, ГВОЗДЕВ ВЛАДИМИР ВИКТОРОВИЧ, ЕГОРОВ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: H03M 13/27

Метки: исправления, кодах, обнаружения, ошибок, рида, соломона

Опубликовано: 15.03.1988

Код ссылки

<a href="https://patents.su/10-1381719-ustrojjstvo-obnaruzheniya-i-ispravleniya-oshibok-v-kodakh-rida-solomona.html" target="_blank" rel="follow" title="База патентов СССР">Устройство обнаружения и исправления ошибок в кодах рида соломона</a>

Предыдущий патент: Устройство для контроля цифровых данных

Следующий патент: Декодирующее устройство

Случайный патент: Светомузыкальное проекционное устройство