Микропрограммное устройство управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

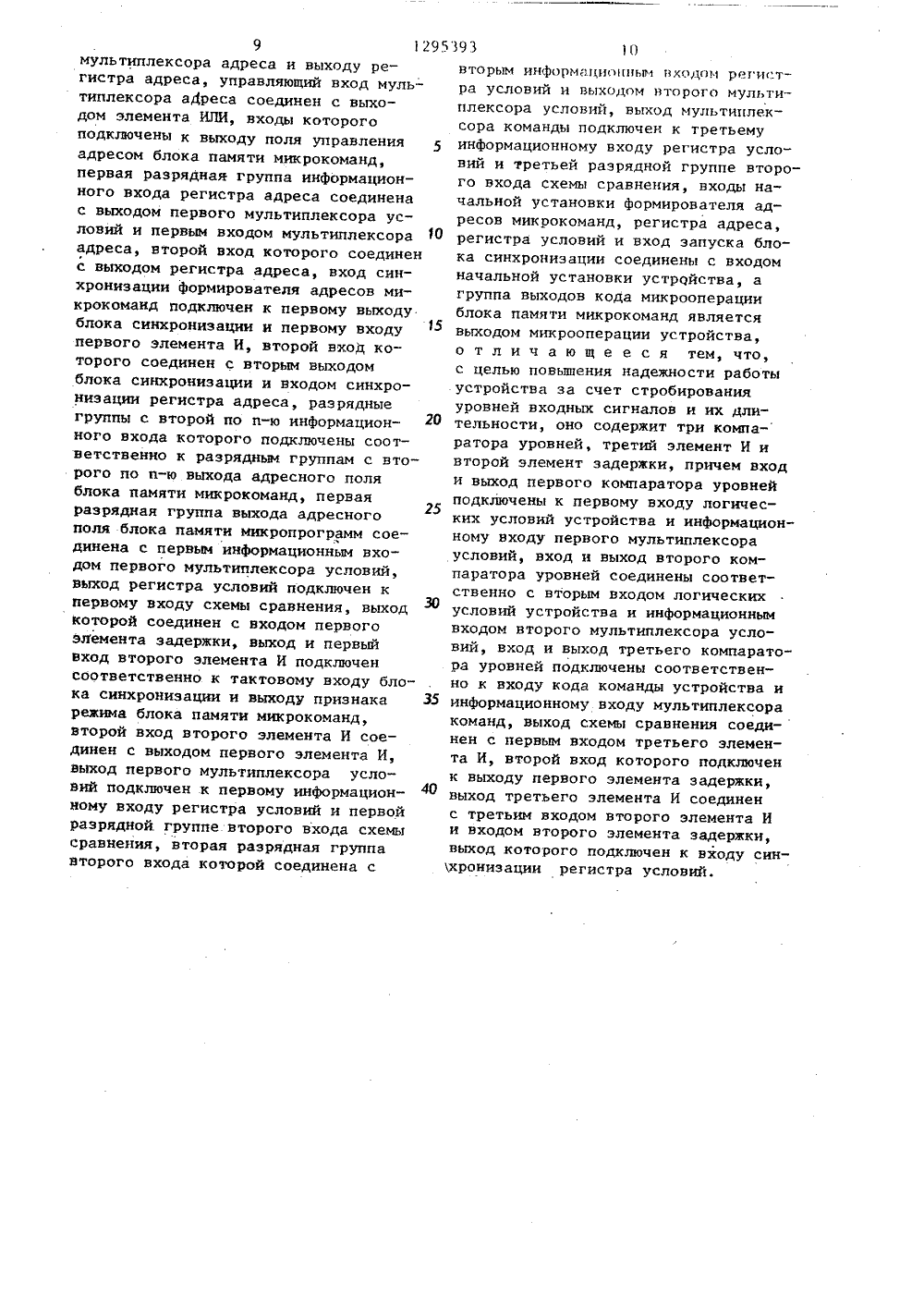

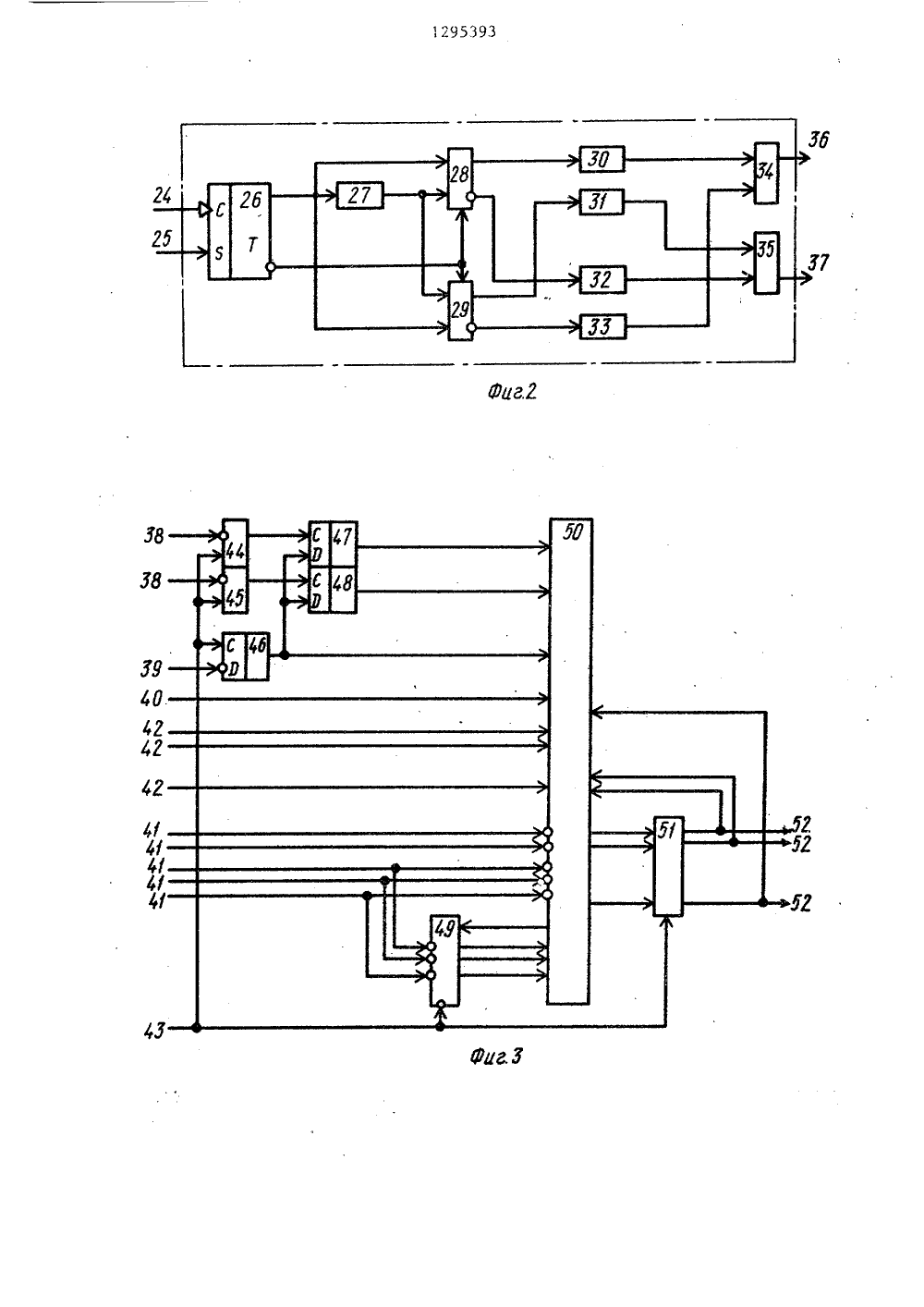

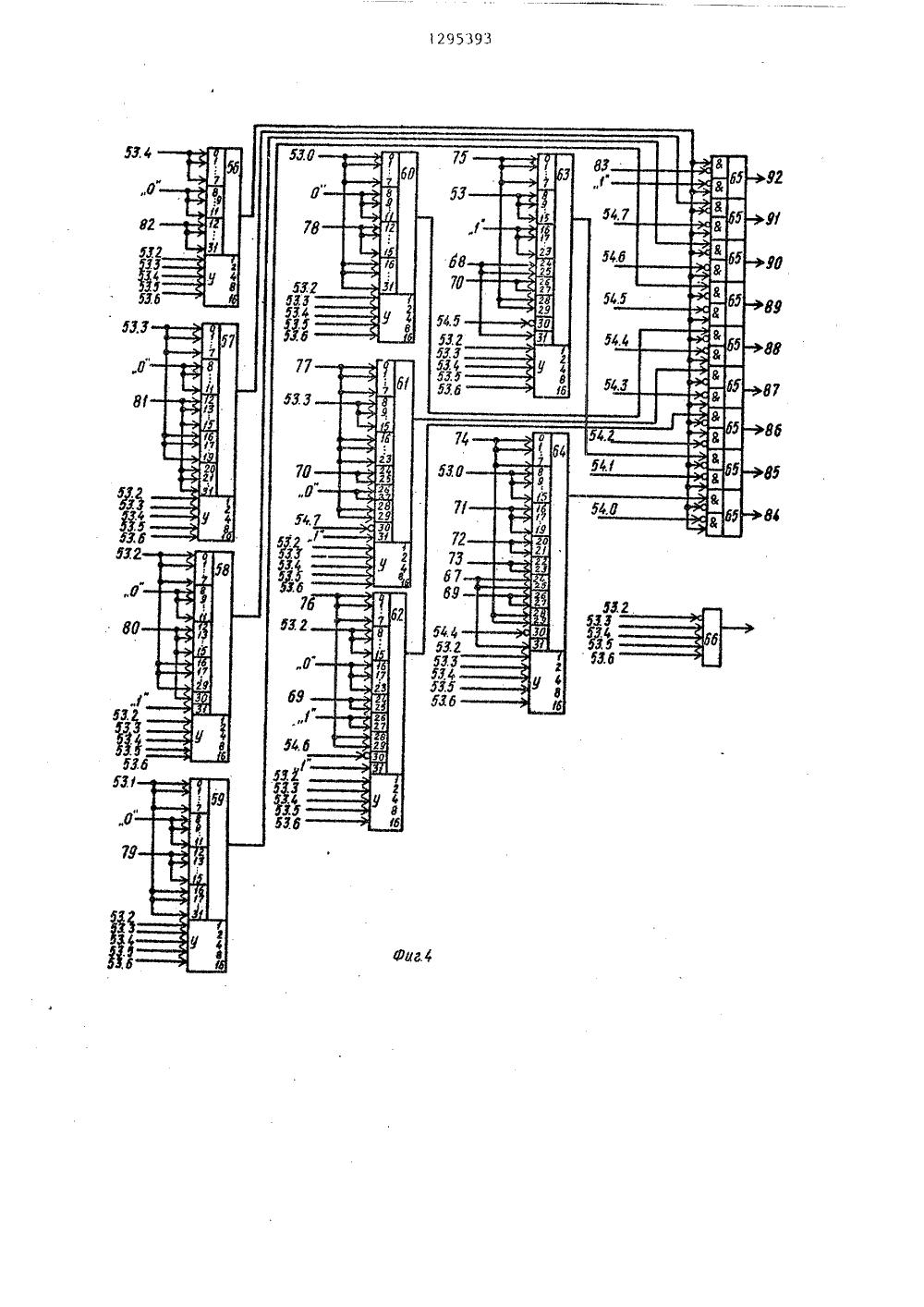

ОПИСАНИЕ ИЗОБРЕТЕНК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ гз гз иг. ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТ(57) Изобретение относится к автомтике и вычислительной технике иможет быть использовано в цифровыхвычислительных системах, а такжетерминальной аппаратуре. Целью изо ретения является повышение надежности работы устройства за счет стробирования уровней входных сигналов иих длительности. С этой целью в устройство, содержащее два мультиплексора 8 и 9 условий, мультиплексор10 команды, мультиплексор 14 адреса,регистр 12 адреса, регистр 13 условий, формирователь 15 адресов микрокоманд, блок 19 памяти микрокоманд,элемент ИЛИ 11, два элемента И 2 и22, элементы 18.1 и 18,2 задержки,схему 16 сравнения и блок 20 синхронизации, введены три компараторауровней, третий элемент И и второйэлемент задержки. 8 ил.1295393 зб Ь г.7 Составител Техред Л.С Виталиев едактор И.Булл 673ственного коми бретений и отк Ж, Раушская аказ 618/55 Тираж ВНИИПИ Госуда по делам из 13035, Москва, Подпис но еССР ет д. 4/5 на приятие, г.ужгород., ул.Проектна ическо Производственно-и Корректор Л. ПилиИзобретение относится к автоматике и вычислительной технике и может быть использдвано в цифровых вычислительных системах, а также терминальной аппаратуре.Целью изобретения является повышение надежности работы устройства за счет стробирования уровней входных сигналов и их длительности.На фиг.1 изображена функциональная схема микропрограммного устройства управления; на Фиг.2 - функциональная схема блока синхронизации; на Фиг.З - функциональная схема Формирователя адресов микрокоманд; на фиг. 4 - схема определения адреса следующей микрокоманды; на Фиг.5 - таблица истинности схемы определения адреса следующей микрокоманды; на фиг.б - формат микрокоманды; на Фиг.7 " временные диаграммы, иллюстрирующие работу устройства; на фиг, 8 - функциональная схема схемы сравнения.Микропрограммное устройство управления (Фиг.1) имеет первый 1 и второй 2 входы логических условий, вход 3 кода команды, вход 4 начальной установки и содержит первый 5, второй б и третий 7 компараторы уровней, первый 8 и второй 9 мультиплексоры условий, мультиплексор 10 команда, элемент ИЛИ 11, регистр 12 адреса и регистр 13 условий, мультиплексор 14 адреса, формирователь 15 адресов микрокоманд, схему 16 сравнения, первый элемент И 1/, первый 18,1 и второй 18.2 элементы задержки, блок 19 памяти микрокоманд, блок 20 синхронизации, второй 21 и третий 22 элементы И, выход 23 микрооперации.Блок синхронизации (фиг,2)имеет вход 24 управления режимом, вход 25 запуска и содержит счетный триггер 26, элемент 27 задержки, первый 28 и второй 29 мультиплексоры, первый 30, второй 31, третий 32 и четвертый 33 генераторы импульсов, первый 34 и второй 35 элементы ИЛИ и второй Зб и первый 37 выходы.Формирователь адресов микрокоманд (фиг.З) имеет вход 38 управления адресным переходом, вход 39 признаков перехода, вход 40 начальной. установки, первый 41 и второй 42 информационные входы, вход 43 синхронизации и содержит первый 44 и второй 45 элементы И, первый 46, второй 47 и третий 48 триггеры, регистр 49 команд, схему 50 определения адреса следующей микрокоманды, регистр 51 адреса и.выход 52.Схема определения следующего адреса (Фиг, 4 и 5) имеет адресные входы 53.0 - 53.6, входы 54,0 - 54.7 команды, выход 55 записи в регистр 49 команд, с первого по девятый мультиплексоры 56-64, девять элементов 2 И-ИЛИ 65, элемент И бб, входы 67 70, соответствующие выходам регистра 49 команд, входы 71 - 73 признаков, соответствующие выходам триггеров 46 - 48, входы 74 - 82, соответствующие выходам регистра 51 адреса, вход 83 начальной установки, соответствующий входу 40 начальной установки на функциональной схеме формирователя 15 (фиг.З), и выходы 84 92.В таблице (фиг.5), иллюстрирующей работу схемы 50 определения адреса следующей микрокоманды, символом "0" ("1") обозначен уровень сигнала на адресном входе или на выходе схе- мы 50, символ Х соответствует безразличному состоянию адресного входа. Символусоответствует единичный уровень в том случае, когда на адресных входах 53.3 - 53.6 схемы 50 присутствуют сигналы единичного уровня, а на.адресном входе 53,2 - сигнал нулевого уровня. В противномслучае символусоответствует нулевой уровень. Символ 11 обозначает уровень счгнала на соответствующем адресном входе или на выходе схемы 50, например 53.2 обозначает уровень сигнала на адресном входе 53.2.Таблица (Фиг.5) показывает зависимость состояний выходов схемы 50 определения адреса следующей микро- команды от состояний ее адресных входов 53,0 - 53.6, состояния сигнала на входе 83 начальной установки, состояний входов 54.0 - 54.7 команды и состояний входов 67. - 82Формат микрокоманды (Фиг,б) содержит шесть полей 93 - 98. Поля 93 и 94 включают группы разрядов микрокоманда, которым соответствуют выходы управления адресным переходом блока 19 памяти микрокоманд, а поле 95 - группу разрядов микрокоманды, которой соответствует выход адресного поля блока 19, и предназначено для формирования адреса следующей микро3 129539 мехи превосходит пороговое значение соответствующего компаратора уровней, и помеха проходит в устройство. Так как сО, то помеха не вызывает изменения режимаработы устройства. В моменты времени С,й и Сю происходят изменения полезных сигналов. Изменения, возникающие в моментыи С, вызывают изменение режима работы устройства, а в момент 1, - 10 нет, так как в последнем случае разряд блокировки блока 19 равен "О".,Рассмотрим работу устройства при выполнении произвольной микрокоманды.По Фронту тактового импульса 106 15 на выходах Формирователя 15 формируется адрес, по которому происходит считывание микрокоманды из блока 19. В соответствии с управляющими сигналами на выходах управления адресным 20 переходом блока 19 на выходах мультиплексоров 8 - 10 присутствует определенная комбинация входных сигналов.В случае несовпадения этой комбн нации и кода, записанного в регистр 13 условий, схема 16 сравнения вырабатывает единичный уровень. Если этот единичный уровень держится по времени меньше 0, то на выходе элемента Зо И 22 присутствует нулевой уровень, Срабатывание схемы 16 вызывается помехой и режим работы устройства не изменяется. Если единичный уровень на выходе схемы 16 держится по времени больше О, то на выходе элемента И 22 возникает единичный уровень, который поступает на вход записи регистра 13, и в него записывается комбинация сигналов с выходов мультиолексоров 8 - 10. Схема 16 вырабатывает сигнал нулевого уровня, который проходит на вход элемента И 22. Таким образом, если имеет место несовпадение кодов на первой и второй группах входов схемы 16, вызванное изменением полезных сигналов, но не помехой, на выходе элемента И 22 вырабатывается единичный импульс, длительность которого определяется элементом 18.2. Единичный импульс с выхода элемента И 22 проходит на выход элемента И 21 и поступает на вход управления режимом блока 20 в том случае, если одновременно выполняются два условия; разряд блокировки имеет единичное значение и сигнал на выходе элемента И 17 имеет единичный уровень, Суть первого условия в том, что микропрограммно разрешается переход к выполнению следующей микрокоманды до завершения полного цикла текущей. Второе условие означает, что оба тактовых сигнала 106 и 107 имеют единичный уровень.Если на выходе элемента И 21 присутствует нулевой уровень, блок 20 синхронизации вырабатывает импульсы 106 и 107 заданной частоты и длительности. В соответствии с кодовой комбинацией на управляющих входах мультиплексора 8 на его выходе присутствует либо один из входных сигналов, либо (при комбинации 000 на управляющих входах) сигнал с первого разряда выхода адресного поля блока 19. Сигнал с выхода мультиплексора 8 поступает на первые информационные входы регистра 12 и мультиплексора 14, Задним фронтом тактового сигнала 107 в регистр 12 осуществляется занесение данных, поступающих на его информационные входы.Элемент ИЛИ 11 производит логическое суммирование значений сигналов на управляющих входах мультиплексора 8. Если на выходе элемента ИЛИ 11 присутствует единичный уровень, то на выход мультиплексора 14 проходит информация с первого его входа, если на выходе элемента ИЛИ 11 - нулевой уровень, то на выход мультиплексора 14 поступает информация с второго его входа, т.е, с первого выхода регистра 12, Таким образом, до. прихода заднего фронта тактового импульса 107 в регистре 12 хранится информация об адресе текущей микрокоманды.По единичному импульсу на входе управления режимом блок 20 Формирует текущий тактовый сигнал 107 и временно снимает тактовый сигнал 106; Исполнение текущей микрокоманды окончено, ее цикл был неполным. В регистре 12 хранится информация об адресе микрокоманды, исполнявшейся до снятия тактового сигнала 106. Так как переходы по условию в устройстве осуществляются под воздействием входных сигналов устройства, то все, кроме первого, разряды регистра 12, которые не связаны с входными сигналами и поэтому не могут быть условиями перехода, используются для Формирования адреса следующей микрокоманды.Назначение элемента ИЛИ 11 и мультиплексора 14 состоит в том, чтобы пропустить на первую разрядную группу второго информационного входа формирователя 15 выбранный мультиплексо ром 8 входной сигнал, который мог измениться за время выполнения микро- команды, или сигнал с первого выхода регистра 12, если условием перехода не является изменение одного из вход 0 ных сигналов, поступающих на вход мультиплексора 8.После паузы блок 20 синхронизации вновь начинает вырабатывать тактовые импульсы 106, по переднему фронту первого из которых происходит формирование адреса следующей микрокомандыРассмотрим работу блока 20 синхронизации (фиг.2).20Для приведения блока в исходное состояние на его вход 25 подается сигнал начальной установки, которым триггер 26 переводится в единичное состояние. Инверсный выход триггера 26, управляющий работой мультиплексоров 28 и 29, пропускает на их прямые выходы сигналы с их первых входов.Генераторы 30 - 33 импульсов вы 30 рабатывают тактовые сигналы в том случае, если на их входах присутствуют сигналы единичного уровня. Таким образом, после появления сигнала начальной установки серии импульсов начинают вырабатывать генераторы 30 и 31 импульсов, так как на их входах присутствуют сигналы единичного уровня. Так как входы генераторов 32 и 33 импульсов связаны с инверсными выходами мультиплексоров 28 и 29 со-. ответственно, на которых присутствуют сигналы нулевого уровня,то после сигнала начальной установки эти генераторы пассивны, а на их выходах - сигналы нулевого уровня.Сигналы с выходов генераторов 30 и 33, а также сигналы с выходов генераторов 31 и 32 логически суммируются на элементах ИЛИ 34 и 35 соответственно. С выходов элементов ИЛИ 34 и 35 сигналы передаются на выходы 36 и 37 блока соответственно. В таком режиме блок 20 работает до появления импульса на входе 24 блока. С входа 24 блока импульс поступает на счетный вход триггера 26, в результате триггер 26 перебрасывается в нулевое состояние, тем самым открывая передачу с вторых входов мультиплексоров 28 и 29 на их выходы. В итоге на инверсном выходе мультиплексора 29 появляется сигнал единичного уровня и с задержкой, определяемой элементом 27, после того появляется сигнал единичного уровня на инверсном выходе мультиплексора 28. Таким образом, с приходом первого единичного импульса на вход 24 блока в работе блока 20 синхронизации происходят, следующие изменения: прекращает вырабатывать тактовые сигналы генератор 31 импульсов, начинает вырабатывать тактовые сигналы генератор 33 импульсов, затем с задержкой прекращает вырабатывать импульсы ге-. нератор 30 импульсов и начинает вырабатывать импульсы генератор 32 импульсов.В этом режиме блок 20 синхронизации работает до появления на его входе 24 следующего импульса, Далее блок 20 функционирует аналогично указанному. Сигналы с выходов всех генераторов 30 - 33 импульсов имеют одинаковые параметры,Формула изобретения Микропрограммное устройство управления, содержащее два мультиплексора условий, мультиплексор команды, мультиплексор адреса, регистр адреса, регистр условий, формирователь адресов микрокоманд, блок памяти микро- команд, элемент ИЛИ, два элемента И, первый элемент задержки, схему сравнения и блок синхронизации, причем управляющие входы первого и второго мультиплексоров условий, мультиплексора команды и вход управления переходом формирователя адресов микрокоманд подключены к одновременным выходам поля управления адресом блока памяти микрокоманд, адресный вход которого соединен с выходом формирователя адресов микрокоманд, первый информационный вход, вход признаков перехода, первая разрядная группа второго информационного входа и разрядные группы с второй по и-ю второго информационного входа которого ,где и - число разрядов адресного поля блока памяти микрокоманд) подключены соответственно к выходу мультиплексора команды, выходу второго мультиплексора условий, выходу9 12953мультиплексора адреса и выходу регистра адреса, управляющий вход мультиплексора адреса соединен с выходом элемента ИЛИ, входы которогоподключены к выходу поля управленияадресом блока памяти микрокоманд,первая разрядная группа информационного входа регистра адреса соединенас выходом первого мультиплексора условий и первым входом мультиплексора 0адреса, второй вход которого соединенс выходом регистра адреса, вход синхронизации формирователя адресов микрокоманд подключен к первому выходублока синхронизации и первому входупервого элемента И, второй вход которого соединен с вторым выходомблока синхронизации и входом синхронизации регистра адреса, разрядныегруппы с второй по и-ю информационного входа которого подключены соответственно к разрядным группам с второго по и-ю выхода адресного поляблока памяти микрокоманд, перваяразрядная группа выхода адресного25поля блока памяти микропрограмм соединена с первым информационным входом первого мультиплексора условий,выход регистра условий подключен кпервому входу схемы сравнения, выходкоторой соединен с входом первогоэлемента задержки, выход и первыйвход второго элемента И подключенсоответственно к тактовому входу блока синхронизации и выходу признака 35режима блока памяти микрокоманд,второй вход второго элемента И соединен с выходом первого элемента И,выход первого мультиплексора условий подключен к первому информацион Оному входу регистра условий и первойразрядной группе второго входа схемысравнения, вторая разрядная группавторого входа которой соединена с вторым информационным водом реГ и тра условий и выходом второго мультиплексора условий, выход мультиплексора команды подключен к третьемуинформационному входу регистра условий и третьей разрядной группе второго входа схемы сравнения, входы начальной установки формирователя адресов микрокоманд, регистра адреса,регистра условий и вход запуска блока синхронизации соединены с входомначальной установки устройства, агруппа выходов кода микрооперацииблока памяти микрокоманд являетсявыходом микрооперации устройства,о т л и ч а ю щ е е с я тем, что,с целью повышения надежности работыустройства за счет стробированияуровней входных сигналов и их длительности, оно содержит три компаратора уровней, третий элемент И ивторой элемент задержки, причем входи выход первого компаратора уровнейподключены к первому входу логических условий устройства и информационному входу первого мультиплексораусловий, вход и выход второго компаратора уровней соединены соответственно с вторым входом логическихусловий устройства и информационнымвходом второго мультиплексора условий, вход и выход третьего компаратора уровней подключены соответственно к входу кода команды устройства иинформационному входу мультиплексоракоманд, выход схемы сравнения соединен с первым входом третьего элемента И, второй вход которого подключенк выходу первого элемента задержки,выход третьего элемента И соединенс третьим входом второго элемента Ии входом второго элемента задержки,выход которого подключен к входу синхронизации регистра условий.

СмотретьЗаявка

3952806, 06.09.1985

ПРЕДПРИЯТИЕ ПЯ Р-6380

МИРЕЦКИЙ ИГОРЬ ЮРЬЕВИЧ, ПЫЖОВ ГЕННАДИЙ ВЕНИАМИНОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммное

Опубликовано: 07.03.1987

Код ссылки

<a href="https://patents.su/10-1295393-mikroprogrammnoe-ustrojjstvo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство для выбора запросов по приоритетам

Случайный патент: Электрический разъем с нулевым усилием стыковки