Преобразователь последовательного двоичного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

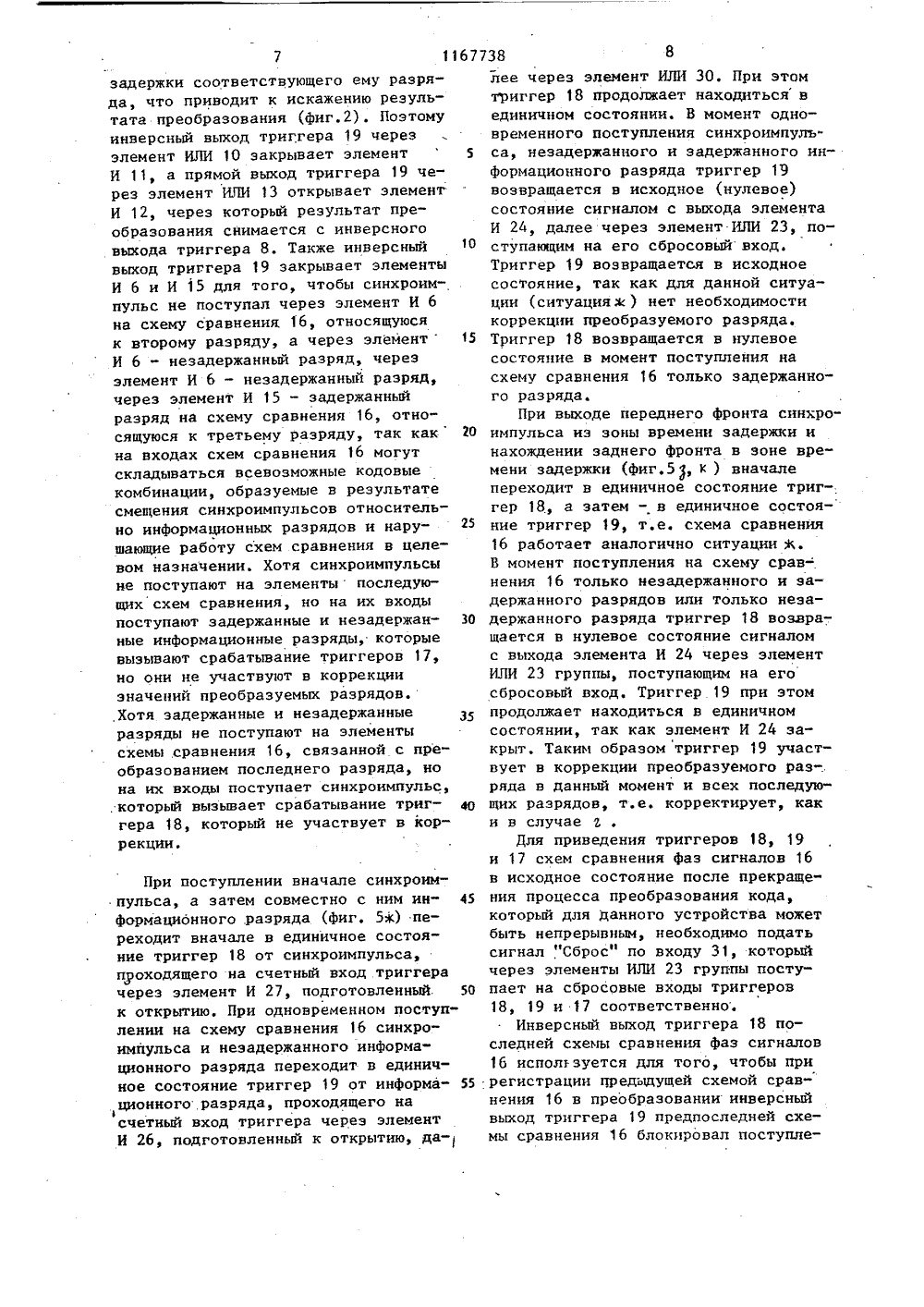

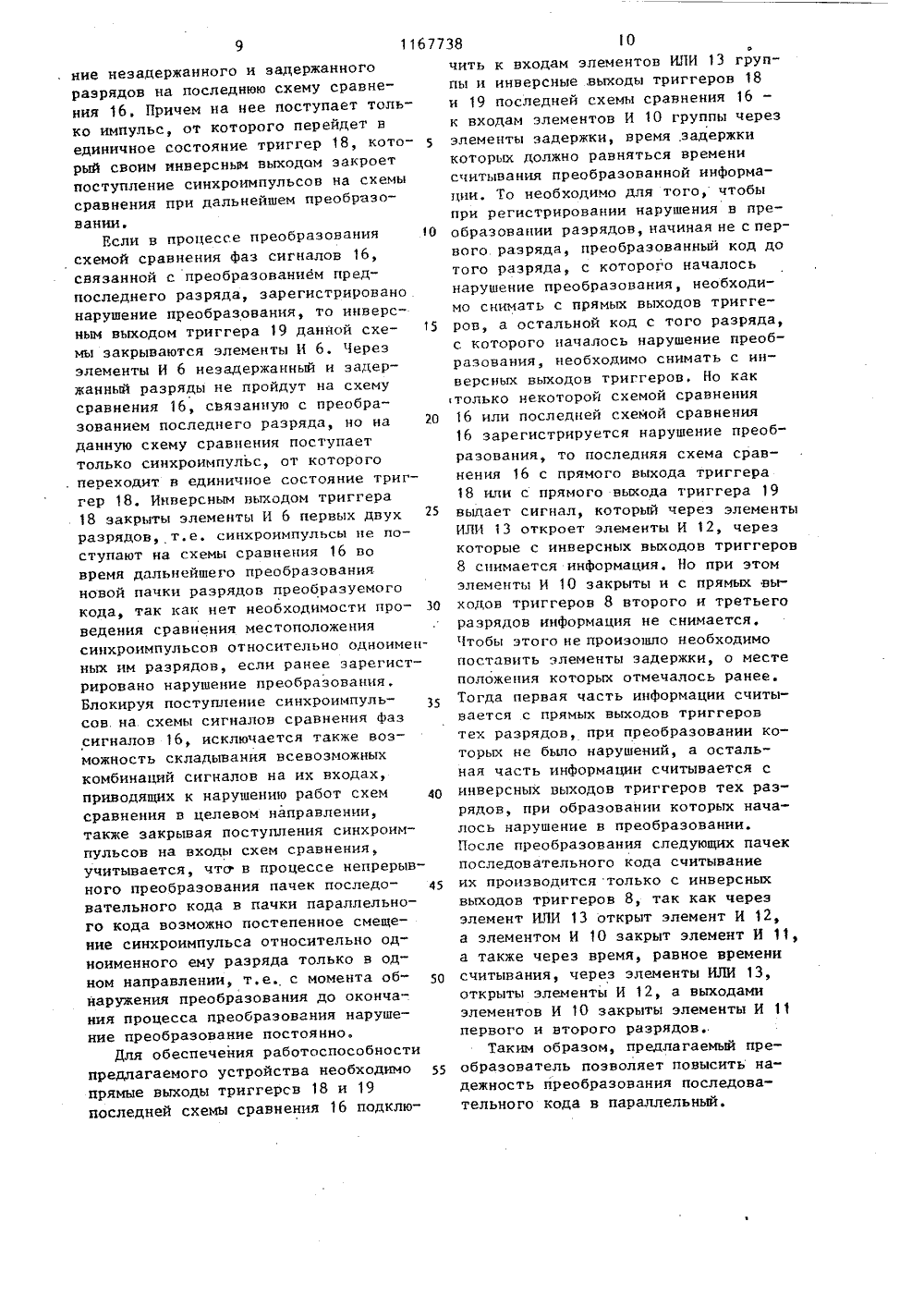

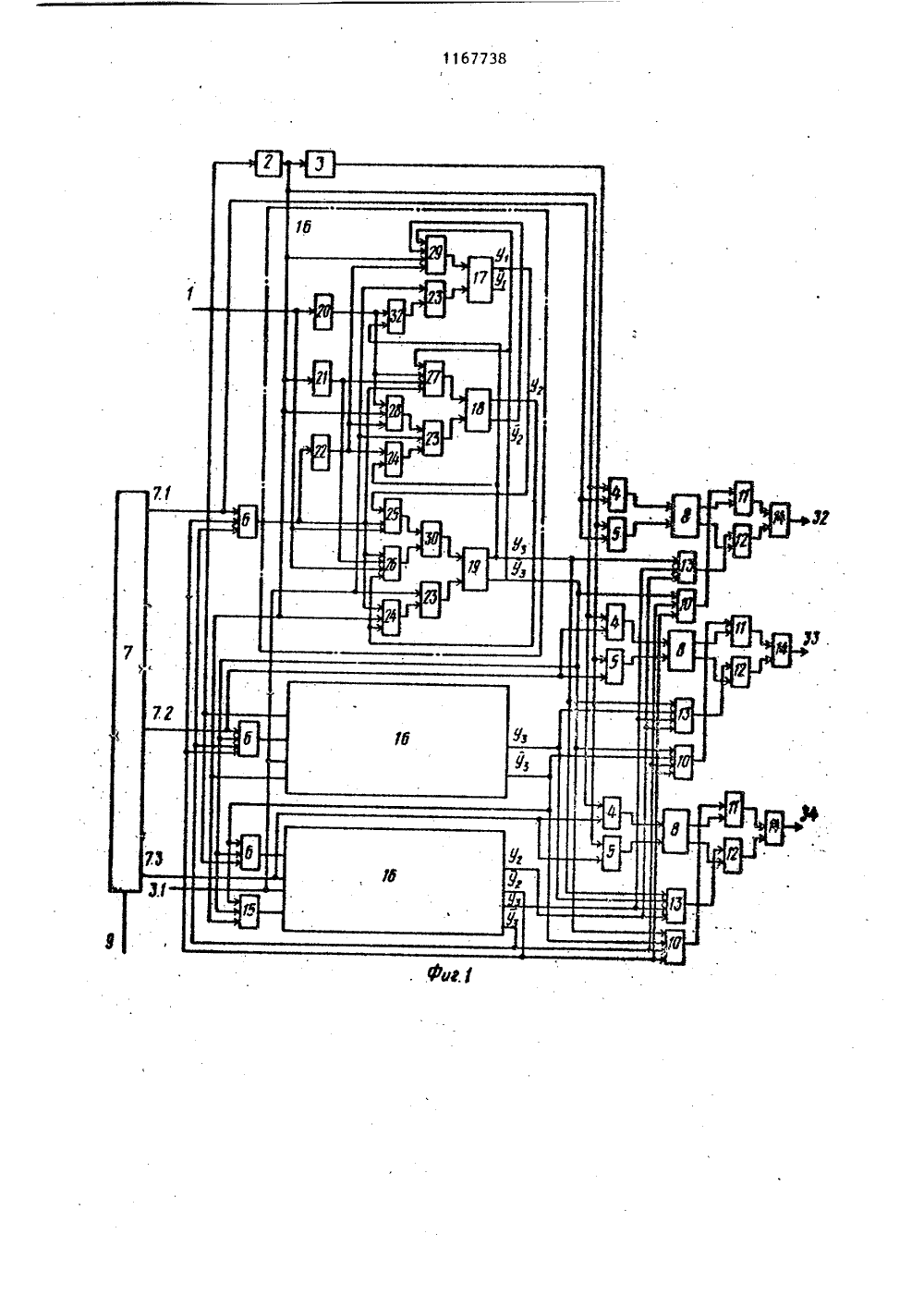

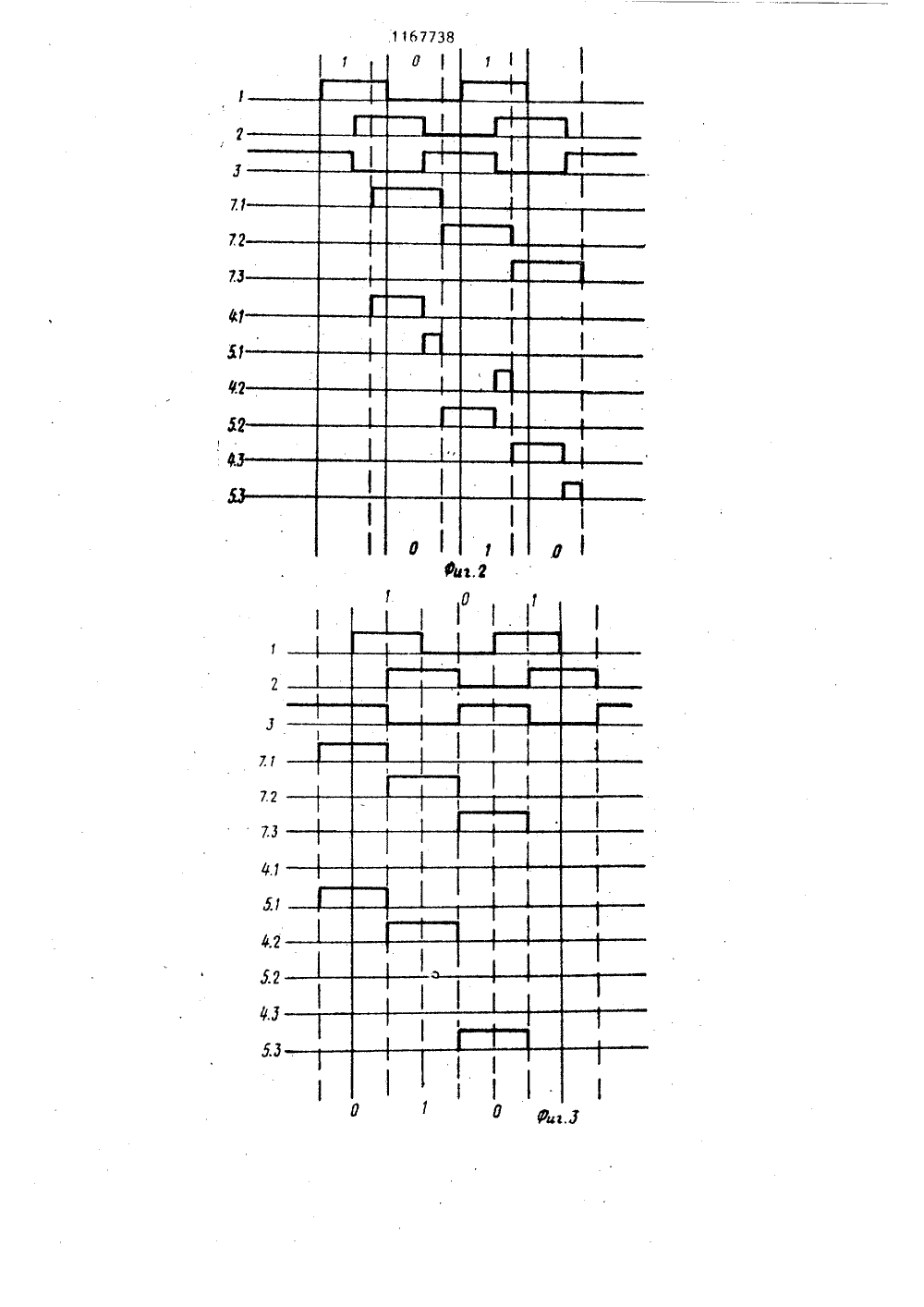

(56) Авторское свидВ 225553, кл. С 06Авторское свидетВ 354410, кл. Н ОЗ 26 Кузне ельство СССР 5/04, 1967. ьство СССР 13/243, 1972 ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ АВТОРСКОМ.К СВИДЕТЕЛЬС(54)(57) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ, содержащий группу триггеров,первую и вторую группы элементов И,распределитель импульсов, элемент НЕи элемент задержки, вход которогосоединен с информационным входом преобразователя, а выход - с входом элемента НЕ и с первыми входами элементов И первой группы, вторые входыкоторых соединены с соответствующимивыходами распределителя импульсов ис первыми входами соответствующихэлементов И второй группы, вторыевходы которых соединены с выходомэлемента НЕ, выходы элементов И первой и второй групп соединены соответственно с единичными и нулевыми входами триггеров группы, вход синхронизации преобразователя соединен с входом запуска распределителя импульсов,о т л и ч а ю щ и й с я тем, что, сцелью повышения функциоиальной возможности преобразователя за счетобеспечения преобразования при произвольных задержках информационныхсигналов и сигнала синхронизации,. внего дополнительно введены четырегруппы элементов И, первая и втораягруппы элементов ИЛИ, элемент И и группа схем сравнения фаз сигналов,каждая из которых содержит три триггера, три элемента НЕ, группу изтрех элементов ИЛИ, группу из трехэлементов И, пять элементов И и эле"мент ИЛИ, причем вход сброса преобразователя соединен с входами сбросавсех схем сравнения фаз сигналовгруппы, а выход элемента задержкисоедцнец с информационными задержанными входами всех схем сравненияфаз сигналов группы, кроме последней,и с первым входом элемента И, выходкоторого соединен с информационнымзадержанным входом последней схемысравнения фаз сигналов группы, тактовые входы всех схем сравценця фазсигналов группы, кроме последней,соединены с выходами соответствующихэлементов И третьей группы, первыевыходы которых соединены с соответствующими выходами распределителя импульсов, последний выход распределителя импульсов соединен с тактовымвходом последней схемы сравнения фазсигналов группы, первый и второй ицверсные выходы которой соединенысоответственно с первыми и вторымивходами элементов И четвертой группыи соответственно с вторыми ц третьими входами элементов И третьей группы,кроме последнего элемента Итретьей группы, первый вход которогосоединен с информационным входом преобразователя и с информационными входами всех схем сравнения фаз сигналов группы, кроме последней, информационный вход которой соединен свыходом последнего элемента И третьейгруппы, первый"инверсный выход-й11 б 7738 7.1 Составитель М. Аршавскийедактор М. Митейко Техред О.Ващишина Корректо охма Заказ 4445/54 кая наб., д. 4 Филиал ППП "Патент", г. Ужгород, ул. Проектно Тираж 872ИИПИ Государственного к по делам изобретений и 035, Москва, Ж, Рау Подпитета СССРткрытий11 б 7738 схемы сравнения фаэ сигналов группы (= 1 п), где и - число разрядов преобразуемого кода, соединен с четвертыми входами"х ( 1 о) элементов И третьей группы и с (+2)-ми входами-х элементов И четвертойчгруппы, выходы которых соединены с первыми входами соответствующих элементов И пятой группы, вторые входы которых соединены с единичными выходами соответствующих триггеров группы, нулевые выходы которых соединены с первыми входами соответствующих элементов И шестой группы, вторые входы которых соединены с выходами соответствующих элементов ИЛИ первой группы, первый и второй входы которых соединены соответственно с первым прямым и вторым прямым выходами п -й схемы сравнения фаз сигналов группы, прямой выход-й схемы сравнения фаэ сигналов группы соединен с (+2)-миВвходами-х элементов ИЛИ первой группы, выходы элементов И пятой и шестой групп соединены с первыми и вторыми входами соответствующих элементов ИЛИ второй группы, выходы которых являются выходами преобразователя, первый инверсный выход -й схемы сравнения фаэ сигналов группы соединен с ( +1)-м входом П-го элемента И третьей группы и с (+1)-м входом элемента И, причем в каждой из схем сравнения фаз сигналов группы информационный вход соединен с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, а через первый элемент НЕ информационный вход схемы сравнения фаз сигналов соединен с первым входом первого элемента И группы, тактовый вход соединен с вторыми входами перИзобретение относится к вычислительной технике и предназначено для систем передачи данных с временным разделением каналов.Целью изобретения является повышение функциональной надежности за вого и второго элементов И, первымвходом третьего элемента И, первымвходом второго элемента И группы, а,через второй элемент НЕ - с.первымвходом третьего элемента И группы ипервыми входами четвертого и пятогоэлементов И, вторые входы которыхсоединены с информационными задержанными входом схем сравнения фазсигналов и вторым входом второго элемента И группы и через третий элемент НЕ - с вторыми входами второгои третьего элементов И, выходы элементов И группы соединены с первымивходами соответствующих элементовИЛИ группы, вторые входы которых соединены с входом сброса, а выходы которых соединены с информационнымивходами соответствующих триггеров,счетный вход первого триггера соединен с выходом пятого элемента И, третий и четвертый входы которого соединены соответственно с инверсными выходами второго и третьего триггеров,счетные входы которых соединены соответственно с выходами первого элемента ИЛИ и третьего элемента И, третий вход которого соединен с инверсным выходом второго триггера, а четвертый вход соединен с выходом первого элемента НЕ и с третьим входомчетвертого элемента И, выход которого соединен с третьим входом третьегоэлемента ИЛИ группы, прямой выходпервого триггера соединен с третьимвходом первого элемента И, прямойвыход второго триггера соединен свторыми входами первого и второгоэлементов И группы, прямой и инверсный выходы второго и третьего триггеров соответственно являются первымии вторыми прямыми и инверсными выходами схемы сравнения фаз сигналов. счет обеспечения преобразования при произвольных задержках информационных сигналов и сигнала синхронизации.На фиг. 1 приведена функциональная схема преобразователя; на фиг.2, 3 и 4 - временные диаграммы его работы, где цифровые обозначения показывают принадлежность диаграмм ксоответствующему элементу схемы,Преобразователь последовательногокода в параллельный соедржит информационный вход 1 преобразователя, элемент задержки 2, элемент НЕ 3, группы элементов И 4, 5 и 6, распределитель импульсов 7, группу триггеров 8,вход 9 синхронизации преобразователя1 Осоединен с входом запуска распределителя импульсов, группы элементовИ 10 - 12, первую и вторую группыэлементов ИЛИ 13 и 14, элемент И 15и группу схем сравнения фаз сигналов 16. Каждая из схем сравнения фазсигналов содержит триггеры 17 - 1.9,элементы НЕ 20 - 22, группу элементов ИЛИ 23, группу элементов И 24,элементы И 25 - 29.и элемент ИЛИ 30. 2 ОВходы сброса схем сравнения фаз сигналов 16 соединены с входом сбросапреобразователя 31. Выходы элементовИЛИ 14 соединены с выходами 32 - 34преобразователя. 25На временной диаграмме (фиг.5)представлены только первые разряды иих синхроимпульсы, так как этогодостаточно для отражения существаработы устройства. Взят крайний случай, т.е. длительность символа равнадлительности синхроимпульса,Устройство для преобразования последовательного двоичного кода работает следующим образом. 15Сигнал информационной последовательности с длительностью импульса,равной длительности символа (телеграфный сигнал), поступает на вход 1 ина элемент задержки 2. С выхода эле- Омента НЕ 3 снимается инверсный сигналеКогда взаимный сдвиг синхроимпульсов и информационных сигналов не превышает предела задержки, создаваемо- бго элементом задержки 2 (ситуации,обозначенные о, 3, Ь на фиг. 5),. тозадержанные прямой и инверсный сигналы поступают на элементы И 4 и 5,щичем прямой сигнал поступает на Оэлементы И 4 группы,;инверсный - наэлементы И 5 группы. На вторые входыданных элементов Й поступают синхроимпульсы, поступающие с распределителя импульсов, а с выходов элементов 5И 4 и 5 выходные сигналы поступаютна входы установки 1 и 0 триггеров 8соответственно. В триггер каждого иэ Разрядов в течение первой половиныдлительности соответствующего спнхроимпульса может записываться ложный,т,е. соответствующий соседнему разряду, сигнал, но в течение второй поло"вины записывается сигнал, соответствующий значению данного.Нри этом триггеры 18, 19 и 17схем сравнения фаз сигналов 16 находятся в нулевом состоянии, хотя ипоступают прямые информационные разряды на элемент И 26, а синхроимпульсы поступают на вход элемента И 25, ноне проходят через них на счетныйвход триггера 19, так как элементИ 26 закрыт прямым выходом триггера18, а элемент И 25 - прямым выходомтриггера 17, До поступления информации на устройство преобразованиятриггеры 17, 18 и 19 схем сравненияфаз сигналов 16 находятся в .нулевомсостоянии, а элементы И 29 подготовлены.к открытию инверсными выходамитриггеров 18 и 19.и выходом элементаНЕ 22, элементы И 27 годготовлены коткрытию инверсным выходом триггера19 и выходами элементов НЕ 20 и 21.Элементы И 25 закрыты прямыми выхода"ми триггеров 17, элементы И 26 подготовлены к открытию выходами элементов НЕ 21, элементы И 24 закрыты прямыми выходами триггеров 19 и18. При одновременном поступленииинформационного разряда и синхроимпульса на преобразователь они поступают на входы элементов И 25, И 26,И 27, И 25, И 26, И 24, но не пройдут через них на счетные входы триггеров 18 и 19, так как элемент И 27закроется выходом элемента НЕ 20,,на входе которого присутствует информационный сигнал, элементы И 25и 26 продолжают находиться в закрытом состоянии, так как триггеры 18и 17 находятся в нулевом состояниии элемент И 29 закрывается выходомэлемента НЕ 22, на входе которогоприсутствует синхроимпульс. При появлении информационного разрядасигнал с выхода .элемента задержки2 на входах И 29 и 24 не пройдет через них, также сигнал с выхода элемента задержки 2 появится на входеэлемента ЧЕ 21,который выходомзакроет элементы И 27 и 26,После исчезновения информационного разряда и синхроимпульса продолжает присутствовать информационный50 сигнал с выхода элемента задержки 2, но и он не проходит черезэлементы И 29 и 24, так как они продолжают находиться закрытыми.Таким образом, для данной ситуа ции (фиг. я) триггеры 18,. 19 и 17 со схем сравнения 16 находятся в нулевом состоянии.Инверсным выходом триггера 19 открыт элемент И 10, через который снимается результат преобразования с прямого выхода триггера 8. С выхода элемента И 5 результат далее через элемент. И 12 поступает на выход 34 преобразователя5При отставании. переднего фронта синхроимпульсов от информационных разрядов в пределах времени задержки (фиг. 5) вначале поступают информационные разряды, которые посту лают на входы элементов И 25 и 26, но не проходят через них на счетный вход триггера 19, Затеи одновременно с информационным разрядом появляется синхроимпульс, для которого схема 25 сравнения 16 ведет себя аналогично как для ситуации, представленной на фиг, 5 а. Далее незадержанный информационны 1 разряд исчезает, но одновременно с задержанным информационным ЗО разрядом продолжает присутствовать синхроимпульс. Задержанный разряд не проходит через закрытые элементы И 29 и 24 на счетные выходы триггеров 19 и 17, так как элемент И 29 закрыт выходом элемента НЕ 22, на 1 входе которого присутствует синхроимпульс, а элемент 24 закрыт прямым выходом триггера 18, так как на его счетном входе отсутствует сиг нал с выхода элемента И 27, закрытого выходом элемента НЕ 21, на входе которого в этот момент присутствует сигнал с выхода элемента задержки 2. Синхроимлульс также не проходит через 45 элементы И 25 и 26. При наличии только синхроимпульса триггеры 1819 и 17 схемы сравнения 16 не сработают аналогично ситуации , представленной на фиг. 5. Преобразованная информация снимается с прямого выхода триггера 8 через элементы 11, ИЛИ 14, так как триггер 19 находится в нулевом состоянии.При совпадении синхроимпульса с 55 задержанным информациьиным разрядом (фиг. 5 В ) триггеры 18, 19 и 17 схемы сравнения 16 не сработают, аналогично ситуациями 5 , представленным на Фиг. 5, и преобразованная информация снимается аналогично как в ранее рассмотренных ситуациях.При выходе переднего фронта синхроимпульса иэ зоны времени задержки (Фиг. 5 г ) вначале появляется информационный разряд. При этом все триггеры схемы сравнения 16 находятся в нулевом состоянии аналогично ранее рассмотренным ситуациям а, Р фиг. 5, Затем одновременно появляется незадержанный и задержанный информа- . ционные разряды. При этом задержанный разряд проходит через элемент И 29, открытый выходом элемента НЕ 22, на счетный вход триггера 17, который переходит в единичное состояние и своим прямым выходом подготавливает к открытию, элемент И 25. Когда одновременно появляются незадержанный разряд и синхроимпульс, то синхроимпульс и незадержанный информационный разряд проходят через элемент И 25, далее через элемент ИЛИ 30 на счетный вход триггера 19, который переходит в единичное состояние и своим прямым выходом подготавливает к открытию элемент И 24. При этом триггер 7 продолжает находиться в нулевом сос" тоянии, так как элемент И 24 по другому входу закрыт выходом элемента НЕ 20. После исчезновения незадержанного информационного разряда продолжают одновременно присутствовать задержанный информационный разряд и синхроимпульс. В момент исчезновения незадержанного информационного разряда с входа элемента НЕ 20 открывается элемент И 24, через который с прямого выхода триггера 9 проходит сигнал, далее проходит через элемент ИЛИ 23 на сбросовый .вход триггера 17 и переводит его в нулевое состояние. После исчезновения задержанного ин-. формационного разряда продолжает присутствовать синхроимпульс, который не проходит через элемент И 27, закрытый инверсным выходом триггера 19, не проходит через элементы И 25, 26 и 24, закрытые прямым выходом триггера 17, Когда отсутствуют сигналы на входах элементов схемы сравнения 16, то триггер 19 продолжает находиться в единичном состоянии, что свидетельствует о том, что зарегистрирован выход переднего фронта синхроимпульса из области времени1167задержки соответствующего ему разряда, что приводит к искажению результата преобразования (фиг.2). Поэтомуинверсный выход триггера 19 черезэлемент ИЛИ 10 закрывает элемент5И 11, а прямой выход триггера 19 через элемент ИЛИ 13 открывает элементИ 12, через который результат пре"образования снимается с инверсноговыхода триггера 8. Также инверсныйвыход триггера 19 закрывает элементыИ 6 и И 15 для того, чтобы синхроимпульс не поступал через элемент И 6на схему сравнения 16, относящуюсяк второму разряду, а через элемент5И 6 - незадержанный разряд, черезэлемент И 6 - незадержанный разряд,через элемент И 15 - задержанныйразряд на схему сравнения 16, относящуюся к третьему разряду, так как20на входах схем сравнения 6 могутскладываться всевозможные кодовыекомбинации, образуемые в результатесмещения синхроимпульсов относительно информационных разрядов и нарушающие работу схем сравнения в целевом назначении. Хотя синхроимпульсыне поступают на элементы последующих схем сравнения, но на их входыпоступают задержанные и незадержанные информационные разряды, которыевызывают срабатывание триггеров 17,но они не участвуют в коррекциизначений преобразуемых разрядов.Котя задержанные и незадержанныеразряды не поступают на элементысхемы .сравнения 16, связанной с преобразованием последнего разряда, иона их входы поступает синхроимпульс,.который вызывает срабатывание триггера 18, который не участвует в коррекции,При поступлении вначале синхроимпульса, а затем совместно с ним ин формационного .разряда (фиг. 5) переходит вначале в единичное состояние триггер 18 от синхроимпульса, пуоходящего на счетный вход триггера через элемент И 27, подготовленный. 50 к открытию. При одновременном поступлении на схему сравнения 16 синхроимпульса и неэадержанного информационного разряда переходит в единичное состояние триггер 19 от информа ционного разряда, проходящего на счетный вход триггера через элемент И 26, подготовленный к открытию, да 738 8лее через элемент ИЛИ 30. При этомтриггер 18 продолжает находиться вединичном состоянии. В момент одновременного поступления синхроимпуль"са, незадержанного и задержанного информационного разряда триггер 19возвращается в исходное (нулевое)состояние сигналом с выхода элементаИ 24, далее через элемент ИЛИ 23, поступающим на его сбросовый вход.Триггер 19 возвращается в исходноесостояние, так как для данной ситуации (ситуацияй ) нет необходимостикоррекции преобразуемого разряда.Триггер 18 возвращается в нулевоесостояние в момент поступления насхему сравнения 16 только задержанного разряда.При выходе переднего фронта синхроимпульса иэ зоны времени задержки инахождении заднего фронта в зоне времени задержки (фиг.5 , к ) вначалепереходит в единичное состояние триггер 18, а затем - в единичное состоя-ние триггер 19, т.е. схема сравнения16 работает аналогично ситуации Ж,В момент поступления на схему срав-нения 16 только неэадержанного и задержанного разрядов или только незадержанного разряда триггер 18 возвращается в нулевое состояние сигналомс выхода элемента И 24 через элементИЛИ 23 группы, поступающим на егосбросовый вход. Триггер 19 при этомпродолжает находиться в единичномсостоянии, так как элемент И 24 закрыт, Таким образом триггер 19 участвует в коррекции преобразуемого раз-.ряда в данный момент и всех последующих разрядов, т.е. корректирует, каки в случае 2,Для приведения триггеров 18, 19и 17 схем сравнения фаз сигналов 16в исходное состояние после прекраще"ния процесса преобразования кода,который для данного устройства можетбыть непрерывным, необходимо податьсигнал "Сброс" по входу 31, которыйчерез элементы ИЛИ 23 группы поступает на сбросовые входы триггеров18, 19 и 17 соответственно.Инверсный выход триггера 18 последней схемы сравнения фаз сигналов16 используется для того, чтобы прирегистрации цредыдущей схемой сравнения 16 в преобразовании инверсныйвыход триггера 19 предпоследней схемы сравнения 16 блокировал поступле1167738 10чить к входам элементов ИЛИ 13 группы и инверсные, выходы триггеров 18и 19 последней схемы сравнения 16 -к входам элементов И 10 группы черезэлементы задержки, время задержкикоторых должно равняться временисчитывания преобразованной информации. То необходимо для того, чтобыпри регистрировании нарушения в преО образовании разрядов, начиная не с первого разряда, преобразованный код дотого разряда, с которого началосьнарушение преобразования, необходимо снимать с прямых выходов тригге 15 рон, а остальной код с того разряда,с которого началось нарушение преобразования, необходимо снимать с инверсных выходов триггеров, Но кактолько некоторой схемой сравнения20 16 или последней схемой сравнения16 зарегистрируется нарушение преобние незадержанного и задержанногоразрядов на последнюю схему сравнения 16, Причем на нее поступает только импульс, от которого перейдет нединичное состояние триггер 18, который своим инверсным выходам закроетпоступление синхроимпульсов на схемьсравнения при дальнейшем преобразовании.Если н процессе преобразованиясхемой сравнения фаз сигналов 16,связанной с преобразованием предпоследнего разряда, зарегистрированонарушение преобразования, то инверсным выходом триггера 19 данной схемы закрываются элементы И б, Черезэлементы И 6 незадержанный и задержанный разряды не пройдут на схемусравнения 16, связанную с преобразованием последнего разряда, но наданную схему сравнения поступаеттолько синхроимпульс, от которого. переходит в единичное состояние триггер 18. Инверсным выходом триггера18 закрыты элементы И 6 первых двух 25разрядов, т,е. сицхроимпульсы це поступают на схемы сравнения 16 вовремя дальнейшего преобразования.новой пачки разрядов преобразуемогокода, так как нет необходимости проведения сравнения местоположениясинхроимпульсов относительно одноименных им разрядов, если ранее зарегистрировано нарушение преобразования,Блокируя поступление синхроимпульсов. на схемы сигналон сравнения Фазсигналов 16, исключается также возможность складывания всевозможныхкомбинаций сигналов на их входах,приводящих к нарушению работ схем 40сравнения в целевом направлении,также закрывая поступления синхроимпульсов на входы схем сравнения,учитывается, чтс в процессе непрерывного преобразования пачек последовательного кода в пачки параллельного кода возможно постепенное смещение синхроимпульса относительно одноименного ему разряда только в одном направлении, т.е. с момента обнаружения преобразования до окончания процесса преобразования нарушение преобразование постоянно,Для обеспечения работоспособностипредлагаемого устройства необходимо 55прямые выходы триггерсв 18 и 19последней схемы сравнения 16 подклюразования, то последняя схема сравнения 16 с прямого выхода триггера18 или с прямого выхода триггера 19выдает сигнал, который через элементыИЛИ 13 откроет элементы И 12, черезкоторые с инверсных выходов триггеров8 снимается информация, Но при этомэлементы И 10 закрыты и с прямых ныходов триггеров 8 второго и третьегоразрядов информация не снимается,Чтобы этого не произошло необходимопоставить элементы задержки, о местеположения которых отмечалось ранее,Тогда первая часть информации считывается с прямых выходов триггеровтех разрядов, при преобразовании которых не было нарушений, а остальная часть информации считывается синверсных выходов триггеров тех разрядов, при образовании которых началось нарушение в преобразовании.После преобразования следующих пачекпоследовательного кода считываниеих производится только с инверсныхвыходов триггеров 8, так как черезэлемент ИЛИ 13 открыт элемент И 12,а элементом И 10 закрыт элемент И 11,а также через время, равное временисчитывания, через элементы ИЛИ 13,открыты элементы И 12, а выходамиэлементов И 10 закрыты элементы И 11первого и нторого разрядовТаким образом, предлагаемый преобразователь позволяет повысить надежность преобразования последовательного кода в параллельный.

СмотретьЗаявка

3695036, 27.01.1984

СЕРПУХОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ ИМ. ЛЕНИНСКОГО КОМСОМОЛА

УЛАСЕВИЧ СЕРГЕЙ ВЛАДИМИРОВИЧ, КУЗНЕЦОВ ОЛЕГ ПАВЛОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: двоичного, кода, параллельный, последовательного

Опубликовано: 15.07.1985

Код ссылки

<a href="https://patents.su/10-1167738-preobrazovatel-posledovatelnogo-dvoichnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного двоичного кода в параллельный</a>

Предыдущий патент: Преобразователь двоичного кода в двоично-десятичный

Следующий патент: Приемник частотно-модулированного сигнала

Случайный патент: Устройство для контроля поверхностной плотности текстильных материалов