Преобразователь форматов данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

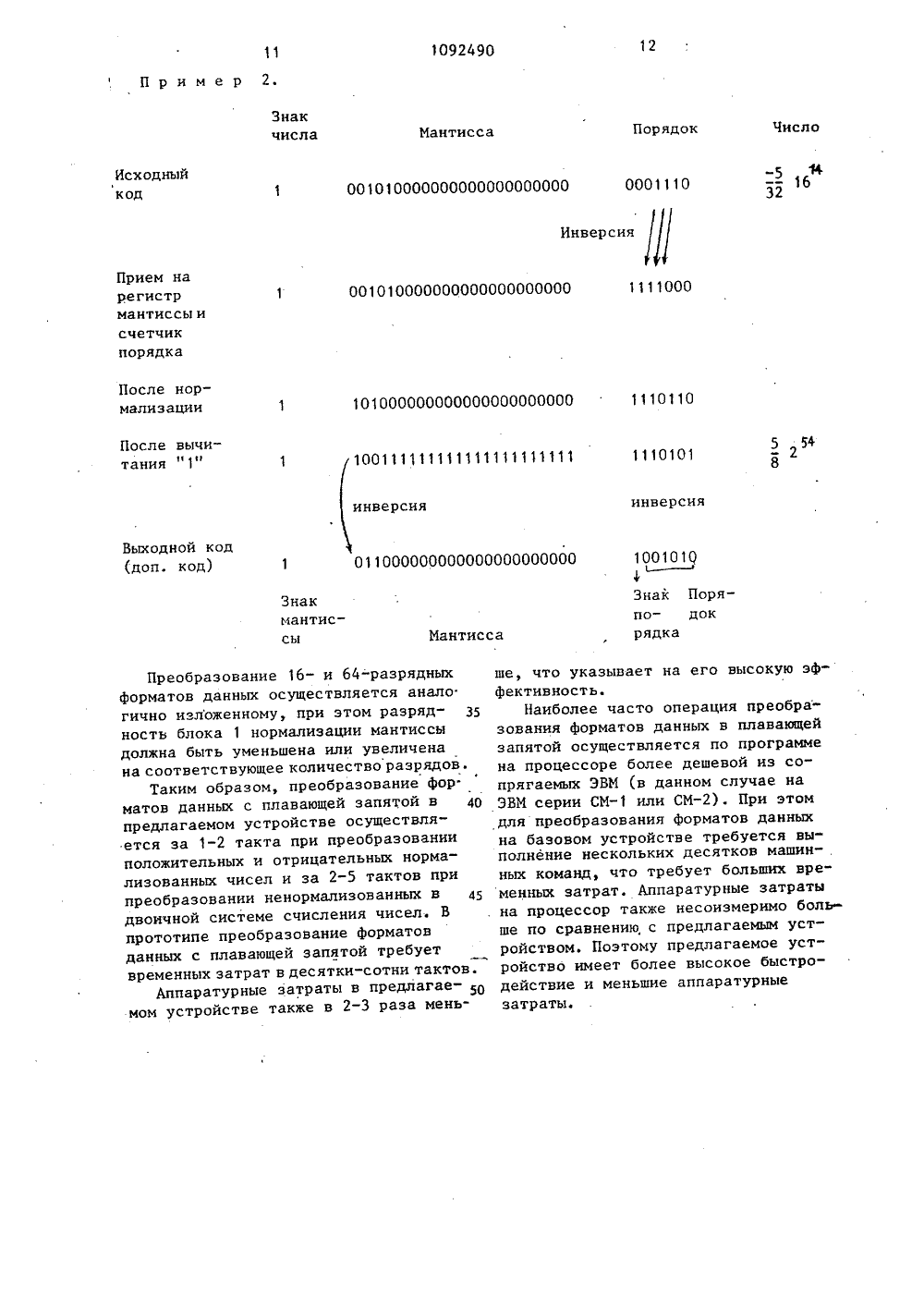

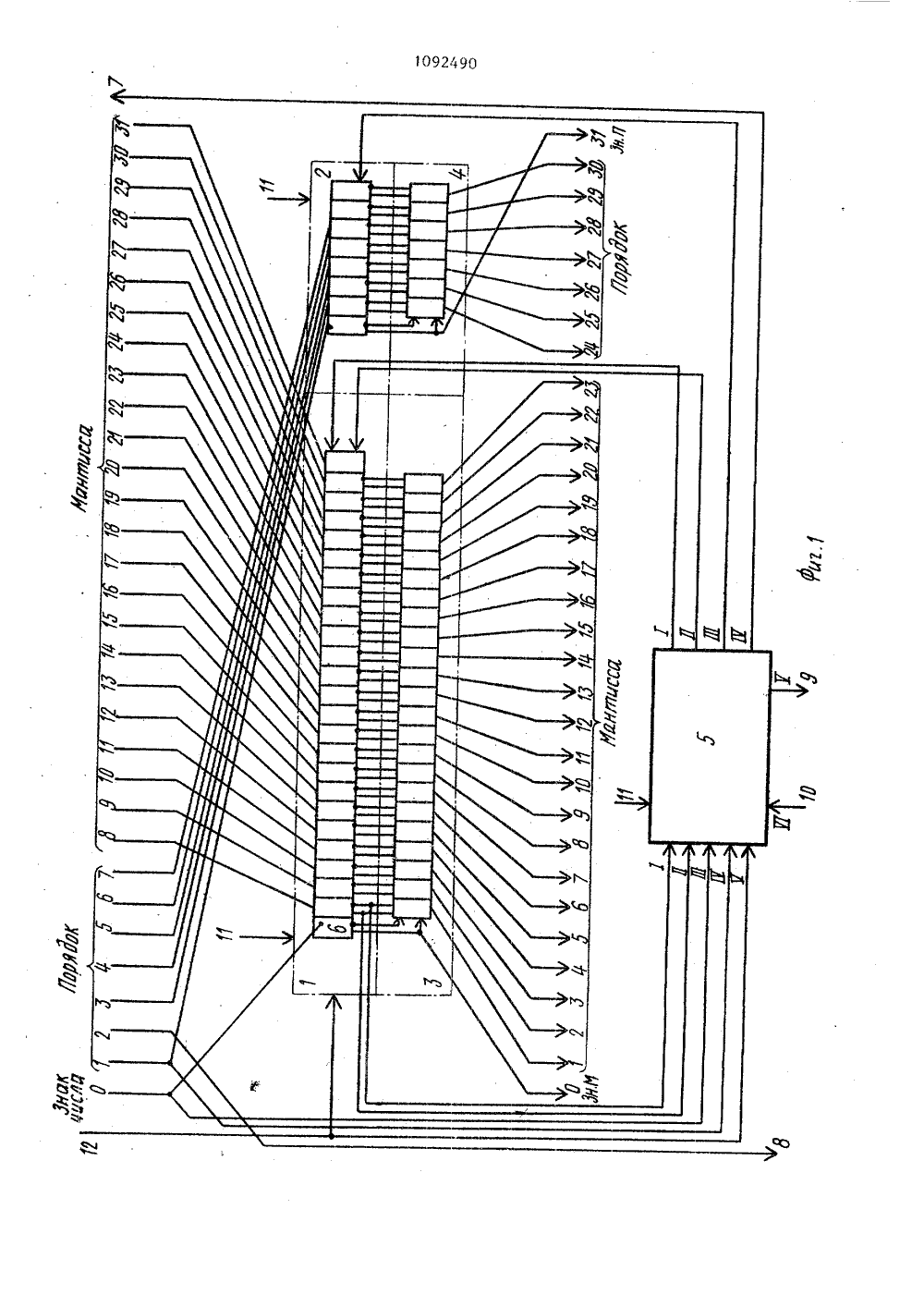

ПИ Заказ 3255/32 Тираж 699 Подписное ал ППП "Патент , г.Ужгород, ул.Проектная, 410единены с тактовым входом блока управления, первый и второй входы анализа режима работы которого соединены с первыми входами первого элемента И и объединены с первыми входами второго, третьего и четвертого элементов И, вторые входы которых и вто рой вход первого элемента И соединены с выходом первого триггера и являются выходом занятости блока управления, вход знака которого соединен с -входом второго триггера и через первый элемент НЕ с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и является выходом сдвига блока управления, вход знака порядка которого соединен через второй элемент НЕ с о -входом третьего триггера и с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и является выходом инкремента блока управления, выход разрешения выдачи которого соединен с выходом четвертого элемента И, третий и четвертый входы которого соединены соответственно с инверсными входами второго и третьего триггеров, Ь -входы которых соединены соответственно с выходами первого и второго элементов ИЛИ, а прямые выходы соединены соответственно с третьими входами второго и третьего элементов И,- и 8 -входы первого триггера соединены соответственно с входами разрешения приема и окончания приема блока управления, выход нормализации которого соединен с выходом третьего элемента ИЛИ.2. Преобразователь по п.1, о т л и ч а ю щ и й с я тем, что в нем блок нормализации мантиссы состоит 92490 из разрядов, первый и второй информационные входы и вход переноса каждого из которых, кроме младшего,соединены с первым и вторым информационнымн выходами и выходом переносасоседнего младшего разряда, причемкаждый разряд блока нормализациимантиссы содержит й 5 -триггер, дваэлемента ИЛИ, две группы по три элемента И, элемент НЕ и элемент И,первый вход которого является входомпереноса разряда блока нормализациимантиссы, разрядный вход которогосоединен с первым входом первого элемента И первой группы и через элемент НЕ с первым входом псрвого элемента И второй группы, вторые входыпервых элементов И первой и второйгрупп соединены с входом разрешенияприема блока нормализации мантиссы,первые входы вторых элементов И первой и второй групп являются прямымиинверсным информационными входамиразряда блока нормализации мантиссы,вторые входы вторых элементов И первой и второй групп соединены с входом сдвига блока нормализации мантиссы, вход инкремента которого соединенс первыми входами третьих элементов Ипервой и второй групп, вторые входыкоторых соединены с выходом элемента И, второй вход которого соединенс последовательным инверсным информационным входом разряда блока нормализации мантиссы, выходы элементов И первой и второй групп соединены с входами соответствующих элементов ИЛИ, выходы которых соединены соответственно с 5 - и К -входами триггера, прямой и инверсный выходы которого и выход элемента И являютсясоответственно последовательными прямым и инверсными информационными выходами и выходом переноса разрядаблока нормализации мантиссы, 1Изобретение относится к цифровой вычислительной технике и может быть использовано при построении устройств согласования ЭВМ с различными Форматами представления данных,2Известен преобразователь форматов данных, содержащий регистр мантиссы, регистр порядка, счетчик порядка и сумматор 1,Недостатками известного устройст ва является невозможность преобраэо 10924звания чисел с шестнадцатиричным основанием и большой объем аппаратуры.Наиболее близким к предлагаемому является преобразователь форматов данных, содержащий двоичный и десятичный регистры мантиссы, старшую и младшие тетрады десятичного регистра мантиссы, блок коррекции, двоичный и десятичный реверсивные счетчики порядка,дешифраторы нуля двоичного и десятичного реверсивных счетчиков порядка, дешифраторы нуля двоичного и десятичного регистров мантиссы, дешифраторы прямого и обратного преобразования, блок управления, триггер направления преобразования, генератор тактовых импульсов, выход которого соединен с входами дешифратора прямого и обратного преобразования, причем тактовый вход блока управления соединен с тактовыми входами регистра мантиссы и счетчика порядка, входы мантиссы преобразователя соединены с разрядными входами регистра мантиссы 225Недостатками известного преобразователя являются низкое быстродействие и большие аппаратурные затраты.30Цель изобретения - повышение быстродействия и сокращение аппаратурных затрат.Поставленная цель достигается тем, что в преобразователь форматов данных, содержащий блок нормализации мантиссы, счетчик порядка, триггер знака мантиссы и блок управления, тактовый вход которого соединен с тактовыми входами блока нормализации40 мантиссы и счетчика порядка и является тактовым входом преобразователя, входы мантиссы которого соединены с информационными входами блока нормализации мантиссы, вход триггера зна 45 ка мантиссы соединен с входом знака преобразователя, входы порядка которого соединены с разрядными входами счетчика порядка, введены коммутатор мантиссы и коммутатор порядка, выходы которых являются выходами ман 50 тиссы и выходами порядка преобразователя соответственно, первый и второй управляющие входы коммутатора мантиссы и коммутатора порядка соединены с прямыми и инверсными выхода ми триггера знака мантиссы и соотетственно старшего разряда счетчика поржицка, выходы всех, кроме старшего,90 разрядов которого соединсны с разряд.ными входами коммутатора порядка,разрядные входы коммутатора мантиссысоединены соответственно с информационными выходами всех, кроме младшего, разрядов блока нормализациимантиссы, вход разрешения приема которого соединен с входом разрешенияприема блока управления и являетсявходом разрешения приема преобразователя, выходы знака и знака порядкакоторого соединены соответственно спрямыми выходами триггера знака порядка и старшего разряда счетчика по.рядка, счетный вход которого соединен с выходом нормализации блока управления, первый и второй входы анализа режима, которого соединены соот"ветственно с прямым и инверснымвыходами старшего разряда блока нор"мализации мантиссы, входы сдвига иинкремента которого соединены соответственно с выходами сдвига и инкремента блока управления, выходы занятости и разрешения выдачи которо о явля.ются соответственно выходами занятостии разрешения выдачи преобразователя,вход окончания приема которого соединен с входом окончания приема блокауправления, входы знака и знака порядка которого соединены соответственно с входами знака и первого разряда порядка преобразователя, входвторого разряда порядка которого является выходом переполнения преобразователя, причем блок управления содержит два элемента НЕ, три элементаИЛИ,четыре элемента И и три К 5 -триггера, синхровходы которых соединены стактовым входом блока управления,первый и второй входы анализа режимаработы которого соединены с первымивходами первого элемента И и объединены с первыми входами второго, третьего и четвертого элементов И, вторые входы которых и второй входпервого элемента И соединены с выходом первого триггера и являются выходом занятости блока упраВления,вход знака которого соединен с5-входом второго триггера и черезпервый элемент НЕ с первым входомпервого элемента ИЛИ, второй входкоторого соединен с выходом второгоэлемента И и является выходом сдвигаблока управления, вход знака порядкакоторого соединен через второй элемент НЕ с 5 -входом третьего триггераи с первым входом второго элемен 1092490та ИПИ, второй вход которого соединен с выходом третьего элемента И и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И и является 5 выходом инкремента блока управления, выход разрешения выдачи которого сое динен с выходом четвертого элемента И, третий и четвертый входы которого соединены соответственно с инверсными входами второго и третьего триггеров, Й -входы которых соединены соответственно с выходами первого и второго элементов ИЛИ, а прямые выходы соединены соответственно с третьими входами второго и третьего элементов И, 5 - и 1 -входы первого триггера соединены соответственно с входами разрешения приема и окончания приема блока управления, выход нормализации которого соединен с выходом третьего элемента ИЛИ.В преобразователе блок нормализации мантиссы состоит из разрядов, первый и второй информационные входы и вход переноса каждого из которых, кроме младшего, соединены с первым и вторым информационными выходами и выходом переноса соседнего младшего разряда, причем каждый разряд ЗО блока нормализации мантиссы содержит Нэ -триггер, два элемента ИЛИ, две группы по три элемента И, элемент НЕ и элемент И, первый вход которого является входом переноса разряда блока нормализации мантиссы, разрядный вход которого соединен с первым входом первого элемента И первой группы и через элемент НЕ с первым входом первого элемента И второй группы, вторые входы первых элементов И первойи второй групп соединены с входом разрешения приема блока нормализации мантиссы, первые входы вторых элементов И первой и второй групп являются прямым и инверсным информационными входами разряда блока нормализации мантиссы, вторые входы вторых элементов И первой и второй групп соединены с входомо сдвига блока нормализации мантиссы, вход инкремента которого соединен с первыми входами третьих элементов И первой и второй групп, вторые входы которых соединены с выходом элемента И, второй вход которого соединен с последовательным инверсным информационным входом разряда блока нормализации мантиссы, выходы элементов И первой и второй групп соединены свходами соответствующих элементов ИЛИвыходы которых соединены соответственно с Б- и К-входами триггера, прямой и инверсный выходы которого ивыход элемента И являются соетветственно последовательными прямым и инверсными информационными выходами и выходом переноса разряда блока нормализации мантиссы.На фиг,1 приведена блок-схемапредлагаемого преобразователя, нафиг,2 - схема блока управления, нафиг.З - схема двух разрядов блоканормализации мантиссы и коммутаторамантиссы.Преобразователь (фиг.1) содержит блок 1 нормализации мантиссы, счетчик 2 порядка, коммутатор 3 мантиссы,коммутатор 4 порядка и блок 5 управления, триггер 6 знака мантиссы, выход 7 занятости, выход 8 переполнения, выход 9 разрешения выдачи, вход10 окончания приема, тактовый вход 11 преобразователя, вход 12 разрешения приема.Блок 5 управления (фиг,2) содержиттриггеры 13-15, элементы НЕ 16-17,элементы ИПИ 18-19, элементы И 20-23,элемент ИЛИ 24.Каждый разряд блока 1 нормализации мантиссы и коммутатора 3 мантиссы (фиг.З) содержит Р -триггер 25,элементы ИЛИ 26-27, две группы элементов И 28-29, элемент НЕ 30, элемент И 31, элемент И-ИЛИ 32.Принцип построения и работу предлагаемого преобразователя рассмотрим на примере преобразования формата данных ЕС ЭВМ в формат СМ ЭВМ.Двоичные числа с плавающей запятой в формате ЕС ЭВМ представляются следующим образом: 1 разряд - знак числа, 7 разрядов - порядок, 24 разряда - мантисса.ОсноваНие счисления в этом формате принято равным 2 =16, поэтому нормализация чисел осуществляется с точностью до тетрады.Порядок чисел представляется увеЬличенным на 2 =64, т.е. смещеннымна числовой оси в положительном направлении на 6 разрядов, в результате чего все порядки являются положительными.Положительные и отрицательные числа с плавающей запятой (их порядкии мантиссы) во всех моделях ЭВМ Единой системы В оперативной памяти хра 1 Р 92490нятся в прямом коде, Знак числа определяется по значению двоичной цифры в знаковом разряде.Диапазон представления нормализованных шестнадцатиричных чисел (по 5абсолютному значению) определяетсяпределами от 16 до 16.64Двоичные числа с плавающей запятойв формате СМ ЭВМ (модели СМ, СМ)представляются следующим образом:1 разряд - знак мантиссы, 23 разряда - мантисса, 7 разрядов - порядок,1 разряд - знак порядка,Основание системы счисления вформате СМ ЭВМ принято равным 2, 15поэтому нормализация чисел осуществляется с точностью до 1 разряда.Положительная мантисса и положительный порядок представляются в прямом коде со знаковыми разрядами равными О.Отрицательная мантисса и отрицательный порядок представляются вдополнительном коде со знаковымиразрядами равными 1,Предполагается, что запятая в мантиссе фиксируется непосредственнослева от ее старшей цифры.Диапазон представления нормализованных чисел (по абсолютному значе(Ынию) находится в пределах от 2до 2 , т.е. значительно уже, чемдиапазон представления чисел в формате ЕС ЭВМ.Преобразователь работает следующим образом.При подключении входного кода иподаче сигнала "Разрешение пРиема"по входу 12 (фиг.1) осуществляетсязапись нулевого разряда (знак числа) 40в нулевой (знаковый) разряд блока 1нормализации мантиссы, 8-31 разрядовв 24-разрядный блок 1 нормализациимантиссы, первого разряда порядка синверсией в знаковый разряд счетчи 45ка 2 порядка, 3-7 разрядов порядка в1-5 разряды счетчика 2 порядков,в 6-7 разряды счетчика 2 порядка приэтом записывается "0". Нулевой и пер.вый разряды входного кода записываются также в триггерах 13 и 1.4 блока5 управления в прямом и инверсномкоде соответственно (фиг.2). СигналнРаэрешение приема", поступившнйтакже в блок 5 управления по пятому55входу, устанавливает триггер 15 вединичное состояние, который подготавливает блок 5 управления к работеи выдает по четвертому выходу сигнал"Занято" на выход 7, предупреждаяисточник входной информации о заня"тости устройства.Знак мантиссы по выходу совпадаетсо знаком входного числа, поэтомуон однозначно отображается через зна.ковый разряд мантиссы на выход, Порядок числа в исходном формате представляется смещенным в положительномнаправлении и все порядки являются положительными, при этом "1" в старшем(первом) разряде порядка свидетельствует о положительном порядке, а 0об отрицательном. Поэтому знак порядка в преобразованном формате определяется как инверсия старшего (первого) разряда порядка входного числа.Диапазон, представления чисел в исходном формате с шестнадцатиричнымоснованием значительно шире, чем возможное представление чисел в форматес двоичным основанием, при этом наличие "1" во втором разряде порядкавходного числа свидетельствует о том,что данное число не может быть преобразовано в выходной формат, поэтому в такой ситуации по выходу 8 выдается сигнал "Переполнение",Число, нормализованное во входномформате с шестнадцатиричным основанием, может оказаться не нормализованным в выходном формате с двоичнымоснованием, поэтому по триггеру 6знака осуществляется контроль нормализации. Если он находится в нуле,то единица на нулевом (инверсном)выходе этого триггера, заведенная напервый вход блока 5 управления, открывает элемент И 20 (фиг.2), который дает разрешение на первый вьмодблока 5 управления для сдвигов (беззнака) блока 1 нормализации мантиссы влево и через элемент ИЛИ 24 натретий выход блока 5 управления длявычитания единиц из счетчика 2 порядка, Сдвиги в блоке 1 нормализациимантиссы и вычитание единиц в счетчике 2 порядка осуществляются под воздействием тактовых импульсов по входу11 до тех пор, пока в старшем (первом)разряде блока нормализации мантиссыне появится "1", Количество возможныхсдвигов, которые должны быть сделаныдля нормализации, равно 0-3. При появлении " 1" в старшем (первом) разряде блока нормализации мантиссы снимается разрешающий сигнал с входа элемента И 20 и, соответствен10 2490 Порядок Число тисса числа 141632 Исходный 001010000000000000000000 1001110 код Инверсия Прием нарегистр мантиссы и счет 0111000 01101 10 0110110 001 100000000000000000010100000000000000000000 Д чик порядкаПосле нормализацииВыходной 10100000000000000000000 код Знакмантиссы Знак Поряпо- докпяпМантисса 9 109 но, с первого и третьего выхода блока управления появляется разрешающий сиг, нал с единичного выхода старшего разряда блока нормализации мантиссы по второму входу блока 5 управления на входах элементов И 21"23, подготавливая блок управления для дальнейшей работы. Если число в блоке 1 нормализации мантиссы сразу оказалось йорма. лизованным, то сдвиги блока 1 нормализации мантиссы и вычитание единицы из счетчика 2 порядка не производятся Отрицательная мантисса и отрицательный порядок в выходном формате должны быть представлены в дополнительном коде со знаковым разрядом равным "1", поэтому после нормализации числа блоком 5 управления осуществляется проверка знака входного числа и старшего разряда порядка, записанных в его триггерах 13 и 14. Если мантисса отрицательна, то единичный выход триггера 13 открывает элемент И 21, выдавая на второй выход разрешающий сигнал для вычитания единицы из содержимого блока 1 нормализации. При отрицательном порядке единичным выходом триггера 14 открывается элемент И 22, который через элемент ИЛИ 24 выдает разреша- ющий сигнал на третий выход для вычи. тания единицы иэ счетчика 2 порядка, При отрицательных мантиссе и порядке проверка их знаков и вычитание единиц иэ блока 1 нормализации мантиссы и счетчика 2 порядка осуществляется одновременно, Следующим тактовым импульсом триггеры 13 и 14 сбрасываются в нулевое состояние, разрешая через элемент И 23 подачу сигнала "Разрешение выдачи" по пятому выходу)Знак Ман блока 5 управления на выход 9 устрой;ства.Триггер б знака, знаковый разрядсчетчика 2 порядка управляют комму таторои 3 мантиссы и коммутатором 4порядка, коммутируя на выход прямойили обратный коц содержимого блока 1нормализации мантиссы и счетчика 2порядка. При положительных знакахкоммутируются прямые коды, при отри.цательных - обратные.После того, как выходной кодбудет принят приемником информации,из него должен поступить сигнал окон чания приема по входу 10, которыйсбрасывает триггер 15 в нулевое состояние, снимает сигнал занятости повыходу 7, после чего устройство готово к приему нового числа.20 Особенностью преобразования мантиссы является также то, что в исходномкоде мантисса представлена 24 разрядами, а в выходном - 23 разрядами,поэтому если после приема мантиссы 25 на блок 1 нормализации мантиссы мантисса оказывается нормализована длядвоичного основания, то происходитпотеря одного разряда мантиссы. Востальных случаях все разряды мантис. ЗО сы сохраняются.Некоторые особенности построенияимеет и блок нормализации мантиссы.В нем кроме обычных функций, выполняемых регистром (прием числа, сдвигсодержимого), имеется возможностьвычитания единицы из его содержимого(как в обычном счетчике). Первые элементы И в группах используются для приема числа, вторые - для сдвига, тре тьи - для вычитания с целью сквозного заема на элементах И.11 р и м е р 1, Преобразованиеформатов данных.12 1092490 Пример 2. Знакчисла Мантисса Порядок Число Исходныйкод 0010100000000000000000005 Й1632 0001110 Инверсия Прием нарегистрмантиссы и 001010000000000000000000 1111000 счетчик порядка После нор- мализации 101000000000000000000000 1110110 После вычитания "1" 5 4 2 8100111111111111111111111 1110101 инверсия инверсия Выходной код(доп. код) 011000000000000000000000 100101 ОЗнак Поряпо- докрядка Знак мантис Мантисса сы Преобразование 16- и 64-разрядных форматов данных осуществляется анало гично изложенному, при этом РазРяд ность блока 1 нормализации мантиссы должна быть уменьшена или увеличена на соответствующее количество разрядов.Таким образом, преобразование фор. матов данных с плавающей запятой в 4 О предлагаемом устройстве осуществля" ется за 1-2 такта при преобразовании положительных и отрицательных нормализованных чисел и за 2-5 тактов при преобразовании ненормализованных в 4 двоичной системе счисления чисел. В прототипе преобразование форматов данных с плавающей запятой требует временных затрат в десятки-сотни тактов.Аппаратурные затраты в предлагае мом устройстве также в 2-3 раза меньше, что указывает на его высокую эффективность.Наиболее часто операция преобразования форматов данных в плавающей запятой осуществляется по программе на процессоре более дешевой из сопрягаемых ЗВМ (в данном случае на ЭВМ серии СМили СМ). При этом для преобразования форматов данных на базовом устройстве требуется выполнение нескольких десятков машинных команд, что требует больших вре" менных затрат, Алпаратурные затраты на процессор также несоизмеримо больше по сравнению с предлагаемым устройством, Поэтому предлагаемое устройство имеет более высокое быстродействие и меньшие аппаратурные затраты.

СмотретьЗаявка

3492714, 17.09.1982

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ ИМ. В. М. ГЛУШКОВА

БОЮН ВИТАЛИЙ ПЕТРОВИЧ, МАМЕДОВ ШАХИН ИСЛАМОВИЧ

МПК / Метки

МПК: G06F 5/02

Опубликовано: 15.05.1984

Код ссылки

<a href="https://patents.su/10-1092490-preobrazovatel-formatov-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь форматов данных</a>

Предыдущий патент: Устройство для приведения -кодов фибоначчи к минимальной форме

Следующий патент: Универсальный логический модуль

Случайный патент: Релейный триггер