Устройство для управления реконфигурацией микропрограммного процессора

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

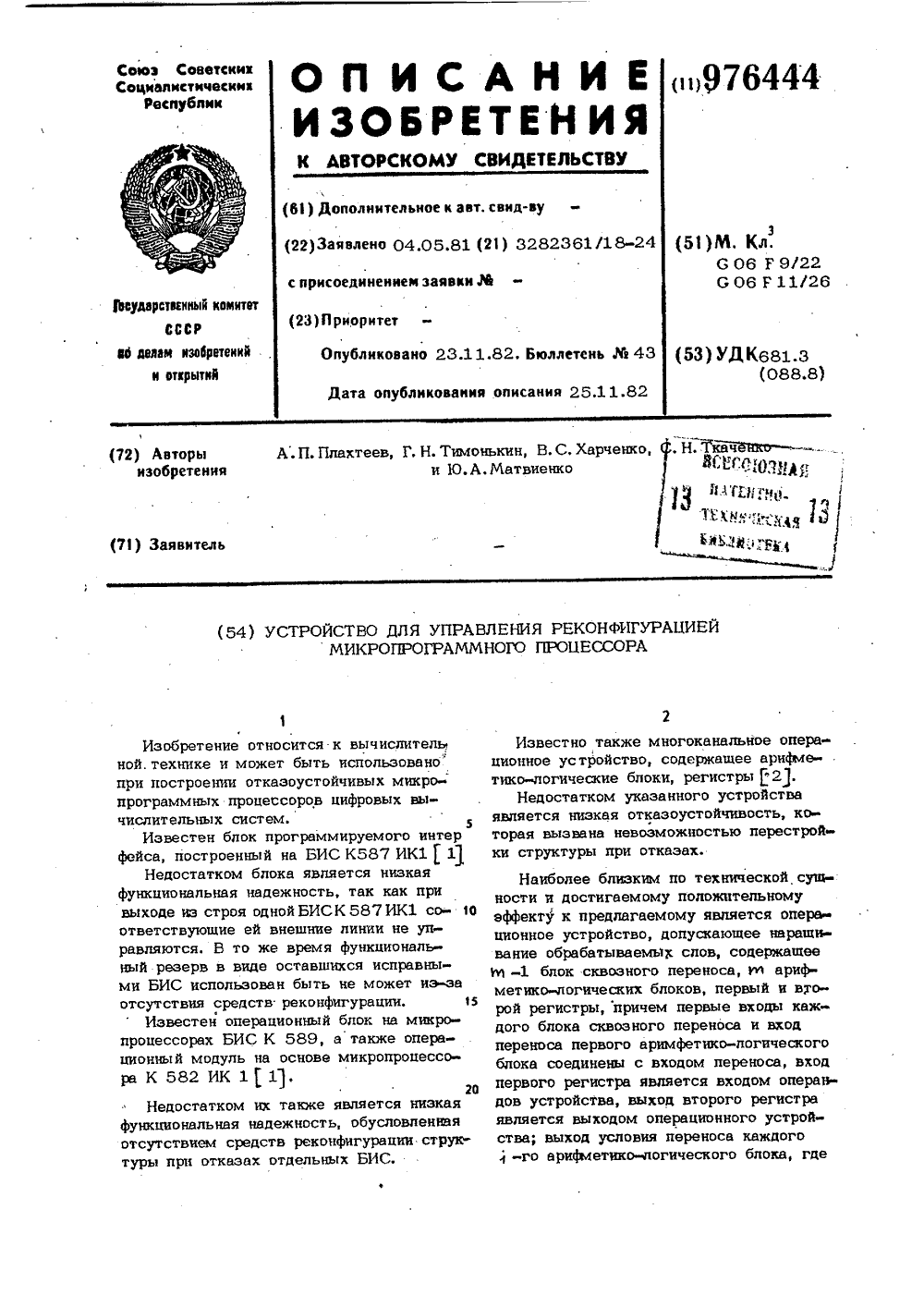

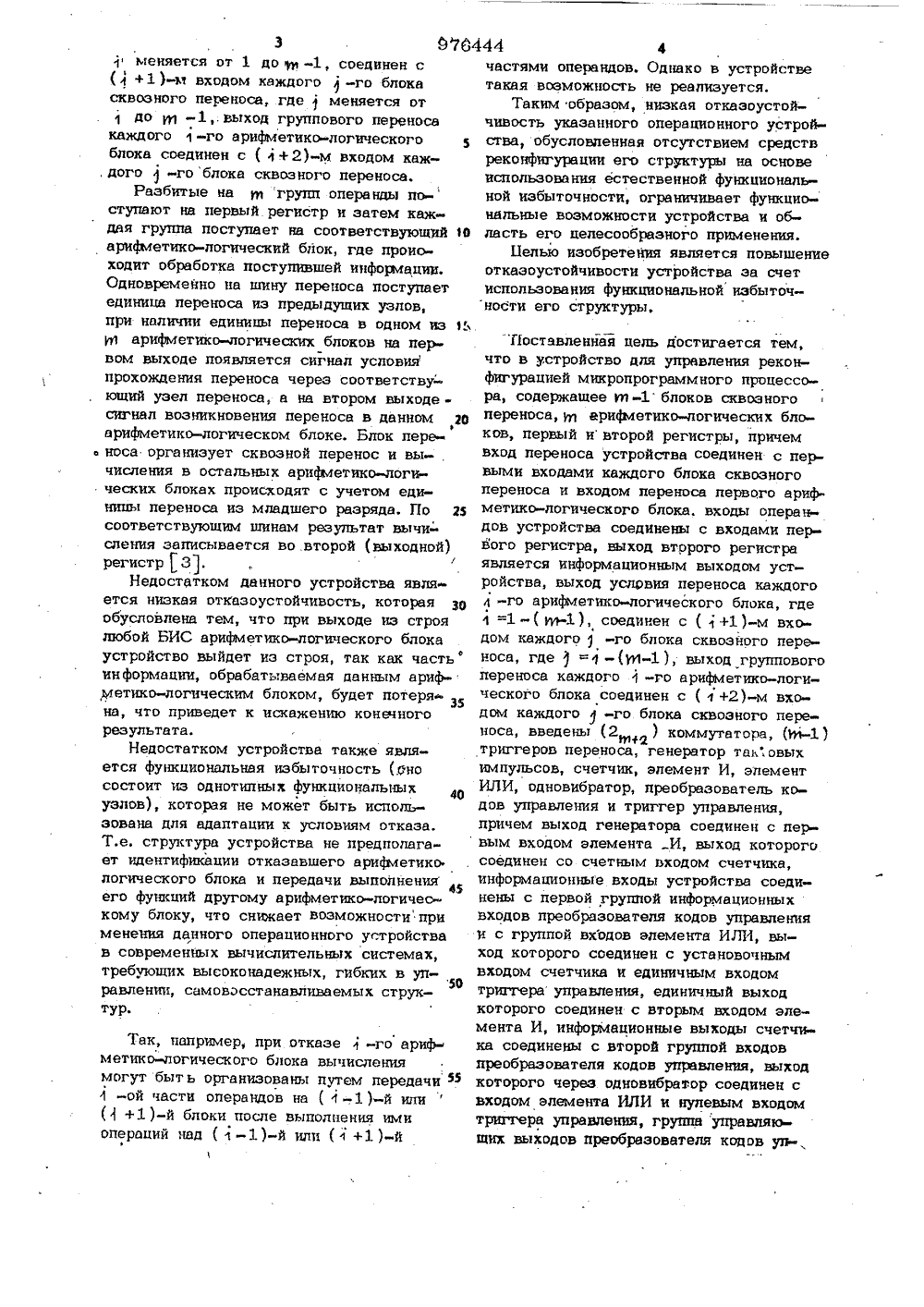

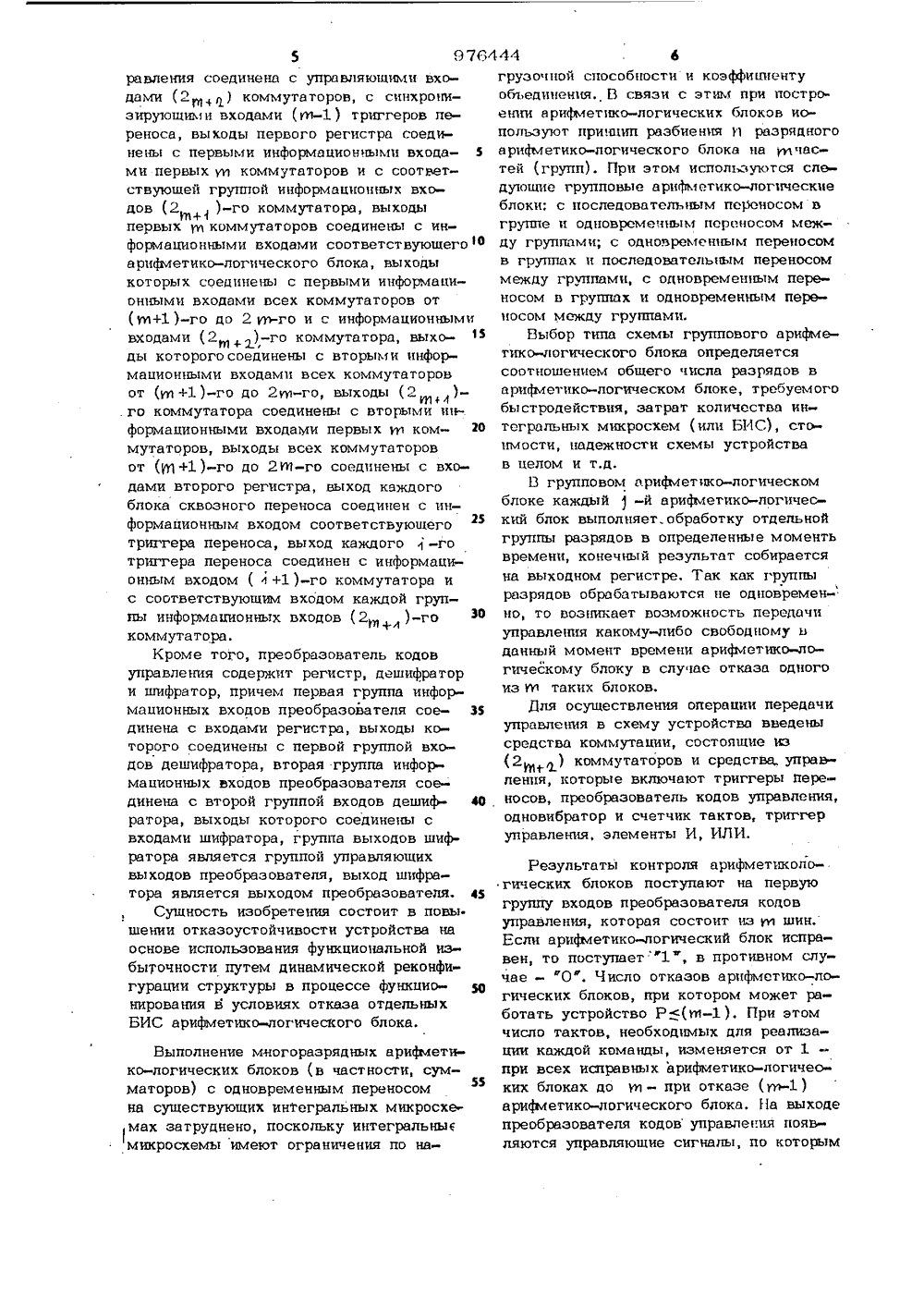

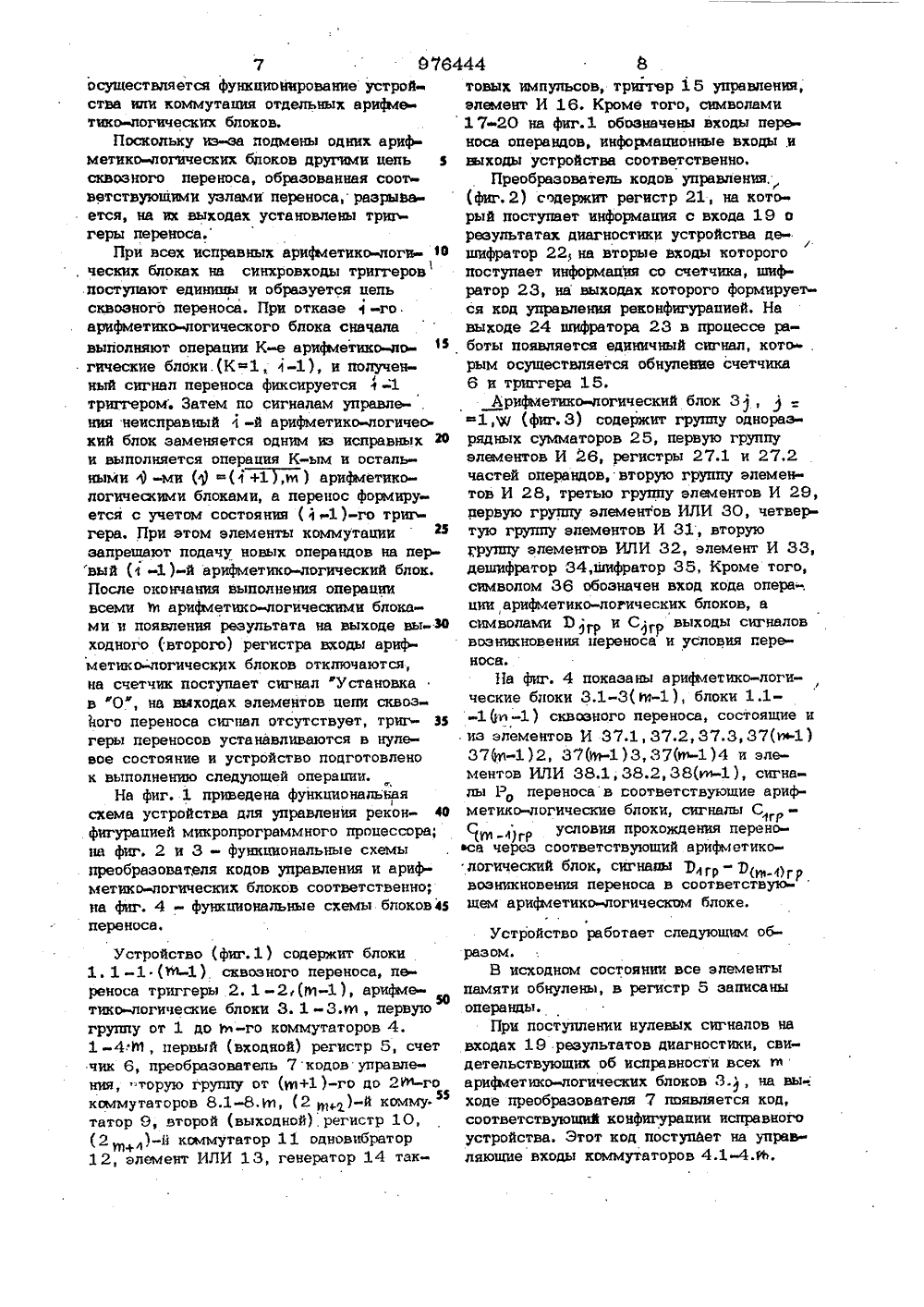

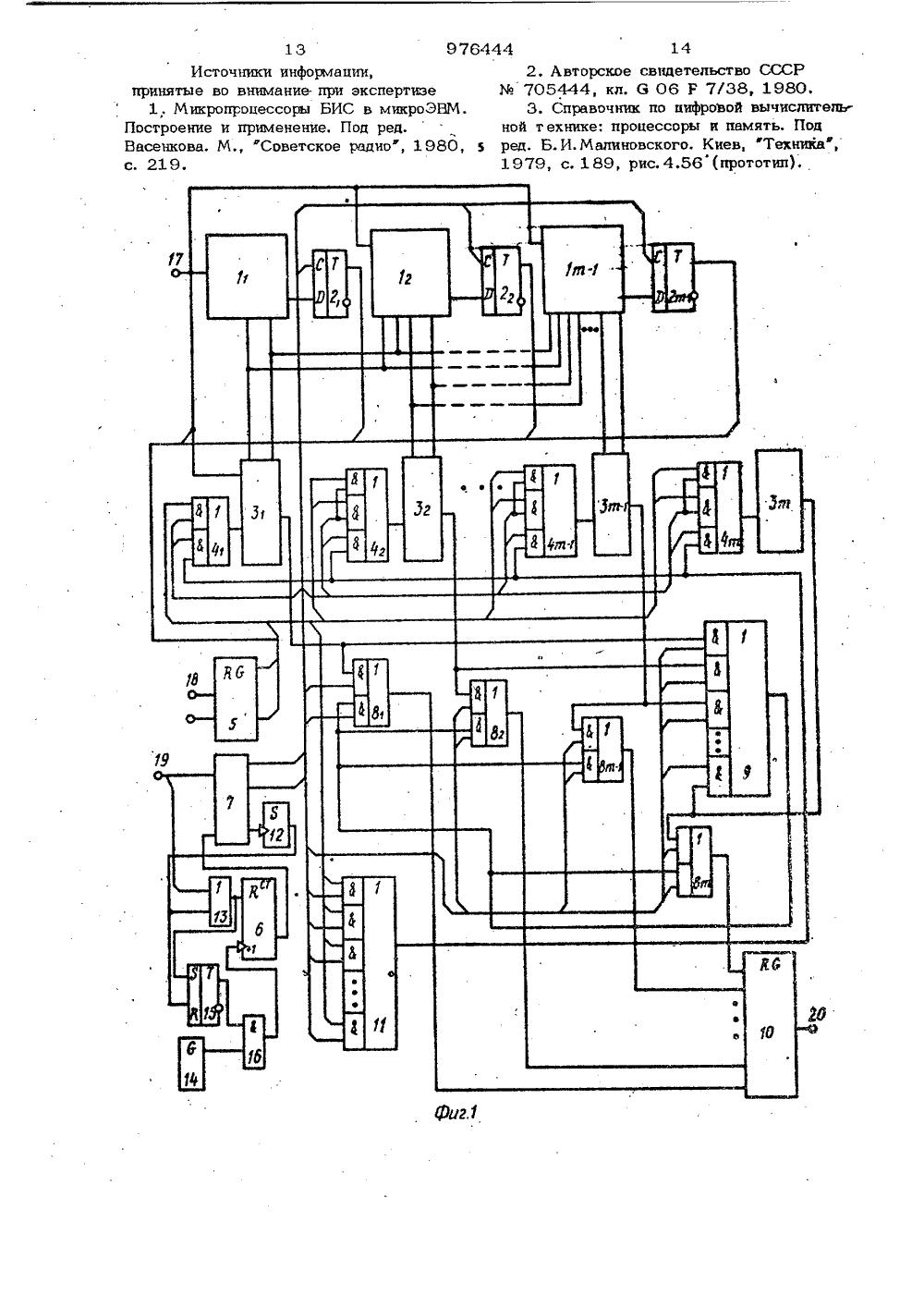

Со 1 оэ СоветскикСоцмалмстмческмкРеснублмк ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТЬРСКЬМУ СВИДЕТЕЛЬСТВУ(51)М, Кл. 0 06 Г 9/22 О 06 Г 11/26 3 Ьоудоретеенный комитет СССР дб делам изобретений н открытнй(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕКОНФИГУРАЦИЕЙ МИКРОПРОГРАММНОГО ПРОЦЕССОРА 1Изобретение относится к вычислитель ной. технике и может быть использовано при построении отказоустойчивых микропрограммных процессоров цифровых вычислительных систем.Известен блок программируемого интер фойса, построенный на БИС К 587 ИК 11Недостатком блока является низкая функциональная надежность, так как при выходе из строя одной БИСК 587 ИК 1 со о ответствующие ей внешние линии не ут- равляются, В то же время функциональ ный резерв в виде оставшихся исправными БИС использован быть не может из-за отсутствия средств реконфигурации. 15вИзвестен операционный блок на микропроцессорах БИС К 589, а также операционный модуль на основе микропроцессора К 582 ИК 11,гоНедостатком их также является низкая функциональная надежность, обусловленная отсутствием средств реконфигурации струк туры при отказах отдельных БИС. Известно также многоканальное опера ционное устройство, содержащее арифметико-логические блоки, регистры2.Недостатком указанного устройства является низкая отказоустойчивость, которая вызвана невозможностью перестройки структуры при отказах. Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому является опера ционное устройство, допускающее наращивание обрабатываемых слов, содержащее М -1 блок сквозного переноса, ич арифметико логических блоков, первый и второй регистры, причем первые входы каждого блока сквозного переноса и вход переноса первого аримфетико-логического блока соединены с входом переноса, вход первого регистра является входом операндов устройства, выход второго регистра является выходом операционного устрой ства; выход условия переноса каждого .1 -го арифметико логического блока, где( +1)-и входом каждого-го блокасквозного переноса, гдеменяется отдо щ -1,. выход группового переносакаждого-го арифметико-логическогоблока соединен с ( 1+2)-м входом каж, дого-го блока сквозного переноса.Разбитые на ул групп операндь 1 поступают на первый регистр и затем каждая группа поступает на соответствующий 16арифметико-логический блок, где проиоходит обработка поступившей информации.Одновременно на шину переноса поступаетединица переноса иэ предыдущих узлов,при наличии единицы переноса в одном из Ьарифметико-логических блоков на первом выходе появляется сигнал условияпрохождения переноса через соответству-ющий узел переноса, а на втором выходесигнал возникновения переноса в данном 2 О1арифметикслогическом блоке. Блок пере. носа организует сквозной перенос и вычисления в остальных арифметико-логических блоках происходят с учетом единиць переноса из младшего разряда. По 2соответствующим шинам результат вычисления записывается во второй (выходной)регистр 3.Недостатком данного устройства является низкая отказоустойчивость, которая ЗОобусловлена тем, что при выходе из строялюбой БИС арифметико-.логического блокаустройство выйдет из строя, так как частьинформации, обрабатываемая данным арифметико-логическим блоком, будет потеряна, что приведет к искажению конечногорезультата,Недостатком устройства также является функциональная избыточность (дносостоит из однотипных функциональныхузлов), которая не может быть использована для адаптации к условиям отказа,Т,е, структура устройства не предполагает идентификации отказавшего арифметикологического блока и передачи выполненияего функций другому арифметико-логическому блоку, что снижает возможности применения данного операционного устройствав современных вычислительных системах,требующих высоконадежных, гибких в управлении, сдмовосстанавливаемых структур. 44 4частями операндов. Однако в устройстве такая возможность не реализуется.Таким образом, низкая отказоустойчивость указанного операционного устройства, обусловленная отсутствием средств реконфигурации его структуры на основе использования естественной функциональной избыточности, ограничивает функциональные возможности устройства и область его целесообразного применения.Целью изобретения является повышение отказоустойчивости устройства эа счет использования функциональной избыточности его структуры."Поставленная цель достигается тем, что в устройство для управления реконфигурацией микропрограммного процессора, содержащее е -1 блоков сквозного переноса,п ерифметико-логических блоков, первый и второй регистры, причем вход переноса устройства соединен с пе выми входами каждого блока сквозногопереноса и входом переноса первого арифметико-логического блока. входы операндов устройства соединены с входами первого регистра, выход втррого регистраявляется информационным выходом устройства, выход условия переноса каждого-го арифметико-логического блока, где1 =1-( м), соединен с ( 1+1)-м входом каждого-го блока сквозного переноса, где= -(уи), выход групповогопереноса каждого-го арифметико-логического блока соединен с ( +2)-м входом каждого-го блока сквозного переноса, введены (2, ) коммутатора, (М) триггеров переноса, генератор тдк, овых импульсов, счетчик, элемент И, элемент ИЛИ, одновибратор, преобразователь кодов управления и триггер управления,причем выход генератора соединен с первым входом элемента И, выход которого соединен со счетным входом счетчика,информационные входы устройства соединены с первой группой информационныхвходов преобразователя кодов управления и с группой входов элемента ИЛИ, выход которого соединен с установочным входом счетчика и единичным входом триггера управления, единичный выход которого соединен с вторым входом эле Так, например при отказе-го арифметико логического блока вычислениямогут быть организованы путем передачи1 -ой части операндов на ( 1-1)-й или(1 +1)-й блоки после выполнения имиопераций над ( -1)-й или ( +1)-й мента И, информационные выходы счетчика соединены с второй группой входов преобразователя кодов управления, выход которого через одновибратор соединен с входом элемента ИЛИ и нулевым входом триггера управления, группа управляющих выходов преобразователя кодов уп-,9764 равления соединена с управляющими входами (2.,) коммутаторов, с сцнхронизирующимц входами (и) триггеров переноса, выходы первого регистра соединены с первыми информационнымц входа ми первых уи коммутаторов и с соответствующей группой информационных входов (2 )-го коммутатора, выходы1 ъ+ 1первых и коммутаторов соединены с информационными входами соответствующегоО арцфметико-логического блока, выходы которых соединены с первыми информационными входами всех коммутаторов от (1 м+1)-го до 2 ауго и с информационными входами (2 + )-го коммутатора, выходы которого соединены с вторыми информационными входамц всех коммутаторов от (ил+1)-го до 2 щ-го, выходы (2 )- . го коммутатора соединены с вторыми ин-. формационными входами первых и ком мутаторов, выходы всех коммутаторов от (И+1)-го до 2 Ю-го соединены с входами второго регистра, выход каждого блока сквозного переноса соединен с информационным входом соответствующего триггера переноса, выход каждого 1-го триггера переноса соединен с информационным входом ( +1)-го коммутатора и с соответствующим входом каждой группы информационных входов (2 )-го ЗоМ+ коммутатора.Кроме того, преобразователь кодов управления содержит регистр, дешифратор и шифратор, причем первая группа информационных входов преобразователя сое динена с входами регистра, выходы ко торого соединены с первой группой входов дешифратора, вторая группа информационных входов преобразователя соединена с второй группой входов дешиф ратора, выходы которого соединены с входами шифратора, группа выходов шифратора является группой управляющих выходов преобразователя, выход шифратора является выходом преобразователя. ЮСущность изобретения состоит в повы. шенин отказоустойчивости устройства на основе использования функциональной избыточности путем динамической реконфигурации структуры в процессе функцио- у нирования в условиях отказа отдельных БИС арифметико-логического блока. Выполнение многоразрядных арифметико-логических блоков (в частности, сумматоров) с одновременным переносом на существующих интегральных микросхемах затруднено, поскольку интегральные микросхемы имеют ограничения по на 44 6грузочной способности и коэффициентуобъединения, В связи с этим при построении арифметцко-логических блоков иопользуют принцип разбиения и разрядногоариметико-логического блока на ичастей (групп). При этом испол зуются сльдующие групповые арцфметико-логическиеблоки: с последовательным переносом вгруппе ц одновременным переносом между группами; с одновременным переносомв группах ц последовательным переносоммежду группами, с одновременным переносом в группах и одновременным переносом между группами.Выбор типа схемы группового арифмьтико-логического блока определяетсясоотношением общего числа разрядов варифметцко-логическом блоке, требуемогобыстродействия, затрат количества интегральных микросхем (илц БИС), стсьнмости, надежности схемы устройствав целом и т,д,В групповом арифметцко-логическомблоке каждый ) -й арифметико-логический блок выполняет. обработку отдельнойгруппы разрядов в определенные моментьвремени, конечный результат собираетсяна выходном регистре. Так как группыразрядов обрабатываются не одновремен-но, то возникает возможность передачиуправления какому-либо свободному вданный момент времени арифметико-логическому блоку в случае отказа одногоиз и таких блоков.Для осуществления операции передачиуправления в схему устройства введенысредства коммутации, состоящие из(21) коммутаторов и средства, управления, которые включают триггеры Переносов, преобразователь кодов управления,одновибратор и счетчик тактов, триггеруправления, элементы И, ИЛИ. Результаты контроля арифметикологических блоков поступают на первую группу входов преобразователя кодов управления, которая состоит из 1 м шин. Если арифметикологический блок исправен, то поступает ф 1 , в противном случае - "О". Число отказов арцфметико-логических блоков, при котором может работать устройство Р с(ю). При этом число тактов, необходимых для реализации каждой команды, изменяется от 1 - при всех исправных арифметико-логичеоких блоках до щ - при отказе (уд) арифметико-логического блока, На выходе преобразователя кодов управления появ ляются управляющие сигналы, по которым7 9 фЯосуществляется функционирование устрой"ства или коммутация отдельных арвметико-логических блоков,Поскольку иэ-эа подмены одних арифметико-логических блоков другими цепь 5сквозного переноса, образованная соответствующими узлами переноса, разрывается, на их выходах установлены триггеры переноса.При всех исправных арифметико-логи 10, ческих блоках на синхровходы триггеровпоступают единипы и образуется цепьсквозного переноса. При отказе -го.арифметико логического блока сначалавыполняют операции К-е арифметико-ло фгические блоки. (К, -1), и полученный сигнал переноса фиксируется-1триггером. Затем по сигналам управле- .ния неисправный-й арифметико-логичеокий блок заменяется одним из исправных фи выполняется операция К-ым и остальными р -ми И (аа+13),м ) ари)мееикалогическими блоками, а перенос формируется с учетом состояния ( и 1)-го триггера, При атом элементы коммутациизапрещают подачу новых операндов на первый ( -1)-й арифметико-логический блок.После окончания выполнения операциивсеми В арифметико-логическими блоками и появления результата на выходе выз 0ходного (второго) регистра входы арифметикологических блоков отключаются,на счетчик поступает сигнал РУстановкав фО", на выходах элементов цепи сквозЙого переноса сигнал отсутствует, триг- ЗЗгеры переносов устанавливаются в нулевое состояние и устройство подготовленок выполнению следующей операции.На фиг. 1 приведена функциональйаясхема устройства для управления реконфигурацией микропрограммного процессора;на фиг. 2 и 3 - функциональные схемыпреобразователя кодов управления и арифметика логических блоков соответственно;на фнг. 4 - функциональные схемы блоков 4 зпереноса,Устройство (фиг. 1) содержит блоки 1. 11 й)-1) сквозного переноса, пе реноса триггеры 2. 1-20 и), арифметико-логические блоки 3. 1-3.е, первую%0 группу от 1 до м-го коммутаторов 4.1 -4 М, первый (входяой) регистр 5, счет чик 6, преобразователь 7 кодов управления, аторую группу от (ин+1)-го до 2 Ф-го коммутаторов 8.1-8.п, (2 а +)-й коммуИ татор 9, второй (выходной) регистр 10, (2 +)-й ксымутатор 11 одновибратор 12, элемент ИЛИ 13, генератор 14 так 444 Ьтовых импульсов, триггер 15 управления,элемент И 16. Кроме того, символами17"20 на фиг,1 обозначены входы переноса операндов, информационные входы,ивыходы устройства соответственно.Преобразователь кодов управления,(фиг. 2) содержит регистр 21, на который поступает информация с входа 19 орезультатах диагностики устройства де/шифратор 22, на вторые входы которогопоступает информация со счетчика, шифратор 23, на выходах которого формируется код управления реконфигурацией. Навыходе 24 шифратора 23 в процессе работы появляется единичный сигнал, которым осуществляется обнуление счетчика6 и триггера 15.Арифметико-логический блок 3 ,1 д/ (фиг. 3) содержит группу одноразрядных сумматоров 25, первую группуэлементов И 26, регистры 27.1 и 27,2частей операндов, вторую группу алементов И 28, третью группу элементов И 29,первую группу алеменгов ИЛИ 30, четвертую группу элементов И 31, вторуюгруппу алементов ИЛИ 32, элемент И 33,дешифратор 34,шифратор 35, Кроме того,символом 36 обозначен вход кода опера-.ции арифметико-логических блоков, асимволами Э гр и Ср выходы сигналоввозникновения переноса и условия переноса.На фиг. 4 показаны арнфметико-логические блоки 3,1-3(и), блоки 1.1-16 и) сквозного переноса, состоящие ииэ элементов И 37.1, 37.2,37.3,37(е)376-1)2, 376 и)3,37(в)4 и элементов ИЛИ 38,1,38.2,38(и), сигналы 1 переноса в соответствующие арифметнко-логические блоки, сигналы Сгр (о)гр условия прохождения перенокз через соответствующий арифметикологический блок, скгнааы )гр - р (е-)грвозникновения переноса в соответствующем арифметико-логическом блоке. Устройство работает следующим образом.В исходном состоянии все элементыпамяти обнулены, в регистр 5 записаны операнды.При поступлении нулевых сигналов навходах 19 результатов диагностики, свидетельствующих об исправности всех еарифметико-логических блоков 3.), на вы-.ходе преобразователя 7 появляется код,соответствующий конфигурации исправногоустройства. Этот код поступает на управляющие входы коммутаторов 4.1-4 л).Поступившие в схему операнды, разбитйе на В групп по р разрядов, каждая, с выхода первого регистра 5 поступают через первые информационные входы коммутаторов 4,1-4.чи на входы арифметико-логи з ческих блоков 3.1-3.в, На первый вход первого арифметикопрлогического блока 3,1 поступает так же сигнал переноса от аналогичного устройства. На синхровходы триггеров переноса 2.1-2,еподаются10 единичные сигналы, по которым сформировавшиеся сигналы переноса поступают через соответствующий коммутатор 4в следующий арифметико-логический блок, Результаты обработки частей операндов 1 ф поступают на первые информационные вхорды коммутаторов 8-8, управляемые разрешающими сигналами с выхода преобразователя 7. С выходов коммутаторов 8.1-8 результирующие коды поступают фй на второй регистр 10, Так как все арифметико-логические блоки 3 исправны, то уже после первого такта на выходе 24 преобразователя 7 появляется единичный сигнал, которым подтверждается нулевое состояние счетчика 6 тактов и триггера 1 5. Резульаат, записанный во втором регистре 10, передается на выход 20 для дальнейшей обработки. В следующем такте на вход 18 регистра 5 поступают Зэ очередные операнды и в случае исправного состояния всех блоков цикл работы снова повторяется.В случае отказа какого-либо арифметико логического блока 3., в-ый раз ряд регистра 21 записывается единичный сигнал. При этом операционное устройство выполняет обработку операндов за два такта. Код с выхода преобразователя 7 в первом такте разрешает прохождение . - 46 групп разрядов операндов через коммутаторы 4.1-4.(-1) на первые (-1)-е арифметико-логические блоки 3.1-3. (1-1 ), а с их выходов (через коммутаторы 8.1- 8.(-1 ).- в соответствующие разряды 4 регистра 10. При этом через коммутаторы 4.1-4.( )-1) разрешается также прохождение сигналов переноса, которые фиксируются триггерами 2-2(-2).Во втором такте содержимое счетчи 50 ка 6 увеличивается на единицу, а на выходе преобразователя 7 появляется код, которым вместо отказавшего-го блока подключается один иэ исправйых блоков .3,1-3.-1 ). -тая группа разрядов фф операндов с выхода регистра 5 через коммутатор 11,а затем через коммутатор 4,4,4 1,(п) поступает на арифметикологический блок 34 . Вместе с этой группой. разрядов в блок 3.0 поступает также и сигнал переноса, зафиксированный триггером 3.б)уруппы разрядов операндов от Я+1) Й до 1 м -й поступают в ариметико-логичео кие блоки 3,(+1)-З.уи через коммутаторы 4.(+1)-4.ил иэ регистра 5, При этом сигнал переноса, формируемый блоком 3.4., проходит в арифметикологический блок 3.(+1) с выхода триггера 2 Я через коммутатор 4.( +1) совместно с (+1)-й группой разрядов операндов.Результат вычисления, формируемый арифметико-логическим блоком 3."Д через коммутатор 9 поступает на второй информационный вход коммутатора 8 и далее в соответствующие разряды регистра 10.Результаты вычислений, полученные в (+1) - И - и -м ариметико-логических, блоках, поступают через коммутаторы 8.(+1) -8.ул в (+1)е груптпа разрядов регистра 10. Таким образом, после считывания из преобразователя 7 второго кода в регистре 10 формируется результат выполнения операции, а сигнал с выхода 21 через одновибратор 12 осуществляет обнуление счетчика 6 и триггера 15. Следовательно, предлагаемое устройство позволяет осуществлять арифметические и логические операции прп наличии отказавшего арифметнко-логического блока за два такта работы.При поступлении очередных операндов на вход 19 вновь приходит код отказав ших арифметико-логических блоков, триггер 15 устанавливается в )Р 1 Р и на счет ный вход счетчика 6 поступают тактовые импульсы. По мере их поступления преобразователь 7 кодов формирует коды управления реконфигурацией, которыми коммутируются входы и выходы арифметико-логических блоков 3.1-3 м. При . выходе иэ строя К(ю) арифметикологических блоков 3. 1 3"1 ,".,3 1 к операционное устройство выполняет вычисления за К+1 такт, Последователь ность выполнения вычислений следующая.В первом такте выполяет вычисления блоки 3,1-3.о,о(.=4(1-), во второмтаКтЕ - блОКИ 3 Ц,О4 б.т 3(1 +-3(4 и) блок 3 9 подключается вместо отказав- щего блике 31 ), а К-м такте - блоки 3), би 1,а ).и-) е, а (к е 1 )-м такте - блоки 39, Чек.1 . При атом праобреаощ тель кодов управления по мереувеличения содержимого счетчика 6 от единицы до (К+1) формирует последовательность44 12 11 9764 кодов, которые управляют коммутаторами4,8, 9 и 11. При выходе из строя (в)-го блока устройство производит вычисления оставшимся работоспособным арифметико-логическим блоком, который за уп тактов последовательно обрабатывает ю групп разрядов операндов, При этом преобразователь 7 кодов управления реконфигурацией последовательно формирует Р кодов, которые путем коммутации осу О . ществляют последовательную передачу групп разрядов операндов в этот блок, а с его выхода - в соответствующие разря. ды регистра 10,Таким образом, предлагаемое устрой ство существенно превосходит известное по отказоустойчивости. Применение уст ройства позволяет строить отказоустойчивые вычислительные системы обеспечивающие также требуемую производительность при заданной интенсивности техт- о ческого обслуживания. формула изобретения 1. Устройство для управления реконфигурацией микропрограммного процессора, содержащее (м) блоков сквозного ,переноса, ю арифметико-логических блоков, первый и второй регистры, причем вход переноса устройства соединен с первыми входами каждого блока сквозного ф переноса и входом переноса первого арифметико-логического блока, входы операнодов устройства соединены с входами пер-вого регистра, выход второго регистра является информационным выходом устройства, выход условия переноса каждого 1 -го арифметико-логического блока, где 1 =1-(щ), соединен с ( +1)-м входом40 каждого ) -го блока сквозного переноса, ,где ) =-(в), выход группового переноса каждбго 1-го арнфметико-логического блока соединен с (1+2)-м входом 1каждого-го блока сквозного переноса, о т л и ч а ю щ е е с я тем, что, с целью повышения, отказоустойчивости, в . устройство введены (2 ю+2) коммутатора, (ю) триггеров переноса, генератор тактовых импульс,сов, счетчик, элемент И, элемент ИЛИ, одновибратор, преобразователь кодов управления и триггер управления, причем выход генератора соединен с первым входом элемента И, выход которого соединен со счетным входом счет-чика, информационные входы устройства соединены с первой группой информационных входов преобразователя кодов упраьления и с группой входов элемента ИЛИ,выход которого соединен с установочнымвходом счетчика и единичным входомтриггера управления, единичный выход которого соединен с вторым входом элемента И, информационные выходы счетчикасоединены с второй группой входов преобразователя кодов управления, выходкоторого через одновибратор соединен свходом элемента ИЛИ и нулевым входомтриггера управления, группа управляющихвыходов преобразователя кодов управления соединена с управляющими входами(2 ю+2) коммутаторов, с синхронизирующими входами (е) триггеров переноса, выходы первого регистра соединеныс первыми информационными входами первых уи коммутаторов и с соответствующей группой информационных входов(2 И+1)-го коммутатора, выходы первыхи коммутаторов соединены с информационными входами соответствующего арифметико-логического блока, выходы которогосоединены с первыми информационнымивходами всех коммутаторов от (вн 1 )-годо 21 ю-го и с информационными входами(21+2)-го коммутатора, . выходы которого соединены с вторыми информационнымивходами всех коммутаторов от (я+1)-годо 2 м-го, выходы (2 и+1)-го .коммутатора соединены с вторыми информационными входами первых щ коммутаторов,выходы всех коммутаторов от (и+1)-годо 2 и-го соединены с входами второгорегистра, выход каждого блока сквозногопереноса соединен с информационнымвходом соответствующего триггера переноса, выход каждого 1 -го триггера переноса соединен с информационным входом ( л +1 )-го коммутатора и с соответствующим входом каждой группы информационных входов (2 Ю+1)-го коммутатора,2, Устройствопо и. 1, о тл ич аю щ е е с я тем, что преобразователь кодов управления содержит регистр, дешифратор и шифратор, причем первая группа информационных входов преобразователя соединена с входами регистра, выходы которого соединены с первой грут- пой входов дешифратора, вторая группа информационных входов преобразователя соединена а второй группой входов дешифратора, выходы которого соединены с входами шифратора, группа выходов шифратора является группой управляющих выходов преобразователя, выход шифратора является выходом преобразователя.13 9764Источники информации,принятые во внимание- при экспертизе1, Микропроцессоры БИС в микроЭВМ.Построение и применение. Под ред,Васенкова. М., "Советское радио, 1980, 3с. 219. 142. Авторское свидетельство СССР М 705444, кл. Я 06 Р 7/38, 1980.3. Справочник по цифровой вычислительной технике: процессоры и память. Под ред, Б.И.Малиновского. Киев, "Техника, 1979, с. 189, рис,4.56 (прототип),

СмотретьЗаявка

3282361, 04.05.1981

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ПЛАХТЕЕВ АНАТОЛИЙ ПАВЛОВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, МАТВИЕНКО ЮРИЙ АНДРЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного, процессора, реконфигурацией

Опубликовано: 23.11.1982

Код ссылки

<a href="https://patents.su/9-976444-ustrojjstvo-dlya-upravleniya-rekonfiguraciejj-mikroprogrammnogo-processora.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для управления реконфигурацией микропрограммного процессора</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Многоканальное устройство для приоритетного управления

Случайный патент: Гидравлический ключ для закрепления деталей в кулачках планшайб крупных токарных станков