Система бинарного кодирования и декодирования сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1781823

Авторы: Волков, Ходоровский

Текст

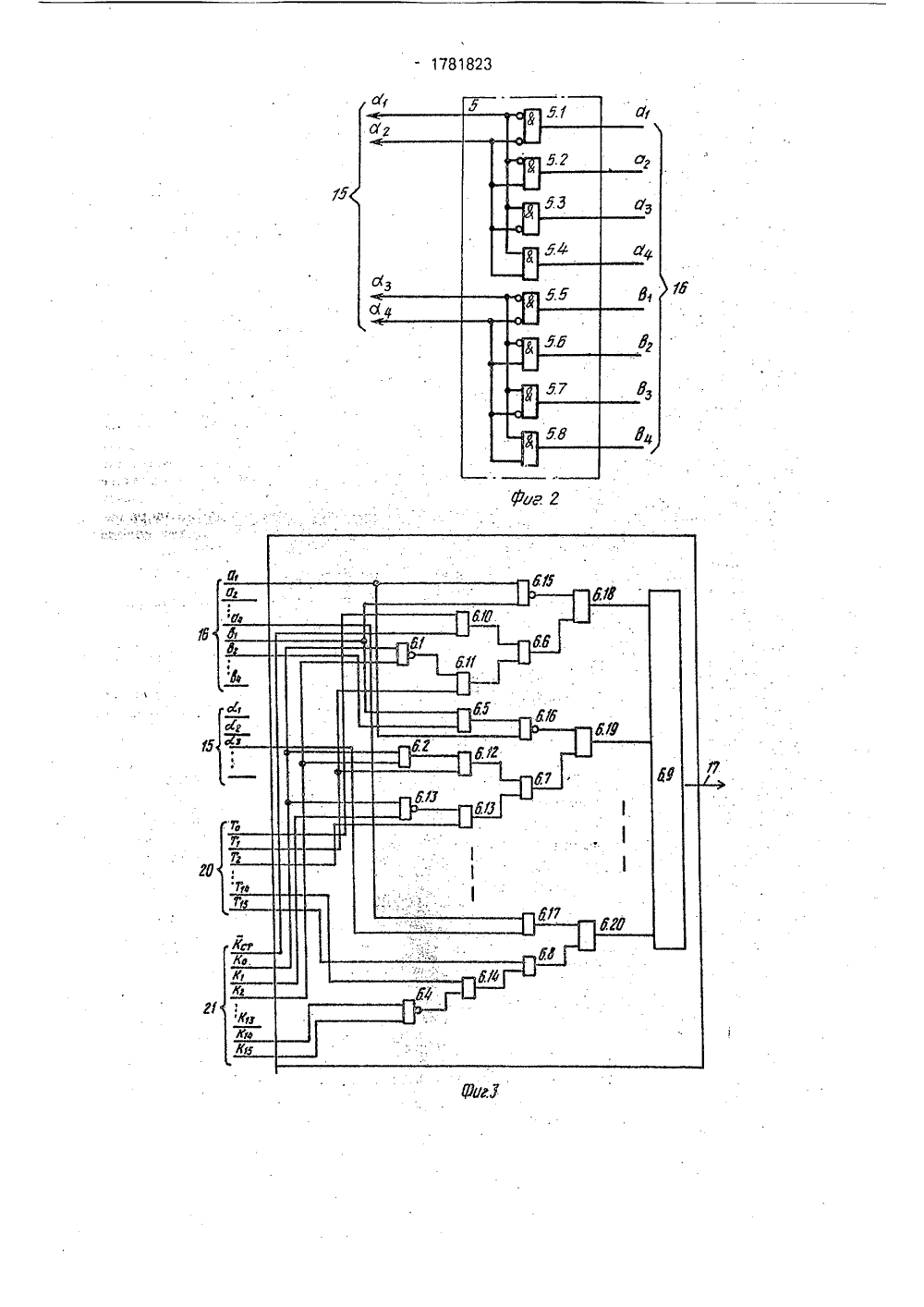

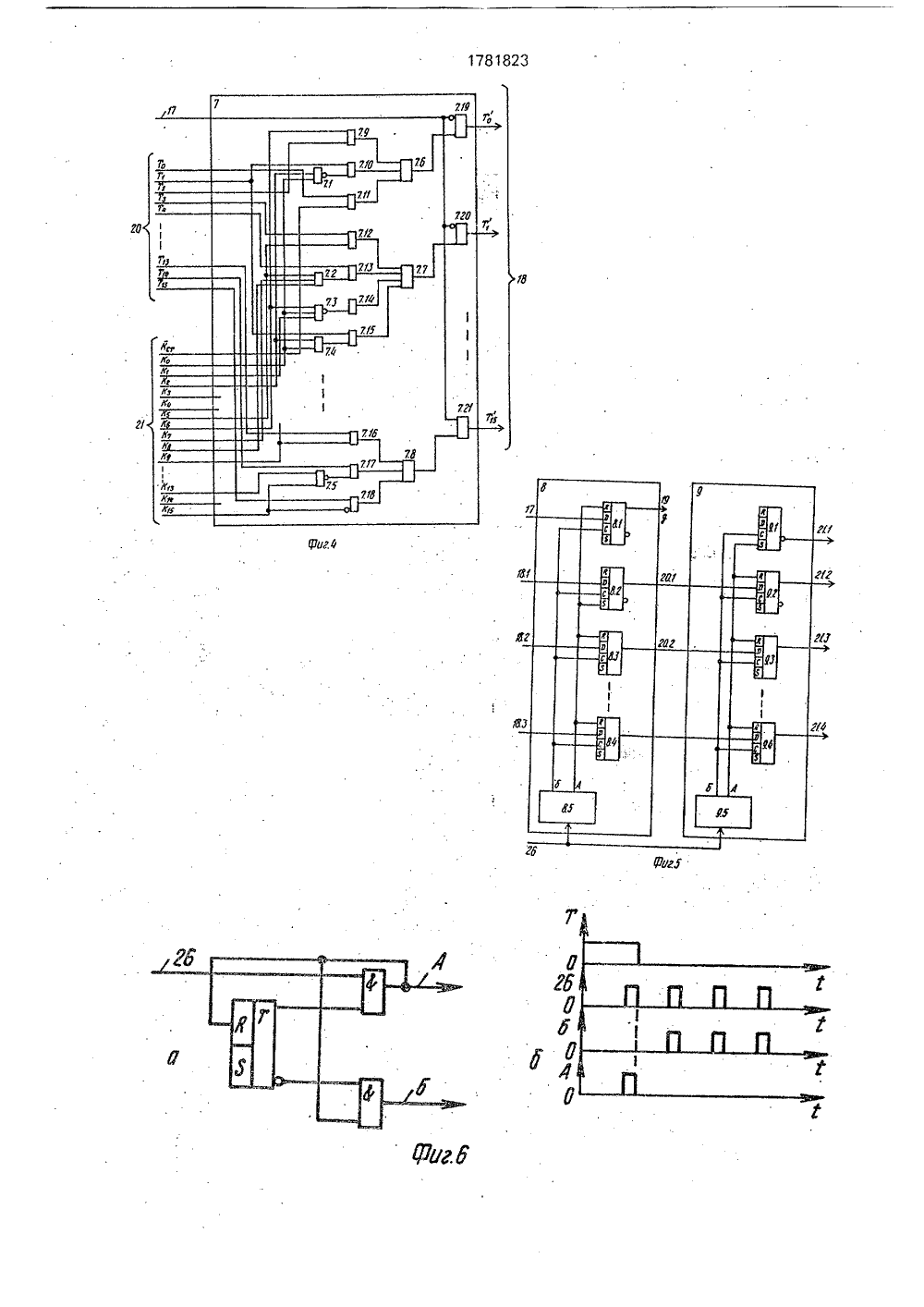

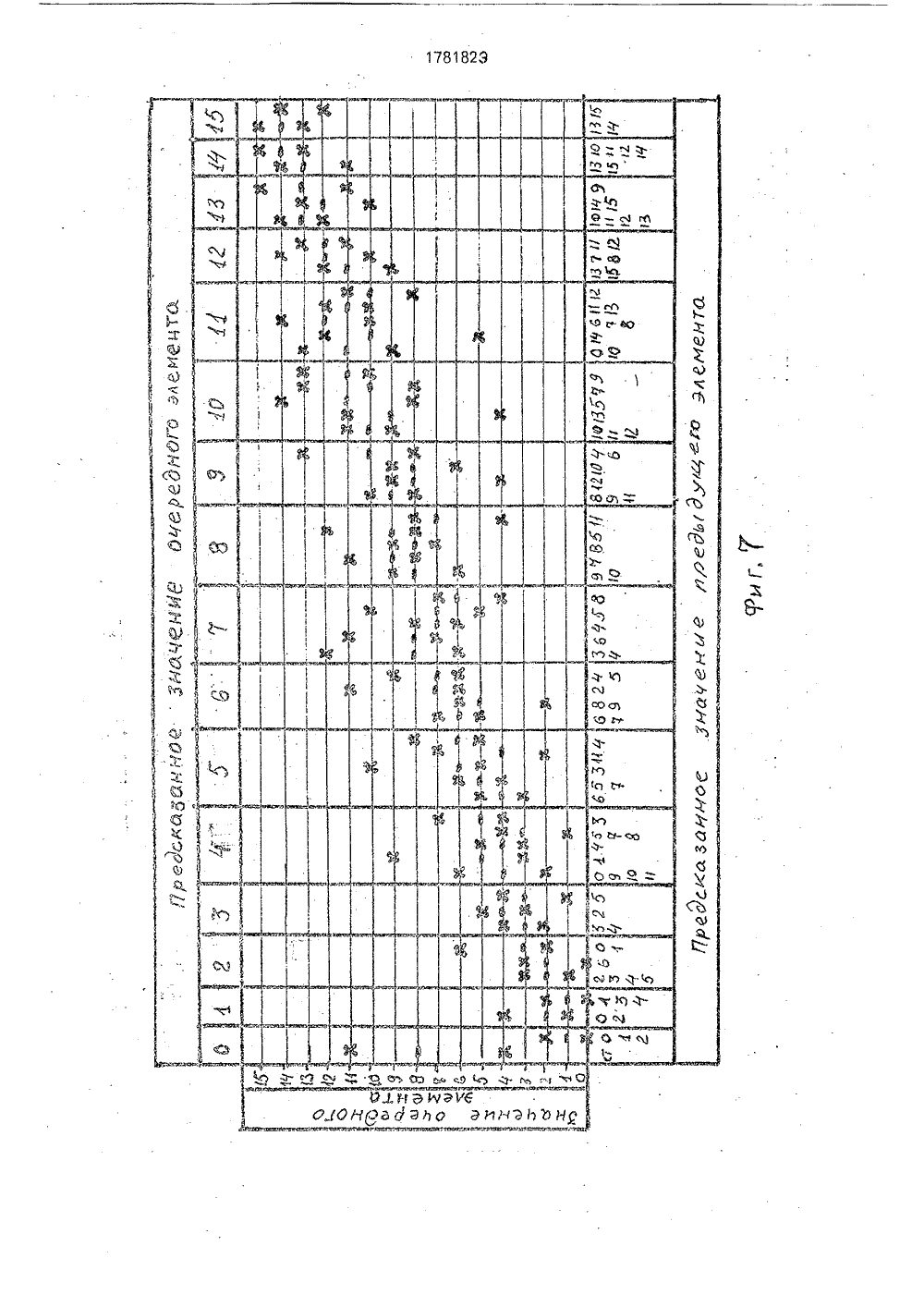

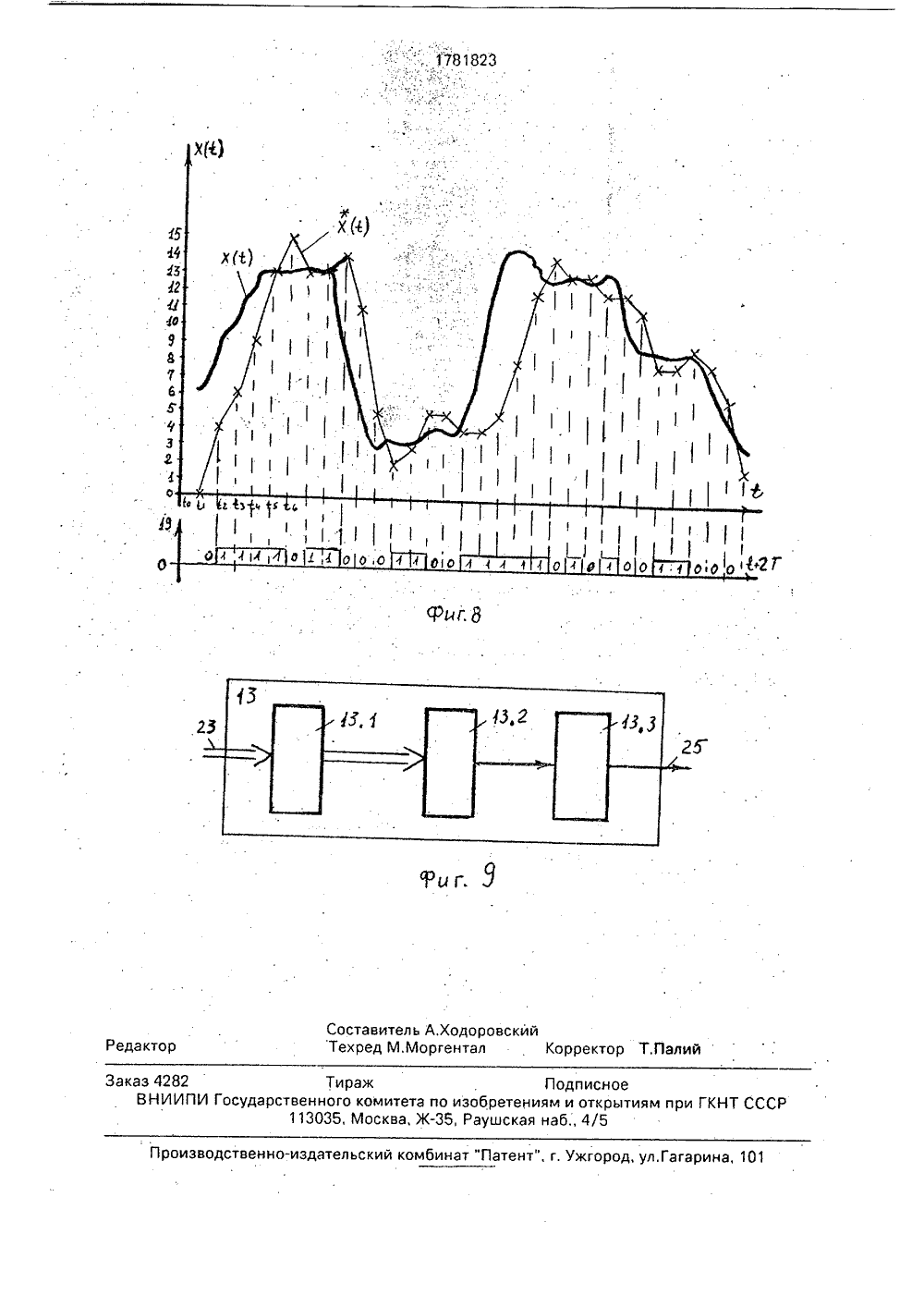

: Ы 2 4, Н 04 В 14/06 5)5 Н 03 М 3/ ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) ПИСАНИЕ ИЗОБРЕТЕНИ АВТОРСКОМУ СВИ ЛЬСТВ вания и декодирования телевизио чевых сигналов позволяет повыси действие и точность системы; Пе сторона 1 содержит аналого-циф образователь 4, кодер 6 выходно и блоки 8,9 памяти, Приемная содержит блок 11 памятй и блок новления, Благодаря введению ющей стороне.1 блока 5 деш кодера 7 предсказанного значен ки, а на приемной стброне 2 - предсказанного значения выбор 12 памяти, в системе обеспечива ставление каждой выборки одним разрядом с применением перест шкал квантования. 9 ил,14(54) СИСТЕМА БИНАРНОГО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ СИГНАЛОВ(57) Изобретение относится к вычислительной технике. Его использование для кодиронных и реть быстроредающая ровой прего сигнала сторона 2 13 восстана передаифрации и ия выбор- кодера 10 ки и блока ется пред- двоичнымрви ваемых10 20 30 35 40 45 50 55 Изобретение относится к вычислительной технике и может использоваться прикодированйй й декодировании телевизионных и речевых сигналов,Известна система кодирования и декодирования сигналов, в которой передающаясторона содержит последовательно соединенные компаратор, триггер и первый местный декодер, состоящий изпоследовательно сбединенных регистрасдвига, логического блокЪ, слогового фильтра, сумматора,"усилителя, амплйтудно-импульсного модулятора и интегратора,соединенного с одним из входов компаратора, а приемная сторона содержит второйместный декодер, аналогичный первому.Недостатком этой системы являетсянизкое быстродействие,Наиболее близкой по технической сущ-.ности к заявляемому изобретению являетсясистема, содержащая канал связи, на передающей стороне - аналого-цифровой преобразователь, информационный вход которогоявляется информационным входом системы,выходы аналого-цифрового преобразователясоединены с первыми входами кодера выходного сигнала, первый и второй блоки памяти,на приемной стороне - первый блок памяти иблок восстановления сигнала, выход которого является выходом системы 2,Недостатком системы является низкоебыстродействие, обусловленное последовательной передачей по каналам связи отдельных разрядов многоразрядных кодоввыборок, и невысокая точность преобразования, ограниченная допустимой частотойформирования отсчетов при данном способе передачи информации и заданной полосе пропускания каналов связи.Целью изобретения является повышение быстродействия и точности системы засчет сокращения времени. затрачиваемогона кодирование каждой выборки, представления каждой выборки одним двоичнымразрядом, и применением при кодйрованииперестраиваемых шкал квантования,На фиг,1 приведена структурная схемасистемы; на фиг.2 - структура блока дешифрации; на фиг,З - структуракодера выходного сигнала; на фиг,4 - структура кодерапредсказанного эначейия выборки; на фиг.5: - функциональйая схема первого и второгоблоков памяти с цепью управления; на фиг,б- схема (а) и временная диаграмма б) работы блока формирования сигналов управления; на фиг.7 - таблица шкал квантования,используемых в рассматриваемом примеререализации системы; на фи.8 - диаграмма,поясняющая работу системы; на фиг,9 -структура блока восстановления,Система бинарного кодирования и декодирования сигналов состоит из передающей 1 и приемной 2 сторон, связанных между собой через канал связи 3, Передающая сторона 1 содержит аналого-цифровой преобразователь 4, блок 5 дешифрации, кодер 6 выходного сигнала, кодер 7 предсказанного значения выборки, первый 8 и второй 9 блоки памяти, Приемная сторона 2 содержит кодер 10 предсказанного значения выборки, первый 11 и второй 12 блоки памяти, блок 13 восстановления сигналов. Первый вход аналого-цифрового преобразователя 4 соединен с информационным входом 14 системы, а выход 15 - с входом блока 5 дешифрации и с первым входом кодера 6 выходного сигнала. Выход 16 блока 5 дешифрации соединен с вторым входом кодера 6 выходного сигнала, выход 17 которого соединен с первым входом первого блока 8 памяти и с входом кодера 7 предскаэанного значения выборки, соединенного выходом 18 с вторым входом первого блока 8 памяти. Первый выход 19 первого блока 8. памяти является выходом передающей стороны, а второй выход 20 соединен с третьим входом кодера 6 выходного сигнала, с вторым входом кодера 7 предсказанного значения выборки и с первым входом второго блока 9 памяти, Выход 21 второго блока 9 памяти соединен с четверть 1 м входом кодера 6 выхбдного сигнала и с третьим входом кодера 7 предсказанного значения выборки, Вход приемной стороны 2 соединен с входом кодера 10 предсказанного значения выборки, соединенного выходом 22 с первым входом первого блока 11 памяти, выход которого соединен с первым входом второго блока 12 памяти, с входом блока 13 восстановления сигнала и с вторым входом кодера 10 предскаЗанного значения выборки, третий вход которого соединен с выходом 24 второго блока 12 памяти, Выход 25 блока 13 восстановления сигнала является выходом системы. Третий вход первого блока 8 памяти и второй вход второго блока 9 памяти передающей стороны, вторые входы аналого-цифрового преобразователя 4, первого 11 и второго 12 блоков памяти приемной стороны являются управляющими и соединены с входом 26 синхронизации,Блок 5 дешифрации (фиг,2) содержит набор двухвходовых элементов И 5,1-5,8, Кодер 6 выходного сигнала фиг,З) содержит набор элементов ИЛИ 6.1 - 6.9 и элементов И 6.10- 6,20. Идентичные кодеры 7 и 10 предсказанного значения выборки (фиг,4) содержат наборы элементов ИЛИ 7,1 - 7,8 и элементов И 7,9 - 7,21. Первый 8 и второй 9 блоки па-.мяти (фиг,5) содеожат наборы Р-триггеров 8,1- выходе 17 кодера б выходного сигнала фор 8.4,9,1 - 9.4 и блоки 8.5, 9.5 формирования мируется единичный импульс (ц=1), а присигналов управления соответственно попадании в нижний - нулевой (9=0), Всем(фиг.б), Отличие блоков памяти приемной и значениям выборок, попавшим на соответпередающей сторон заключается в отсутст ствующий участок шкалы, приписываетсявии в первом блоке 11 памяти приемной одно оценочное значение, отмеченное крестороны О- триггера для запоминания вы- стиком, Это оценочное значение принимаходного сигнала (позиция 8.1 на фиг.5) и в ется в следующем такте за предсказанноеналичии на входах блоков формированиязначение очередной выборки. Первый блоксигналов управления в первом 11 и втором 10 8 памяти используется для запоминания на12 блоках памяти элементов задержки по- такт выходного сигнала передающей стороступающих сигналов на один такт, В качест- ны (О-триггер Тп 8,1 на фиг,5) а также униве элементов задержки можно тарного кода очереднОго предсказанногоиспользовать, например, О-триггеры, вклю- значения выборки (О-триггеры 8.2 - 8.4 начаемые на входах блоков формирования 15 фиг,5). Второй блок 9 памяти используетсясигналов управления. Блок 13 восстановле- для хранения предсказанного значенияния сигнала (фиг.9) содержит последова- предшествующей выборки, Еще по одномутельно соединенные шифратор 13.1, Р-триггеру используется в этих блоках дляцифроаналоговый преобразователь (ЦАП) запоминания информации о начале работы13,2 и фильтр нижних частот 13.3. 20 системы (О-триггер Кст 9,1 на фиг,5 во втоСистема бинарного кодирования и де- ром блоке 9 памяти передающей стороны икодирования сигналов работает следующим соответствующий О-триггер во втором блообразом, ке 12 памяти приемной стороны).Для перевода системы в исходное со- На первом интервале(т 1. 12) предсказанстояние (момент времени то на фиг,8) й-Я ное значение выборки равно нулю ( = О, То=триггеры блоков 8.5, 9,5 формирования =1) и в единичном состоянии находится Рсигналов управления (фиг,5,6) устанавлива- триггер Кст 9.1, указывающий на начало преются в единичное состояние, Аналогичная образования. Поэтому кодирование на этомоперация производится на приемной сторо- участке осуществляется по шкале, указанне системы Все О-триггеры блоков 30 ной в левом столбцетаблицы. Кодирование8,9,11,12 памяти переводятся в нулевые со- выходного сигнала передающей стороныстояния, Для упрощения чертежей цепи на- осуществляется кодером 6 выходногосигначальной установки на фигурах не показаны, ла, на который поступает выходной код АЦППервым импульсом синхропоследова- а а 2 аз а, выходные сигналы а 1, а 2, аз, а 4,тельности в момент времени т 1 (фиг,8) О Ь 1,Ь 2,ЬЗ, Ь 4,блока 5 дешифрации,выходныетриггер 8,2 первого блока 8 памяти и сигйалы Т, То - Т 15 О-триггеров 8,1 - 8.4О-триггер 9,1 второго блока 9 памяти пере- первого блока 8 памяти и выходные сигналыдающей стороны переводятся в единичное К К 1 - К 15 О-триггеров 9.1 - 9,4 второгосостояние, а все остальные О-триггеры этих блока 9 памяти передающей стороны,.Рабоблоков и блоков памяти приемной стороны 40 та и структура кодера б выходного сигналаостаются в нулевых состояниях. Одновре- описывается логическими выражениями вименно на выходе аналого-цифровогопреоб- да;разователя 4 фиксируется и-разрядный кодпервой выборки(в рассматриваемом приме. р = (ТчКчт+ ТККч+ КкаЬ 1 ч (Т 1 ККо+ кк)+ре п=4), 45 т Тв(Уч т К 1) а 1(О ч Ьк 1 т+ (Тг(йо+ К 1) + Тзйк) кНа интервале (т 1, и) происходит кодиро- (а 1 + а 2 + а 1 Ь 4) + (ТЗК 2+ Т 4(Ко+ К 9+ К 1 о+ К 11+вание первой выборки. принцип кодирова- + к 4)+(т 5(к 6+ к 11)( а 1 +а 2 ) +(т 4(к 1+ кз)+ния поясняется таблицей на фиг.7. Каждому +Т 5(К 5+ К 7) + Тг(Ка+ К 9)(а 1 + а 2 Ь 1) + (Т 5(КЗ+)-му предсказанному значению предшест- (Т (К + К + К)+ Г (К + К К ) Т (Квующей выборки (в рассматриваемом при- +К )+ Т К. ) +(Т (К К) Т (Кмере ,)с(0,1,15) соответствует своя шкала +К )+Т К )( Ь ) (Т (К )квантования, приведенная в столбце, отмеенном указанными значениямии) Каж 55 (Т 1 1 гК 1 Кдая шкала состоит из двух участков,разделенных горизонтальной чертой. П ипопаданий очередной выборки (значения +К+ Т+ К+К 15) + Т 14(К 1 з + К 1 ва 4 Ь 1 + %4(1 з + К 15верхний участок соответствуоотеи шкапы ивСигналы, соответствующие переменным а и Ь, используемым в этом выражении, формируются на выходе 16 блока 5 дешифрации, работа и структура которого описываются формулами. 5 Ь 1= аЗ Б Ь 2 = (УЗ Х 4 Ьз= ЯзЩ Ь 4 = (23(24 (2) 10 Й 1 Йг Й 1 ГХ 2 Х 1 О,2 Ф Сг а 1= а 2= Т 0 = (ТОКст + Т 1(КО + К 2) + Т 2 К 69Т 1 = (Т 1(КО+ К 2) + Т 2(КО+ К 1+ Кб) + ТзК 5++Т 13 К 9+ Т(К 13+ К 159 В результате обработки на выходе 17 кодера 6 выходного сигнала формируется сигнал д, соответствующий участку шкалы, внутри которого находится код первой вы-. борки (в нашем примере 9 = О). Этот сигнал поступает одновременно на О-вход О-триггера 8,1 первого блока 8 памяти и на вход кодера 7. предсказанного значения выборки. На другие входы кодера 7 предсказанно го значения выборки подается унитарный код тоТ 1 т 15 предсказанного значения выборки (на первом интервале - это код 1000) и код КстКОК 1 К 15 с выхода 21 второго блока 9 памяти, На первом интервале - это код 1000, Работа и структура кодера предсказанного значения выборки описывается логическими выражениями:30 Т 12 = (Т 7(КЗ + К 4) + ТЯК 5 + Т 11(К 11 + К 13++К 14) + Т 12(К 13 + К 159 + (Т 13(К 9 + К 14 + К 15) + +Т 15 К 15) 9Т 13 =- (Тд(К 4 + Кб) + Т 10 (К 7 + Кд) + Т 11(КО + +К 10) + Т 12(К 11+ К 12) + Г 13(К 14+ К 15)9 + (Т 14(К 13+ + К 15) + Т 15(К 13+ К 14)9Т 14 = (Т 1 ОК 5+ Т 11(Кб + К 7 + Кв) + Т 12(К 7+ +К 8) + Т 13(К 9 + К 14 + К 15) + Т 14(К 13 + К 15) + +Т 15 К 15) 9Т 15 = (Т 13 К 9+ Т 14(К 13+ К 15) + Т 15 К 15)9 (3) В результате выполнения указанных вычислений на выходе 18 кодера 7 предсказанного значения выборки формируетсяунитарный код ТОТ( Т(2 Т 15 (в нашем случае - это код четырех; 0000100), Таким образом, к концу первого такта на О-вход соответствующего О-триггера первого блока 8 памяти подается единичный сигнал, Единичный сигнал присутствует в это время и на О-входе О-триггера 9,2 второго блока 9 памяти, Следующим тактовым импульсом в момент времени 12 указанные триггеры переводятся в единичное состояние. Одновременно в единичное состояние устанав-. ливаются О-триггеры То и Кст первого 11 и второго 12 блоков памяти приемной стороны, Таким образом, состояние О-триггеров первого 11 и второго 12 блоков памяти приемной стороны повторяют состояния соответствующих триггеров первого 8 и второго 9 блоков памяти передающей стороны в предшествующем такте, Все остальные . триггеры блоков памяти переводятся в нулевые состояния, Одновременно на выходе 15 аналого-цифрового преобразователя 4 фиксируется код второй выборки.В соответствии с таблицей на фиг,7 кодирование на интервале (тг, 13) осуществляется по шкале, соответствующей предсказанному значению выборки, равному четырем =4) и нулевому предсказанному значению предшествующей выборки 0=0). На этом интервале на выходе 17 кодера выходного сигнала б формируется сигнал 9= 1, а на выходе 18 кодера 7 предсказанного значения выборки унитарный код ТОТ 1 Т 6 Т 15 (00000010,0), соответствующий ( = 6, Одновременно с выхода 23 первого блока 11 памяти приемной стороны снимается унитарный код предсказанного значения первой выборки, а на входах О-триггеров этого блока формируется унитарный код предсказанного значения второй выборки. Следующим тактовым импульсом в момент сз в первый блок 8 памлти заносится унитарный код предска-, занного значения очередной выборки (1 = 6), а во второй блок 9 памяти передающей стороны и первый блок 11 памяти приемной стороны заносится унитарный код предсказанного значения предшествующей выборки О=4), а во второй блок 12 памяти приемной стороны - предсказанное значение первой выборки. Одновременно на выходе аналого-цифрового преобразователя 4 фиксируется код третьей выборки, На интервале 1 з, т 4) на передающей стороне происходит кодированиа третьей выборки, Одновременно на выходе 22 кодера 10 предсказанного значения выборки приемной стороны формируется унитарный код предсказанного значения третьей выборки (1=6), а на выходе 25 блока 13 восстановления формируется сигнал%(1), аппроксимирующий сигнал Х(т) на участке 11 Л 2. Далее процесс преобразования протекает аналогично. Для наглядности сигнал 3(с) на фиг,8 сдвинут влево на два такта.В системе бинарного кодирования и декодирования сигналов время, затрачиваемое на кодирование, складывается из времени выполнения логических операций в блоке 5 дешифрэции, в кодере 6 выходного сигнала, кодере 7 предсказанного значения выборки и времени записи информации в первый 8 и второй 9 блоки памяти, При реализации системы на серийных интегральных схемах транзисторно-транзисторной логики время. затрачиваемое на кодирова ние не превышает 70 нсек, что соответствует тактовой частоте порядка 14 МГц,Перестраиваемыми параметрами шкал квантования, используемыми в процессе кодирования - декодирования, являются пороговые уровни и оценочные значения кодируемых выборок. При выборе шкал квантования на очередном такте кодирования учитываются не только величины и знаки приращений выборок в предшествующих тактах, но и сами предсказанные значения выборок. Это позволяет повысить точность преобразования. Формула изобретенияСистема бинарного .кодирования и декодирования сигналов, содержащая канал связи, на передающей стороне - аналогоцифровой преобразователь, информационный вход которого является информационным входом системы, выходы аналого-циф рового преобразователя соединены спервыми входами кодера выходного сигна ла, первый и второй блоки памяти, на приемной стороне - первый блок памяти и блок восстановления сигнала, выход которого является выходом системы, о т л и ч а ю щ а яс я тем, что, с целью повышения быстродей ствия и точности системы, в нее введены напередающей стороне кодер предсказанного значения выборки и блок дешифрации, входы которого подключены к соответствующим выходам аналого-цифрового 15 преобразователя, выходы блока дешифрации соединены с вторыми входами кодера выходного сигнала, выход которОго подключен к первым входам первого блока памяти и кодера предсказанного значения выбор ки, выходы которого соединены с вторымивходами первого блока памяти, первый выход которого подключен к входу канала связи, вторые выходы первого блока памяти соединены с третьими входами кодера вы ходкого сигнала, вторыми входами кодерапредсказанного значения выборки и информационными входами второго блока памяти, выходы которого подключены к четвертьм входам" коДера выходного сигна ла и третьим входам кодера предсказанногозначения выборки, на приемной стороне - второй блок памяти и кодер предсказанного значения выборки, первый вход которого подключен к выходу канала связи, выходы 35 кодера предсказанного значения выборкисоединены с информационными входами первого блока памяти, выходы которого подключеньг"к входам блока восстановления сигнала, первым входам кодера пред сказанного значения выборки иинформационным входам второго блока памяти, выходы которого соединены с третьими входами кодера предсказанного значения выборки, входы синхронизации 45 аналого-цифрового преобразователя и блоков памяти передающей стороны и блоков памяти приемной стороны объединены и являются входом сийхронизации системы.1781823 Составитель А.ХодоровскиТехред М,Моргентал ктор Т,Пал Ре р Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101 аказ 4282 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4880950, 14.11.1990

ЦЕНТР НАУЧНО-ТЕХНИЧЕСКОЙ ДЕЯТЕЛЬНОСТИ ИССЛЕДОВАНИЙ И СОЦИАЛЬНЫХ ИНИЦИАТИВ

ХОДОРОВСКИЙ АЛЕКСАНДР ЗИНОВЬЕВИЧ, ВОЛКОВ АЛЕКСАНДР МИХАЙЛОВИЧ

МПК / Метки

МПК: H03M 3/00, H03M 7/34, H04B 14/06

Метки: бинарного, декодирования, кодирования, сигналов

Опубликовано: 15.12.1992

Код ссылки

<a href="https://patents.su/9-1781823-sistema-binarnogo-kodirovaniya-i-dekodirovaniya-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Система бинарного кодирования и декодирования сигналов</a>

Предыдущий патент: Устройство для определения абсолютного положения вала исполнительного механизма

Следующий патент: Устройство для приема и передачи информации с многозначным кодированием

Случайный патент: Клиновой огнеупорный кирпич