Устройство для приема и передачи информации с многозначным кодированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1781824

Авторы: Коноплянко, Лосева, Попович

Текст

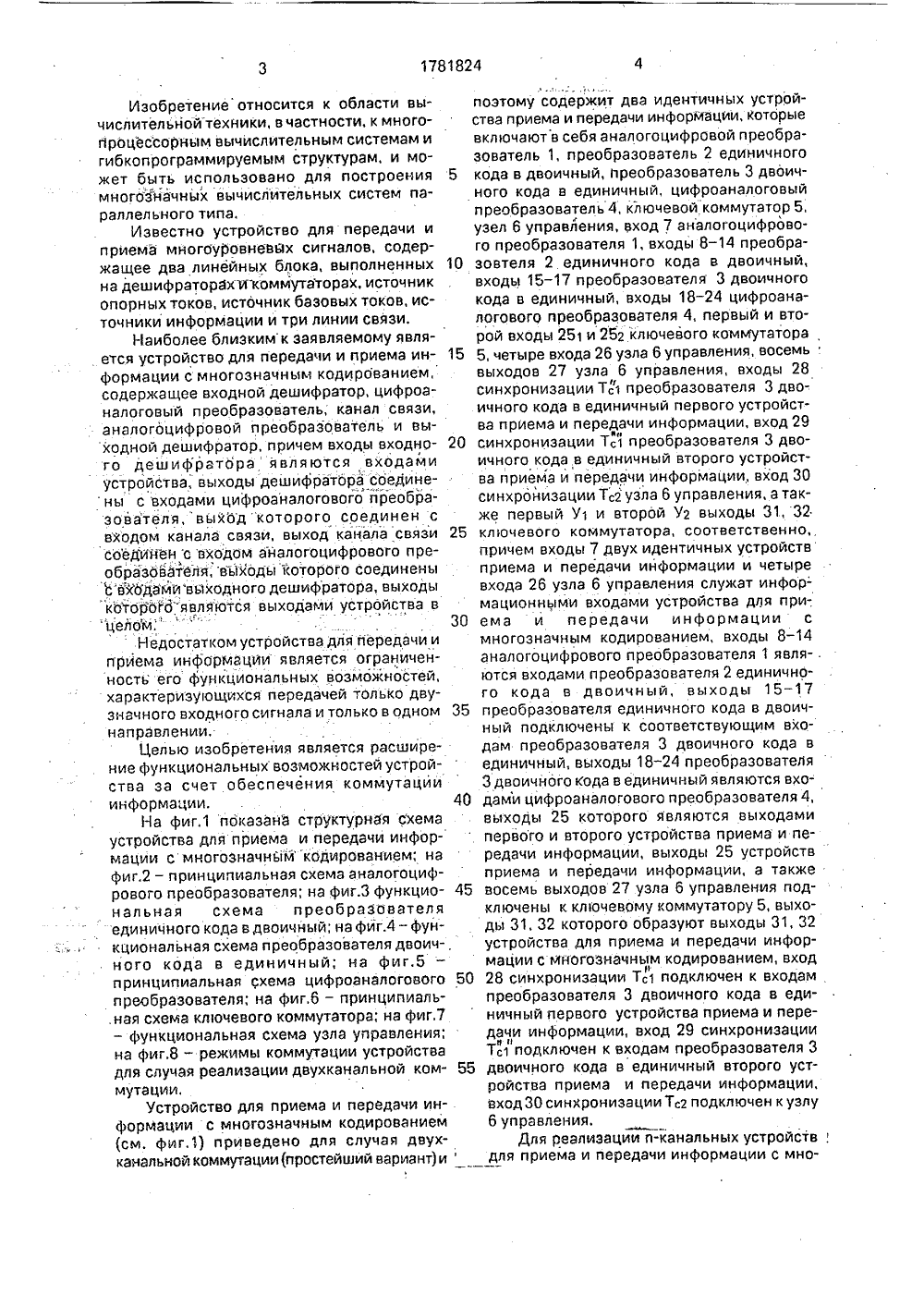

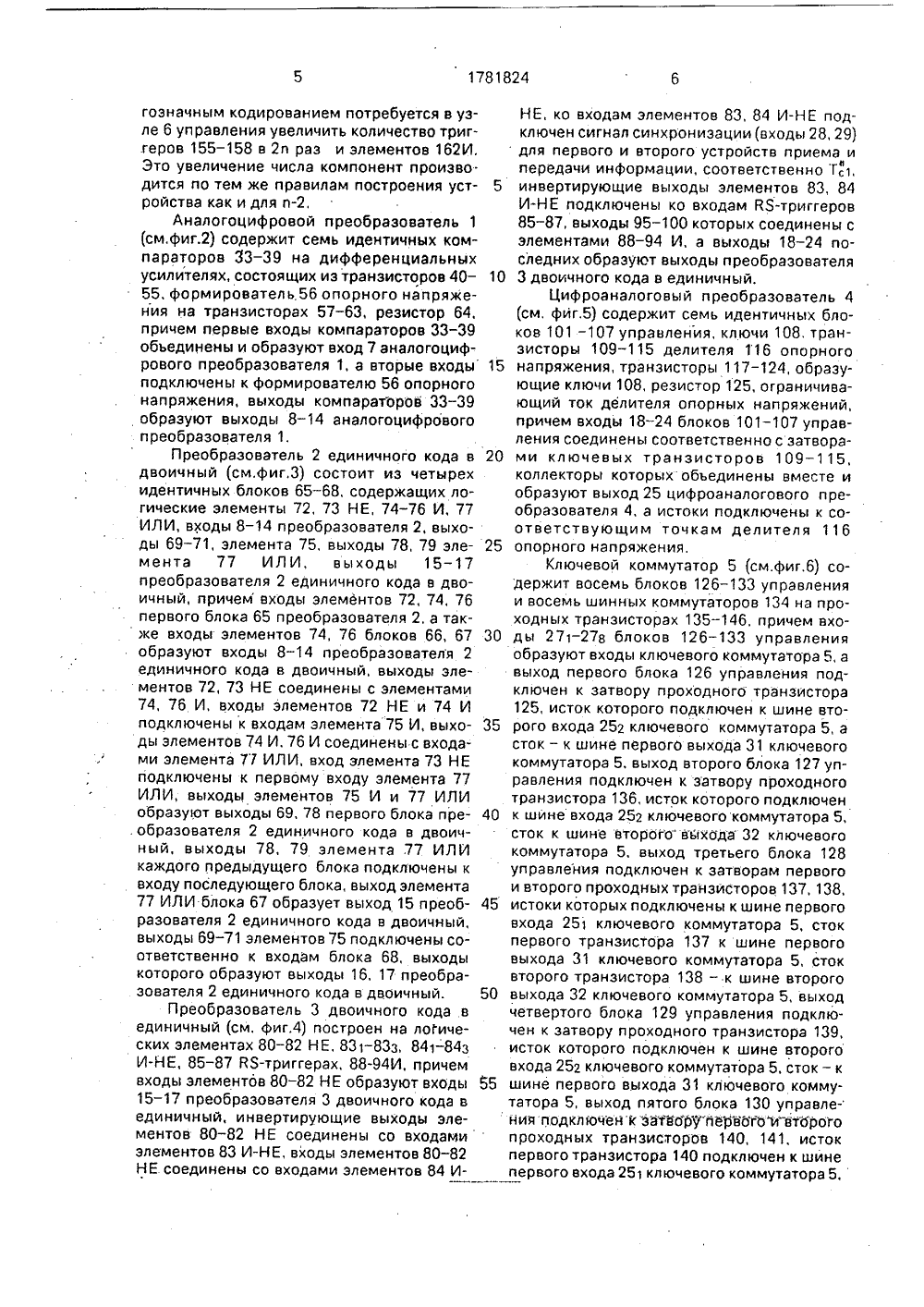

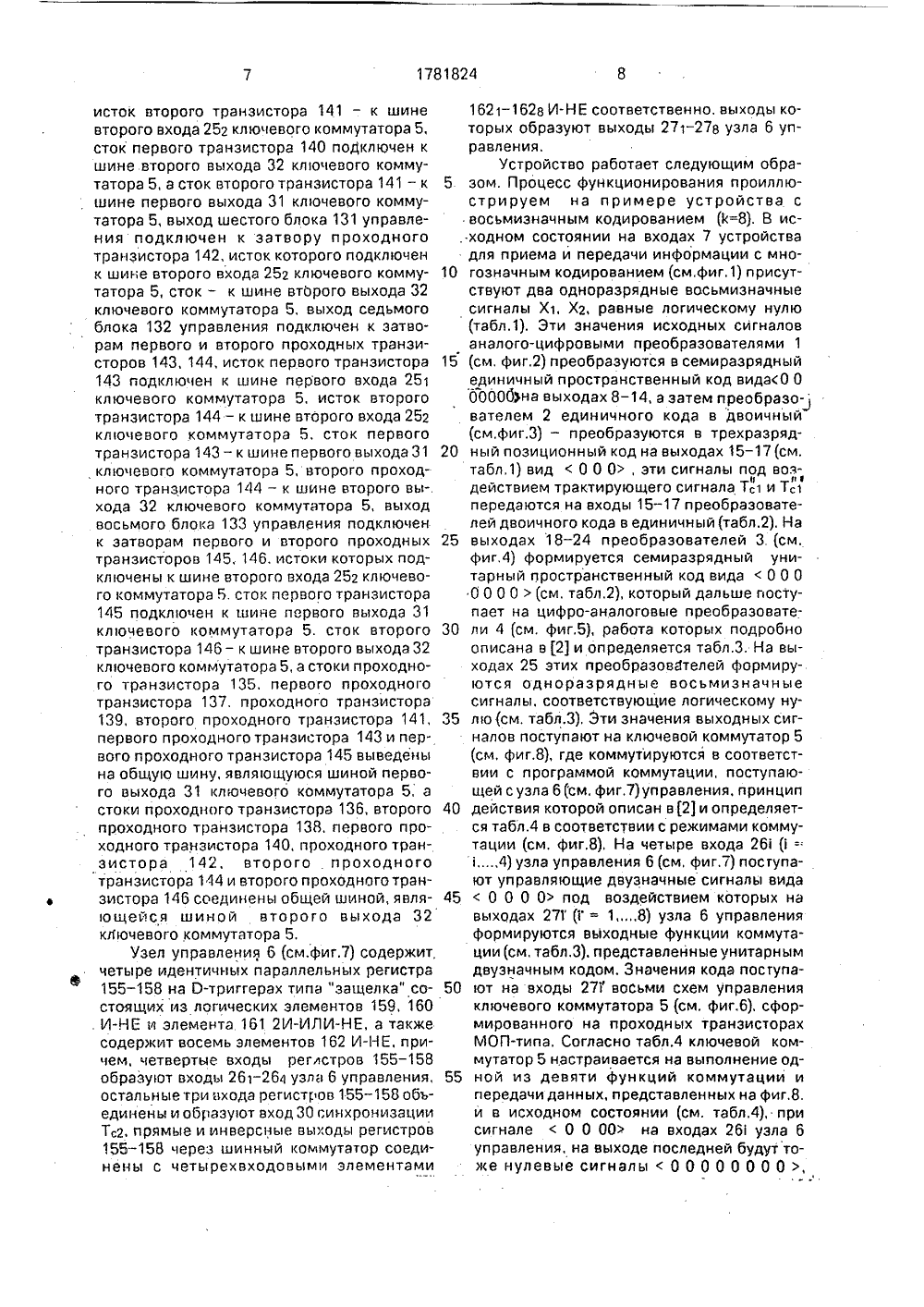

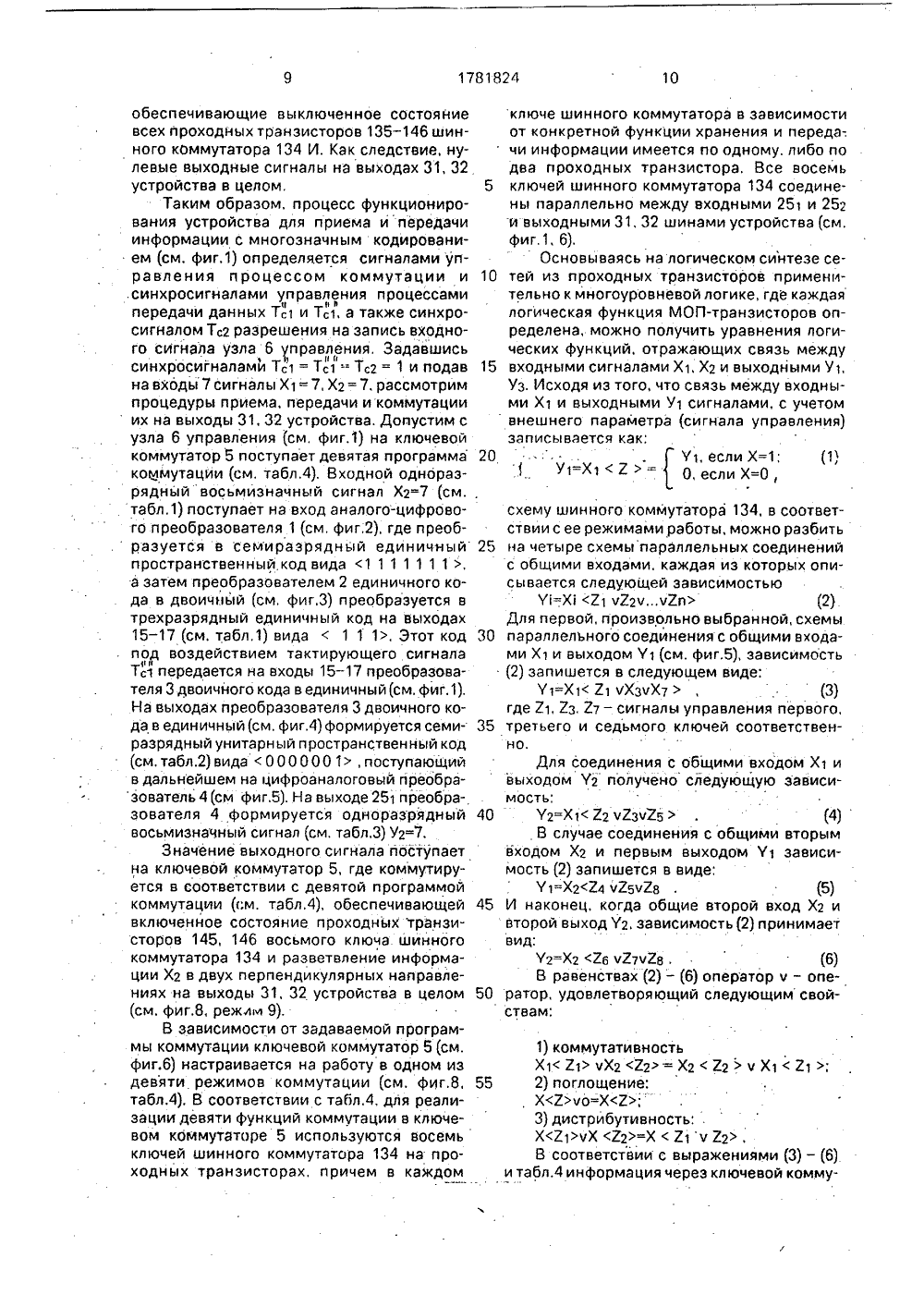

(71) Научно-исследовательский институт бытовой радиоэлектронной аппаратуры (72) З,Д.Коноплянко, Г,Б.Попович йТ.В,Лосева(56) Авторское свидетельство СССР М 1203565, кл. 6 08 С 19/28, 1983.Авторское свидетельство СССР й 1206830, кл, О 08 С 19/28, 1984.(54) УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ С МЙОГОЗНАЧНЫМ КОДИРОВАНИЕМ ГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(57) Изобретение относится к вычислительной технике, Его использование в многопроцессорных вычислительных системах, например, параллельного типа позволяет расширить функциональные возможности за счет обеспечения коммутации информации, Устройство содержит аналого-цифровой преобразователь 1, преобразователь 2 единичного кода в двоичный, преобразователь 3 двоичного кода в единичный, цифроаналоговый преобразователь 4 и канал 7 связи, Благодаря введению ключевого коммутатора 5 и узла 6 управления, а также дополнительных цепочек блоков 1 - 4, обеспечивается комму. тация входной информации по любому направлению. 2 з.п. ф-лы, 8 ил. 4 табл,19 1781824 20 Таблица 1 аблица 2 3. Устройство по п,1, о т л и ч а ю щ е ес я тем, что преобразователь двоичного кода в единичный содержит первый-третий элементы НЕ, первый-шестой элементы ИНЕ, первый-третий ВЯ-триггеры и первый- седьмой элементы И, первые входы всех элементов И-НЕ объединены и являются тактовым входом преобразователя, вход )- го элемента НЕ =1,2,3) объединен с вторым входом 2)-го элемента И-НЕ и является соответствующим входом преобразователя, выход 1-го элемента НЕ соединен с вторым входом (2)-1)-го элемента И-НЕ, выходы (2)- 1)-го и 2)-го элементов И-НЕ подключены 5 соответственно к В- и Я-входам)-го ВЯ-триггера, прямые и инверсные выходы всех ВЯ- триггеров подключены к соответствующим входам первого-седьмого элементов И, выходы которых являются выходами преобра зователя.1781824 режии 2 е режим 5 м жии жии ре мишинец.Макси Реда кт Коррек аказ 4282 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям 113035, Москва, Ж; Раущская наб., 4/5 ГКНТ СС Производственно-издательский комбинат "Патент", г, Ужгород, ул,Гагарина, 1 О 1 Составитель ГТехред М.Мор повинталИзобретениеотносится к области вы- поэтому содержит два идентичных устрой- числительнойтехники, в частности, к много- ства приема и передачи информацйи, которые процессорным вычислительным системам и включают в себя аналогоцифровой преобрэгибкопрограммируемым структурам, и мо- зовэтель 1, преобразователь 2 единичного жет быть использовано для построения 5 кода в двоичный, преобразователь 3 двоичмногозначных вычислительных систем па- ного кода в единичный, цифроаналоговый раллельного типа. преобразователь 4, ключевой коммутатор 5,Известно устройство для передачи и узел 6 управления, вход 7 аналогоцифровоприемэ многоуровневйх сигналов, содер- го преобразователя 1, входы 8 - 14 преображащее два линейных блока, выполненных 10 зовтеля 2 единичного кода в двоичный, на дешифраторэхИ коммутаторах, источник . входы 15-17 преобразователя 3 двоичного опорных токов, источник базовых токов, ис- кода в единичный, входы 18 - 24 цифроанаточники информации и три линии связи. логового преобразователя 4, первый и втоНаиболее близкимк заявляемому явля- рой входы 251 и 252 ключевого коммутатора ется устройство для передачи и приема ин 5, четыре входа 26 узла 6 управления, восемь формации с многозначным кодированием, выходов 27 узла 6 управления, входы 28 содержащее входной дешифратор, цифроа- синхронизации ТС 1 преобразователя 3 двоналоговый преобразователь, канал связи, ичного кода в единичный первого устройстэналогоцифровой преобразователь и вы- ва приема и передачи информации, вход 29 ходной дешифратор, причем входы входно синхронизации Тд преобразователя 3 двого дешифратора являются входами ичного кода в единичный второгоустройстустройства, выходы дешифратора соедине- ва приема и передачи информации, вход 30нь 1 с входами цифроаналогового преобра- синхронизации ТС 2 узла 6 управления, а такзователя, выход которого соединен с же первый У 1 и второй У 2 выходы 31, 32 входом канала связи, выход канала связи 25 ключевого коммутатора, соответственно, соединенсвходом аналогоцифрового пре- причем входы 7 двух идентичных устройств образователя,выходы которого соединены приема и передачи информации и четыре с"вхбдэмйвыходного дешифраторэ, выходы входа 26 узла 6 управления служат инфор- которого"являются выходами устройства в мационными входами устройства для при 30 ема и передачи информации сНедостаткомустройствадляпередачии многозначным кодированием, входы 8-14 ириема информации является ограничен- аналогоцифрового преобразователя 1 явля- . ность его функциональнь 1 х возможностей, ются входами преобразователя 2 единично- характеризующихся передачей только дву- го кода в двоичный, выходы 15 - 17 значноговходногосигналаитольководном 35 преобразователя единичного кода в двоичнаправлении, ный подключены к соответствующим вхоЦелью изобретения является расшире- дэм преобразователя 3 двоичного кода в ние функциональных возможностей устрой-единичный, выходы 18-24 преобразователя ства за счет обеспечения коммутации 3 двоичного кода в единичный являются вхоинформации. 40 дами цифроаналогового преобразователя 4,На фиг,1 покэзэна структурная схема выходы 25 котороо являются выходами устройства для приема и передачи инфор- первого и второго устройства приема и пемэции с многозначным кодированием; на редачи информации, выходы 25 устройств фиг.2 - принципиальнаясхемааналогоциф- приема и передачи информации, а также рового преобразователя; на фиг.З функцио восемь выходов 27 узла 6 управления поднальная схема преобразователя ключены к ключевому коммутатору 5, вь 1 хоединичного кода в двоичный; на фиг.4 - фуй- ды 31, 32 которого образуют выходы 31, 32 кциональная схема преобразователя двоич-, устройства для приема и передачи инфорного кода в единичный; на фиг.5 - мациис мйогозначным кодированием, вход принципиальная схема цифроаналогового 50 28 синхронизации Т 1 подключен к входам преобразователя; на фиг,6 - принципиаль- преобразователя 3 двоичного кода в еди.ная схема ключевого коммутатора; нэ фиг,7 ничный первого устройства приема и пере - функциональная схема узла управления; дачи информации, вход 29 синхронизации на фиг.8 - режимы коммутации устройства Тс 1 подключен к входам преобразователя 3 для случая реализациидвухканальной ком двоичного кода в единичный второго устмутации, ройства приема и передачи информации,Устройство для приема и передачи ин- вход 30 синхронизацииТС 2 подключенкузлу формации с многозначным кодированием 6 управления.(см. Фиг.1) приведено для случая двух- Для реализации и-канальных устройств, канальной коммутации(простейший вариант) идля приема и передачи информации с мно10 объединены и образуют вход 7 аналогоцифрового преобразователя 1, а вторые входы 15подключены к формирователю 56 опорного 20 25 30 50 входы элементов 80-82 НЕ образуют входы 55 15-17 преобразователя 3 двоичного кода в единичный, инвертирующие выходы элементов 80 - 82 НЕ соединены со входами элементов 83 И-НЕ, входы элементов 80 - 82 НЕ соединены со входами элементов 84 Игозначным кодированием потребуется в узле 6 управления увеличить количество триггеров 155-158 в 2 п раз и элементов 162 И, Это увеличение числа компонент произво. дится по тем же правилам построения устройства как и для п,Аналогоцифровой преобразователь 1 (см,фиг.2) содержит семь идентичных компараторов 33-39 на дифференциальных усилителях, состоящих из транзисторов 40 - 55, формирователь,56 опорного напряжения на транзисторах 57-63, резистор 64, причем первые входы компараторов 33-39 напряжения, выходы компараторов 33 - 39 образуют выходы 8-14 аналогоцифрового преобразователя 1. Преобразователь 2 единичного кода в двоичный (см.фиг,3) состоит из четырех идентичных блоков 65 - 68, содержащих логические элементы 72, 73 НЕ, 74 - 76 И, 77 ИЛИ, входы 8 - 14 преобразователя 2, выходы 69-71, элемента 75, выходы 78, 79 элемента 77 ИЛ И, выходы 15 - 17 преобразователя 2 единичного кода в двоичный, причем входы элементов 72, 74, 76 первого блока 65 преобразователя 2, а также входы элементов 74, 76 блоков 66, 67 образуют входы 8 - 14 преобразователя 2 единичного кода в двоичный, выходы элементов 72, 73 НЕ соединены с элементами 74, 76 И, входы элементов 72 НЕ и 74 И подключены к входам элемента 75 И, выходы элементов 74 И, 76 И соединены с входами элемента 71 ИЛИ, вход элемента 73 НЕ подключены к первому входу элемента 77 ИЛИ, выходы элементов 75 И и 77 ИЛИ образуют выходы 69, 78 первого блока пре.образователя 2 единичного кода в двоичный, выходы 78, 79 элемента 77 ИЛИ каждого предыдущего блока подключены к входу последующего блока, выход элемента 77 ИЛИ блока 67 образует выход 15 преобразователя 2 единичного кода в двоичный, выходы 69 - 71 элементов 75 подключены соответственно к входам блока 68, выходы которого образуют выходы 16, 17 преобразователя 2 единичного кода в двоичный.Преобразователь 3 двоичного кода в единичный (см, фиг.4) построен на логических элементах 80 - 82 НЕ, 831-83 з, 841-84 з И-НЕ, 85-87 ВЯ-триггерах, 88-94 И, причем 35 40 45 НЕ, ко входам элементов 83, 84 И-НЕ подключен сигнал синхронизации (входы 28, 29) для первого и второго устройств приема и передачи информации, соответственно Т, инвертирующие выходы элементов 83, 84 И-НЕ подключены ко входам ЯЯ-триггеров 85-87, выходы 95 - 100 которых соединены с элементами 88-94 И, а выходы 18-24 последних образуют выходы преобразователя 3 двоичного кода в единичный.Цифроаналоговый преобразователь 4 (см, фиг,5) содержит семь идентичных блоков 101 -107 управления, ключи 108, транзисторы 109 - 115 делителя 116 опорного напряжения, транзисторы 117-124, образующие ключи 108, резистор 125, ограничивающий ток делителя опорных напряжений, причем входы 18 - 24 блоков 101 - 107 управления соединены соответственно с затворами ключевых транзисторов 109 - 115, коллекторы которых объединены вместе и образуют выход 25 цифроаналогового преобразователя 4, а истоки подключены к соответствующим точкам делителя 116 опорного напряжения,Ключевой коммутатор 5 (см.фиг.6) содержит восемь блоков 126 - 133 управления и восемь шинных коммутаторов 134 на проходных транзисторах 135 - 146, причем входы 271 - 278 блоков 126 - 133 управления образуют входы ключевого коммутатора 5, а выход первого блока 126 управления подключен к затвору проходного транзистора 125, исток которого подключен к шине второго входа 252 ключевого коммутатора 5, а сток - к шине первого выхода 31 ключевого коммутатора 5, выход второго блока 127 управления подключен к затвору проходного транзистора 136, исток которого подключен к шиневхода 252 ключевого коммутатора 5, сток к шине второго-выхода 32 ключевого коммутатора 5, выход третьего блока 128 управления подключен к затворам первого и второго проходных транзисторов 137, 138, истоки которых подключены к шине первого входа 251 ключевого коммутатора 5, сток первого транзистора 137 к шине первого выхода 31 ключевого коммутатора 5, сток второго транзистора 138 - к шине второго выхода 32 ключевого коммутатора 5, выход четвертого блока 129 управления подключен к затвору проходного транзистора 139, исток которого подключен к шине второго входа 252 ключевого коммутатора 5, сток - к шине первого выхода 31 ключевого коммутатора 5, выход пятого блока 130 управле- ния подключенк "затвору"Первого и второго проходных транзисторов 140, 141, исток первого транзистора 140 подключен к шине первого входа 251 ключевого коммутатора 5,исток второго транзистора 141 - к шине второго входа 252 ключевого коммутатора 5, сток первого транзистора 140 подключен к шине второго выхода 32 ключевого коммутатора 5, а сток второго транзистора 141 - к шине первого выхода 31 ключевого коммутатора 5, выход шестого блока 131 управления подключен к затвору проходного транзистора 142, исток которого подключен к шине второго входа 252 ключевого коммутатора 5, сток - к шине второго выхода 32 ключевого коммутатора 5, выход седьмого блока 132 управления подключен к затворам первого и второго проходных транзисторов 143, 144, исток первого транзистора 143 подключен к шине первого входа 251 ключевого коммутатора 5, исток второго транзистора 144 - к шине второго входа 252 ключевого коммутатора 5, сток первого транзистора 143 - к шине первого выхода 31 ключевого коммутатора 5, второго проходного транзистора 144 - к шине второго выхода 32 ключевого коммутатора 5, выход восьмого блока 133 управления подключен к затворам первого и второго проходных транзисторов 145, 146, истоки которых подключены к шине второго входа 252 ключевого коммутатора 5. сток первого транзистора 145 подключен к шине парного выхода 31 клочевого коммутатора 5. сток второго транзистора 146 - к шине второго выхода 32 ключевого коммутатора 5, а стоки проходного транзистора 135, первого проходного транзистора 137, проходного транзистора 139, второго проходного транзистора 141, первого проходного транзистора 143 и первого проходного транзистора 145 выведены на общуо шину, являощуюся шиной первого выхода 31 ключевого коммутатора 5; а стоки проходного транзистора 136, второго проходного транзистора 138, первого проходного транзистора 140, проходного транзистора 142, второго, проходного транзистора 144 и второго проходного транзистора 146 соединены общей шиной, являющейся шиной второго выхода 32 кЛючевого коммутатора 5.Узел управления б (см.фиг,7) содержит, четыре идентичных параллельных регистра 155 - 158 на О-триггерах типа "защелка" состоящих из логических элементов 159, 160 . И-НЕ л элемента 161 2 И-И.ПИ-НЕ, а также содеркит восемь элементов 162 И-НЕ. причем, четвертые входы реглстров 155 - 158 образуют входы 261-26 л узла 6 управления, остальные три входа регистров 155 - 158 объединены и образуют вход ЗО синхронизации Тс 2, прямые и инверсные вьпгоды регистров 155-158 через шинный коммутатор соединены с четырехвходовыми элементами 162 в 16 И-НЕ соответственно, выходы которых образуют выходы 271-278 узла б управления,Устройство работает следующим обра 5 эом. Процесс функционирования проиллюстрируем на примере устройства свосьмизначным кодированием (1=8). В исходном состоянии на входах 7 устройствадля приема и передачи информации с мно 10 гозначным кодированием (см.фиг,1) присутствуют два одноразрядные восьмиэначныесигналы Х 1, Х 2, равные логическому нулю(табл,1). Эти значения исходных сигналованалого-цифровыми преобразователями 115 (см, фиг,2) преобразуются в семиразрядныйединичный пространственный код вида 0 0ООООФна выходах 8-14, а затем преобразо-вателем 2 единичного кода в двоичный(см.фиг,З) - преобразуются в трехразряд 20 ный позиционный код на выходах 15-17 (см.табл,1) вид0 0 0, эти сигналы под возн недействием трактирующего сигнала Т и Т,передаются на входы 15 - 17 преобразователей двоичного кода в единичный (табл.2). На25 выходах 18-24 преобразователей 3 (см.фиг.4) формируется семиразрядный унитарный пространственный код вида0 О 0О 0 О О(см. табл,2), который дальше поступает на цифро-аналоговые преобразовате 30 ли 4 (см. фиг,5), работа которых подробноописана в 2) и определяется табл.З, На выходах 25 этих преобразователей формируются одноразрядные восьмизначныесигналы, соответствующие логическому ну 35 лю(см. табл,З), Эти значения выходных сигналов поступают на ключевой коммутатор 5(см, фиг.8), где коммутируются в соответствии с программой коммутации, поступающей с узла 6 (см, фиг,7) управления, принцип40 действия которой описан в 2 и определяется табл.4 в соответствии с режимами коммутации (см. фиг.8), На четыре входа 26 ( =:4) узла управления 6 (см, фиг,7) поступают управляющие двузначные сигналы вида450 0 0 0 под воздействием которых навыходах 271 ( = 1.8) узла 6 управленияформируются выходные функции коммутации (см, табл.З). представленные унитарнымдвузначным кодом. Значения кода поступа 50 ют на входы 27 восьми схем управленияключевого коммутатора 5 (см. фиг.б), сформированного на проходных транзисторахМОП-типа, Согласно табл.4 ключевой коммутатор 5 настраивается на выполнение од 55 ной из девяти функций коммутации ипередачи данных, представленных на фиг,8,и в исходном состоянии (см. табл.4), присигналеО 0 00 на входах 26 узла 6управления, на выходе последней будут токе нулевые сигналыО 0 0 0 О 0 О 0 ,обеспечивающие выключенное состояние всех проходных транзисторов 135 - 146 шинного коммутатора 134 И. Как следствие, нулевые выходные сигналы на выходах 31, 32 устройства в целом.Таким образом, процесс функционирования устройства для приема и передачи информации с многозначным кодированием (см, фиг.1) определяется сигналами управления процессом коммутации и .синхросигналами управления процессами11 1 Впередачи данных Т 1 и Та. а также синхросигналом ТС 2 разрешения на запись входного сигйала узла 6 управления, Задавшись) ИИсинхросигналами Т,1 = Т,1.ТС 2 = 1 и подав на входы 7 сигналы Х 1= 7, Х 2 = 7, рассмотрим процедуры приема, передачи и коммутации их на выходы 31, 32 устройства. Допустим с узла 6 управления (см, фиг.1) на ключевой коммутатор 5 поступает девятая программа коммутэцйи (см, табл,4), Входной одноразрядный восьмизначный сигнал Х 2=7 (см. табл,1) поступает на вход аналого-цифрового преобразователя 1 (см, фиг,2), где преобразуется в семиразрядный единичный пространственный код вида 1 1 1 1 1 1 1 , а затем преобразователем 2 единичного кода в двоичный (см, фиг,З) преобразуется в трехразрядный единичный код на выходах 15 - 17 (см. табл,1) вида1 1 1, Этот код под воздействием тактирующего сигналаиТс 1 передается на входы 15-17 преобразователя 3 двоичного кода в единичный (см, фиг.1). На выходах преобразователя 3 двоичного кода в единичный (см, фиг,4) формируется семи- разрядный унитарный пространственный код (см. табл.2) вида0 О О О О О 1, поступающий в дальнейшем на цифроаналоговый преобразователь 4 (см фиг.5), На выходе 251 преобразователя 4 формируется одноразрядный восьмизначный сигнал (см. табл,З) У 2=7.Значение выходного сигнала поступает на ключевой коммутатор 5, где коммутируется в соответствии с девятой программой коммутации (см, табл,4), обеспечивающей включенное состояние проходных транзисторов 145, 146 восьмого ключа. шинного коммутатора 134 и разветвление информации Х 2 в двух перпендикулярных направлениях на выходы 31, 32 устройства в целом (см, фиг,8, режлм 9),В зависимости от задаваемой программы коммутации ключевой коммутатор 5 (см, фиг.б) настраивается на работу в одном из девяти режимов коммутации (см. фиг,8, табл.4). В соответствии с табл,4, для реализации девяти функций коммутации в ключевом коммутаторе 5 используются восемь ключей шинного коммутатора 134 на проходных транзисторах, причем в каждом ключе шинного коммутатора в зависимостиат конкретной функции хранения и переда-.чи информации имеется по одному, либо подва проходных транзистора, Все восемь5 ключей шинного коммутатора 134 соединены параллельно между входными 251 и 252и выходными 31, 32 шинами устройства (см.фиг.1, 6),Основываясь на логическом синтезе се 10 тей из проходных транзисторов применительно к многоуровневой логике, где каждаялогическая функция МОП-транзисторов определена, можно получить уравнения логических функций. отражающих связь между15 входными сигналами Х 1, Х 2 и выходными У 1,Уз. Исходя из того, что связь между входными Х 1 и выходными У 1 сигналами, с учетомвнешнего параметра (сигнала управления)записывается как:20У 1, если Х=1; (1)У=Х"Е= О, если Х=О,схему шинного коммутатора 134, в соответствии с ее режимами работы, можно разбить25 на четыре схемы параллельных соединенийс общими входами, каждая из которых описывается следующей зависимостьюЮ=Х Е 1 Ч 72 ччсп (2)Для первой, произвольно выбранной, схемыЗО параллельного соединения с общими входами Х 1 и выходом У 1(см, фиг.5), зависимость(2) запишется в следующем виде:У 1=Х 1 г 1 чхзчХ 7 , (3)где 71, 7 з, Ь - сигналы управления первого,35 третьего и седьмого ключей соответственно,Для соединения с общими входом Х 1 ивыходом У 2 получено следующую зависимость40 У 2=х 1 Е 2 ЧЕзч 25. (4)В случае соединения с общими вторымвходом Х 2 и первым выходом У 1 зависимость (2) запишется в виде:У 1=Х 224 ч 25 Ч 78 .(5)45 И наконец, когда общие второй вход Х 2 ивторой выход У 2, зависимость(2) принимаетвид:У 2=Х 2 Еб ч 77 чЕв, (6)В равенствах (2) - (6) оператор ч - опе 50 ратор, удовлетворяющий следующим свойствам:1) коммутативн остьХ 1 1 чХ 2 Е 2 = Х 2Е 2ч Х 1Е 1 :2) поглощение:, Х 7 чо=Х 7;3) дистрибутивность:Х 71 чХ Е 2=ХЕ 1 ч Е 2В соответствии с выражениями (3) - (6)и табл.4 информация через ключевой коммутатор 5 передается одновременно по двум ем, передается через АЦП 1, преобразованезависымим, пересекающимся в про- тель 2 единичного кода вдвоичный, преобстранстве каналам, При этом ключевой ком- разователь 3 двоичного кода в единичный и мутатор 5 в соответствии с сигналами ЦАП 4 первогоустройства для приема и пеуправления, поступающими с узла 6 управ редачи информации на ключевой коммуталения (см. табл.4), может передавать много- тор 5, где коммутируется и через проходной значные сигналы Х, Х 2 по двум транзистор 136 второгоключашинногокомнезависимым каналам 251 и 252 в прямом мутатора 134 поступает в перпендикулярнапдавлении, разветвлять информацию в ном направлении на выход 32 У и далее на двух пространственных направлениях, из вход последующего устройства,менять направление передачи информации, В том случае, когда на узел управления передавать информацию подвум независи подается сигнал=0 0 (см, табл,4), мым, пересекающимся или разветвляю- ключевой коммутатор 5 настраивается на щимся в пространстве каналам(см.фиг.8). разветвление информации из первого уст(примеру, в случае поступления на вхо ройства для приема и передачи информации ды 26 узла управления 6 (см,фиг,7) управля- (см. фиг.8, режим 4), Информация Х 1, постующего сигнала= 0 0 0 0 (см. табл,4, режим пившая на вход первого устройства для при), ключевой коммутатор 5 настраивается на ема и передачи -информации в разъединение информационных входов и горизонтальном направлении, через АЦП 1, выходов, в результате чего информация Х 1 и 20 преобраозватель 2 единичного кода в двоХ 2 не проходитчерезустройстводля приема ичный, преобразователь 3 двоичного кода в и передачи информации с многозначным ко- единичный и ЦАП 4 поступает на ключевой дированием (см, фиг.8), Функция разъеди- коммутатор 5, где коммутируется и через нения выполняется также в тех случаях, проходные транзисторы 137, 139 третьего. когда на узел 6 управления поступают уп ключа шинного коммутатора 134 выдается равляющие сигналы00;0; 00 ;одновременно в двух перпендикулярных О ;0; О,. , - пространственных направлениях; вПри подаче на узел 6 управления (смгоризонтальном - на выход 31 У и в фиг.7) сигнал=0 0 0(см, табл.4) устройство вертикальном - на выход 32 У,для приема и передачи информации с мно При передаче на узел 6 управления сиггозначным кодированием настраивается, нал= 0 00 (см, табл,4) ключевой коммутана выполнение функции передачи сигнала в тор 5 настраивается на выполнение первом устройстве для приема и передачи функции пространственного поворота ининформации (см. фиг,8, режим 2), При этом формации во втором устройстве для примногозначный сигнал Х поступает через 35 ема и передачи информации (см. фиг.8, аналого-цифровой преобразователь 1 и пре- режим 5). В этом случае многозначный сигобразователь 2 единичного кода в двоичный нал Х 2 поступает в вертикальном направлена входы 16 - 17 преобразователь 3 двоично- нии на второе устройство для приема и го кода в единичный и цифра-аналоговый передачи информации, а затем коммутирупреобразователь первого устройства для 40 ется в ключевом коммутаторе 5 и через проприема и передачи информации, передает- ходной транзистор 139 четвертого ключа ся на входы 25 ключевого коммутатора 5(см. шинного коммутатора выдается в перпендифиг.б). При этом проходные транзисторы кулярном первоначальному горизонталь - 146 закрыты и управляющий сигнал ном направлении на выход 31 У и далее на .схемы 137 управления ключевого коммута последующие устройства.тора 5 поступает на затвор транзистора 135 Если на управляющий вход узла 6 уппервого ключа шинного коммутатора (см, равления поступает сигнал= 00 (см. фиг.б), после чего сигнал Х передается че-. табл.4), то ключевой коммутатор 5 настраирез транзистор 135 в прямолинейном про- вает устройство для приема и передачи инстранствонном направлении на выход У 1. 50 формации на реализацию функции (см. фиг.6 и фиг,8, режим 2), расхождения информации в первом и втоЕсли на узел управления 6 поступает ром устройствах, для приема и передачи сигнал= ОО 0 (см, табл.4), ключевой информации(см. фиг,8, режим 6), При этом коммутатор 5 настраивается на выполнение многозначная информация поступает одно- функции пространствейного поворота ин временно по двум входам 7 Х и Хр как в формации в первом устройстве приема и горизонтальном, так и в вертикальном напередачи информации (см. фиг.8, режим 3). правлениях. Затем информация преобразуПри этом сигнал Х 1. поступивший на вход ется в многозначную, как в первом, так и во первого устройства для приема и передачи втором устройствах для приема и передачи информации с многозначным кодировани- информации, и коммутируется в ключевомкоммутаторе 5, после чего изменяет пространственное направление и расходится:информация Х передается на выход 32 Уг,а информация Хг поступает на выход 31 У 1и далее на вход последующего устройства; 5В случае появления управляющего вектора= 0 0 0(см, табл.4), ключевой коммутатор 5 настраивает устройство для приемаи передачи информации на реализациюфункции прямой передачи информации без 1 Оизменения направления во втором устройстве для приема и передачи информации(см. фиг,8, режим 7), При этом информацияХг поступает на вход второго устройства дляприема и передачи информации и, через 15АЦП 1, преобразователь 2 единичного кодав двоичный, преобразователь 3 двоичногокода в единичный и ЦАП 4 поступает на вход25 ключевого коммутатора 5, где коммутируется и без изменения направления переда. ется на выход 32 (Уг),При передаче на узел управления 6 сигнала=.0 0(см, фиг,8, режим 8) ключевойкоммутатор 5 настраивается на выполнениефункции пространственного пересечения 25информации. В этом случае многозначнаяинформация поступает одновременно надва входа 7 устройства для приема и пере дачи информации в перпендикулярных направлениях, после чего информация беэ 30изменения начального вида передается наключевой коммутатор 5, где коммутируетсяи не меняя пространственного направленияи не разветвляясь передается на выходы:сигнал Х 1 - поступает нд выход 31 (У 1), сигнал Хг - на выход 32 (Уг) и далее на последу. ющие устройства с многозначнымкодированиемНаконец, при появлении последнеговозможного управляющего сигнала= 0 040(см, табл,4), ключевой коммутатор 5 настраивает устройство для и риема и передачи информации на выполнение функцииразветвления информации во втором устройстве для приема и передачи информации (см. фиг,8, режим 9), При этоммногозначный сигнал Хг поступает на вход7 второго устройства для приема и передачиинформации. затем через АЦП 1 преобразователь 2 единичного кода в двоичный, преобразователь 3 двоичного кода в единичныйи ЦАП 4 поступает на ключевой коммутатор5, после чего разветвляется и выдается через выходы 31 (У 1) и 32 (Уг) в двух перпендикулярных направлениях. 55Работа преобразователя 2 единичногокода в двоичный описывается в табл.1 ифиг,3, Сигналы, соответствующие 1-эначным входным сигналам Х и Хг, схемами 1АЦП (см, фиг.8) преобразуются в простран 5) а 6 ч ч(31 аг чЧ 31 дгаз) д 435) 3637 ственный единичный код на выходах 8-14(см, табл.1). Эти единичные сигналы преобразователем 2 преобразуются в трехразрядный позиционный двузначный код. Преобразователь 2 содержит в восьмизначном варианте устройства четыре идентичных каскада 65-68, первые три,входа 8 - 10 которых подключены к младшим разрядам АЦП 1. Сигналы первых трех младших разрядов АЦП 1 преобразуются в сумму значений разрядов первым каскадом 65 преобразователя 2, на выходах 69. 78 которого формируется результат суммирования с переносом соответственно. Логические функции, реализуемые первым каскадом 65 могут быть описаны, в силу специфики отраженного (термометрического) кода (см. табл.1) на выходе АЦП 1, следующими выражениями: Я ет ааг Ч а 1 агаэ, Р 1= ааг В каскаде 66 преобразователя 2 осуществляется, аналогично каскаду 65, суммирование результата предыдущей суммы с четвертым а 4 и пятым 35 разрядами АЦП 1, На выходах 79 и 70 второго каскада 66 преобразователя 2 формируется результат со- . отеетстеенно суммы аа н переноеа Р 2: Яг = 534 ч 5134 д 5, Рг = Я 34 = (а 1 аг ча аг аз)34. В каскаде 67 преобразователя 2 выполняется аналогичное суммирование результатов суммирования предыдущих двух каскадов 65 и 66 преобразователя 2 с шестым а 6 и седьмым 37 разрядами АЦП 1. С первого выхода третьего каскада 67 преобразователя 2, являющегося первым выходом преобразователя поступает окончательный результат суммирования Я. На втором выходе 71 третьего каскада 67 преобразователя 2 формируется результата переносаР = 3236 = 3134 ч 31 а 435) 36 =(ааг ч а 1 агаз) а 4 ч (31 аг 31 агдз)а 435) а 6, который дальше поступает нд вход каскада 68 преобразователя 2,С учетом рекуррентного характера процесса сложения всех семи разрядов, а также . процессов формирования переносов полная сумма обеспечивает преобразование пространственного семиразрядного кода в двузначный позиционный код и сигналы на выходах 15 - 17 преобразователя 2 могут соответственно быть описаны следующими логическими функциями31=5 5286 ч 8 гсГ 637 = (5134 ч 513435) 36 ч ч(Яфа 4 Ч 313435) 3637 =вг = Р 1 = Р 1 Р 2 ч Р 1 Р 2 Рз = а 1 а 251 а 4 ч юж= щйВЛ 3 Ю ЪВТВЮ а,а 2 аз) а 4;вз = Р 2 = Р 1 Р 2 =- а 1 а 231 а 4 = а 1 а 2(а 1 а 2 ч а 1 а 2 аз)а 4,Для рассматриваемого нами примера многозначных сигналов Х 1 = Х 2 = 7 с выходов АЦПна выходы 8 - 14 преобразователя 2 поступа 1 от -семиразрядные коды а 1 а 2 аза 4 а 5 а 8 а 7 =(см. табл,4). При подставке соответствуощих зйачений а ( = 1,7), ВыражЕния в 1-вз дают на выходах 15-17 преобразователя 2 получаем Я = 1, Р 1 = 1, Р 2 =1, что подтверждает правильность выполнения преобразований устройством преобразователя 2,Работа преобразователя 3 двоичного кода в единичный описывается табл,2 и фиг.4, СигналыВ 1 в 2 вз, являющиеся двузначными эквивалентами многозначного кода, поступают с выходов 15 - 17 на дешифратор 3 и преобразуются им "в" семйразрядный унитарный пространственный код на Выходах 18 - 24 (см. табл,2),В восьмизначном варианте преобразователь 3 содержит (см. фиг.4) трйвходных инверторы 80-82, которые совместно со схемами 83, 8 И и ВЯ - триггерами 85-87 формиру 1 от из двузначных сигналов В 1 в 2 вз прямые и инверсные сигналы В 1 В 1 В 2 В 2 взвз, действующие впараллель на трахвходовые коньюнкторы 88-94, На выходах 18-24 коньюнкторов 88-94 образуются соответствующие значения пространственного семиразрядного унитарного кода (см. табл,2). Соответственно этой же таблицы истинности преобразователь 3 формирует СЛЕДУЮЩИЕ ЛОГИЧЕСКИЕ ФУНКЦИИ: С 1=В 1 В 2 ВЗ; С 2="В 1 В 2 ВЗ; СЗ=В 1 В 2 ВЗ; С 4=В 1 В 2 ВЗ с 5=В 1 В 2 ВЗ: Сб=В 1 В 2 ВЗ С 7=В 1 В 2 ВЗ,В рассматриваемом нами примере работы устройства, когда на входы каналов коммутации поданы сигналы Х 1=Х 2=7, с выходов преобразователя 2 на входы 15 - 17 преобразователей поступают сигналы, которые логическими элементами 80 - 84 и триггерами 85-87 преобразуются к виду00О. и поступают на соответствующие входы собственно преобразователя. сформированного из трехвходовых схем 88 - 04 И, На выходах 18-24 образуются 9 (см. табл,2) выходные сигналы видаО О О 0 О 0, которые поступают на соответствующие входы схем 4 цифро-аналоговых преобразователей. Единственная поступившая логическая единица на вход 24 обеспечивает включение седьмого каскада схемы 4, проходного транзистора 115 и подачу на выход 25 (=1,2) сигналов Х 1=Х 2=-7. Выходы 25 соответственно коммутируются схемой 5 ключевого коммутатора по процедурам, описанным ранее.Для хранения управляющих сигналов инастройки ключевого коммутатора 5 в уст ройстве для приема и передачи информациисодержится узел 6 управления (см, фиг,1). В узле 6 используются четыре О-триггера типа "защелка" 155-158 и линейный дешифратор на четыре входа и восемь выходов, состоя щий из элементов И-НЕ (см, фиг,7).Работа узла 6 управления заключаетсяв следующем, На входы 26 узла 6 управления поступают управляющие двузначные сигналы 1 - 4, служащие для настройки узла 15 6 управления (см, фиг,7 и табл.4), Под воздействием вектора управляющих сигналов=- (11, 2, 3, 4) образуются различные типы выходных функций У 1 = Г 1(Х 1 Х 2) и У 2=-1-2(Х 1,Х 2), где Х 1, Хг и У 1, У 2 - входные и 20 выходные к-значные сигналы соответственно, которые приведены в табл,4 и определяют вид передачи данных от входов к выходам устройства для приема и передачи информации с многозначным кодировани ем(см. Фиг,8). После поступления управляющих двузначных сигналов на входы О-триггеров 155 - 158 они дешифруются линейным дешифратором на элементах И-НЕ, после чего на восьми выходах 27 дешифрэ тора формируются сигналы управления11 8:1=4121314, 12=1234, 13 234,4 = 1121314, 15=11121314 16=1234, Г 7 = 1112314, 18 = 11121314 (См, фиг.7) служащие для настройки схем 126- 133 управления ключевого коммутатора 5 35 (см. Фиг.б),Таким образом, предлагаемое устройство для приема и передачи информации с многозначным кодированием позволяет управлять параллельными пространственны ми направлениями движения информации.Выходы устройства свободны от помех, что обусловлено дискретным принципом продвижения данных, Использование преобразователей кодов в устройстве для приема и 45. передачи информации позволяет мультиплицировать и передать многозначные данные в другие устройства, функционирующие в том же многозначном структурном алфавите, Крометого; Введениеи использование 50 преобразователей К-значных сигналов вдвузначные обеспечивает относительное снижение числа внешних связей за счет большей пропускной способности при многозначном кодировании устройства для при ема и передачи информации, К примеру, прииспользовании четырехзначного кодирования и параллельной передачи байта данных число оводов, при параллельной передаче каждого бита данных, увеличивается только в четыре раза. по сравнению с двузначным10 15 20 25 30 35 40 45 50 55 вариантом параллельного байтного передатчика. В четерыхзначном варианте увеличивается также в 2 раза пропускная способность, в восьмизначном - в 3 раза. Использование в устройствах приема и передачи данных с многозначным кодированием ключевого коммутатора позволяет мультиплицировать данные в и перпендикулярных направлениях, что в сложных многопроцессорных системах позволяет пространственным способом решать задачи приоритетов и очередей, расширяя тем самым функциональные воэможности многозначных вычислител ьн ых структур. П редложенный вариант устройства демонстрирует также возможность симбиоза АЦП и ЦАП, а также аналоговых коммутаторов совместно с цифровой двузначной схемотехникой, обеспечивая ми кроэлектронную реализацию многозначного кодирования и многозначных структур и систем. Разработанные логические соотношения, описывающие процессы функционирования устройства позволяют автоматизировать процессы синтеза таких структур и систем с помощью ЭВМ,Формула изобретения 1, Устройство для приема и передачи информации с многозначным кодированием, содержащее первый канал связи, выход которого подключен к входу первого аналого-цифрового преобразователя. выходы которого соединены с входами первого преобразователя единичного кода в двоичный, первый преобразователь двоичного кода в единичный, выходы которого подключены к входам первого цифроаналогового преобразователя, о т л и ч а ю щ е ес я тем, что, с целью расширения функциональных возможностей путем обеспечения коммутации информации. в устройство введены второй - п-й каналы связи(п 2), второй - и-й аналого-цифровые преобразователи единичного кода в двоичный, второй - и-й преобразователи двоичного кода в единицный, второй - п-й цифроаналоговые преобразователи, ключевой коммутатор и узел управления, вход синхронизации и управляющие входы которого являются одноименными входами устройства, выходы узла управления подключены к управляющим входам ключевого коммутатора, выходы первого преобразователя единичного кода в двоичный подключены к информационным входам первого преобразователя двоичного кода в единичный, тактовый вход которого является первым тактовым входом устройства, тактовый вход 1-го преобразователя двоичного кода в единичный 1=2 п) является 1-м тактовым входом устройства,выход 1-го канала связи подключен к входу 1-го аналого-цифрового преобразователя, выходы которого через 1-й преобразователь единичного кода в двоичный подключены к информационным входам 1-го преобразователя двоичного кода в едйнйчный, выходы которого соединены с входами 1-го цифроаналогового преобразователя, выходы первого - и-го цифроаналоговых преобразователей подключены соответственно к первому - и-му информационным входам ключевого коммутатора, первый - и-й выходы которого являются одноименными выходами устройства.2. Устройство по п,1, о тл ича ю щеес я тем, что преобразователь единичного кода в двоичный содержит первый - четвертый логические блоки, каждый из которых включает в себя первый и второй элементы НЕ, первый - третий элементы И и элемент ИЛИ, первые входы первого и второго элементов И первого логического блока объединены и являются первым входом преобразователя, выходы элементов ИЛИ в первом и втором логических блоках подключены к первым входам первого и второго элементов И соответственно во втором и третьем логических блоках, вход первого элемента НЕ и второй вход второго элемента И в каждом из первого-третьего логических блоков объединены и являются соответствующими входами преобразователя, первый вход третьего элемента И в каждом из первого-третьего логических блоков являются соответствующими входами преобразователя, выход второго элемента И первого логического блока соединен с первыми входами первого и второго элементов И четвертого логического блока, выход второго элемента И второго логического блока подключен к входу первого элемента НЕ и второму входу второго элемента И четвертого логического блока, выход второго элемента И третьего логического блока подключен к первому входу третьего элемента И четвертого логического блока, выходы первого и второго элементов НЕ в каждом логическом блоке соединены с вторыми входами соответственно первого и третьего элементов И того же логического блока, выход первого элемента И в каждом логическом блоке соединен с первым входом элемента ИЛИ и входом второго элемента НЕ того же логического блока, выход третьего элемента И в каждом логическом блоке подключен к второму входу элемента ИЛИ того же логического блока, выход элемента ИЛИ третьего логического блока и выходы элемента ИЛИ и второго элемента И четвертого логического блока являются соответствующими выходами преобразователя,

СмотретьЗаявка

4877150, 24.10.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ БЫТОВОЙ РАДИОЭЛЕКТРОННОЙ АППАРАТУРЫ

КОНОПЛЯНКО ЗЕНОВИЙ ДМИТРИЕВИЧ, ПОПОВИЧ ГАЛИНА БОГДАНОВНА, ЛОСЕВА ТАТЬЯНА ВИТАЛЬЕВНА

МПК / Метки

МПК: G08C 19/28, H03M 5/20

Метки: информации, кодированием, многозначным, передачи, приема

Опубликовано: 15.12.1992

Код ссылки

<a href="https://patents.su/17-1781824-ustrojjstvo-dlya-priema-i-peredachi-informacii-s-mnogoznachnym-kodirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема и передачи информации с многозначным кодированием</a>

Предыдущий патент: Система бинарного кодирования и декодирования сигналов

Следующий патент: Пороговый декодер сверточного кода

Случайный патент: Способ изготовления арматурного каркаса железобетонной напорной трубы с отводом