Устройство для вычисления локаторов ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

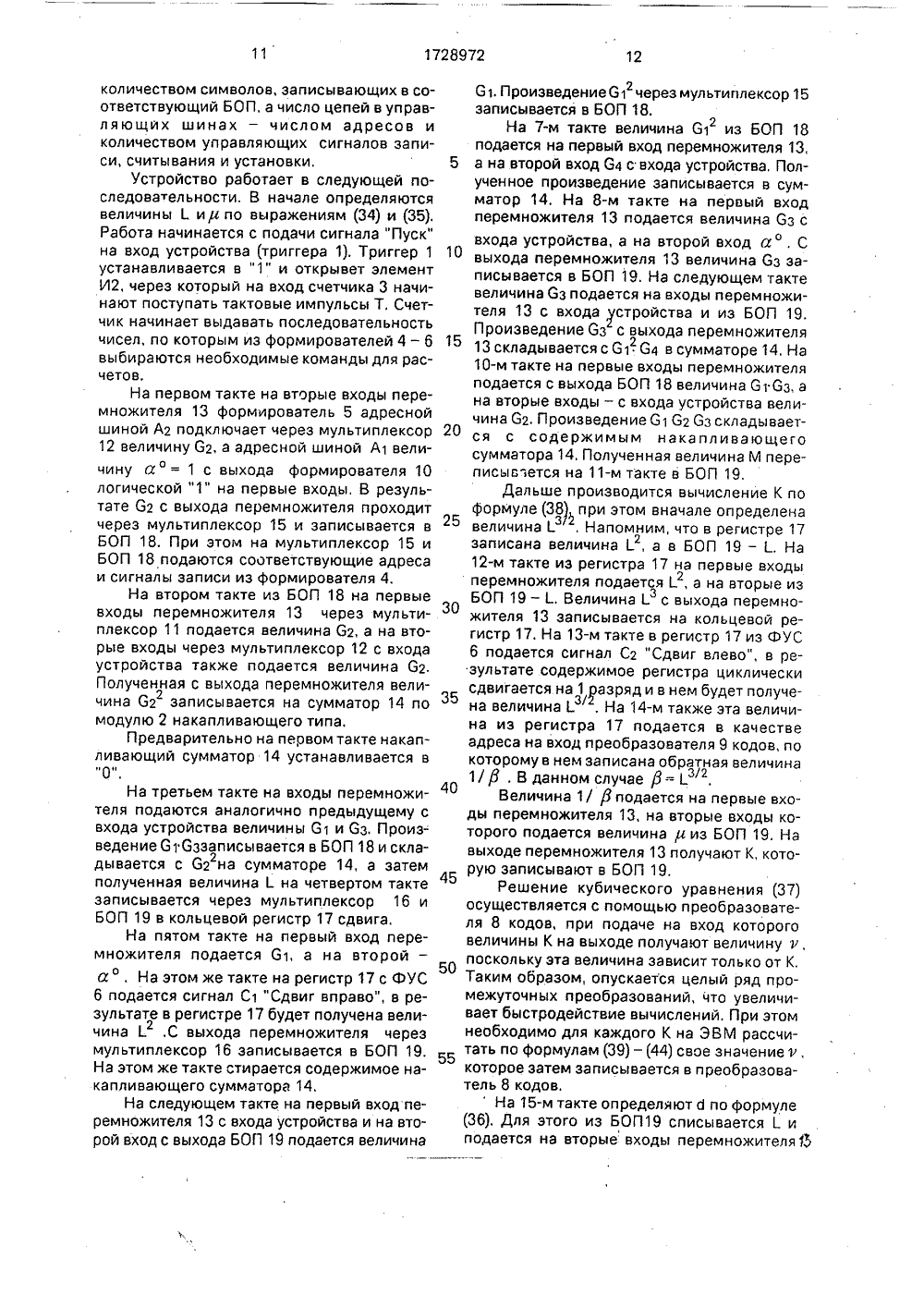

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 172897 П 9 я)5 Н 13/00, 13/02 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(71) Научно-исследовательский институт вычислительной техники, Пензенский политехнический институт и Институт проблемпередачи информации АН СССР(56) Блох З.Л,и Зяблов В, В. Обобщенныекаскадные коды, - М.: Связь, 1976, с,111 -120,Авторское свидетельство СССРМ 1216832, кл, Н 03 М 13/00, 1986,Авторское свидетельство СССРК":. 1603532,к л, Н 01 1 1/16, 1987,(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОКАТОРОВ ОШИБОК(57) Изобретение относится к вычислительной технике. Его использование в устройствах декодирования инфорМации позволяет повысить быстродействие за счет сокращения в 2,5 раза числа тактов работы. Устройство содержит триггер 1, элемент И 2, счетчик 3 импульсов, формирователи 4, 5, 9 адресов, формирователь 6 управляющих сигналов, преобразователи 7 и 8 кодов, формирователь 10 логической единицы, мультиплексоры 11, 12, 15 и 16, перемножитель 13, накапливающий сумматор 14 по модулю два, кольцевой регистр 17, блоки 18 и 19 оперативной памяти 1-2,-3-4-15-17-9-11-13- 14-16-19-7-12-13-15-18-11, 4-19-8-12, 3-5-11, 3-6-17, 14-15-17, 5-12, 10-11, 10-12, 13-16, 4-16, 4-18, 19-12, 1 ил. ЩИзобретение относится к вычислистельной техники и может быть использовано в устройствах декодированияинформации, закодированной кодом РидаСоломона. 5Известно устройство для вычислениялокаторов ошибок, в котором используетсяпроцедура Ченя. Это устройство содержитрегистр, каждый разряд которого содержитячейку памяти, умножитель на обратный 10элемент поля Галуа а и сумматор по модулю два,Определение локаторов осуществляется путем последовательного занесения в регистр всех возможных элементов поля,сдвига содержимого регистра и проверкиего состояния, Если содержимое регистраравно О, то внесенный элемент поля являет.ся локатором ошибки,Недостатком устройства является егонизкое быстродействие, так как на вычисление, например, четырех локаторов требуется 4255 сложений и 4255 умножений.Известно устройство для нахождениядвух локаторов ошибок, содержащее три 25блока постоянной памяти, элемент И, четыре регистра, три коммутатора, дешифратор,перемножитель, группу из щ триггеров, дваблока оперативной памяти, три элементаНЕ и группу из щсумматоров по модулюдва.Недостатком устройства является ограниченная кратность исправляемых ошибок,Наиболее близким по технической сущности к предлагаемому является устройство 5для определения локаторов ошибок, в котором обеспечивается обнаружение четырехлокаторов ошибок Х 1 - Х 4 путем решенияключевого уравнения четвертой степени6(Х) = Х + 61 Х + 62 Х + 6 зХ + 64 (1) 40в котором61= Х 1+ Хг+ Хз+ Ха;62 = Х 1 Х 2 + Х 1 Хз + Х 1 Х 4 + Х 2 Хз + Х 2 Х 4 + ХзХ 4;6 з = Х 1 Х 2 Хз+ Х 1 Х 2 Х 4+ Х 1 ХзХа+ Х 2 ХзХ 4; (2)64 = Х 1 Х 2 хзх 4.45Коэффициенты ключевого уравнения 61-:- : 64 определяются по системе рекуррентных уравнений:Я 5+ Я 46 + Язбг+ Ягбз+ Я 164 = 0;Яб + Я 561 + Я 462 + Язбз + Я 264 = 0; (3)Я 7+ Яв 61+ Я 562.+ Я 46 з+ Язба = 0;Яв + Я 761 + Явбз + Я 569 + Я 46 а = О,где Я 1 - . Яв - синдромы ошибок,При этом процесс расчета и преобразований принятых символов, каждый из которых содержит гп бит в поле Галуа 6 Е(2 ),осуществляется в нормальном базисе, Всеэлементы (символы) поля 6 Ц 2 ) можнопредставить в виде степени примитивного(7) (8) (9) Уравнение (6) можно представить в биквадратной форме элемента а. Если примитивный элементаудовлетворяет дополнительному условию: элементы а, а, а, а , аявляются линейно, независимыми над6 Р(2 ), то они образуют нормальный базис,В таблицах неприводимых многочленовможно выбрать примитивный многочлен соответствующей степени, корни которогоа линейно независимы, где= О, 1, 2, ,2а - 1. Тогда произвольный элементУ.Е 6 Р(2 ) может быть представлен какнекоторая степень а и в и виде разложенияпо нормальному базисущ - 1у ; у аг аа(у)=оПредставление элемента у в виде разложения по нормальному базису удобно привозведении в степень вида 2 и извлечениякорня степени 2. Например, если элемент1у=у а+у 1 аг+уга 4++у,п 1, ащ -1возвести в квадрат, то получим(г 4 сг) к"гсв + ТГт- у " ы + )ффи + "2 Ф +3 лО ъ2(в - 1)так как а=а. Таким образом, возведение в квадрат означает циклическийсдвиг элемента на один разряд вправо. Извлечение квадратного корня осуществляется сдвигом на один разряд влево. Этоупрощает операции возведения в квадрат иизвлечения квадратного корня, что увеличивает быстродействие.Для нахождения локаторов ошибок необходимо преобразовать уравнениеХ +Х 61+Х 62+Хбз+64=0 (4)1 6 з 4подстановкой Х = - + ( - ) формула (4)уприводится к виду2(16)иО =с (17)кубическое уравнение (14) приводится к виду1 +К 11+1=0,Заменой переменной т = К 1 у получаему +у+ - о.1КОбозначим й =, тогда1Куг+у+л =О, (18)Для элементов поля Галуа ОР(2 ), представленных в нормальном базисе, кореньуравнения (18)у (О, п 1, п 1+ пг, п 1+ пг+ пз.п 1+ пг+". пгп-.1), (ю)где Ь - 1-й разряд символа и,Приведем квадратное уравнение (15) к удобному для решения виду с помощью подстановки В = У 1(1+Д ). В результате получимг(1д 2)2Для нахождения локаторов ошибочных комбинаций необходимо найти величиныЬ =К 1(23)гВ результате получимя +8+О =О. (24)Корни уравнения (24) получают по выра- жениям Приведем второе квадратное уравне 5 ние 2 + АЕ+ С = 0 к каноническому виду я +8+7=0, (27)где и гС(28)10Соответствующие корням уравнениясимволы получают из выраженийПутем преобразования символов, соответствующих элементам поля Галуа, по выражениям (4) - (30) находятся локаторыошибок Х 1 - Х 4.Однако данное устройство обладаетнизким быстродействием, так как на определение всех локаторов ошибок тратится107 тактов.Это затрудняет исправление ошибок винформации, принимаемой из высокоскоростных устройств, например оптическихЗУ,Цель изобретения - увеличение быстро 0 действия вычисления локаторов ошибок винформации, защищенной циклическимикодами,Поставленная цель достигается тем, чтов устройство для вычисления локаторовошибок, содержащее триггер, установочный вход которого является входом пускаустройства, выход триггера соединен с первым входом элемента И, второй вход которого является тактовым входом входом40 устройства, выход элемента И подключен ксчетному входу счетчика импульсов, входобнуления которого объединен с входом обнуления триггера и является входом обнуления устройства, выходы счетчика импульсовсоединены со входами первого и второгоформирователей адресов и формирователяуправляющих сигналов, выходы которогоподключены к соответствующим управляющим входам кольцевого регистра сдвига,первые и вторые выходы второго формирователя адресов соединены с адресными входами соответственно первого и второгомультиплексоров, выходы которых подключены к первым и вторым входам перемножителя, выходы которого соединены спервыми информационными входами третьего мультиплексора, выходы первого формирователя адресов подключены кадресным входам третьего мультиплексора(32) и первого и второго блоков оперативной памяти (БОП), формирователь логической единицы, выход которого соединен с первыми информационными входами первого и второго мультиплексоров, вторые и третьи информационные входы которых являются соответственно первыми - четвертыми информационными входами устройства, выходы первого БОП соединены с четвертыми информационными входами первого мультиплексора, выходы второго БОП подключены к четвертыминформационным входам второго мультиплексора и входам первого и второго преобразователей кодов, выходы которых соединены соответственно с пятыми и шестыми информационными входами второго мультплексора, накапливающий сумматор по модулю два, выходы которого подключены к вторым информационным входам третьего мультиплексора, дополнительно включены третий преобразователь кодов и четвертый мультиплексор, первые информационные входы которого объединены с входами накапливающего сумматора по модулю два и подключены к выходам перемножителя, адресные и вторые информационные входы четвертого мультиплексора подключены к выходам соответственно первого формирователя адресов и накапливающего сумматора по модулю два, выходы третьего мультплексора соединены с информационными входами первого БОП и кольцевого регистра сдвига, выходы которого подключены непосредственно и через третий преобразователь кодов соответственно к пятым и шестым информационным входам первого мультиплексора, выходы четвертого мультиплексора соединены с информационными входами второго БОП, выходы которого являются выходами устройства.На чертеже представлена структурная схема устройства для вычисления локаторов ошибок. Устройство содержит триггер 1, элемент И 2, счетчик 3 импульсов, первый 4 и второй 5 формирователи адресов, формирователь 6 управляющих сигналов (ФУС). первый - третий преобразователи 7 - 9 кодов, формирователь 10 логической единицы, первый 11 и второй 12 мультиплексоры, перемножитель 13, накапливающий сумматор 14 по модулю два, третий 15 и четвертый 16 мультиплексоры, кольцевой регистр 17 сдвига, первый 18 и второй 19 блоки оперативной памяти (БОП). Установочный вход триггера 1 является входом пуска, входы сброса триггера 1 исчетчика 3 соединены с цепью "Установка" в "0", первый вход элемента И 2 соединен с 5 10 15 20 25 30 35 40 выходом триггера 1, а на второй вход поданы тактовые импульсы Т, выходы счетчика 3 объединены с адресными входами первого 4 и второго 5 формирователей адресов и ФУС 6, выходы первого формирователя 4 соединены соответственно с адресными входами третьего 15 и четвертого 16 мультиплексоров и управляющими входами первого 18 и второго 19 БОП, первый С 1 и второй Сг выходы ФУС 6 соединены с управляющими входами кольцевого регистра 17 сдвига, выходы формирователя 5 соединены соответственно с адресными входами первого 11 и второго 12 мультиплексоров, выходы которых соединены соответственно с первь,ми и вторыми входами перемножителя 13, выход формирователя 10 соединен с первыми входами первого 11 и второго 12 мультиплексоров, выходы перемножителя 13 поданы на первые информационные входы третьего 15 и четвертого 16 мультиплексоров и на сумматор 14, выходы накапливающего сумматора 14 поданы на вторые информационные входы третьего 15 и четвертого 16 мультиплексоров, выходы третьего мультиплексора 15 объединены с входами кольцевого регистра 17 сдвига и информационными входами первого БОП 18, выходы которого поданы на четвертые входы первого мультиплексора 11, выходы кольцевого регистра 17 сдвига соединены непосредственно и через третий преобразователь 9 кодов соответственно с пятыми и шестыми входами первого мультиплексора 11, выходы четвертого мультиплексора 16 соединены с информационными входами второго БОП 19, выходы. которого являются выходами устройства и объединены с четвертыми входами второго мультиплексора 12 и входами первого 7 и второго 8 преобразователей кодов, выходы последних соединены соответственно с пятыми и шестыми входами второго мультиплексора 12, вторые 11 и третьи 12 входы первого и второго мультиплексоров являются соотвественно первыми и четвертыми информационными входами устройства.Размерность в поля Галуа ба ) равна числу информационных цепей. Управляющие входы содержат адресные цепи, а также цепи записи, считывания и установки., Для нахождения локаторов Х 1 - . Х 4 ошибок необходимо решить уравнение (4), Произведем преобразование указанного уравнения, для чего представим его в биквадратной форме(43)В результате получиму +у+а=О;у 1 = (О, а 1, а 1+ аг,а 1+ аг + ат); (44) 35 уг=1+ у 1. (45) Иэ выражений (32) и (33) можно пол учитьА + 61 А +,и =- О. (46) Заменим А = О 61. В результате получим Ог+ О+т=О, (47) 45ргдет= - ,6(48) мтогда иО 1=(0, 11, т 1+ тг,л 1+ тг++17); (49)О 2 = 1+ О 1, (50) 50Из выражения (32)иВ =61+А; (51)О = 62+ С+,и, (52)Тогдаи64= С(62+ С+ и) (53) 55 рОтсюда С +(62+ и) С+64=0. ЗаменимС=(6 г+,и) ю (54) ГВ результате получим ов +в+р=О, (55)(бб)у 1=(0, Г 1, Ь+ Гг,Л 1+ Ь++ Ф 7); (67)Х 4 = Хз+ В. (68)Устройство работает следующим образом.Программы работы устройства записаны в формирователях 4 и 5 адресов и формирователе 6 управляющих сигналов, Этиформирователи построены на основе блоков постоянной памяти. Они осуществляютуправление мультиплексорами, выдают адреса и сигналы записи и считывания в БОП,На основе блоков постоянной памятипостроены преобразователи 7 - 9 кодов, Сомощью третьего преобразователя 9 беется обратная величина 1/ ф, где Р - элеент поля Галуа Щ 2), а - размерностьоля. Первый преобразователь кодов 7 исользуется для ускорения решения уравнеия второй степени, а второйреобразователь 8 - уравнения третьей стеени.При этом на входной мультиплексор 11одаются величины 61 и 6 З, а на мультилексор 12 - 62 и 64. Формирователи 4 - баботают по жесткому алгоритму,Устройство работает с элементами поляалуа 6 Е(2 ), поэтому каждая информацинная шина имеет а цепей (разрядов). Чисо цепей в адресных шинах определяется01. Произведение 61 через мультиплексор 15 записывается в БОП 18.На 7-м такте величина 61 из БОП 18подается на первый вход перемножителя 13, 5 а на второй вход 04 с входа устройства, Полученное произведение записывается в сумматор 14, На 8-м такте на первый вход перемножителя 13 подается величина 0 з с входа устройства, а на второй вход а . С выхода перемножителя 13 величина 6 з записывается в БОП 19. На следующем такте величина 0 з подается на входы перемножителя 13 с входа устройства и из БОП 19.Произведение 0 з с выхода перемножителя 13 складывается с 01 04 в сумматоре 14, На210-м такте на первые входы перемножителя подается с выхода БОП 18 величина 016 з, а на вторые входы - с входа устройства величина 02. Произведение 6102 6 з складывается с содержимым накапливающего сумматора 14, Полученная величина М переписыв-ется на 11-м такте в БОП 19,Дальше производится вычисление К поформуле (38 при этом вначале определена величина , Напомним, что в регистре 17З 2записана величина , а в БОП 19 - , На 12-м такте из регистра 17 на первые входы перемножителя подается , а на вторые из2БОП 19 - 1. Величина 1 с выхода перемнозжителя 13 записывается на кольцевой регистр 17. На 13-м такте в регистр 17 из ФУС 6 ПОдаЕтСя СИГНаЛ С 2 нСдВИГ ВЛЕВО", В рЕ- зультате содержимое регистра циклически сдвигается на 1 разряд и в нем будет получена величина. На 14-м также эта величи 3/на из регистра 17 подается в качестве адреса на вход преобразователя 9 кодов, по которому в нем записана обратная величина1/ ф, В данном случае Р" =- Р 2.Величина 1/,В подается на первые входы перемножителя 13, на вторые входы которого подается величина,и из БОП 19, На выходе перемножителя 13 получают К, которую записывают в БОП 19.Решение кубического уравнения (37)осуществляется с помощью преобразователя 8 кодов, при подаче на вход которого величины К на выходе получают величину ю, поскольку эта величина зависит только от К, Таким образом, опускается целый ряд промежуточных преобразований, что увеличивает быстродействие вычислений. При этом необходимо для каждого К на ЭВМ рассчитать по формулам (39) - (44) свое значение ю, которое затем записывается в преобразовавходы перемножителя 13 через мультиплексор 11 подается величина 02, а на вторые входы через мультиплексор 12 с входаустройства также подается величина 62.Полученная с выхода перемножителя величина 62 записывается на сумматор 14 по 35модулю 2 накапливающего типа.Предварительно на первом такте накапливающий сумматор 14 устанавливается вн 0",На третьем такте на входы перемножителя подаются аналогично предыдущему свхода устройства величины 61 и 0 з. Произведение 610 ззаписывается в БОп 18 и складывается с 62 на сумматоре 14, а затемполученная величинана четвертом тактезаписывается через мультиплексор 16 иБОП 19 в кольцевой.регистр 17 сдвига,На пятом такте на первый вход перемножителя подается 61, а на второй -50а . На этом же такте на регистр 17 с ФУС6 подается сигнал С 1 "Сдвиг вправо", в результате в регистре 17 будет получена величина,С выхода перемножителя черезмультиплексор 16 записывается в БОП 19.На этом же такте стирается содержимое накапливающего сумматора 14.На следующем такте на первый вход перемножителя 13 с входа устройства и на второй вход с выхода БОП 19 подается величина количеством символов, записывающих в соответствующий БОП, а число цепей в управляющих шинах - числом адресов и количеством управляющих сигналов записи, считывания и установки.Устройство работает в следующей последовательности. В начале определяются величиныи,и по выражениям (34) и (35). Работа начинается с подачи сигнала "Пуск" на вход устройства (триггера 1). Триггер 1 устанавливается в н 1" и открывет элемент И 2, через который на вход счетчика 3 начинают поступать тактовые импульсы Т, Счетчик начинает выдавать последовательность чисел, по которым из формирователей 4 - 6 выбираются необходимые команды для расчетов,На первом такте на вторые входы пере- множителя 13 формирователь 5 адресной шиной А 2 подключает через мультиплексор 12 величину 62, а адресной шиной А 1 величину а = 1 с выхода формирователя 10 логической м 1 н на первые входы. В результате 02 с выхода перемножителя проходит через мультиплексор 15 и записывается в БОП 18. При этом на мультиплексор 15 и БОП 18 подаются соответствующие адреса и сигналы записи из формирователя 4.На втором такте из БОП 18 на первые тель 8 кодов,На 15-м такте определяют б по формуле(36). Для этого из БОП 19 списывается . иподается на вторые входы перемножителя ба на первые входы подается а . Полученный результат аозаписывается в регистр 17 сдвига. На 16-м такте из ФУС 6 наэтот регистр подается сигнал Сг "Сдвигвлево", в результате чего в нем получаютвеличину 4;.На 17-м такте на первые входы перемножителя 13 подается с регистра 17 величина /Г. При этом из БОП 19 списываетсяК и в качестве адреса подается на вход преобразователя 8 кодов, на выходе которогополучают величину м, которая подается навторые входы перемножителя 13.Полученную на выходе величину,и записывают в накапливающий сумматор 14 ив БОП 19. После этого приступают к вычислению р по формуле (56),,цля этого вначале вычисляют знаменатель. На 18-м такте на первые входы перемножителя 13 подается величина а, а навторые - 6 г с входа устройства, Величина 0 гс выхода перемножителя 13 подается насумматор 14, где складывается с,и. Полученная сумма на 19-м такте параллельно 25записывается на кольцевой регистр 17 сдвига и в БОП 18.На 20-м такте регистр 17 из ФУС 6подается сигнал С 1 "Сдвиг вправо", в результате в нем будет получена величина (6 г 30+,и ) . На 21-м такте эта величина в качествеадреса подается на вход преобразователя 9кодов, по которому в нем записана обратнаявеличина 1/В . Здесь 3=(0 г+,и) . Величина 1/Р подается на первые входы перемножителя 13, а на вторые входы подается 64 свхода устройства. На выходе перемножителя 13 будет получена величина р, котораязаписывается в БОП 19,Дальше находится корень в квадратного уравнения (55), Поскольку он зависиттолько от р, то для нахождения его используется преобразователь 7 кодов. В нем поадресу, задаваемому величиной р, записанкорень в, Поэтому на 22-м такте величина 45списывается из БОП 19 и подается на входпреобразователя 7. Полученная на его выходе величина через мультиплексор 12 подается на вторые входы перемножителя 13, напервые входы которого выдается величина0 г +,и из БОП 18.В результате в соответствии с выражением (54) на выходе перемножителя 13 получают величину С, которую записывают вБОП 19, Далее аналогично предыдущему 55решают квадратное уравнение (47). Для этого свободный член т находят по выражению(48). Отметим, что знаменатель 01 был рассчитан ранее и записан в БОП 18. Для получения 1/01 необходимо 01 переписать в кольцевой регистр 17 сдвига. На 23-м такте величина 61 подается на первые входы перемножителя 13, на вторые входы которого подается а О, .С выхода перемножителя 13 величина 61 записывается в регистр 17. На 24-м такгте величина 61 г подается на вход преобразователя 9 кодов, с выхода которого величина 1/61 подается на первые входы перемножителя 13, на вторые входы которого подается величинаи из БОП 19. Величина с с выхода перемножителя 13 записывается в БОП 19.Затем определяют величину А по выражению (46). Для этого на 25-м такте на первые входы перемножителя 13 подается величина 01 с входа устройства, а на вторые входы - величина О, которая получается на выходе преобразователя 7 кодов при подаче на его вход величины с из БОП 19.Полученную на выходе перемножителя 13 величину А записывают в накапливающий сумматор 14, кольцевой регистр 17 и в БОП 18, После этого определяют свободный член е квадратного уравнения (60). На 26-м такте на кольцевой регистр 17 подается сигнал С 1 "Сдвиг вправо", в результате в нем будет получена величина А, На следующем такте эта величина подается на вход преобразователя 9 кодов, с выхода которого величина 1/А подается на первые входыгперемножителя 13, а на вторые входы поступает величина С из БОП 19. Результат умножения езаписывается в БОП 19.На 28-м такте определяется первый локатор ошибок Х 1 по выражению (58), Для этого на первые входы перемножителя 13 подается величина А из БОП 18, Величина я списывается из БОП 19 и подается на вход преобразователя 7 кодов, с выхода которого полученную величинурподают на вторые входы перемножителя 13.Таким образом, первый локатор ошибок, полученный на выходе перемножителя 13, записывают в БОП 19. Дальше определяют второй локатор Хг ошибок по (62), Отметим, что величина А уже записана в блоке 18. Поэтому на 29-м тракте на первые входы перемножителя 13 подается величина а , а на вторые входы локатор Х 1 из БОП 19, С выхода перемножителя 13 локатор Х 1 подается на сумматор 14, где складывается с А, В результате в блоке 14 будет получен локатор ошибок Хг, который на 30-м такте списывается в БОП 19,Затем необходимо определить величину В по выражению(51). Для этого на 31-м такте на первые входы перемножителя 13подается величина 61 с входа устройства, а на вторые входы - а , С выхода перемножителя 13 01 записывают в накапливающий сумматор 14. На 32-м такте на первые входы перемножителя 13 подается величина А из БОП 18, а на вторые входы - а. Величина А с выхода перемножителя 13 подается в накапливающий сумматор 14, где складывается с 61. В результате будет получена величина В, которая на 33-м такте списывается в БОП 18 и кольцевой регистр 17,Далее определяется величина О по формуле (52), На 34-м такте на первые входы перемножителя 13 подается а, а на вторые входы - величина 8 с входа устройства,5 10 15 82 с выхода перемножителя 13 записывается в накапливающий сумматор 14. На 20следующем такте на первые входы перемножителя 13 подается а, а на вторые - величина С из БОП 19,С выхода перемножителя 13 величина Сподается в накапливающий сумматор 14,где складывается с 62. Аналогично на 36-мтакте в накапливающем сумматоре 14 происходит сложение 62+ С с величиной,и,которую списывают из БОП 19, В результатебудет получена величина О, которая на 37-мтакте записывается в БОП 19. Затем определяется свободный член 1 квадратногоуравнения (65) по формуле 66). Для этого на38-м такте из ФУС 6 на кольцевой регистр17 подается сигнал С 1 "Сдвиг вправо", врезультате в нем будет получена величинаВ . На 39-м такте величина В подается навход преобразователя 9 кодов, с выхода которого величина 1/В подается на первыевходы перемножителя 13, на вторые входы 40которого подается величина О из БОП 19,Полученная величина 1 записывается в БОП19.На 40-м такте на первые входы перемножителя 13 подается величина В из БОП18, При этом величина 1 списывается из БОП19 и подается на вход преобразователя 7кодов, с выхода которого величину у подаютна вторые входы перемножителя 13.В результате на выходе перемножителя13 в соответствии с выражением 64) получают третий локатор ошибок Хз, который параллельно записывают в накапливающийсумматор 14 и в БОП 19,На 41-м такте на первые входы перемножителя 13 подается величина В из БОП18, а на вторые входы - а . С выхода перемножителя 13 величина В подается в накапливающий сумматор 14, где складывается с Хз, В результате получают четвертый локатор Х 4 ошибок, который на 42-м такте записывается в БОП 19, На этом заканчивается определение ошибок Х 1 - . Х 4.Таким образом, в предлагаемом устройстве для нахождения четырех локаторов ошибок требуется 107 тактов, а в предлагаемом - только 42, следовательно, предлагаемое устройство обеспечивает существенно большее быстродействие.Формула изобретения Устройство для вычисления локаторов ошибок, содержащее триггер, установочный вход которого является входом пуска устройства, выход триггера соединен с первым входом элемента И, второй вход которого является тактовым входом устройства, выход элемента И подключен к счетному входу счетчика импульсов, вход обнуления которого объединен с входом обнуления триггера и является входом обнуления устройства, выходы счетчика импульсов соединены с входампервого и второго формирователей адресов и формирователя управляющих сигналов, выходы которого подключены к соответствующим управляющим входам кольцевого регистра сдвига, первые и вторые выходы второго формирователя адресов соединены с адресными входами соответственно первого и второго мультиплексоров, выходы которых подключены к первым и вторым входам перемножителя, выходы которого соединены с первыми информационными входами третьего мультиплексора, выходы первого формирователя адресов подключены к адресным входам третьего мультиплексора и первого и второго блоков оперативной памяти, формирователь логической единицы, выход которого соединен с первыми информационными входами первого и второго мультиплексоров, вторые и третьи информационные входы которых являются соответственно первыми - четвертыми информационными входами устройства, выходы первого блока оперативной памяти соединены с четвертыми информационными входами первого мультиплексора, выходы второго блока оперативной памяти подключены к четвертым информационным входам второго мультиплексора и входам первого и второго преобразователей кодов, выходы которых соединены соответственно с пятыми и шестыми информационными входами второго мультиплексора, накапливающий сумматор по модулю два, выходы которого подключены к вторым информационным входам третьего мультипликатора, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в устройство введены тре.40 45 50 Составитель О.РевинскийРедактор Н.Лазоренко Техред М.Моргентал Корректор С. Шевкун Заказ 1414 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб 4/5 Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 тий преобразователь кодов и четвертый мультиплексор, первые информационные входы которого объединены с входами накапливающего сумматора по модулю два и подключены к выходам перемножителя, адресные и вторые информационные входы четвертого мультиплексора подключены к выходам соответственно первого формирователя адресов и накапливающего сумматора по модулю два, выходы третьего мультипликатора соединены с информационными входами первого блока оперативной памяти и кольцевого регистра сдвига, выходы которого подключены непосредственно и через третий преобразователь ко дов соответственно к пятым и шестыминформационным входам первого мультиплексора выходы четвертого мультиплексора соединены с информационными входами второго блока оперативной памя ти, выходы которого являются входами устройства,

СмотретьЗаявка

4809873, 04.04.1990

НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ, ПЕНЗЕНСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ, ИНСТИТУТ ПРОБЛЕМ ПЕРЕДАЧИ ИНФОРМАЦИИ АН СССР

САВЕЛЬЕВ БОРИС АЛЕКСАНДРОВИЧ, ЗИНОВЬЕВ ВИКТОР АЛЕКСАНДРОВИЧ, ТОЛОВ АНДРЕЙ ВАДИМОВИЧ, ДУДКИН АЛЕКСАНДР МИХАЙЛОВИЧ, МИГУНОВ БОРИС АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: H03M 13/00, H03M 13/02

Метки: вычисления, локаторов, ошибок

Опубликовано: 23.04.1992

Код ссылки

<a href="https://patents.su/9-1728972-ustrojjstvo-dlya-vychisleniya-lokatorov-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления локаторов ошибок</a>

Предыдущий патент: Преобразователь форматов данных

Следующий патент: Многоканальное устройство для передачи и приема сигналов тока по линии связи

Случайный патент: 403014