Кодер балансного кода 3b2q

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

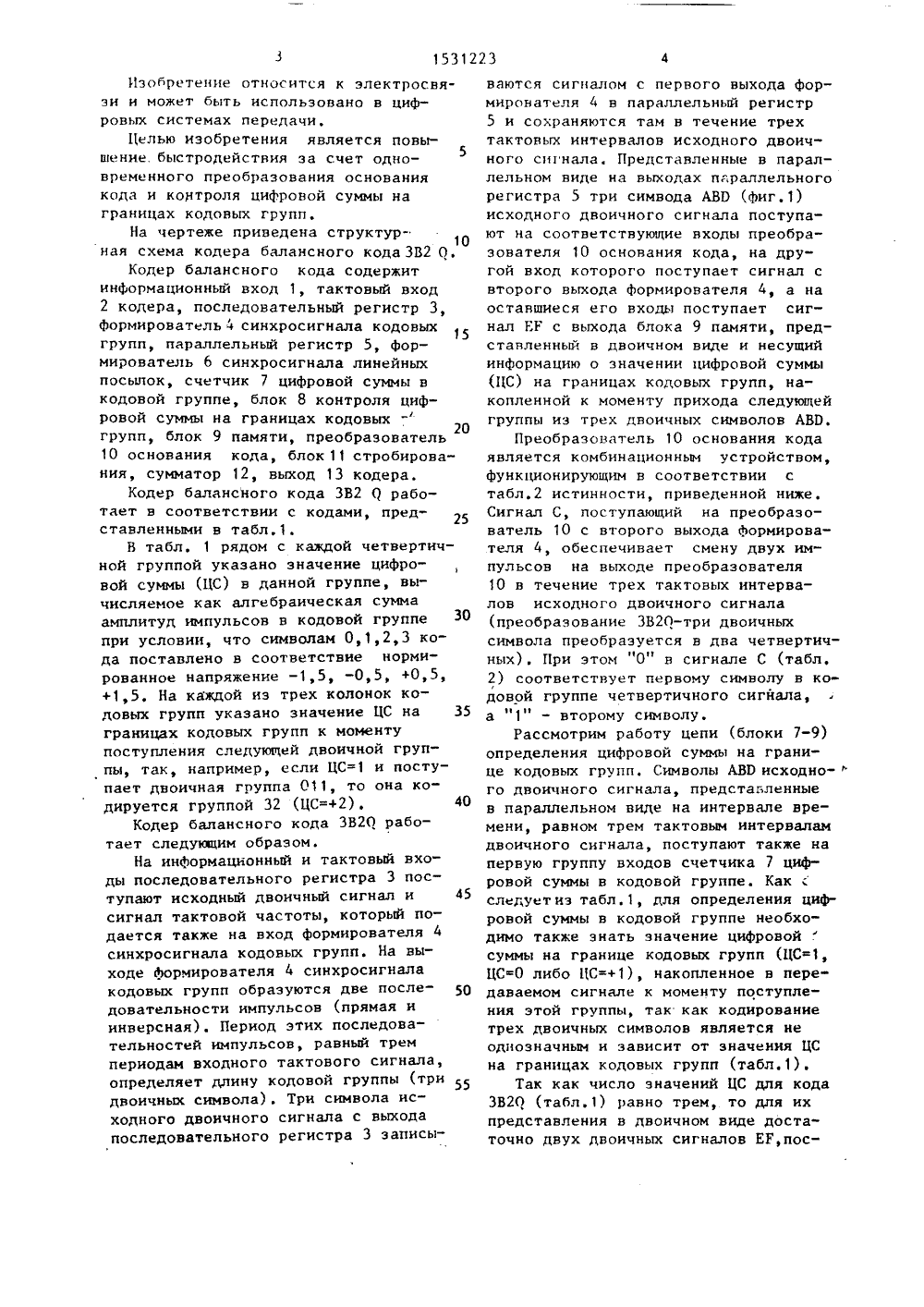

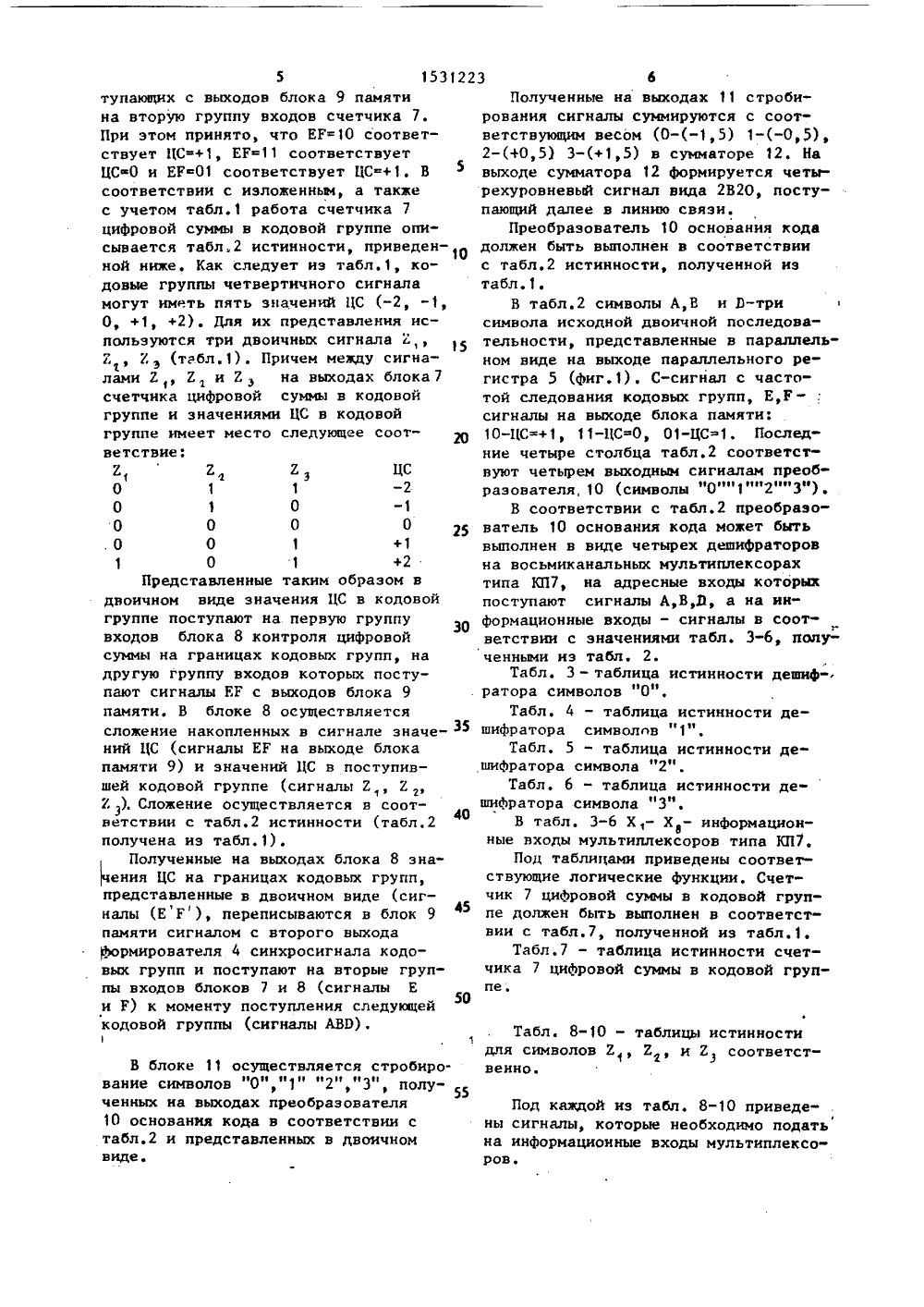

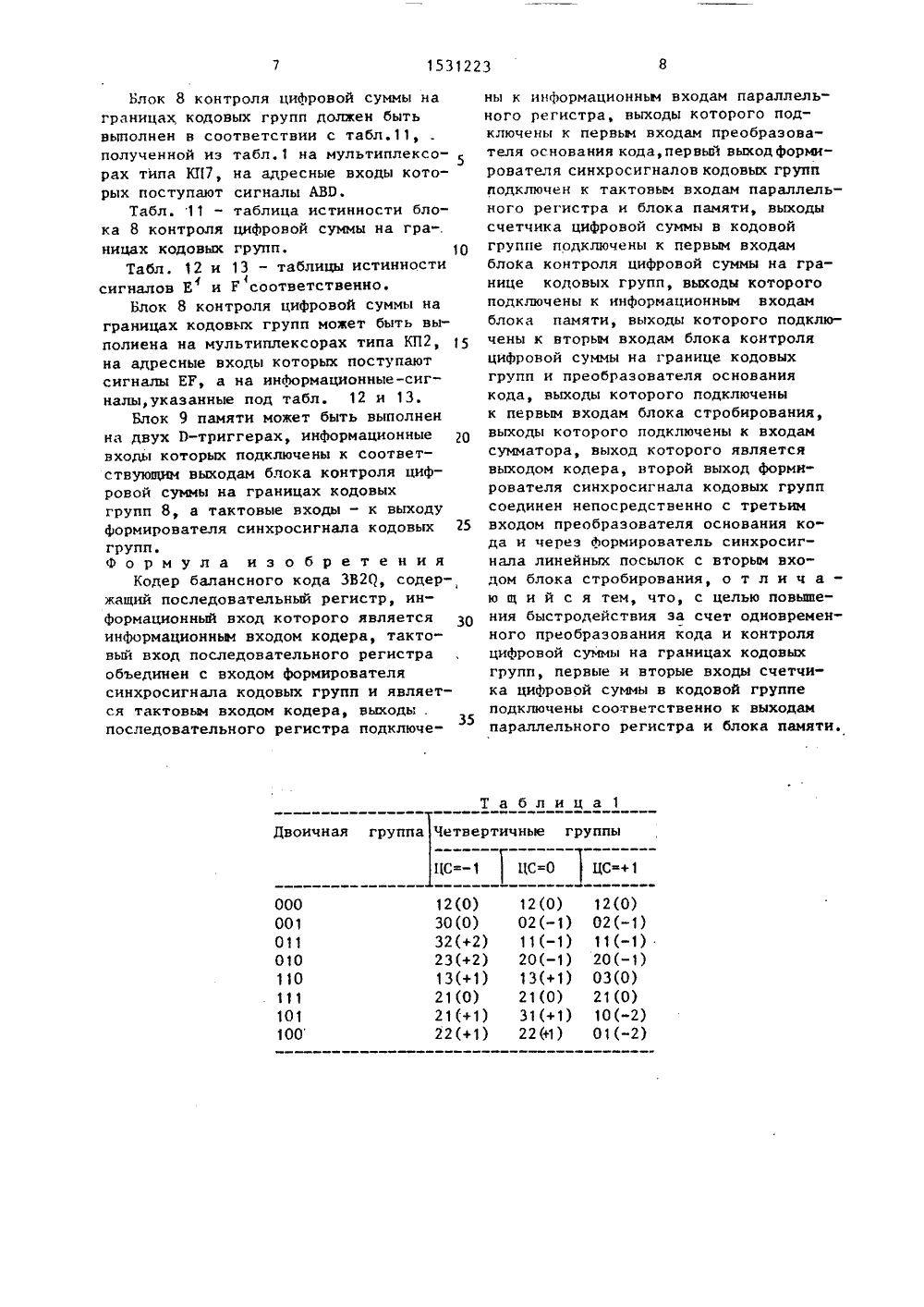

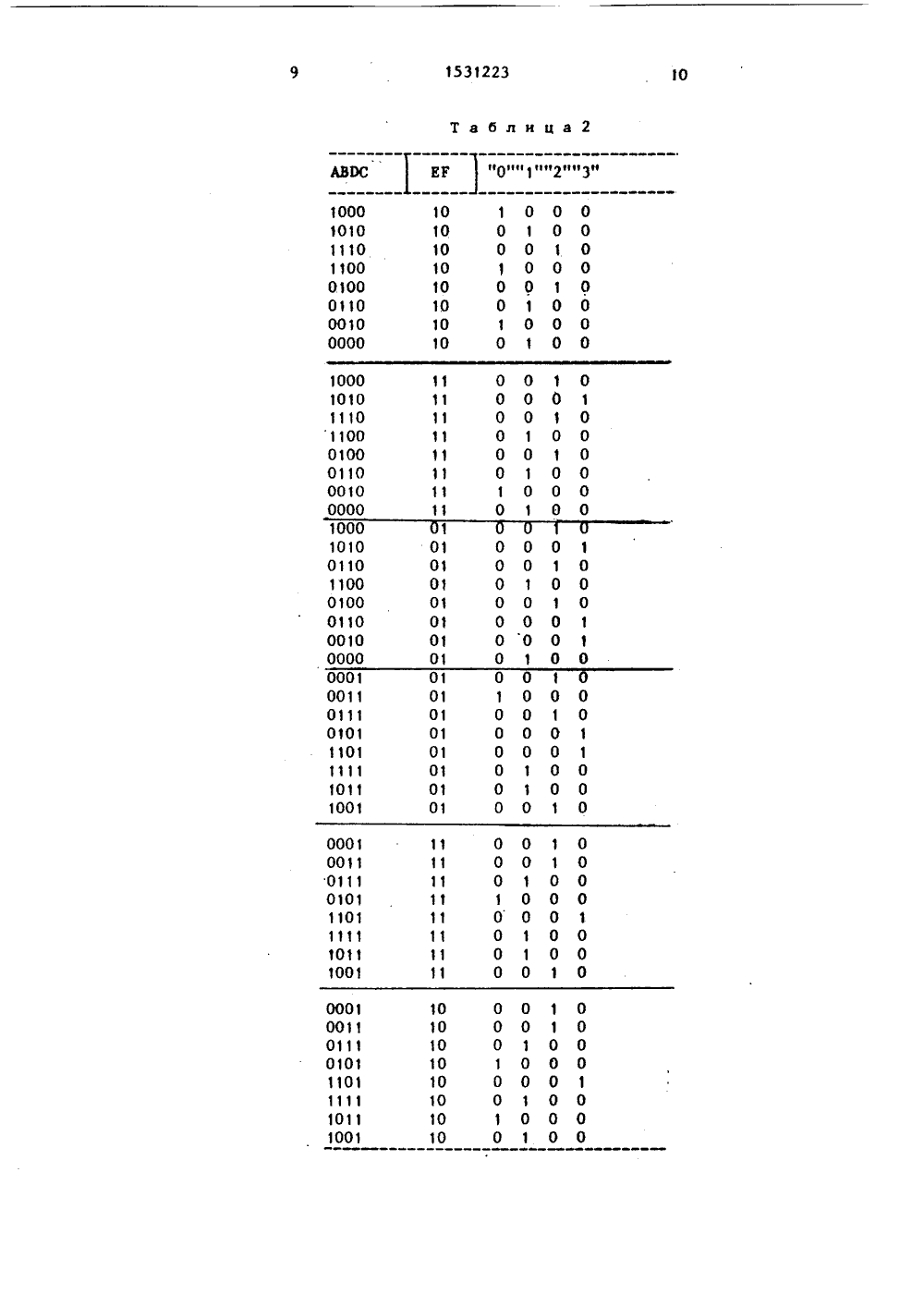

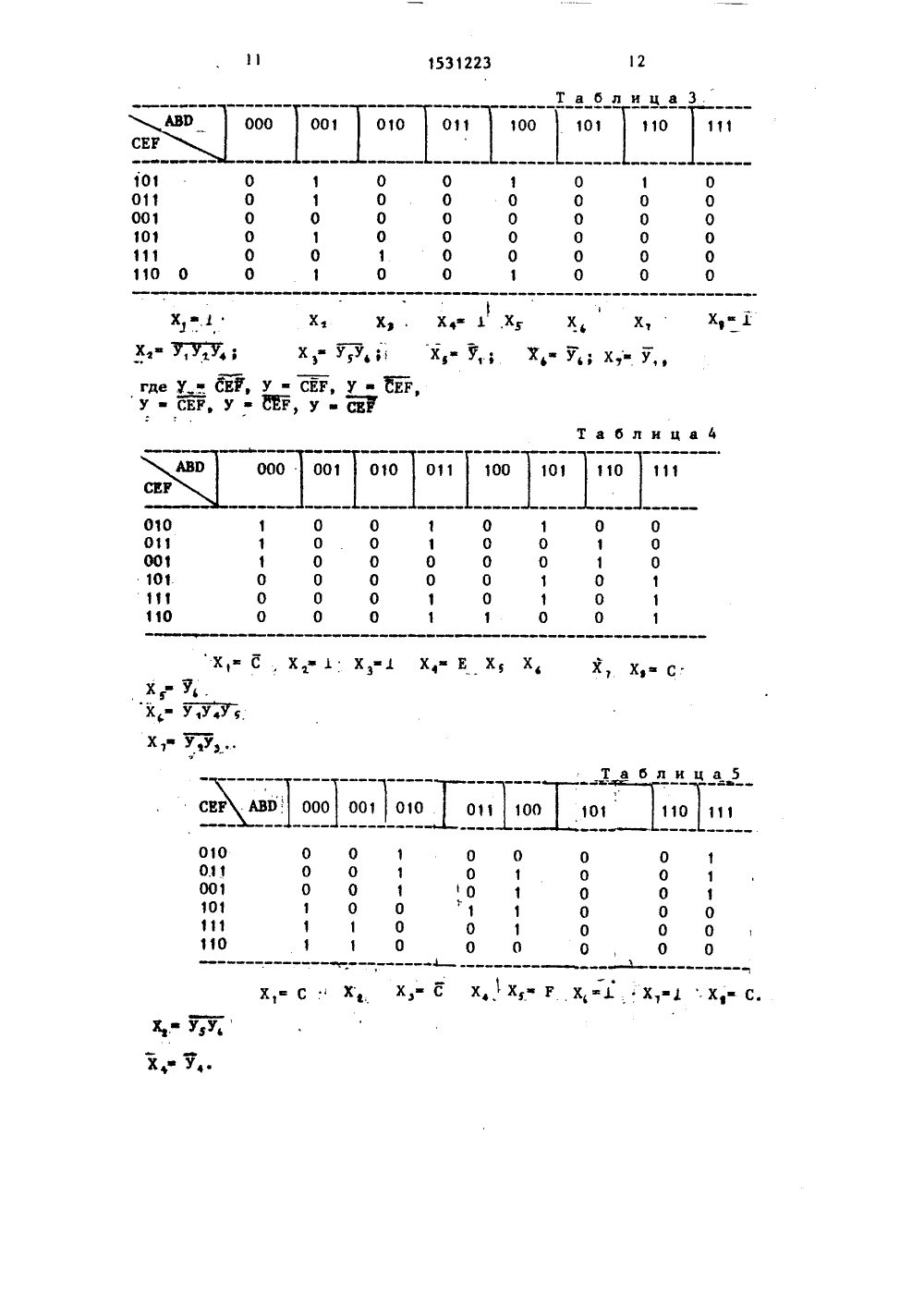

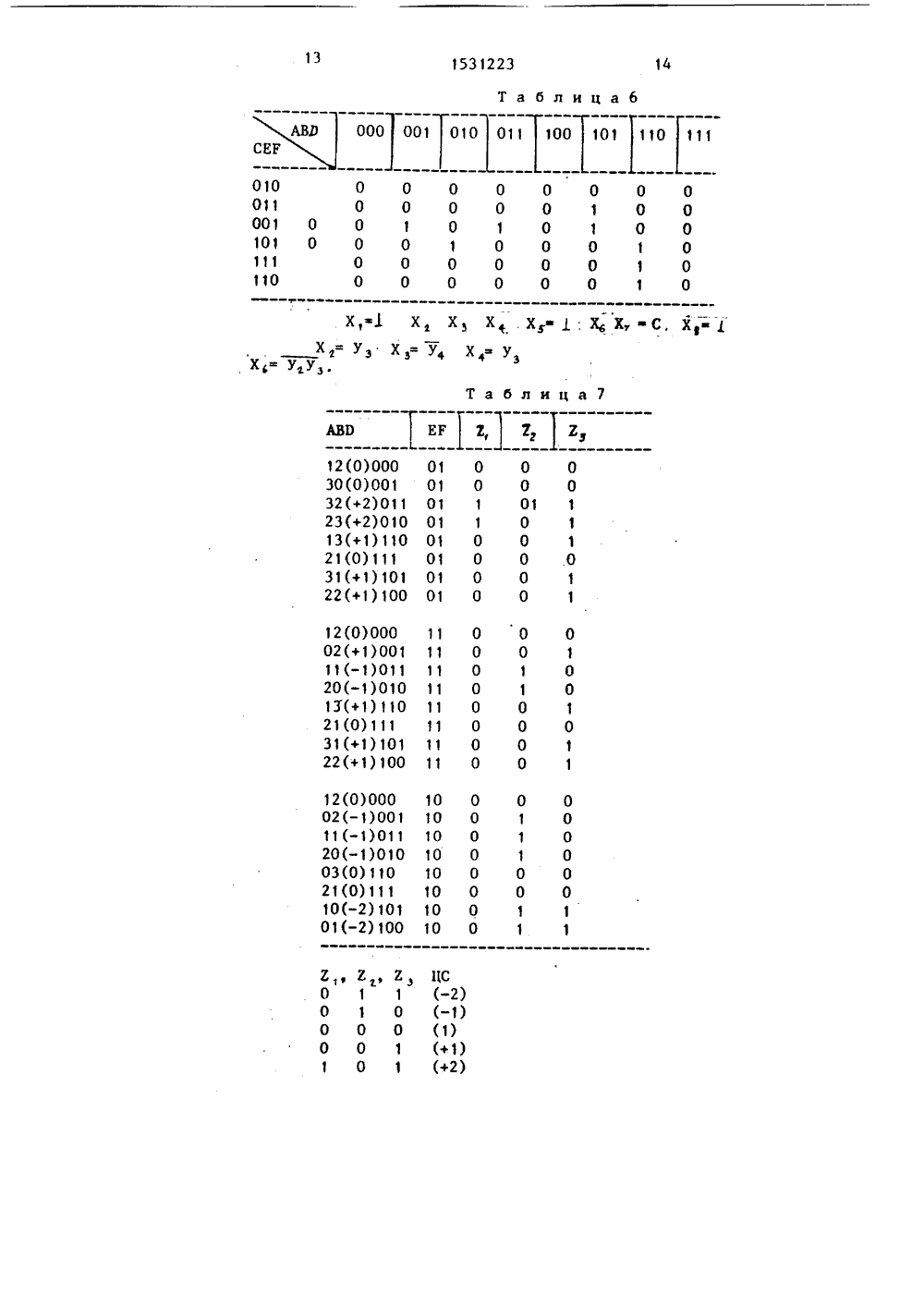

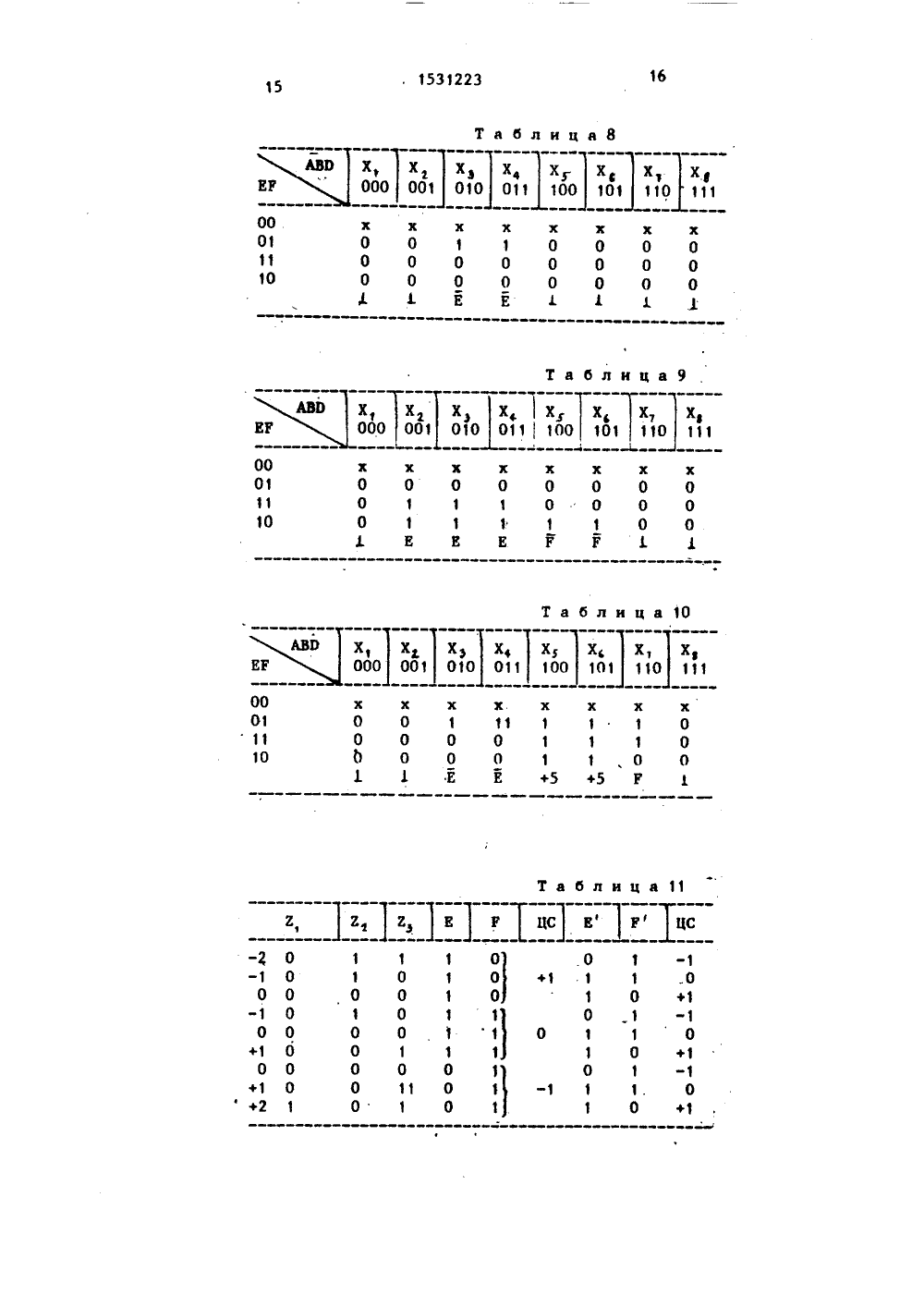

.80153 1)4 Н 03 И 5/18 ИСАНИЕ ИЗОБРЕТЕН ЕЛЬСТВ АВТОРСКОМУ С лектров цифации. строГОСУДАРСТВЕННЫЙ КОМИТЕТйо ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГННТ СССР(56) Авторское свидетельство СССРУ 688082, кл. Н 04 1. 5/00, 1976,Авторское свидетельство СССРВ 1244803, кл. Н 04 1. 5/00, 1984.(54) КОДЕР БАЛАНСНОГО КОДА ЗВ 2(57) Изобретение относится к эсвязи и может найти применениеровых системах передачи информЦель изобретения - повышение бьдействия эа счет одновременного преразования основания кода и контроля цифровой суммы на границах кодовых групп. При этом определение цифровой суммы в группе осуществляется с учетом цифровой суммы на границах кодовых групп. Кодер балансного кода ЗВ 2 О содержит информационный вход 1 тактовый вход 2, последовательный регистр 3, формирователь 4 синхросиг нала кодовых групп, параллельный регистр 5, формирователь 6 синхросиг нала линейных посылок, счетчик 7 цифровой суммы в кодовой группе, блок 8 контроля цифровой суммы на границах кодовых групп, блок 9 памяти, преобразователь 10 основания кода, блок 11 стробирования, сумматор 12, выход 13. 1 ил., 13 табл,Изобретение относится к электросвяэи и может быть использовано в цифровых системах передачи,Целью изобретения является повышение. быстродействия за счет одно 5временного преобразования основаниякода и коНтроля цифровой суммы награницах кодовых групп,На чертеже приведена структурная схема кодера балансного кода ЗВ 2 О.Кодер балансного кода содержитинформационный вход 1, тактовый вход2 кодера, последовательный регистр 3,формирователь 4 синхросигнала кодовыхгрупп, параллельный регистр 5, формирователь 6 синхросигнала линейныхпосылок, счетчик 7 цифровой суммы вкодовой группе, блок 8 контроля цифровой суммы на границах кодовых -групп, блок 9 памяти, преобразователь10 основания кода, блок 11 стробирования, сумматор 12, выход 13 кодера.Кодер балансного кода ЗВ 2работает в соответствии с кодами, представленными в табл,1.В табл. 1 рядом с каждой четвертичной группой указано значение цифровой суммы (ЦС) в данной группе, вычисляемое как алгебраическая суммаамплитуд импульсов в кодовой группе ЗОпри условии, что символам 0,1,2,3 кода поставлено в соответствие нормированное напряжение -1,5, -0,5, +0,5,+1,5, На каждой из трех колонок кодовых групп указано значение ЦС на 35границах кодовых групп к моментупоступления следующей двоичной группы, так, например, если ЦС=1 и поступает двоичная группа 011, то она кодируется группой 32 (ЦС=+2), 40Кодер балансного кода ЗВ 20 работает следующим образом.На информационный и тактовый вхо"ды последовательного регистра 3 поступают исходный двоичный сигнал и 45сигнал тактовой частоты, который подается также на вход формирователя 4синхросигнала кодовых групп. На выходе формирователя 4 синхросигналакодовых групп образуются две после Одовательности импульсов (прямая иинверсная). Период этих последовательностей импульсов, равный тремпериодам входного тактового сигнала,определяет длину кодовой группы (три 55двоичных символа). Три символа исходного двоичного сигнала с выходапоследовательного регистра 3 записываются сигналом с первого выхода формирователя 4 в параллельный регистр 5 и сохраняются там в течение трех тактовых интервалов исходного двоичного сигнала. Представленные в параллельном виде на выходах и;раллельного регистра 5 три симвода АВ 0 (фиг.1) исходного двоичного сигнала поступают на соответствующие входы преобразователя 10 основания кода, на другой вход которого поступает сигнал с второго выхода формирователя 4, а на оставшиеся его входы поступает сигнал ЕГ с выхода блока 9 памяти, представленный в двоичном виде и несущий информацию о значении цифровой суммы (ЦС) на границах кодовых групп, накопленной к моменту прихода следующей группы из трех двоичных символов АВР.Преобразователь 1 О основания кода является комбинационным устройством, функционирующим в соответствии с табл,2 истинности, приведенной нижеСигнал С, поступающий на преобразователь 10 с второго выхода формирователя 4, обеспечивает смену двух импульсов на выходе преобразователя 10 в течение трех тактовых интервалов исходного двоичного сигнала (преобразование ЗВ 20-три двоичных символа преобразуется в два четвертичных). При этом "0" в сигнале С (табл.2) соответствует первому символу в кодовой группе четвертичного сигнала, а "1" - второму символу.Рассмотрим работу цепи (блоки 7-9) определения цифровой суммь на границе кодовых групп. Символы АВО исходно- " го двоичного сигнала, представленные в параллельном виде на интервале времени, равном трем тактовым интервалам двоичного сигнала, поступают также на первую группу входов счетчика 7 цифровой суммы в кодовой группе. Как следует из табл.1, для определения цифровой суммы в кодовой группе необходимо также знать значение цифровой суммы на границе кодовых групп (ЦС 1, ЦС 0 либо ЦС=+1), накопленное в передаваемом сигнале к моменту поступления этой группы, так как кодирование трех двоичных символов является не однозначным и зависит от значения ЦС на границах кодовых групп (табл.1).Так как число значений ЦС для кода ЗВ 20 (табл.1) равно трем, то для их представления в двоичном виде доста" точно двух двоичных сигналов ЕГ,пос1531223 5тупающих с выходов блока 9 паияти на вторую группу входов счетчика 7. При этом принято, что ЕГ 1 О соответствует ЦС=+1, ЕГ 11 соответствует ЦСО и ЕГ 01 соответствует ЦС"+ 1. В соответствии с изложенньм, а также с учетом табл.1 работа счетчика 7 цифровой суммы в кодовой группе описывается табл.2 истинности, приведенной ниже. Как следует из табл.1, кодовые группы четвертичного сигнала могут иметь пять значений ЦС (-2, -1, О, +1, +2). Для их представления используются три двоичных сигнала 2 2 , Е з (табл.1). Причем между сигналами 2 Е и Е на выходах блока 7 счетчика цифровой суммы в кодовой группе и значениями ЦС в кодовой группе имеет место следующее соответствие: ЕЕ 2 ЦС 0 1 1 -2 0 1 0 -1 0 0 0 о .0 0 1 +1 1 0 1 +2Представленные таким образом в двоичном виде значения ЦС в кодовой группе поступают на первую группу входов блока 8 контроля цифровой суммы на границах кодовых групп, на другую группу входов которых поступают сигналы ЕГ с выходов блока 9 памяти. В блоке 8 осуществляется сложение накопленных в сигнале значе ний ЦС (сигналы ЕГ на выходе блока памяти 9) и значений ЦС в поступившей кодовой группе (сигналы 2 Е, 2 ). Сложение осуществляется в соответствии с табл,2 истинности (табл,240 получена из табл.1).Полученные на выходах блока 8 знаения ЦС на границах кодовых групп, представленные в двоичном виде (сигналы (Е Г), переписываются в блок 9 памяти сигналом с второго выхода формирователя 4 синхросигнала кодовых групп и поступают на вторые группы входов блоков 7 и 8 (сигналы Е и Г) к моменту поступления следующей50 кодовой группы (сигналы АВЭ).1 В блоке 11 осуществляется стробироченных на выходах преобразователя 10 основания кода в соответствии с табл.2 и представленных в двоичном виде. 6Полученные на выходах 11 стробирования сигналы суииируются с соответствующим весом (0-(-1,5) 1-(-0,5), 2-(+0,5) 3-(+1,5) в сумматоре 12. На выходе сумматора 12 формируется четырехуровневый сигнал вида 2 В 20, поступающий далее в линию связи.Преобразователь 10 основания кода должен быть выполнен в соответствии с табл.2 истинности, полученной из табл,1.В табл.2 символы А,В и В-три символа исходной двоичной последовательности, представленные в параллельном виде на выходе параллельного регистра 5 (фиг.1). С-сигнал с частотой следования кодовых групп, Е,Г- сигналы на выходе блока памяти: 10-ЦС=+1, 11-ЦС О, 01-ЦС 1. Последние четыре столбца табл.2 соответствуют четырем выходным сигналаи преобразователя, 1 О (символы "0"123").В соответствии с табл.2 преобразователь 10 основания кода может быть выполнен в виде четырех дешифраторов на восьмиканальных мультиплексорах типа КП 7, на адресные входы которых поступают сигналы А,В,Л, а на информационные входы - сигналы в соответствии с значениями табл. 3-6, попученньми из табл. 2.Табл, 3 - таблица истинности дешифратора символов "0".Табл. 4 - таблица истинности дешифратора символов "1".Табл, 5 - таблица истинности дешифратора символа "2"Табл. 6 - таблица истинности дешифратора символа "3".В табл. 3-6 Х, - Х- информацнонные входы мультиплексоров типа КП 7.Под таблицами приведены соответствующие логические функции, Счетчик 7 цифровой суммы в кодовой группе должен быть выполнен в соответствии с табл.7, полученной из табл.1,Табл.7 - таблица истинности счетчика 7 цифровой суммы в кодовой группе. Табл. 8-10 - таблицы истинности для символов Е 1, Е , и Е соответственно. Под каждой из табл. 8-10 приведены сигналы, которые необходимо подать на информационные входы мультиплексоров.1531223 Таблица 1 Двоичная группа Четвертичные группы ЦС=О ЦС=+1 12(0) 30 (0) 32(+2) 23(+2) 13 (+1) 21(0) 21 (+1) 22 (+1) 12 (0)02 (-1)11(-1)20 (-1)13 (+1)21(0)31 (+1)22 (+1 ) 12(0)02 (-1)11 (-1)20 (-1)03(0)21 (0)10 (-2)01(-2)г 000 001 011 010 110 111 101 100 Блок 8 контроля цифровой суммы на границах кодовых групп должен быть выполнен в соответствии с табл.11, полученной из табл,1 на мультиплексо рах типа КП 7, на адресные входы которых поступают сигналы АВО.Табл. 11 - таблица истинности блока 8 контроля цифровой суммы на гра-. ницах кодовых групп. 10Табл. 12 и 13 - таблицы истинности сигналов Е и Г соответственно.(Блок 8 контроля цифровой суммы на границах кодовых групп может быть выполнена на мультиплексорах типа КП 2, на адресные входы которых поступают сигналы ЕР, а на информационные-сигналы,указанные под табл. 12 и 13,Блок 9 памяти может быть выполнен на двух О-триггерах, информационные щ входы которых подключены к соответствующим выходам блока контроля цифровой суммы на границах кодовых групп 8, а тактовые входы - к выходу формирователя синхросигнала кодовых 25 групп.Формула изобретенияКодер балансного кода ЗВ 2, содержащий последовательный регистр, информационный вход которого является информационным входом кодера, тактовый вход последовательного регистра объединен с входом формирователя синхросигнала кодовых групп и является тактовым входом кодера, выходы . последовательного регистра подключены к информационньи входам параллельного регистра, выходы которого подключены к первым входам преобразователя основания кода, первый выход формирователя синхросигналов кодовых группподключен к тактовым входам параллельного регистра и блока памяти, выходысчетчика цифровой суммы в кодовойгруппе подключены к первым входамблока контроля цифровой суммы на границе кодовых групп, выходы которогоподключены к информационным входамблока памяти, выходы которого подключены к вторым входам блока контроляцифровой суммы на границе кодовыхгрупп и преобразователя основаниякода, выходы которого подключенык первым входам блока стробирования,выходы которого подключены к входамсумматора, выход которого являетсявыходом кодера, второй выход формирователя синхросигнала кодовых группсоединен непосредственно с третьимвходом преобразователя основания кода и через формирователь синхросигнала линейных посылок с вторым входом блока стробирования, о т л и ч а -ю щ и й с я тем, что, с целью повышения быстродействия за счет одновременного преобразования кода и контроляцифровой суммы на границах кодовыхгрупп, первые и вторые входы счетчика цифровой суммы в кодовой группеподключены соответственно к выходампараллельного регистра к блока памяти.18 153 223 17 Та блица 12 з з Та блица 3К ЕР ОО 01 0 0 0О 00 1 О0 1 11 0 01 0 11 1 01 1 11 1 1 х х х О х х 2 Е 1 Ез Составитель О.ТюринаРедактор Н.Лазаренко Техред Л.Сердюкова Корректор О.Ципле Заказ 7966/56 Тирах 884 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат Патент , г. Уагород ул. ГагариГага ина 101 0 0 0 0 0 1 0 1 1, 0 1 0 1 1 1 1 0 1 0 1 0 1 0 1 О 1 1 1 х 1 х 1 О х 0 х х х х 1 х х х х х х х х 0 1 х О 1 О 1 х х х х х х х х х

СмотретьЗаявка

4292889, 03.08.1987

ПРЕДПРИЯТИЕ ПЯ Р-6609

КОТИКОВ ИГОРЬ МИХАЙЛОВИЧ, ЧЕРНЫЙ ВЛАДИМИР ЭМИЛЬЕВИЧ, ВАЙС ЭММАНУИЛ АРОНОВИЧ, КАПЛУНОВ ПАВЕЛ ГРИГОРЬЕВИЧ

МПК / Метки

МПК: H03M 5/18

Метки: балансного, кода, кодер

Опубликовано: 23.12.1989

Код ссылки

<a href="https://patents.su/9-1531223-koder-balansnogo-koda-3b2q.html" target="_blank" rel="follow" title="База патентов СССР">Кодер балансного кода 3b2q</a>

Предыдущий патент: Адаптивный аналого-цифровой преобразователь

Следующий патент: Дешифратор

Случайный патент: Разборная контактная пара