Модуль пересчетной схемы в минимальном р-коде фибоначчи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1511862

Автор: Арутюнян

Текст

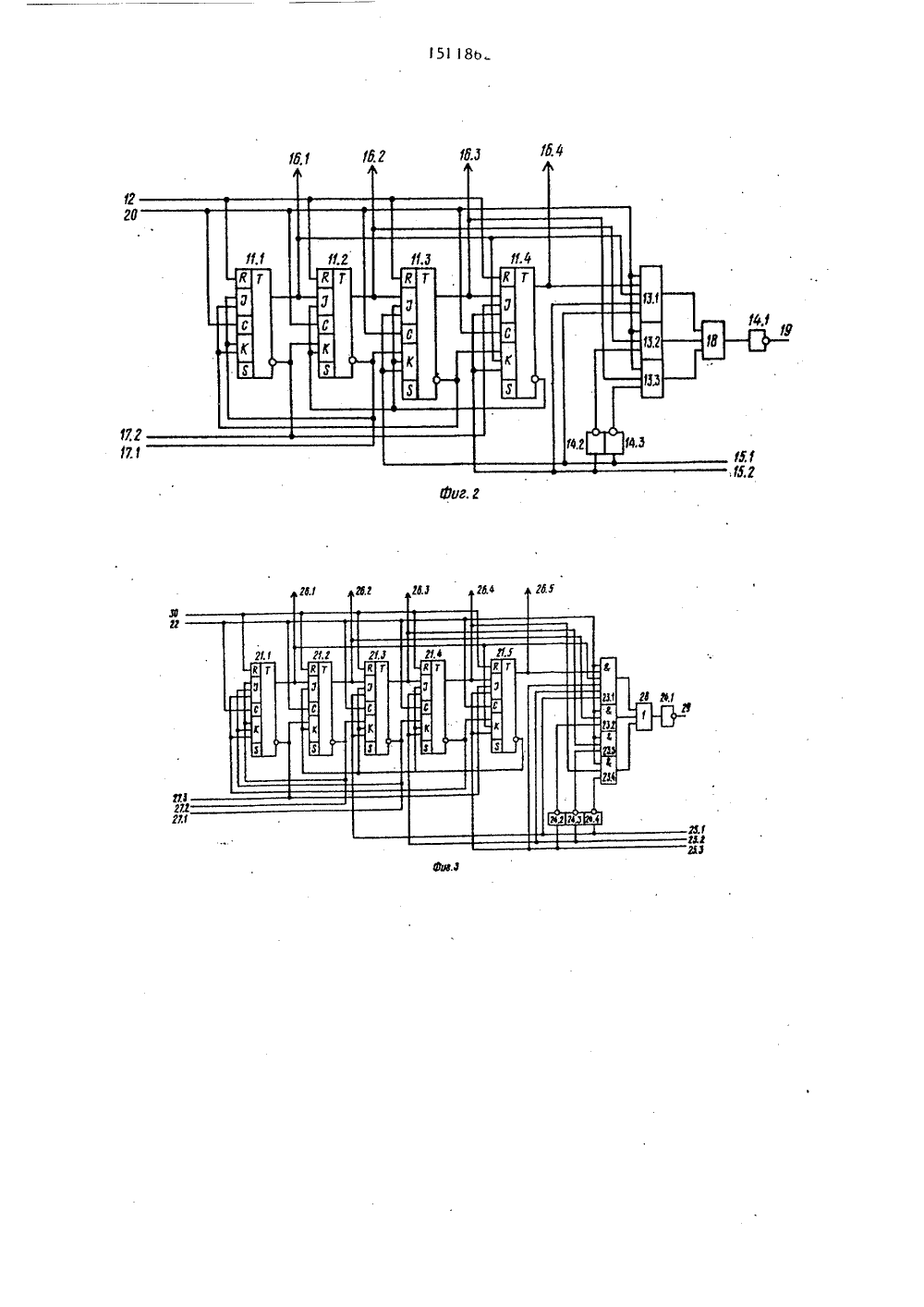

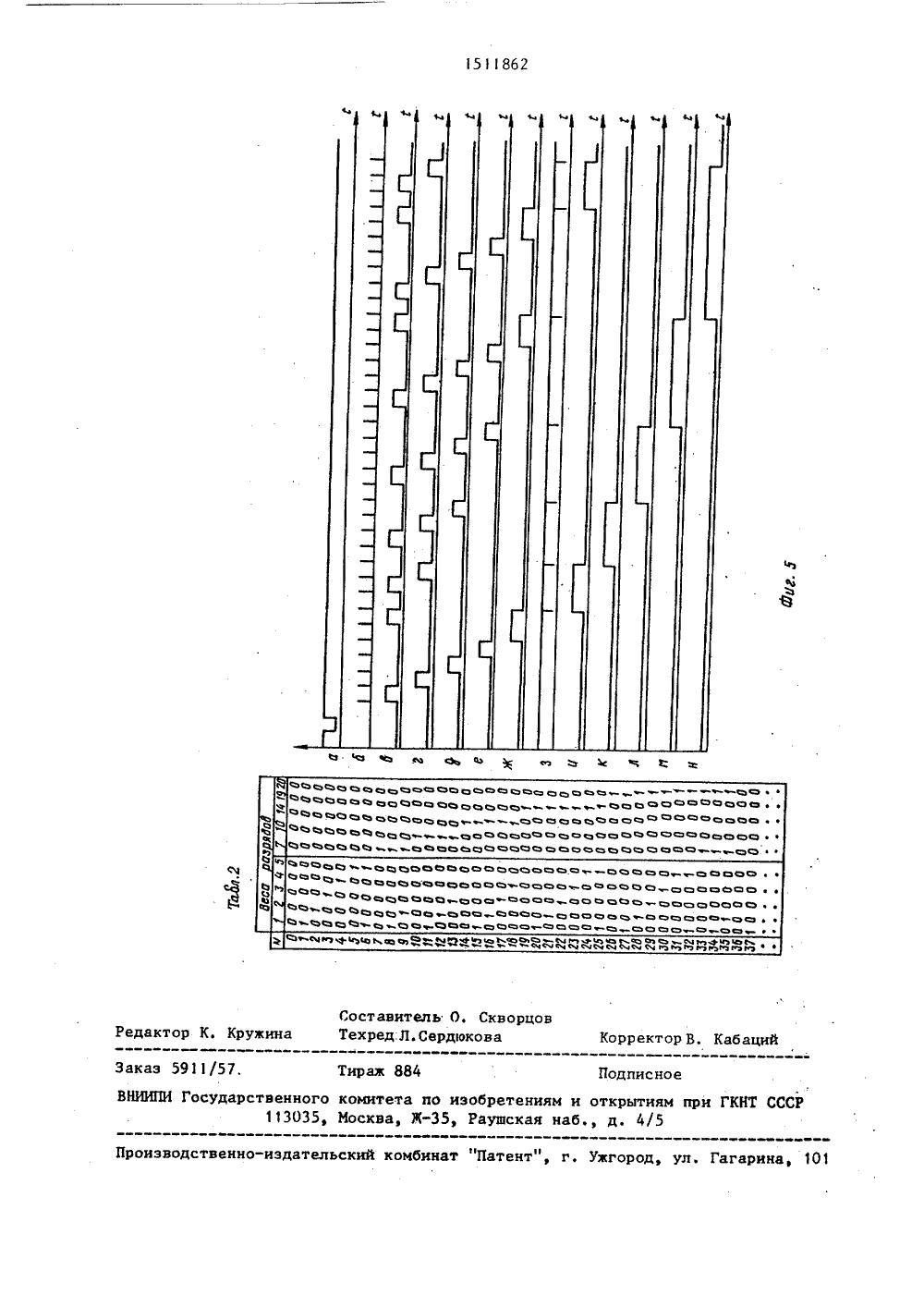

.С.4 Л Е .Б,. ,". ПИСА ОБРЕТЕНИЯ ТЕЛЬСТВ К АВТОРСКОМ 2можностью наращивания разрядности. Цель изобретения - расширение функциональных воэможностей и области применения путем обеспечения пересче та в Р-кодах Фибоначчи, где Р1,2, 3,Устройство содержит первый, второй и (Р+2)-й триггеры, первый и второй элементы НЕ, Р-й управляющий вход и Р-й управляющий выход. Для достижения цели в него дополнительно введены Ртриггер, Р"1 элементов И, Рэлементов НЕ, Руправляющие входы и Руправляющие выходы. Выбор требуемого кода осу" ществляется подачей сигналов на управ ляющие входы. 2 табл., 5 ил. У 36(56) Авторское свидетельство СССРР 1172006, кл. Н 03 К 23/48, 1985Авторское свидетельство СССРИф 1322467, кл, Н 03 К 23/00, .1987(54) МОДЕЛЬ ПЕРЕСЧЕТНОИ СХЕМ В МНИМАЛЬНОМ Р-КОДЕ ФИБОНАЧЧИ(57) Изобретение относится к импуной технике. Может быть использовдля многоразрядного пересчета импусов в минимальном коде Фибоначчилюбом значении Р = 1,2,3, с во ь ль Изобретной техни мпульсользоваение относите и может быгоразрядногоминимальн к мы, описывающие работственно при Р2 и РПредлагаемый (Р+2)дуль пересчетной схенимальном Р-коде ФибоТК-триггеры 1.1-1,Р+2са, элементы И 3.1-3;НЕ 4.1-4.Р+2, входы у5.Р, информационные в6.Р+2, управлякюцие выэлемент ИЛИ 8, выходсчетный вход 10. м соответ но пе чета Фибоначч 3 с зрядности сов в ом кР начен при любомвоэможноспо Р+2. и наращивания р Цель изобрете функциональных в применения путем та в Р-кодах Фиб 3,4,На фиг. пред случая функционал пересчетной схемь ия - расширезможностей иобеспеченияначчи, где Р е области для общего а модуля ьном Р-коо же, в- то же, .4 и 5 диаграмМодуль пересч мальном 2-коде содержит 1 К-триг 12 сброса, элеме менты НЕ 14.1-14 15.1 и 15.2 инфо 16,1-16.4,управл тавлена я схем минимап фиг,на чи; н врем"коде Фибоначчи 3-коде Фибонач оды пересчета и ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГННТ СССР-разрядный мо"мы (фиг.1) в миначчи содержитнину 2 сбро"Р, элементыправления 5. 1 ыходы 6.1 ходы 7.1-7.Р,9 переноса и етной схемы в миниФибоначчи (фиг.2) геры 11.1-11.4, шину нты И 13.1-13,3, эле .3, входы управления рмационные выходы яющие . выходы 17.140 3 151186 17.2, элемент ИЛИ 18, выход 19 переноса и счетный вход 20,Модуль пересчетной схемы в 3-коде Фибоначчи (фиг.З) содержит 1 К-триггеры 21,1-21,5, кину 22 сброса, элементы И 23.1-23.4, элементы НЕ 24.1" 24.4,. нходы управления 25.1-25,3, информационные выходы 26.1-26.5, управляющие выходы 27,1-27.3, элемент 1 О ИЛИ 28, выход 29 переноса и счетный вход 30.Функционирование пересчетной схемы в минимальных Р-кодах Фибоначчи объясняется на примерах для Р 2 5 (фиг.2) и Р 3 (фиг.З).Модуль пересчетной схемы при Р=2 (фиг.2) имеет четыре разряда.Для наращивания разрядности общей схемы отдельные пересчетные модули 20 объединяются следующим образом, Выход 19 переноса каждого модуля схемы соединяется со -счетным входом 12 последующего модуля, управляющие выходы 17.1-17.2 - соответственно с управляющими входами 15.1 и 15.2 предыдущего модуля, входы 20 сброса объединяются.Функционирование пересчетной схемы при Р=2 и совместном включении, 30 например, двух модулей происходит следующим образом.В исходном состоянии все триггеры 11.1-11,4 пересчетных схем находятся в нулевых состояниях (табл.1). 35 При этом на входах 15.1 и 15.2 первого модуля присутствует потенциал логической единицы (с управляющих выходов 17.1 и 17,2), При поступлении первого тактового импульса (фиг,4 б) на счетный вход 12 первого модуля триггер 10,1 устанавливается в состояние логической единицы (Лиг,4 в), т.к. на его всех 1- и К-входах присутствуют потенциалы логической единицы, поступающие с инверсных выходов 1 К-триггеров 11,2 и 11.3. Этот же импульс записывает нуль в триггер 11.2, т.к. на его первом входе присутствует потенциал логического нуля,. подаваемый 50 с прямого выхода триггера 11.1, а на К-входах присутствуют потенциалы логической единицы, подаваемые с инверсных выходов триггеров 11.1 и 11.4. Первым тактовым импульсом 1 К триггер 11.3 тоже устанавливается в нулевое состояние, т.к. на его первом 1-входе присутствует потенциал логического нуля, подаваемый от пря 2 4мого выхода триггера 11.2, а на К-нходах - потенциалы логической единицы, подаваемые соответственно с инверсного выхода триггеров 11.2, 11.4 и с первого управляющего входа 15.1. Триггер 11,4 находится в режиме хранения, т.к. на его втором 1-входе и первом К-входе присутствуют потенциалы логического нуля, подаваемые от триггеров 11.3 и 11.1 соответственно. На выходе лересчетной схемы устанавливается код 0000000 1.При поступлении второго тактового импульса уровень потенциалов на 1- и К-входах триггера 11.1 соответствует логической единице, поэтому он переключается н противоположное состояние логического нуля. На 1-входах триггера 11.2 присутствует потенциал логической единицы, а на первом К-входе - потенциал логического нуля и поэтому по приходу второ" го тактового импульса он переходит в состояние логической единицы (фиг.4 г), Так как значения логических потенциалов на - н К-входах триггеров 11.3 и 11.4 соответствуют режимам записи нуля и хранения, то они не меняют. свое состояние. На выходе пересчет" ной схемы устананливается код 00000010.Перед поступлением третьего такто" ного импульса на первых 1-.и К-.входах триггера 11. присутствуют нулевые логические потенциалы с инверсного,выхода триггера 11,2 и он находится в режиме хранения. На выходах триггера 11.2 присутствуют логические потенциалы, соответствующие режиму записи нуля, а на 1- и К-входах ,триггера 1,3 - логические потенциалы, соответствующие режиму записи единицы. На 1- и К-входах же триггера 11.4 присутствуют потенциалы, соответствующиережиму хранения, и по приходу третьего. тактового импульса на выходе пересчетной схемы устанавливается код 00000100 (фиг.4 д).Перед поступлением четвертого тактового импульса триггер 11.1 находится в режиме хранения, триггер 1.2- в режиме записи нуля, триггер 11.3 " в режиме записи нуля, а триггер 11.4- в режиме записи единицы. После поступления четвертого тактоного импульса на выходе пересчетной схемы устанавливается код 00001000 (фиг.4 е).Перед поступлением пятого тактово, го импульса триггер 11.1 находится в1862 О 5 20 30 35 40 45 50 55 5 15режиме переключения, а триггеры 11.211.4 - в режиме хранения. После поступления пятого тактового импульсана выходе пе ре счетной схемы уст анавливается код 00001001,При поступпении шестого тактового импульса триггеры первого модулянаходятся: триггер 11. 1 - в режимепереключения, триггеры 11,2 и 11.3в режимах храненияа триггер 11.4 -в режиме записи нуля,На первом, втором и третьем входах первого элемента И 13,1 присутствуют потенциалы логической единицы,подаваемые с прямых выходов триггеров 11.1 и 11.4 и с управляющих входов 15,1 и 15.2 пересчетной схемы.Таким образом, шестой тактовый импульс устанавливает все триггерыпервого модуля в исходное состояниеи через первый элемент И 13.1, элемент ИЛИ 18 и первый элемент НЕ 14.1с выхода 19 первого модуля поступаетна вход 12 второго модуля. При этомтриггер 11.1 второго модуля устанавливается в единичное состояние(фиг,4 а). На выходе пересчетной схемы устанавливается код 00010000.При этом на выходе 17.2 второго модуля появляется потенциал логическо"го нуля, поступающий на вход 15.2первого модуля.Седьмой тактовый импульс аналогично устанавливает триггеры первогомодуля в состояния: триггер 11.1в состояние логической единицы, триггеры 11.2 - 11.4 свои состояния неменяют. На выходе пересчетной схемыустанавливается код 0001000.Восьмой тактовый импульс устанавливает триггеры первого модуля в состояния: триггер 11.1 - логическогонуля, триггер 11.2 - логической единицы, триггеры 11.3 и 11,4 свои состояния не меняют. На выходе пересчетной схемы устанавливается код 00010010В этом. состоянии на первом и вто"ром входах второго элемента И 13.2первого модуля присутствуют потенциалы логической единицы, подаваемыесоответственно с прямого выхода триггера 11.2 и с выхода элемента НЕ 14,2.Перед приходом девятого тактовогоимпульса триггеры первого модуля находятся в режимах; триггер 11.1хранения, триггер 11.2 - записи нуля,триггеры 11,3 и 11.4-хранения. Девятый тактовый импульс устанавливает триггеры первого модуля в исходное состояние и с выхода 19 первого модуля поступает на вход 12 второго модуля. На выходе пересчетной схемы устанавливается код 00100000 (фиг.4 и).Десятый тактовый импульс аналогично устанавливаеттриггеры первого модуля в состояния: триггер 11.1 логической единицы, триггеры 11.2 - 1.4 свои состояния не меняют.На выходе пересчетной схемы устанавливаетсй код 0000001.Одиннадцатый тактовый импульс аналогично устанавливает триггеры первого модуля в состояние: триггер 11.1 - логического нуля, триггер ;11.2 - логической единицы, триггеры 1.3 и 11.4 свои состояния не меняют.На выходе пересчетной схемы устанавливается код 00100010. Двенадцатый тактовый импульс устанавливает триггеры первого модуля в состояния: триггер 1.1 свое состояние не меняет, триггер 11.2 - в состояние логического нуля, триггер 11.3 в состояние логической единицы,триггер 11.4 свое состояние не меняет, На выходе пересчетной схемы устанавливается код 00100100. В этом случае на первом и втором входах третьего элемента И 13. 3 присутствуют потенциалы логической единицы, подаваемые соответственно с выхода триггера 11.3 и выхода элемента 14.3, т.к, на управляющем входе 15.1 первого модуля присутствует потенциал логического нуля. Перед приходом тринадцатого тактового импульса триггеры первого модуля находятся в режимах: триггер 11.1 - хранения,триггеры 11.2 и 11,3 - записи нуля,триггер 11.4 - хранения. Таким образом, тринадцатый тактовый импульсустанавливает триггеры первого модуля в исходное состояние и с выхода 19 первого модуля поступает на вход12 второго модуля. На выходе пересчетной схемы устанавливается код 01000000 (фиг. 4 к), В дальнейшем пе;. ресчетная схема функционирует анало, гично. Модуль пересчетной схемы при Рщ 3 (фиг.3)имеет пять разрядов, а для наращивания разрядности общей схемы ряд модулей объединяются следующим образом. Выход 29 переноса каждого модуля соединяется со счетнымвходом 22 последующего модуля, уп 1511862равляющие выходы 27,1, 27.2 и 27,3 -соответственно с управляющими входами25.1, 25.2 и 25.3 предыдущей, входы30 сброса объединяются.Функционирование пересчетной схемыпри Р=З и совместном включении, например, двух модулей происходит аналогично описанной схеме при Р=2, Отличие заключается лишь в том, что 10при Р=З 1 К-триггеры первого модуляустанавливаются в исходное состояниекаждый раз не только после переполнения модуля, а также после установки одного из ТК-триггеров 21,1-21,3в единичное состояние второго модуля (см. т абл, 2. ),Модуль пересчетной схемы в общем случае при Р = и; где и = 1,2,3,имеет Р+2 разрядов, а для наращивания разрядности общей схемы ряд моду"лей объединяется следующим образом.Выход переноса 9 каждого модуля.(фиг.1) соединяется со счетным входом 10 последующего модуля, управляющие выходы 7.1-7.Р - соответственнос управляющими входами 5.1-5.Р предыдущего модуля, а входы 30 сбросаобъединяются,30. Функционирование пересчетной схемы при Р = и и совместном включении, например, двух модулей происходит аналогично описанным схемам при Р 2 и РЗ. Отличие заключается в том, что при Р=п 1 К-триггеры первого модуля устанавливаются в исходное состояние каждый раз не только после переполнения модуля, а также после установки одного из триггеров 1.1 - 40 1.Р.1 второго модуля в единичное состояние.Таким образом, предлагаемый модуль пересчетной схемы позволяет произвести пересчет импульсов в минимальных кодах Фибоначчи при любых значениях Р=1,2,3 что свидетельствует о его широких функциональных возможностях и области применения.50формула изобретения Модель пересчетной схемы в минимальном Р-коде Фибоначчи.(где Р=1,2, 3), содержащая первый, второй и (Р+2)-й триггеры, входы сброса которых объединены и подключены к входу сброса пересчетной схемы, первый и второй элементы И, первый и второй элементы НЕ, первый вход первого элемента И является Р-м управляющим входом пересчетной схемы, единичные выходы триггеров являются соответст вующими информационными выходами пересчетной схемы, инверсный выход первого триггера является Р-м управ-. ляющим выходом пересчетной схемы, прямой выход второго триггера соединен с первым входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, прямой.вы ход первого триггера подключен к второму входу первого элемента И, первому 1-входу второго триггера и первому .К-входу (Р+2)-го триггера, первый К-вход второго триггера н первый 1-вход (Р+2)-го триггера объединены и подключены к инверсному выходу первого триггера, инверсный выход второго триггера подключен к первым 1- и К-входам первого триггера, прямой выход (Р+2)-го триггера подклю" чен к третьему входу первого элемента И, выход которого подключен к второму входу элемента ИЛИ, подключенного выходом к входу первого элемента НЕ, инверсный выход (Р+2)"го триггера подключен к вторым 1- и К-вхо-. дам второго триггера, третьи 1" и К-входы (Р+2)-го триггера и вход второго элемента НЕ объединены и подключены к Р-му управляющему входу пересчетной схемы, выход второго элемента НЕ подключен к второму входу второго элемента И, синхровходы,триггеров, четвертый вход первого элемента И и третий вход второго элемента И объединены н подключены ксчетному входу пересчетной схемы, а выход первого элемента НЕ подключен к выходу переноса пересчетной схемю, о т л и ч а ю щ а я с я тем, что, с целью расширения функциональных возможностей и области применения за. счет обеспечения пересчета при Р=2,3, 4 она дополнительно содержит Ртриггеров, Рэлементов И, Р"1 элементов НЕ, Руправляющих входов и Руправляющих выходов, причем третьи входы дополнительных элементов И и синхронизирующие входы дополнительных триггеров объединены и подключены к счетному входу пересчетной схемы, каждые д-е 1- и К-входы триггера первого разряда соединены с ин-, версным выходом триггера (д+1)-го разряда, где д 1,2 (Р+), вто 9 151 рые 1- й К-входы каждого ш-го триггера с третьего по (Р+2)-й разрядов . соединены соответственно с прямыми и инверсными выходами триггера (щ)- го разряда, первые 1-,и К-входы всех триггеров с третьего по (Р+1)-й разрядов соединены с инверсным выходом триггера (Р+2)-го разряда, а их третьи 1- и К-входы - с входами управления соответственно с первого по (Р)-Й, первые входы с третьего по (Р+1)-й элементов И соединены соответственно с прямыми выходами триг 18621 Огеров с третьего по (Р+1)-й разрядов,а вторые входы - с выходами с третьего по (Р+1)-й элементов НЕ, входы 5которых соединены с входами управления с (1-1)-го по первый и с соответствующими дополнительными входами первого элемента И, а инверсные выходытриггеров с второго по Р-Й разрядовсоединены с соответствующими управ-ляющими выходами с второго по Р-Й,выходы дополнительных элементов Исоединены с дополнительными входамиэлемента ИЛИ.151862 а о оьоооьььььь авьо ьь ооь о ооооое ьь ьь оььооооььь о ьь ь о о о ь ь ььоч ч О оо,ь-о ьо оо ьои ф.ьооььФ о э оо оь ао оьФ Ффсл мйс к Фсч ь ы ыью Ф ьь (ч Зъ фъ э В 3 фыыфыфъ ьъ ечр Фъчв ьцьъ-чье тзфсэедыъьч цыссСоставитель О. Скворцов едактор К. Кручина Техред Л.Сердокова Корректор В. Кабаказ 5911/57 ираж 8 одписно НИИПИ Государственного комитета по изобретениям н о 113035, Москва, Я, Раушская наб., в ею Ш ем ш етшыю 4 ШВФронэводственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 10 сэььььоьььо ььььь ьь ьоо ь ьь ьо оь ььььььььььььсз оь ьоое ооофо щ о ь е о о ь ,. ь оъсо ьъ съоо-оьь ооь-ьь оь ььь ь сьоь ч ььоьм ооооьоф оокрытиям при ГКНд. 4/5

СмотретьЗаявка

4385410, 29.02.1988

ПРЕДПРИЯТИЕ ПЯ А-1376

АРУТЮНЯН САМВЕЛ ГАРУШЕВИЧ, АРУТЮНЯН ВАГАН ШАВАРШОВИЧ

МПК / Метки

МПК: H03K 23/40

Метки: минимальном, модуль, пересчетной, р-коде, схемы, фибоначчи

Опубликовано: 30.09.1989

Код ссылки

<a href="https://patents.su/9-1511862-modul-pereschetnojj-skhemy-v-minimalnom-r-kode-fibonachchi.html" target="_blank" rel="follow" title="База патентов СССР">Модуль пересчетной схемы в минимальном р-коде фибоначчи</a>

Предыдущий патент: Счетчик импульсов в максимальных р-кодах фибоначчи

Следующий патент: Реверсивный счетчик

Случайный патент: Способ формирования покрытий