Генератор псевдослучайных последовательностей

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

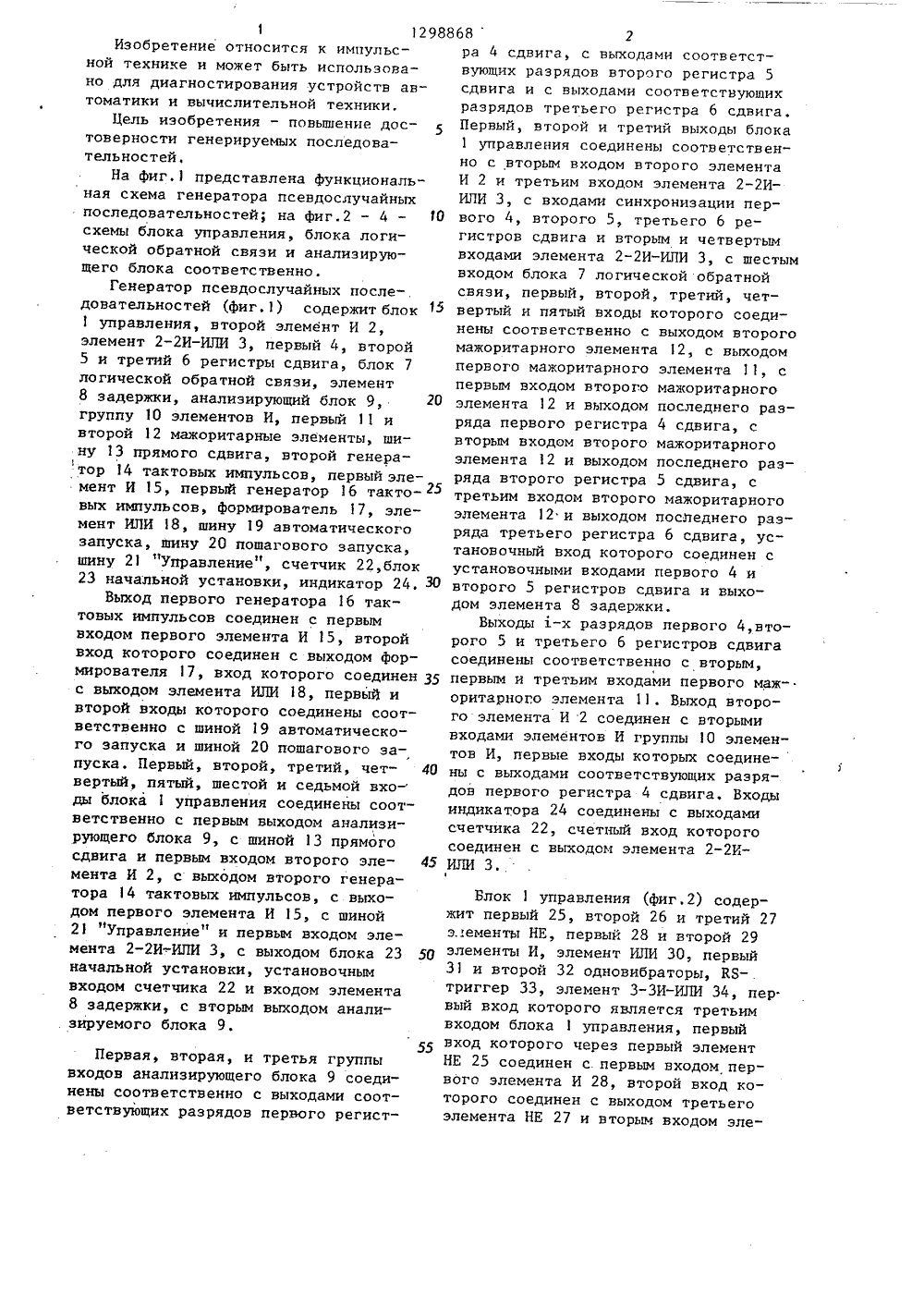

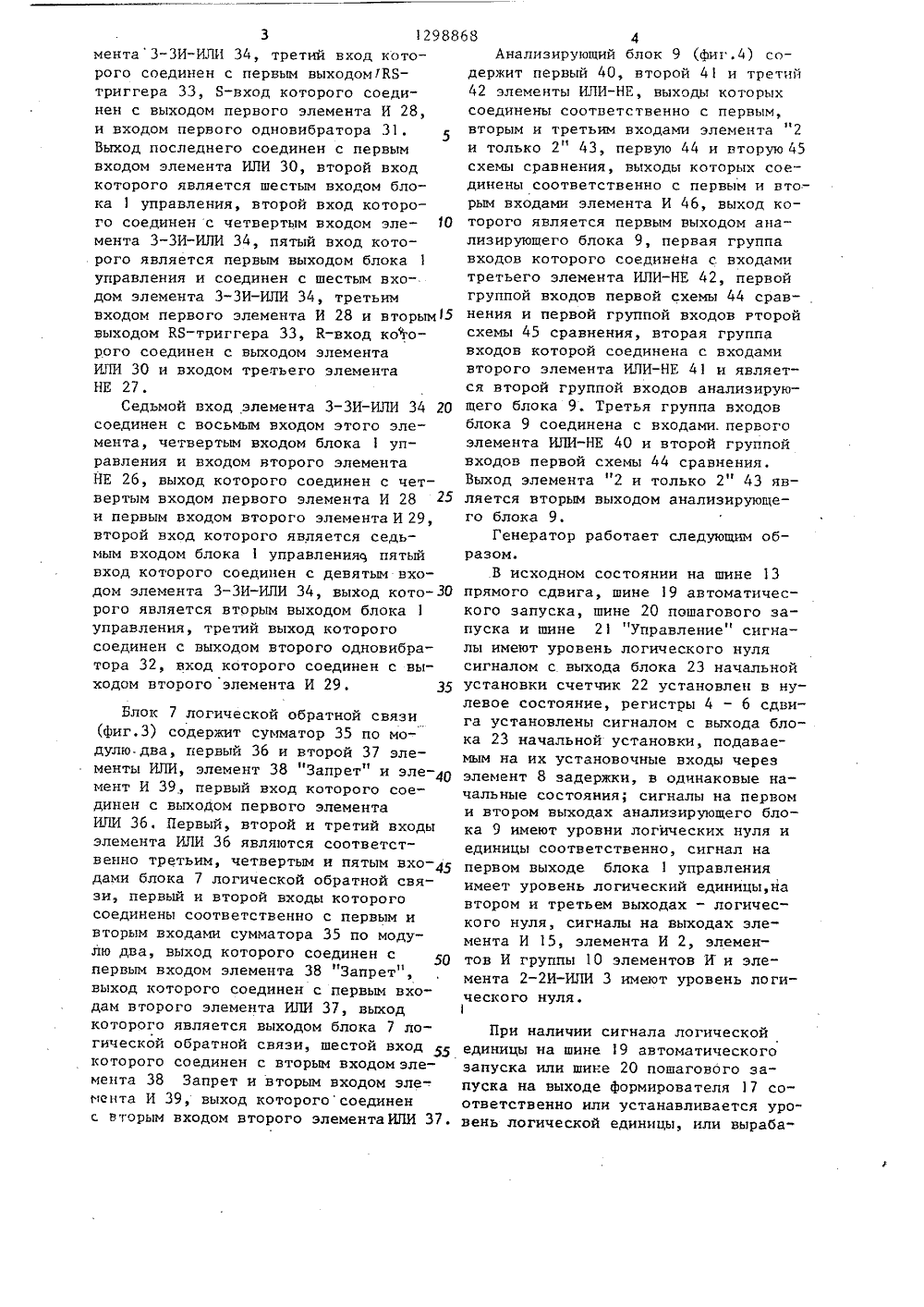

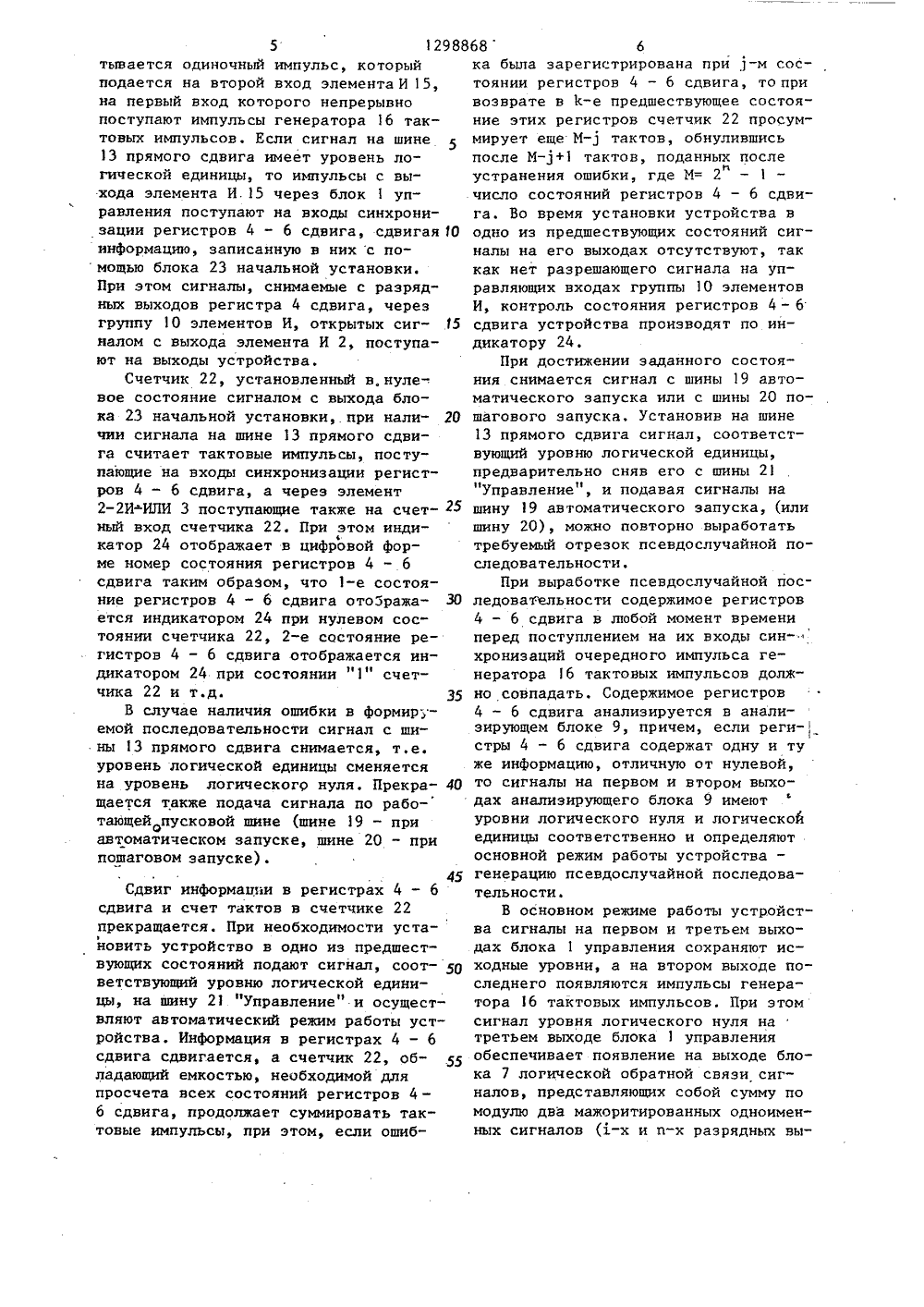

,80129886 я)4 НОЗК 3/ О ОПИСАНИЕ ИЗОБРЕТЕН СТ Бюл. 1= 1 в, С.С.Б лкания 2 (088, 8) .П. Модел язи. - М. ование канаСвязь, 1979 во ССС 2, 197 видетельс С 06 Р 1/ ЛУЧАЙНЫХ ПОСЛЕ к импульсспользоватноси т быт роиств авехники. вания у тельнойповыше емых пос е достоедователь -т регистр оде АРСТВЕННЫЙ НОМИТЕТ СССР ЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ К АВТОРСКОМУ СВИ Е(56) Галкин Алов систем свс.62,63.Авторское сВ 756397, кл.(57) Изобретение оной технике и можено для диагносциротоматики и вычислиЦель изобретения -верности генерируностей. Устройство 4 сдвига, группу 10 элементов И, элемент И 15, генератор 16 тактовых импульсов, формирователь 17, элементИЛИ 18, счетчик 22, блок 23 начальнойчстановки, индикатор 24 и шины 13,19,20 и 21 прямого сдвига,автоматического запуска,пошагового запуска и"Управление" соответственно. Для достижения поставленной цели в устройство введены блок 1 управления, элемент2 И,элемент 2-2 И-ИЛИ З,регистры 5 и 6сдвига, блок 7 логической обратной связи, элемент 8 задержки, анализирующийблок 9, мажоритарные элементы 11 и12, генератор 14 тактовых импульсови образованы новые связи между элементами устройства. В описании пред в Жставлены примеры конкретного выполнения блока 1 управления, блока 7 ло- М Фгической обратной связи и аналиэиру- (ющего блока 9. 3 з.п. ф-лы, 4 ил.12988Изобретение относится к импульсной технике и может быть использовано для диагностирования устройств автоматики и вычислительной техники,Цель изобретения - повышение достоверности генерируемых последовательностей.На фиг. представлена функциональная схема генератора псевдослучайных последовательностей; на фиг.2 - 4 - 1 О схемы блока управления, блока логической обратной связи и анализирующего блока соответственно.Генератор псевдослучайных после-. довательностей (фиг.) содержит блокуправления, второй элемент И 2, элемент 2-2 И-ИЛИ 3, первый 4, второй 5 и третий 6 регистры сдвига, блок 7 логической обратной связи, элемент 8 задержки, анализирующий блок 9, 20 группу 10 элементов И, первый 11 и второй 12 мажоритарные элементы, шину 13 прямого сдвига, второй генератор 14 тактовых импульсов, первый элемент И 15, первый генератор 16 тактовых импульсов, формирователь 17, элемент ИЛИ 18, шину 19 автоматического запуска, шину 20 пошагового запуска, шину 2) "Управление", счетчик 22,блок 23 начальной установки, индикатор 24, 30Выход первого генератора 16 тактовых импульсов соединен с первым входом первого элемента И 15, второй вход которого соединен с выходом формирователя 17, вход которого соединен 35 с выходом элемента ИЛИ 18, первый и второй входы которого соединены соответственно с шиной 19 автоматического запуска и шиной 20 пошагового запуска. Первый, второй, третий, чет вертый, пятый, шестой и седьмой вхо- ды блока 1 управления соединены соответственно с первым выходом анализирующего блока 9, с шиной 13 прямого сдвига и первым входом второго эле мента И 2, с выходом второго генератора 14 тактовых импульсов, с выходом первого элемента И 15, с шиной 21 "Управление" и первым входом элемента 2-2 И-ИЛИ 3, с выходом блока 23 50 начальной установки, установочным входом счетчика 22 и входом элемента 8 задержки, с вторым выходом анализируемого блока 9. дов первого регистра 4 сдвига, Входы индикатора 24 соединены с выходами счетчика 22, счетный вход которого соединен с выходом элемента 2-2 КИЛИ 3. Первая, вторая, и третья группы входов анализирующего блока 9 соединены соответственно с выходами соответствующих разрядов первого регист 682ра 4 сдвига, с выходами соответствующих разрядов второго регистра 5сдвига и с выходами соответствующихразрядов третьего регистра 6 сдвига.Первый, второй и третий выходы блока1 управления соединены соответственно с вторым входом второго элементаИ 2 и третьим входом элемента 2-2 ИИЛИ 3, с входами синхронизации первого 4, второго 5, третьего 6 регистров сдвига и вторым и четвертым входами элемента 2-2 И-ИЛИ 3, с шестым входом блока 7 логической обратнойсвязи, первый, второй, третий, четвертый и пятый входы которого соедииены соответственно с выходом второгомажоритарного элемента 12, с выходомпервого мажоритарного элемента 11, с первым входом второго мажоритарногоэлемента 12 и выходом последнего разряда первого регистра 4 сдвига, свторым входом второго мажоритарного элемента 12 и выходом последнего разряда второго регистра 5 сдвига, с третьим входом второго мажоритарногоэлемента 12 и выходом последнего разряда третьего регистра 6 сдвига, установочный вход которого соединен сустановочными входами первого 4 ивторого 5 регистров сдвига и выходом элемента 8 задержки. Выходы 1-х разрядов первого 4,второго 5 и третьего 6 регистров сдвигасоединены соответственно с вторым,первым и третьим входами первого мажоритарного элемента 11. Выход второго элемента И 2 соединен с вторыми входами элементов И группы 10 элементов И, первые входы которых соединены с выходами соответствующих раэряБлок 1 управления (фиг,2) содержит первый 25, второй 26 и третий 27 э,.ементы НЕ, первый 28 и второй 29 элементы И, элемент ИЛИ 30, первый 31 и второй 32 одновибраторы, КБ- . триггер 33, элемент 3-ЗИ-ИЛИ 34, пер. вый вход которого является третьим входом блока 1 управления, первый вход которого через первый элемент НЕ 25 соединен с. первым входом первого элемента И 28, второй вход которого соединен с выходом третьего элемента НЕ 27 и вторым входом эле68 4Анализирующий блок 9 (фиг.4) содержит первый 40, второй 41 и третий42 элементы ИЛИ-НЕ, выходы которыхсоединены соответственно с первым,вторым и третьим входами элемента "2и только 2" 43, первую 44 и вторую 45схемы сравнения, выходы которых соединены соответственно с первым и вторым входами элемента И 46, выход которого является первым выходом анализирующего блока 9, первая группавходов которого соединена с входамитретьего элемента ИЛИ-НЕ 42, первойгруппой входов первой схемы 44 сравнения и первой группой входов рторойсхемы 45 сравнения, вторая группавходов которой соединена с входамивторого элемента ИЛИ-НЕ 41 и является второй группой входов анализирующего блока 9. Третья группа входовблока 9 соединена с входами. первогоэлемента ИЛИ-НЕ 40 и второй группойвходов первой схемы 44 сравнения.Выход элемента "2 и только 2" 43 является вторым выходом анализирующего блока 9,Генератор работает следующим образом.В исходном состоянии на шине 13прямого сдвига, шине 19 автоматического запуска, шине 20 пошагового запуска и шине 21 "Управление" сигналы имеют уровень логического нулясигналом с выхода блока 23 начальнойустановки счетчик 22 установлен в нулевое состояние, регистры 4 - 6 сдвига установлены сигналом с выхода блока 23 начальной установки, подаваемым на их установочные входы черезэлемент 8 задержки, в одинаковые начальные состояния; сигналы на первоми втором выходах анализирующего блока 9 имеют уровни логических нуля иединицы соответственно, сигнал напервом выходе блока 1 управленияимеет уровень логический единицы,навтором и третьем выходах - логического нуля, сигналы на выходах элемента И 15, элемента И 2, элементов И группы 10 элементов И и элемента 2-2 И-ИЛИ 3 имеют уровень логического нуля.1 Блок 7 логической обратной связи (фиг.З) содержит сумматор 35 по модулю.два, первый 36 и второй 37 элементы ИЛИ, элемент 38 "Запрет" и элемент И 39, первый вход которого соединен с выходом первого элемента ИЛИ ЗбПервый, второй и третий входы элемента ИЛИ Зб являются соответственно третьим, четвертым и пятым входами блока 7 логической обратной связи, первый и второй входы которого соединены соответственно с первым и вторым входами сумматора 35 по модулю два, выход которого соединен с первым входом элемента 38 "Запрет", выход которого соединен с первым входам второго элемента ИЛИ 37, выход которого является выходом блока 7 логической обратной связи, шестой вход которого соединен с вторым входом элемента 38 Запрет и вторым входом элемента И 39, выход которогосоединен с вторым входом второго элементаИПИ 37. 3 12988 мента 3-ЗИ-ИЛИ 34, третий вход которого соединен с первым выходомКБ- триггера 33, Б-вход которого соединен с выходом первого элемента И 28, и входом первого одновибратора 31.Выход последнего соединен с первым входом элемента ИЛИ 30, второй вход которого является шестым входом блока 1 управления, второй вход которого соединен с четвертым входом зле О мента 3-ЗИ-ИЛИ 34, пятый вход которого является первым выходом блока 1 управления и соединен с шестым входом элемента 3-ЗИ в И 34, третьим входом первого элемента И 28 и вторым 5 выходом КБ-триггера 33, К-вход которого соединен с выходом элемента ИЛИ 30 и входом третьего элемента НЕ 27.Седьмой вход элемента 3-ЗИ-ИЛИ 34 20 соединен с восьмым входом этого элемента, четвертым входом блока 1 управления и входом второго элемента НЕ 26, выход которого соединен с четвертым входом первого элемента И 28 25 и первым входом второго элемента И 29, второй вход которого является седьмым входом блока 1 управления пятый вход которого соединен с девятым входом элемента 3-ЗИ-ИЛИ 34, выход которого является вторым выходом блока 1 управления, третий выход которого соединен с выходом второго одновибратора 32, вход которого соединен с выходом второго элемента И 29. 35 При наличии сигнала логической единицы на шине 19 автоматического запуска или шике 20 пошагового запуска на выходе Формирователя 17 соответственно или устанавливается уровень логической единицы, или выраба"5 12988 тывается одиночный импульс, который подается на второй вход элемента И 15, на первый вход которого непрерывно поступают импульсы генератора 16 тактовых импульсов. Если сигнал на шине 13 прямого сдвига имеет уровень логической единицы, то импульсы с выхода элемента И.15 через блок 1 управления поступают на входы синхронизации регистров 4 - 6 сдвига, сдвигая 10 информацию, записанную в них с помощью блока 23 начальной установки. При этом сигналы, снимаемые с разрядных выходов регистра 4 сдвига, через группу 10 элементов И, открытых сиг налом с выхода элемента И 2, поступают на выходы устройства.Счетчик 22, установленный внулевое состояние сигналом с выхода блока 23 начальной установки, при нали чии сигнала на шине 13 прямого сдвига считает тактовые импульсы, поступающие на входы синхронизации регистров 4 - б сдвига, а через элемент 2-2 И ИЛИ 3 поступающие также на счет иый вход счетчика 22. При этом индиФкатор 24 отображает в цифровой форме номер состояния регистров 4 - 6 сдвига таким образом, что 1-е состояние регистров 4 - 6 сдвига отобража ется индикатором 24 при нулевом сос" тоянии счетчика 22, 2-е состояние регистров 4 - 6 сдвига отображается индикатором 24 при состоянии счетчика 22 и т.д. 35В случае наличия ошибки в формируемой последовательности сигнал с шины 13 прямого сдвига снимается, т.е. уровень логической единицы сменяется на уровень логического нуля. Прекра" 40 щается также подача сигнала по работающей пусковой шине (шине 19 - при автоматическом запуске, шине 20 - при пошаговом запуске).45Сдвиг информации в регистрах 4 - 6 сдвига и счет тактов в счетчике 22 прекращается. При необходимости устанавить устройство в одно из предшестВующих состояний подают сигналр соот 50 ветствующий уровню логической единицы, иа шину 21 "Управление" и осуществляют автоматический режим работы устройства, Информация в регистрах 4 - 6 сдвига сдвигается, а счетчик 22, об- .55 падающий емкостью, необходимой для просчета всех состояний регистров 4 - 6 сдвига, продолжает суммировать тактовые импульсы, при этом, если ошиб 68 6ка была зарегистрирована при 1-м состоянии регистров 4 - 6 сдвига, то при возврате в Е-е предшествующее состояние этих регистров счетчик 22 просуммирует еще Мтактов, обнулившись после М+1 тактов, поданных послелустранения ошибки, где М= 2 - 1 число состояний регистров 4 - 6 сдвига. Во время установки устройства в одно из предшествующих состояний сигналы на его выходах отсутствуют, так как нет разрешающего сигнала на управляющих входах группы 10 элементов И, контроль состояния регистров 4 - 6 сдвига устройства производят по индикатору 24.При достижении заданного состояния снимается сигнал с шины 19 автоматического запуска или с шины 20 пошагового запуска. Установив на шине 13 прямого сдвига сигнал, соответствующий уровню логической единицы, предварительно сняв его с шины 21 "Управление", и подавая сигналы на шину 19 автоматического запуска, (или шину 20), можно повторно выработать требуемый отрезок псевдослучайной последовательности.При выработке псевдослучайной последовательности содержимое регистров 4 - 6 сдвига в любой момент времени перед поступлением на их входы син" хронизаций очередного импульса генератора 16 тактовых импульсов должно совпадать. Содержимое регистров 4 - б сдвига анализируется в анализирующем блоке 9, причем, если реги- стры 4 - б сдвига содержат одну и ту же информацию, отличную от нулевой, то сигналы на первом и втором выходах анализирующего блока 9 имеют уровни логического нуля и логической единицы соответственно и определяют основной режим работы устройства - генерацию псевдослучайной последовательности.В основном режиме работы устройства сигналы на первом и третьем выходах блока 1 управления сохраняют исходные уровни, а на втором выходе последнего появляются импульсы генератора 16 тактовых импульсов. При этом сигнал уровня логического нуля на третьем выходе блока 1 управления обеспечивает появление на выходе блока 7 логической обратной связи сигналов, представляющих собой сумму по модулю два мажоритированных одноименных сигналов (1-х и п-х разрядных вы 7 12988ходоврегистров 4 - 6 сдвига соответственно), вводимых н блок 7 логической обратной связи через первый ивторой входы последнего с выходовмажоритарных элементов 11 и 12, Еслииз-за воздействия помехи регистры 4 -6 сдвига не содержат одну и ту же информацию, отличную от нулевой, хотябы в двух регистрах, то имеет местоискажение информации первого вида, 10которому на обоих выходах анализирующего блока 9 соответствуют сигналыуровня логического нуля. Если жеиз-за воздействия помехи два любыхрегистра сдвига обнулились, то имеетместо искажение информации второговида, которому на первом выходе анализирующего блока 9 соответствуетуровень логической единицы, а на втором выходе последнего - уровень логического нуля,Устранение искажений информацииосуществляется в режиме коррекции,вкоторый устройство переводится бло -ком 1 управления при обнаружении ис 25кажений информации. Обнаружение искажений реализуется после поступленияна входы синхронизациирегистров 4 -6 сдвига очередного импульса генератора 16 тактовых импульсов путем опроса в блоке 1 управления состоянийвыходов анализирующего блока 9.В режиме коррекции независимо отвида искажения информации на второмвыходе блока 1 управления появляются 35импульсы генератора 14 тактовых импульсов, а на первом выходе блока 1управления появляется сигнал, имеющий уровень логического нуля и блокирующий через элемент И 2 выходные 40сигналы устройства, а через третийвход элемента 2-2 И-ИЛИ 3 блокирующий счетный вход счетчика 22 от импульсов генератора 14 тактовых импульсов45Если блок 1 управления переводитгенератор псевдослучайных последовательностей в режим коррекции при обнаружении искажения информации первого вида, то сигнал на третьем выходе блока 1 управления сохраняет уровень логического нуля, при которомна выходе блока 7 логической обратной связи появляются сигналы, представляющие собой сумму по модулю два 55мажоритированных одноименных сигналов (х-х и и-х разрядных выходов регистров 4 - 6 сдвига соответственне),68 8вводимых в блок 7 логической обратной связи через первый и второй входы последнего с выходом мажоритарных элементов 11 и 12, Если же блок 1 управления переводит генератор псевдослучайных последовательностей в режим коррекции при обнаружении искажения информации второго вида, то сигнал на третьем выходе блока 1 управления имеет уровень логической единицы, при котором сигналы на выходе блока 7 логической обратной связи повторяют сигналы, поступающие на один из входов (третий, четвертый или пятый) последнего с и-го разрядного выхода необнуленного регистра сдвига, так как на два других входа блока 7 логической обратной связи поступают сигналы с п-х разрядных выходов обнуленных регистров сдвига.Состояния выходов блока 1 управления, соответствующие режиму коррекции, должны сохраняться в течение времени, необходимого для и-кратного сдвига информации, содер;ащейся в регистрах 4 - 6 сдвига в момент перевода устройства в режим коррекции, до поступления очередного импульса генератора 16 тактовых импульсов, что обеспечивает восстановление информации (устранение искажений) в регистрах 4 - 6 сдвига до полного совпадения их содержимого. После устранения искажений блок 1 управления автоматически переходит в исходное состояние и устройство готово к выдаче отрезка псевдослучайной последовательности, в котором были обнаружены искажения, и выработке последующих отрезков псевдослучайной последовательности.Блок 1 управления работает следующим образом, В исходном состоянии КБ-триггер 33 установлен в нулевое состояние, сигнал на третьем входе блока 1 управления представляет собой последовательность тактовых импульсов, сигналы на втором, четвертом, пятом, шестом и седьмом входах, втором и третьем выходах блока 1 управления имеют уровень логического нуля, сигналы на первом входе и первом выходе блока 1 управления имеют уровень логической единицы, при этом прохождение сигналов с выходов элементов НЕ 26 и 27 и второго нулевого выхода КБ-триггера 33, имеющих уровень логической единицы, через эле9 12988 мент И 28 блокируется сигналом с выхода элемента НЕ 25, имеющим уровень логического нуля, а сигналом с первого (единичного) выхода КЯ-триггера 33 заблокировано поступление тактовых импульсов через третий вход блока 1 управления и первый вход элемента . 3-ЗИ-ИЛИ 34 на второй выход блока 1 управления.Если на второй или пятый вход бло ка 1 управления подан сигнал, имеющий уровень логической единицы, и на четвертый вход блока 1 управления поступают тактовые импульсы, то через седьмой вход элемента 3-ЗИ-ИЛИ 34 тактовые импульсы поступают на второй выход блока 1 управления, С четвертого входа блока 1 управления тактовые импульсы поступают также на вход элемента НЕ 26, инвертирующего 20 эти импульсы, что позволяет поддерживать уровень логической единицы на выходе последнего между двумя ближайшими соседними тактовыми импульсами, поступающими на четвертый вход блока25 1 управления. При этом на выходе элеО мента И 28 появляется сигнал, имеющий уровень логической единицы и переводящий КВ-триггер 33 в единичное состояние, при котором блокируется прохождение тактовых импульсов с четвертого входа блока 1 управления на второй выход блока 1 управления, а сигнал на выходе элемента И 28 имеет уровень логического нуля, 35 В единичном состоянии КБ-триггера 33 на втором выходе блока 1 управления появляются сигналы, поступающие через третий вход блока 1 управления щ на первый вход элемента 3-ЗИ-ИЛИ 34., Сигнал, переводящий ЕБ-триггер 33 в единичйое состояние, поступает на вход первого одновибратора 31 с задержкой на входе, что обеспечивает подачу на первый вход элемента ИЛИ 30 импульса, осуществляющего установку через элемент ИЛИ 30 КЯ-триггера 33 в нулевое состояние, при этом через элемент НЕ 27 блокируется элемент 50 И 28, а по второму входу элемента 3-ЗИ-ИЛИ 34 блокируется поступление сигналов через третий вход блока 1 управления и первый вход элемента 3-ЗИ-ИЛИ 34 на второй выход блока управления. КЗ-триггер ЗЗ устанавливается в исходное состояние также сигналом с шестого входа блокауправления. Сигнал на третьем выходе 68 1 Облока 1 управления имеет уровень логической единицы после запуска второго одновибратора 32, реализуемогочерез второй элемент И 29, когда сигналы на четвертом и седьмом входахблока 1 управления имеют уровни логического нуля и логической единицысоответственно.Блок 7 логической обратной связиработает следующим образом. В исходном состоянии сигналы на входах и выходе блока 7 логической обратной связи имеют уровни логического нуля.Если сигнал на шестом входе блока7 логической обратной связи имеетуровень логической единицы, то наего выходе сигнал имеет уровень логической единицы, если хотя бы на одиниз его входов (третий, четвертый, пятый) подан сигнал, имеющий уровеньлогической единицы, Если сигнал нашестом входе блока 7 логической обратной связи имеет уровень логического нуля, то на его выходе появляютсясигналы, представляющие собой суммупо модулю два сигналов, поданных наего первый и второй входы,Анализирующий блок 9 работает следующим образом. Если на входы первой,второй м третьей групп его входов поступает одноименная информация, тосигналы на его первом и втором выходах имеют уровни логической единицыи логического нуля соответственно.Если на входы второй, третьей илипервой, третьей или первой, второйгрупп входов анализирующего блока 9поступает нулевая информация, то сигналы на его первом и втором выходахимеют уровни логического нуля и логической единицы соответственно, Если на входы первой, второй и третьейгрупп входов анализирующего блока 9не поступает одноименная информацияили последняя поступает лишь на входы второй, третьей или первой, третьей или первой, второй групп его входов, то сигналы на его первом и втором выходах имеют уровни логическогонуля. Формула изобретения 1, Генератор псевдослучайных последовательностей, содержащий первый регистр сдвига, выходы разрядов которого соединены с первыми входами элементов И группы элементов И, бло начальной установки, выход которого12988 б 8 50 55 соединен с установочным входом счетчика, выходы разрядов которого соединены с соответствующими входами индикатора, первый генератор тактовыхимпульсов, выход которого соединен с первым входом первого элемента И,второй вход которого соединен с выходомФормирователя, вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого соединены с шиной 10 автоматического запуска и с шиной пошагового запуска соответственно, шину прямого сдвига, шину "Управление", отличающийся тем, что, с целью повышения достоверности генери о руемых последовательностей, в него введены второй и третий регистры сдвига, второй элемент И, элемент 2- 2 И-ИЛИ, блок управления, элемент задержки, анализирующий блок, второй генератор тактовых импульсов, блок логической обратной связи, первый и второй мажоритарные элементы, выходы которых соединены с вторым и первым25 входами соответственно блока логической.обратной связи, выход которого соединен с информационными входами первого, второго и третьего регистровсдвига, установочные входы которыхсоединены с выходом элемента задержки, вход которого соединен с выходом блока начальной установки и шестымвходом блока управления, первый, второй, третий, четвертый, пятый, шестой и седьмой входы которого соедине- З 5 ны соответственно с первым выходом анализирующего блока, шиной прямого сдвига и первым входом второго элемента И, выходом второго генератора тактовых импульсов, выходом первого элемента И, шиной "Управление" и первым входом элемента 2-2 И-ИЛИ, вторым выходом анализирующего блока, перваягруппа входов которого соединена ссоответствующими выходами разрядов первого регистра сдвига, вход синхронизации которого соединен с входамисинхронизации второго и третьего регистров сдвига, вторым и четвертымвходами элемента 2-2 И-ИЛИ и вторымвыходом блока управления, третий выход которого соединен с шестым входом блока логической обратной связи,третий; четвертый и пятый входы которого соединены соответственно свыходом последнего разряда первогорегистра сдвига и первым входом второго мажоритарного элемента, с выходом последнего разряда второго регистра сдвига и вторым входом второго мажоритарного элемента, с выходом последнего разряда третьего регистра сдвига и третьим входом второго мажоритарного элемента, первый вход первого мажоритарного элемента соединен с выходом -го разряда второго регистра сдвига, выходы разрядов которого соединены с соответствующими входами второй группы входов анализирующего блока, входы третьей группы входов которого соединены с соответствующими выходами разрядов третьего регистра сдвига, выход д-г( разряда которого соединен с третьим. входом первого мажоритарного элемента, второй вход которого соединен с выходом -го разряда первого регистра сдвига, счетный вход счетчика соединен с выходом элемента 2-2 И-ИЛИ, третий вход которого соединен с первым выходом блока управления и вторым входом второго элемента И, выход которого соединен с вторыми входами элементов И группы элементов. И.2. Генератор по п.1, о т л и ч а ю щ и й с я тем, что блок управления содержит первый, второй и третий элементы НЕ, первый и второй элементы И, элемент ИЛИ, первый и второй одновибраторы, КБ-триггер, элемент З-ЗИ-ИЛИ, первый вход которого является третьим входом блока управления, первый вход которого через первый элемент НЕ соединен с первым входом первого элемента И, второй вход которого соединен с выходом третьего элемента НЕ и вторым входом элемента З-ЗИ-ИЛИ, третий вход которого соединен с первым выходом КБ-триггера, Б-вход которого соединен с выходом первого элемента И и входом первого одновибратора, выход которого соединен с первым входом элемента ИЛИ, второй вход которого является шестым входом блока управления, второй вход которого соединен с четвертым входом элемента З-ЗИ-ИЛИ, пятый вход которого является первым выходом блока управления и соединен с шестым входом элемента З-ЗИ-ИЛИ, третьим входом первого элемента И и вторым выходом КБ-триггера, Р.-вход которого соединен с выходом элемента ИЛИ и входом третьего элемента НЕ, седьмой вход элемента 3-ЗИ-ИЛИ соединен с восьмым входом :этого элемента, четвертым входом бло 12988 ка управления и входом второго элемента НЕ, выход которого соединен с четвертым входом первого. элемента И и первым входом второго элемента И, второй вход которого является седьмым входом блока управления, пятый вход которого соединен с девятым входом элемента З-ЗИ-ИЛИ, выход которого является вторым выходом блока управления, третий выход которого сое- Ю динен с выходом второго одновибратора, вход которого соединен с выходом второго элемента И.3. Генератор по п.1, о т л и ч аю щ и й с я тем, что блок логичес кой обратной связи содержит сумматор по модулю два, первый и второй элементы ИЛИ, элемент "Запрет" и элемент И, первый вход которого соединен с выходом первого элемента ИЛИ, 20 первый, второй и третий входы которого являются соответственно третьим, четвертым и пятым входами блока логической обратной связи, первый и второй входы которого .соединены соответственно с первым и вторым входами сумматора по модулю два, вйход которого соединен с первым входом элемента "Запрет", выход которого соединен с первым входом второго элемента ИЛИ, 3 О выход которого является выходом блока логической обратной связи, шестой, 68 14 вход которого соединен с вторым входом элемента Запрет" н вторым входом элемента И, выход которого соединен с вторым входом второго элемента ИЛИ.4, Генератор по п.1, о т л и ц аю щ и й с я тем, что анализирующийблок содержит первый, второи и третий элементы ИЛИ-НЕ, выходы которых,соединены соответственно с первым,вторым и третьим входами элемента"2 и только 2", первую и вторую схемы сравнения, выходы которых соединены соответственно с первым и вторым входами элемента И, выход которого является первым выходом анализирующего блока, первая группа входовкоторого соединена с входами третьего элемента ИЛИ-НЕ, первой группойвходов первой схемы сравнения и первой группой входов второй схемы сравнения, вторая группа входов которойсоединена с входами второго элементаИЛИ-НЕ и является второй группой входов анализирующего блока, .третьягруппа входов которого соединена свходами первого элемента ИЛИ-НЕ ивторой группой входов первой схемысравнения, выход. элемента "2 и только 2" является вторым выходом анализирующего блока,12988 бй Составитель Ю.,Бу Техред А.Кравчук тров Корректор А. Тяско едактор В.Пет Закаэ 896 5 ПодписноеСССР д.4 твенно-полиграфическое предприятие,г,ужгород,ул.Проектная,4 роиэ Тираж 9 ВНИИПИ Государст по делам иэобр 1 13035, Москва, 2енного комитетатений и открытий

СмотретьЗаявка

3982243, 25.11.1985

Р. А. Церелов, С. С. Белкания и В. Н. Анисимов

ЦЕРЕЛОВ РОБЕРТ АЛЕКСАНДРОВИЧ, БЕЛКАНИЯ СЕВЕРЯН СЕВЕРЯНОВИЧ, АНИСИМОВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 3/84

Метки: генератор, последовательностей, псевдослучайных«

Опубликовано: 23.03.1987

Код ссылки

<a href="https://patents.su/9-1298868-generator-psevdosluchajjnykh-posledovatelnostejj.html" target="_blank" rel="follow" title="База патентов СССР">Генератор псевдослучайных последовательностей</a>

Предыдущий патент: Генератор псевдослучайного импульсного потока

Следующий патент: Программируемый генератор импульсов

Случайный патент: Гаситель крутильных колебаний