Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

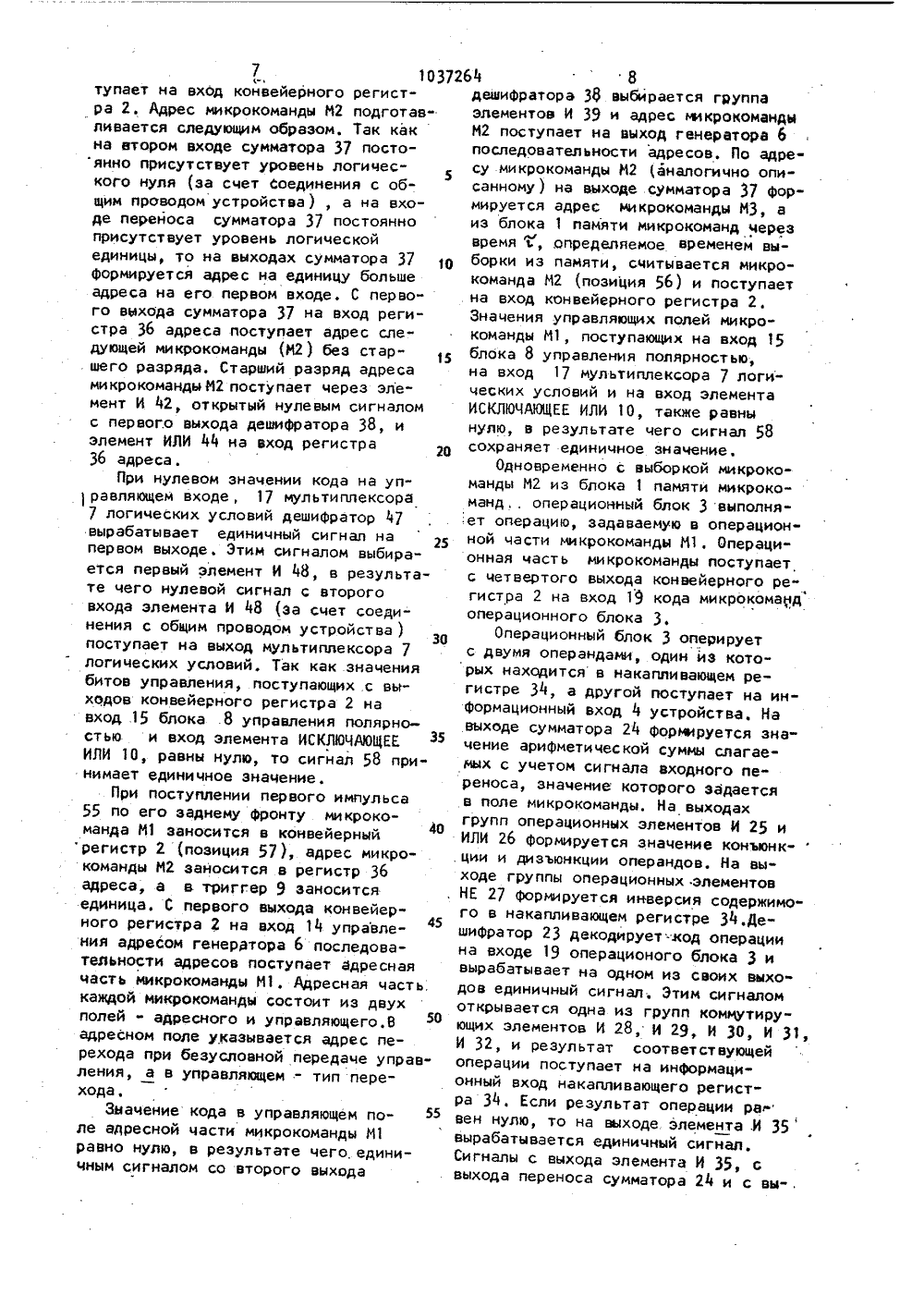

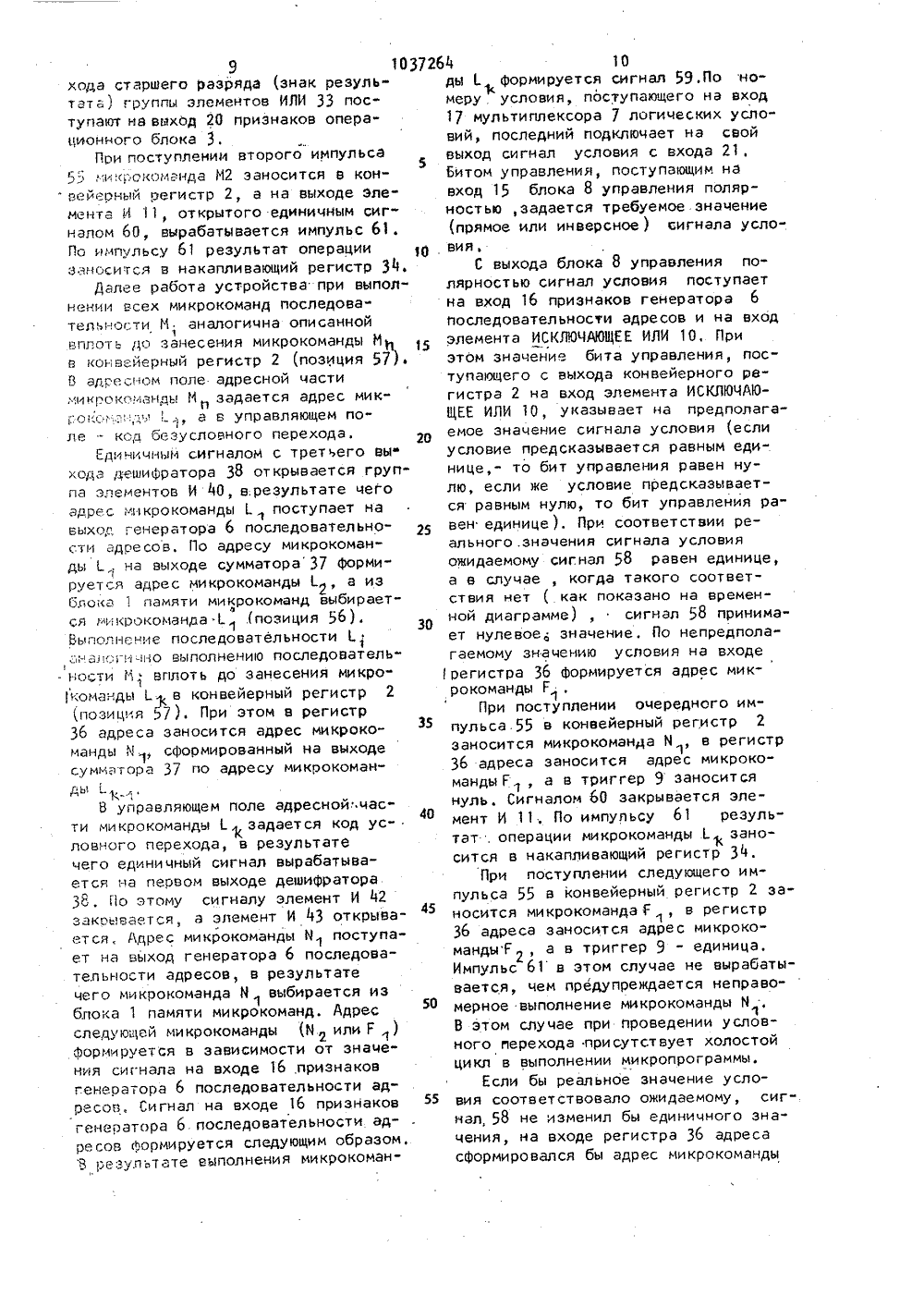

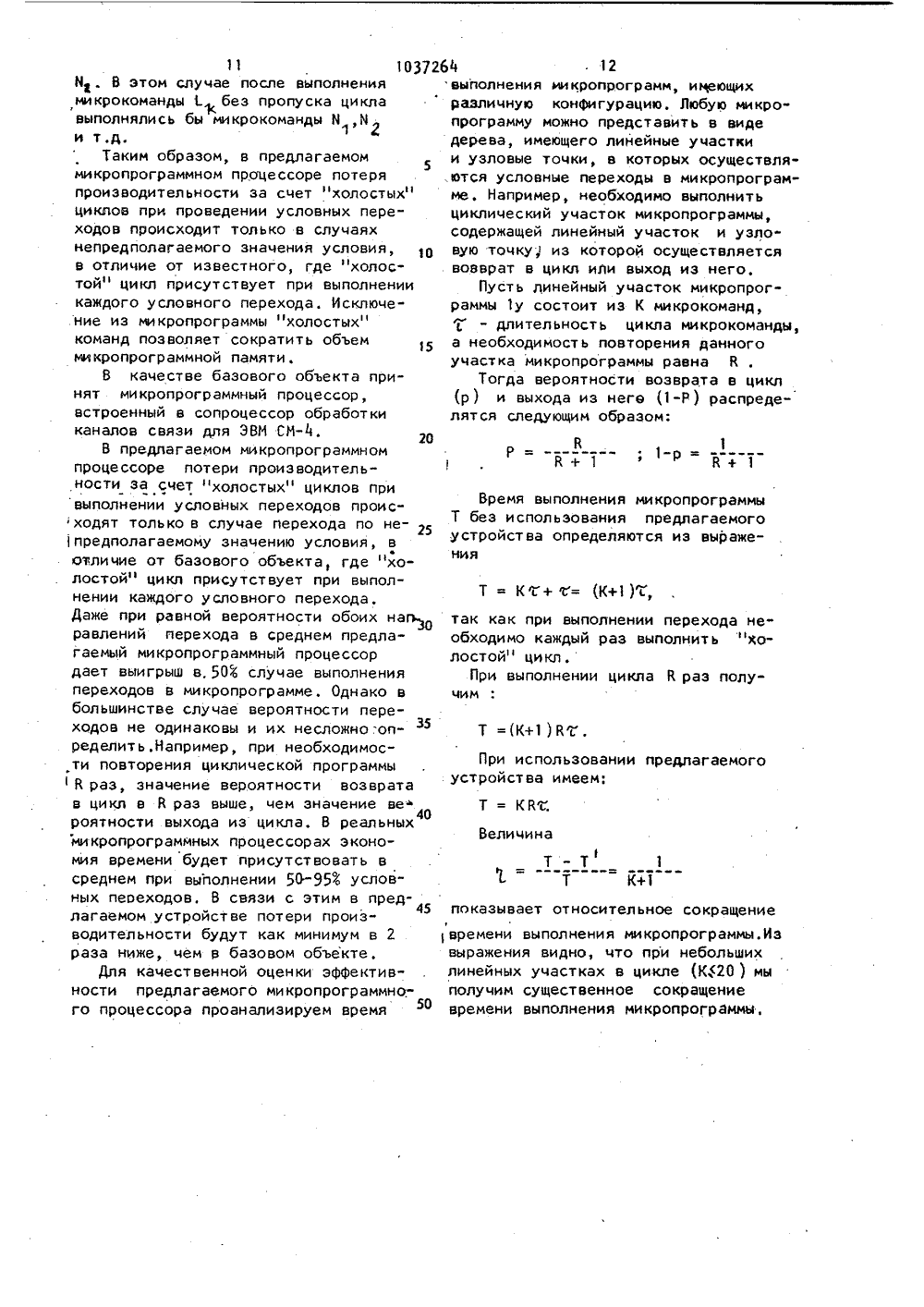

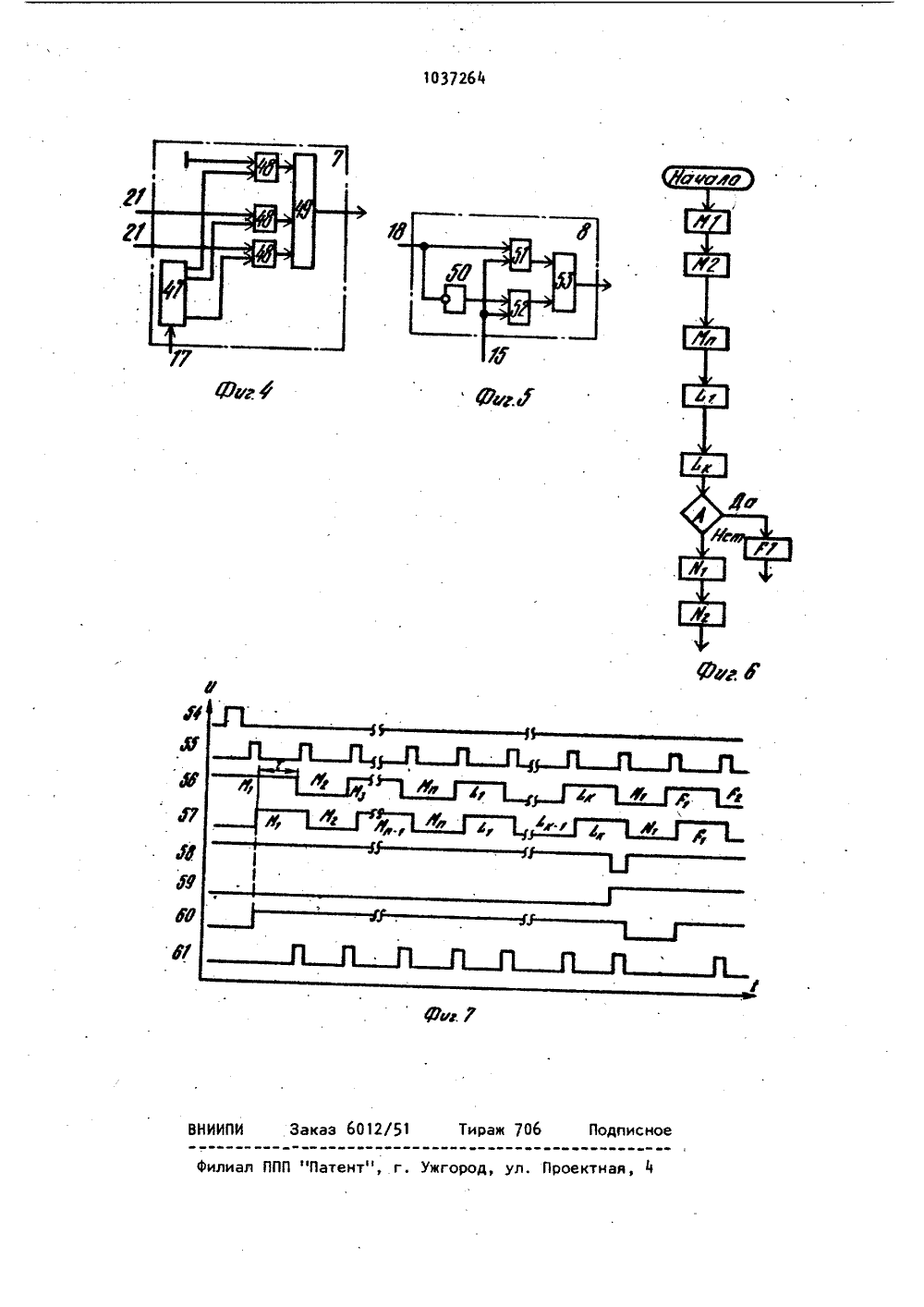

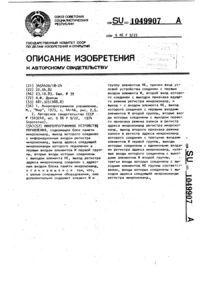

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУ БЛИН ОВ (11) зав О об С 15 ЕТЕНИ И И СТВУ РСКОМУ СВИДЕТ 3425037/1 19.04.82 23,08. 83.А. В, Поло(21 (22 (46 (72 юл. М 31ский и Ю, Я, Пуш ре ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54)(57) МИКРОПРОГРАММНый ПРОЦЕССОР, содержащий блок памяти микрокоманд, конвейерный регистр, операционный блок, информационные вход и выход которого являются соответственно ин-формационными входом и выходом устрой ства, генератор последовательности адресов, мультиплексор. логических условий и блок управления полярностью, выход которого соединен с входом признаков генератора последовательности адресов, выход которого соединен с адресным входом блока, памяти микрокоманд, выход которого соединен с информационным входом конвейерного регистра, первый, второй, третий и четвертый выходы которого со" единены соответственно с входом управления адресом генератора последовательности адресов, с управляющим входом блока управления полярностью, с управляющим входом мульти- плексора логических условий и с входом кода микрокоманд операционного блока, выход признаков которого соединен с информационным входом мультиплексора логических условий, выход которого соединен с информационным входом блока управления полярностью, вход синхронизации генератора последовательности адресов является вхо-е дом синхронизации устройства и соединен с входом занесения конвейерного регистра, о т л и ч а ю щ .и й с я тем, что, с целью повышения произ- водительности, он содержит триггер, а элемент И и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы которого соединены с выходом вы блока управления полярностью и пя- ( тым выходом конвейерного регистра, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ сое-. динен с информационным входом триггера, выход которого соединен с первым , входом элемента И,выход которого сое-. динен с входом синхронизации операционного блока, вход занесения триггера и второй вход элемента И соединены с входом синхронизации устройст ва,1037Изобретение относи тся к вычи слительной технике и может быть использовано для обработки данных в систе"мах управления,Известен микропрограммный процессоР содержащий блок памяти микрокоманд, конвейерный регистр, генератор последовательности адресов, операционный блок и мультиплексор логических условий 1Недостатком данного процессора является низкая производительностьвследствие того, что при выполнениикаждого условного перехода непроизводительно расходуется микрокомандный цикл,Наиболее близким к изобретениюпо технической сущности является микропрограммный процессор, содержащийблок памяти микрокоманд, крнвейерныйрегистр, операционный блок, генераторпоследовательности адресов, мультиплексор логических условий и блокуправления полярностью 2 1.В известном микропрограммном процессоре совмещены в одном микропрограммном цикле выполнение текущей микрокоманды, хранимой на конвейерномрегистре, с выборкой следующей микрокоманды из блока памяти микроко" ЗОманд. Однако при выполнении условных переходов следующая после условного перехода микрокоманда выбирается раньше, чем формируется логичес"кое условие, определяющее направле"ние перехода. Поэтому для каждогоусловного перехода в микропрограминые предусматривается "холостая"микрокоманда, выполняющая функциюзадержки на один цикл, 40ИНаличие холостых" циклов при выпол.нении микропрограммы снижает производительность известного микропрограммного процессора.Кроме того, этот микропрограммный 45процессор имеет большой объем микропрограммной памяти за счет наличия в микропрограмме "холостых"микрокоманд,Целью изобретения является повы- ушение производительности.Поставленная цель достигаетсятем, что микропрограммный процессор,содержащий блок памяти микрокоманд,конвейерный регистр, операционныйблок, информационные вход и выходкоторого являются соответственно информационными входом и выходом уст 26 Й )Аройства, генератор последовательности адресов, мультиплексор логических условий и блок управления полярностью, выход которого соединен свходом признаков генератора последовательности адресов, выход которого соединен с адресным входом блока памяти микрокоманд, выход которого соединен с информационным входом конвейерного регистра, первый, второй, третий и четвертый выходы которого соединены соответственно с входом управления адресом генератора последовательности адресов, с управляющимвходом блока управления полярностью,с управляющим входом мультиплексора логических условий и с входомкода микрокоманд операционного блока,выход признаков которого соединен синформационным входом мультиплексора логических условий, выход которогосоединен с информационным входом блока управления полярностью, входсинхронизации генератора последовательности адресов является входомсинхронизации устройства и соединенс входом занесения конвейерногорегистра, содержит триггер, элементИ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входыкоторого соединены с выходом блокауправления полярностью и пятым выходом конвейерного регистра, выходэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен синформационным входом триггера,выход которого соединен с первым входом элемента И, выход которого соединен с входом синхронизации операционного блока, .вход занесениятриггера и второй вход элемента И соединены с входом синхронизации устройства.При таком решении значение условия предсказывается наперед. Еслиреальное значение условия совпадает с предполагаемым, то условныйпереход выполняется без "холостого"цикла, Если же реальное значениеусловий отличается ат предполагаемого - при выполнении условного перехода присутствует "холостой" цикл,Сокращение "холостых" циклов приработе устройства повышает его производительность.Кроме того, при таком решенииотпадает необходимость в использовании "холостых" микрокоманд,вследствие чего сокращается объем микропрограммной памяти устройства.2644 6 последовательности адресов и с 3 1037На Фиг. 1 представлена схема предлагаемого процессора; на фиг. 2 схема операционного блока; на Фиг,3 схема генератора последовательностейадресов; на.фиг. 4 - схема мультиплексора логическихусловий; на5.Фиг, 5.- схема блока управления полярностью; на фиг. б- алгоритмы микропрограммы; на фиг. 7- временнаядиаграмма работы устройства.10Иикропрограммный процессор содержит. блок 1 памяти микрокоманд,конвейерный регистр 2, операционный блок3, информационные вход 4 и выход 5 которого являются соответственноинформационными входом и выходомустройства, генератор 6 последовательности адресов, мультиплексор 7логических условий, блок 8 управления полярностью, триггер 9,элементИСКЛЮЧАЮЩЕЕ ИЛИ 10, элемент И 11, атакже входы 12 синхронизации и 13 начальной установки устройства,Выход блока 1 памяти микрокомандсоеДинен с информационным входом кон25вейерного регистра 2, первый входкоторого соединен с входом 14 управления адресом генератора 6 последовательности .адресов,Второй выход конвейерного регист 30ра 2 соединен с управляющим входом15 блока 8 управления полярностью,выход которого соединен с входом 16признаков генератора 6 йоследовательности адресов и с входом элементаИСКЛЮЧАЮЩЕЕ ИЛИ 10. Третий выходконвейерного регистра 2 соединен с управляющим входом 17 мультиплексора 7логических условий, выход которогосоединен с информационным входом 18блока управления полярностью. Четвер 40.тый выход конвейерного регистра 2соединен с .входом 19 кода микрокоманд операционного блока 3,. выход.20признаков которого соединен с информационным входом 21, мультиплексора7 логических условий, Пятый выход конвейерного регистра 2 соединен с входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, выход которого соединен с информационным входом триггера 9.50Выход генератора 6 последовательности адресов соединен с адреснымвходом блока 1 памяти микрокоманд. Выход триггера 9 соединен с,первымвходом элемента И 11, второй вход которого соединен с входами занесенияконвейерного регистра 2 и - .1 ггера 9,с входом синхронизации генератора входом 12 синхронизации устройства,Выход элемента И 11 соединен с входом 22 синхронизации операционного блока 3. Установочные входы конвейерного регистра 2, генератора 6последовательности адресов и триггера 9 соединены с входом 13 начальнойустановки устройства.Операционный блок 3 (фиг.2) содержит дешифратор 23 операций, сумма"тор 24, группы операционных элементовИ 25, ИЛИ 26, и НЕ 27, группы коммутирующих элементов И 28, И 29, И 30,И 31, И 32, группу элементов ИЛИ 33,накапливающий регистр 34 и элементИ 35,Вход деюифратора 23 операций ивход переноса сумматора 24 соедине"ны с входом 19 кода микрокомандоперационного блока 3. Выходы дешифратора 23 операций соединены с входами групп комчутирующих элементовИ 28, И 29, И 30, И 31, И 32, выходыкоторых .соединены с.,входами группй злементов ИЛИ 33, Выход группы элементов ИЛИ 33 соединен с информационным входом накапливающего регистра34 и с входом элемента И 35, Входзанесения накапливающего регистра34 является входом 22 синхронизации операционного блока 3. Выход накапливающего регистра 34 являетсяинформационным выходом 5 устройстваи соединен с первыми входами сумматора 24, групп операционных элементовИ 25, ИЛИ 26 и с входом группы опера"ционных элементов НЕ 27. Вторые входы сумматора 24, группоперационных элементов, И 25, ИЛИ 26и вход группы коммутирующих элементовИ "31 соединены с информационнымвходом 4 устройства. Выходы сумматора 24,групп операционных элементовИ 25, ИЛИ 26, НЕ 27 соединены с входами коммутирующих элементов И 28,И 29, И 30, И 32 соответственно,Выход переноса сумматора 24, выходстаршего разряда группы элементовИЛИ 33 и выход элемента И 35 являются выходом 20 признаков операционного блока 3,Генератор 6 последовательности адресов (фиг.3 ) содержит регистр 36адреса, сумматор 37, дешифратор 38,группы элементов И 39, И 40. и ИЛИ 41,элементы И 42, И 43, ЙЛИ 44, ИЛИ 45и НЕ 46,Выход регистра 36 адреса соединен с входом группы элементов И 39,выход которой совдинен с входом груп"пы элементов ИЛИ 41, Выход группыэлементов ИЛИ 41 является выходомгенератора 6 последовательности ад"ресов и соединен с первым входомсумматора 37, второй вход которогосоединен с входом элемента НЕ 46 иобщим проводом устройства. Выход эле" Омента НЕ 46 соединен с входом переноса сумматора 37, первый и второйвыходы которого соединены соответст"венно с первым информационныи входомрегистра 36 адреса и входом элемента И 42, Вход дешифратора 38 и входгруппы элементов И 40 являются входом14 управления адресом генератора 6последовательности адресов,20 Первый выход дешифратора 38 соединен с входами элементов И 43,ИЛИ 45 и с инверсным входом элементаИ 42, выход которого соединен с входом элемента ИЛИ 44. Второй выходдещифратора 38 соединен с входом элемента ИЛИ 45, выход которого соединен с входом группы элементов И 39,Третий выход дешифратора 38 соединенс входом группы элементов И 40, выход которой соединен с входом группы элементов ИЛИ 41, Вход элементаИ 43 является входом 16 признаковгенератора 6 последовательности адресов, Выход элемента И 43 соединен,через элемент ИЛИ 44 с вторым ин 35формационным входом регистра 36 адреса, входы занесения и адреса которого являются, соответственно входом 2 синхронизации и входом 13 на 40чальной установки устройства,. Мультиплексор 7 логических условий (Фиг,4) содержит дешифратор 47,группу элементов И 48 и элемент ИЛИ 49Вход дещифратора 47 является вхо дом 17 мультиплексора 7 логических условий, Выходы дешифратора 47-,соединены с первыми входами элементов И группы элементов И 48, выходы которых через элемент ИЛИ 49 соединены с 50 выходом мультиплексора 7 логических условий, Второй вход первого элемента И группы элементов И 48.соединен с общим проводом устройства, Вторые входыостальных элементов И группы элемен- .55 тов И 48 являются информационным входом 21 мультиплексора 7 логических условий.1037264 ЬБлок 8 управления полярностью(Фиг,5 ) содержит элементы НЕ 50,И,51,И 52, и ИЛИ 53.Входы элементов НЕ 50 и И 5, соединены с информационным входом 16 блока8 управления полярностью. Выход элемента НЕ 50 соединен с входом элемента И 52, инверсныйвход которогосоединен с входом элемента И 51 и суправляющим входом 15 блока 8 управления полярностью. Выходы элементовИ 51 и И 52 соединены с входами эле"мента ИЛИ 53, выход которого является выходом блока 8 управления полярэостью,На фиг, 6 показан алгоритм микропрограммы, где символами И .,М 1,Г (1= 1,2,3пМ ) обозначейы последовательности микрокоманд,асимволом А - проверяемое логическоеусловие.На фиг. 7 показана временная диаграмма работы устройства, где: 54 сигнал начальной установки на входе 13; 55- импульсы на входе 2 синх,ронизации; 56 - коды микрокомандна выходе блока 1 памяти микрокоманд; 57 - коды микрокоманд на выхо"де конвейерного регистра 2; 58- сиг;нал на выходе элемента ИСКЛЮЧАЮЩЕЕИЛИ 10;59 -сигнал условия на выходе20 признаков генератора 6 последовательности адресов; 60- сигнал навыходе триггера 9; 61 - импулвс навыходе элемента И 11,Для более четкого понимания работы устройства рассмотрим выполнениеим примера микропрограммы, алгоритмкоторой показан на Фиг.б.Работа устройства производитсяв соответствии с временной диаграммой (Фиг.7).На вход 13 устройства подаетсясигнал 54, по которому конвейерныйрегистр 2, триггер 9 и регистр 36адреса устанавливаются в нуль.По нулевому коду на входе 14 генератора 6 последовательности адресов дешифратор 38 вырабатывает единичный сигнал на своем втором выходе. Этим сигналом через элементИЛИ 45 выбирается группа элементовИ 39, в результате чего нулевойадрес с выхода регистра 36 адресапередается на выход генератора6 последовательности адресов,йо нулевому адресу из блока 1 памяти микрокоманд выбирается перваямикрокоманда И (позиция 56 ) и пос40 7. 10372 тупает на вход конвейерного регистра 2, Адрес микрокоманды М 2 подготавливается следующим образом. Так как на втором входе сумматора 37 постоянно присутствует уровень логичес 5 кого нуля (за счет Соединения с общим проводом устройства ), а на входе переноса сумматора 37 постоянно присутствует уровень логической единицы, то на выходах сумматора 37 формируется адрес на единицу больше адреса на его первом входе. С первого выхода сумматора 37 на вход регистра 36 адреса поступает адрес следующей микрокоманды (М 2 ) без старшего разряда. Старший разряд адреса микрокоманды М 2 поступает через элемент И 42, открытый нулевым сигналом с первого выхода дешифратора 38, и элемент ИЛИ 44 на вход регистра 36 адреса.При нулевом значении кода на уп равляющем входе, 17 мультиплексора 7 логических условий дешифратор 47 вырабатывает единичный сигнал напервом выходе . Этим сигналом выбирается первый элемент И 48, в результате чего нулевой сигнал с второговхода элемента И 48 (за счет соединения с общим проводом устройства )30поступает на выход мультиплексора 7 логических условий, Так как значения битов управления, поступающих .с выходов конвейерного регистра 2 на вход 15 блока .8 управления полярностью и вход элемента ИСКЛЮЧАЮЩЕЕИЛИ 10, равны нулю, то сигнал 58 принимает единичное значение.При поступлении первого импульса 55 по его заднему Фронту микрокоманда М 1 заносится в конвейерный регистр 2 (позиция 57 ), адрес микрокоманды М 2 заносится в регистр 36 адреса, а в триггер 9 заносится единица. С первого выхода конвейерного регистра 2 на вход 14 управления адресом генератора 6 последовательности адресов поступает адреснаячасть микрокоманды М 1, Адресная часть.каждой микрокоманды состоит из двухполей - адресного и управляющего.8адресном поле указывается адрес перехода при безусловной передаче управления, а в управляющем - тип перехода,Значение кода в управляющем поле адресной части микрокоманды М 1равно нулю, в результате чего, единичным сигналом со второго выхода 64 8дешифратора 38 выбирается группаэлементов И 39 и адрес микрокомандыМ 2 поступает на выход генератора 6последовательности адресов, По адресу микрокоманды И 2 (аналогично описанному ) на выходе сумматора 37 Формируется адрес микрокоманды М 3, аиз блока 1 памяти микрокоманд черезвремя ь, апределяемое временем выборки из памяти, считывается микрокоманда М 2 (позиция 56) и поступает. на вход конвейерного регистра 2,Значения управляющих полей микро"команды М 1, поступаоцих на вход 15блока 8 управления полярностью,на вход 17 мультиплексора 7 логических условий и на вход элементаИСКЛЮЧАЮЩЕЕ ИЛИ 1 О, также равнынулю, в результате чего сигнал 58сохраняет единичное значение,Одновременно с выборкой микрокомэнды М 2 из блока 1 памяти микрокоманд операционный блок 3 выполняет операцию, задаваемую в операционной части микрокоманды М 1Операционная часть микрокоманды поступаетс четвертого выхода конвейерного регистра 2 на вход 19 кода микрокомандоперационного блока 3.Операционный блок 3 оперируетс двумя операндами, один из которых находится в накапливающем регистре 34, а другой поступает на информационный вход 4 устройства. Навыходе сумматора 24 Формируется зна"чение арифметической суммы слагаемых с учетом сигнала входного переноса, значение которого задаетсяв поле микрокоманды. На выходахгрупп операционных элементов И 25 иИЛИ 26 формируется значение конъюнк-ции и дизьюнкции операндов, На выходе группы операционных элементовНЕ 27 формируется инверсия содержимого в накапливающем регистре 34,ДешиФратор 23 декодирует-мод операциина входе 19 операционого блока 3 ивырабатывает на одном из своих выходов единичный сигнал. Этим сигналомоткрывается одна из групп коммутирующих элементов И 28, И 29, И 30, И 31,И 32, и результат соответствующейоперации поступает на информаци"онный вход накапливающего регистра 34, Если результат операции равен нулю, то на выходе элемента И 35вырабатывается единичный сигнал .Сигналы с выхода элемента И 35, свыхода переноса сумматора 24 и с вы-, 1037261 10хода старшего разряда (знак результата) группы элементов ИЛИ 33 поступают нв выход 20 признаков операционного блока 3.При поступлении второго импульса55, и,;акоманда М 2 заносится в конвейерный регистр 2, а на выходе эле"мента И 1 открытого единичным сиг"налом 60, вырабатывается импульс 61.По импульсу б результат операциизаносится в накапливающий регистр 31.Далее работа устройства при выполнении всех микрокоманд последова"тельности М; аналогична описаннойвпготь до занесения микрокоманды М 11в конвейерный регистр 2 (позиция 57)О адресном поле адресной частимикрокоманды М задается адрес мик:,о,:с г-,:, ., а в управляющем поле - коц безусловного перехода.Единичным сигналом с третьего вы"хода дешифратора 38 открывается группа элементов И М 0, в.результате чегоадрес мнкрокоманды . поступает навыход генератора 6 последовательности адресов, По адресу микрокомандына выходе сумматора 37 формируется адрес микрокоманды 2, а изблока 1 памяти микрокоманд выбирает"лся микрокоманда , .позиция 56),Выполнение последовательности . ;:на: оги-,но выполнению последователь" - ности Мвплоть до занесения микрокоманды . 1, в конвейерный регистр 2(позиц, я 57 ). При этом в регистр36 адреса заносится адрес микрокоманды Мсформированный на выходесумматора 37 по адресу микрокоманды "1, .В управляющем поле адресной части микрокомандызадается код ус- .ловного перехода, в результате чего единичный сигнал вырабатывается на первом выходе дешифратора38, По этому сигналу элемент И 12 закрывается, а элемент И 3 открывается, Адрес микрокоманды й поступает на выход генератора б последовательности адресов, в результатечего микрокоманда й 1 выбирается изблока 1 памяти микрокоманд. Адресследующей микрокоманды (Иили Г 1) формируется в зависимости от значения сигнала на входе 16,признаков генератора 6 последовательности адресов, гигнал на входе 16 признаков генератора 6 последовательности адресов формируется следующим образом. В результате выполнения микрокоман регистра 36 формируется адрес микрокоманды ГПри поступлении очередного импульса.55 в конвейерный регистр 2 заносится микрокоманда М, в регистр 36 адреса заносится адрес микрокоманды Г, а в триггер 9 заносится нуль. Сигналом 60 закрывается элемент И 11, По импульсу 61 результат . операции микрокоманды .,1, заносится в накапливающий регистр 31,При поступлении следующего импульса 55 в конвейерный регистр 2 заносится микрокоманда Г , в регистр 36 адреса заносится адрес микрокомандыГ 2, а в триггер 9 - единица. Импульс 61 в этом случае не вырабатывается, чем предупреждается неправомерное выполнение микрокоманды М, В этом случае при проведении условного перехода присутствует холостой цикл в выполнении микропрограммы.Если бы реальное значение условия соответствовало ожидаемому, сиг"нал, 58 не изменил бы единичного значения, на входе регистра 36 адресасформировался бы адрес микрокоманды 35 40 45 50 55 ды . формируется сигнал 59.По номеру условия, поступающего на вход17 мультиплексора 7 логических условий, последний подключает на свойвыход сигнал условия с входа 21,Битом управления, поступающим навход 15 блока 8 управления полярностью ,задается требуемое значение(прямое или инверсное) сигнала усло вия зС выхода блока 8 управления полярностью сигнал условия поступаетна вход 16 признаков генератора 6последовательности адресов и на входэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, Приэтом значение бита управления, поступающего с выхода конвейерного регистра 2 на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10, указывает на предполагаемое значение сигнала условия (еслиусловие предсказывается равным единице,- то бит управления равен нулю, если же условие предсказывается равным нулю, то бит управления равен единице). При соответствии реального .значения сигнала условияожидаемому сиг.нал 58 равен единице,а в случае , когда такого соответствия нет ( как показано на временной диаграмме) , сигнал 58 принимает нулевое, значение, По непредполагаемому значению условия на входе11 10372й. В этом случае после выполнениямикрокоманды 1.без пропуска циклавыполнялись бы микрокоманды й ,й1и т.д,Таким образом, в предлагаемоммикропрограммном процессоре потеряпроизводительности за счет "холостых"циклов при проведении условных переходов происходит только в случаяхнепредполагаемого значения условия,в отличие от известного, где "холостой" цикл присутствует при выполнениикаждого условного перехода. Исключение из микропрограммы "холостых"команд позволяет сократить объеммикропрограммной памяти.В качестве базового объекта принят микропрограммный процессор,встроенный в сопроцессор обработкиканалов связи для ЭВИ СИ-ч.В предлагаемом микропрограммномпроцессоре потери производительности за счет "холостых" циклов привыполнении условных переходов происходят только в случае перехода по не1 предполагаемому значению условия, вотличие от базового объекта, где "холостой" цикл присутствует при выполнении каждого условного перехода.Даже при равной вероятности обоих наъравлений перехода в среднем предлагаемый микропрограммный процессордает выигрыш в. 504 случае выполненияпереходов в микропрограмме. Однако вбольшинстве случае вероятности переходов не одинаковы и их несложноопределить.Например, при необходимости повторения циклической программыВ раз, значение вероятности возвратав цикл в В раэ выше, чем значение ве40роятности выхода из цикла. В реальныхмикропрограммных процессорах экономия времени будет присутствовать всреднем при выполнении 50-95 условных переходов. В связи с этим в пред 45лагаемом устройстве потери производительности будут как минимум в 2раза ниже, чем в базовом объекте,Для качественной оценки зфФективности предлагаемого микропрограммно;го процессора проанализируем время 6 ч 12выполнения микропрограмм, имеющих различную конфигурацию, Любую микропрограмму можно представить в виде дерева, имеющего линейные участки и узловые точки, в которых осуществля,ются условные переходы в микропрограмме, Например, необходимо выполнить циклический участок микропрограммы, содержащей линейный участок и узловую точку из которой осуществляется возврат в цикл или выход иэ него,Пусть линейный участок микропрограммы 1 у состоит из К микрокоманд,- длительность цикла микрокоманды, а необходимость повторения данного участка микропрограммы равна В ,Тогда вероятности возврата в цикл(р ) и выхода из неге (1-Р ) распределятся следующим образом: Время вы полнения микропрограммы Т без использования предлагаемого устройства определяются иэ выраже- ния так как при выполнении перехода не" обходимо каждый раз выполнить "холостои" цикл .При выполнении цикла В раз полу- чим При использовании предлагаемогоустройства имеем; показывает относительное сокращение1 времени выполнения микропрограммы.Иэвыражения видно, что при небольшихлинейных участках в цикле (К 20) мыполучим существенное сокращениевремени выполнения микропрограммы, 103726 й

СмотретьЗаявка

3425037, 19.04.1982

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ ЦЕНТРАЛЬНОГО НАУЧНО ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ, ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропрограммный, процессор

Опубликовано: 23.08.1983

Код ссылки

<a href="https://patents.su/9-1037264-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Микропроцессор

Следующий патент: Устройство для моделирования процесса обслуживания заявок

Случайный патент: Листоподборочная машина