Микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

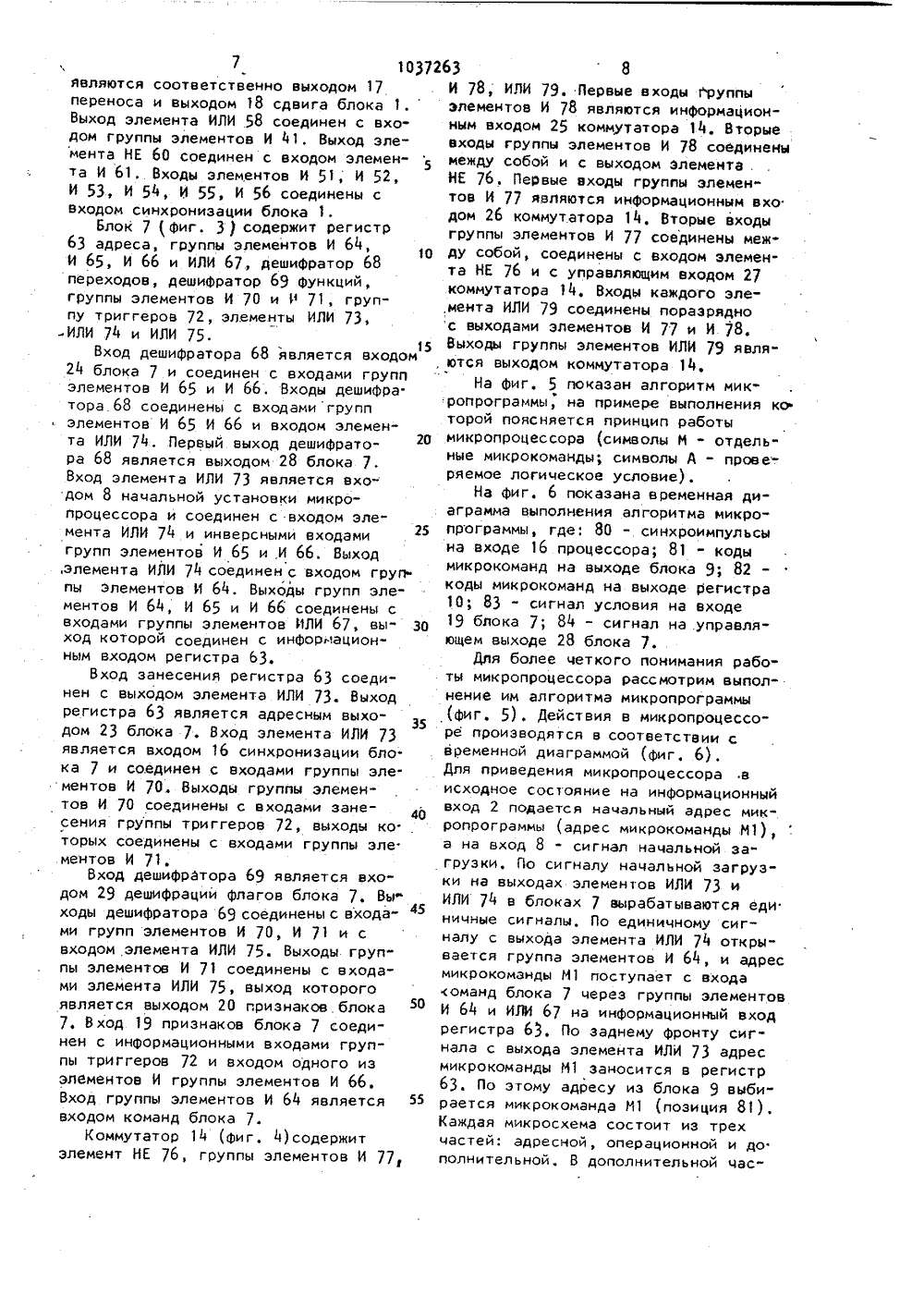

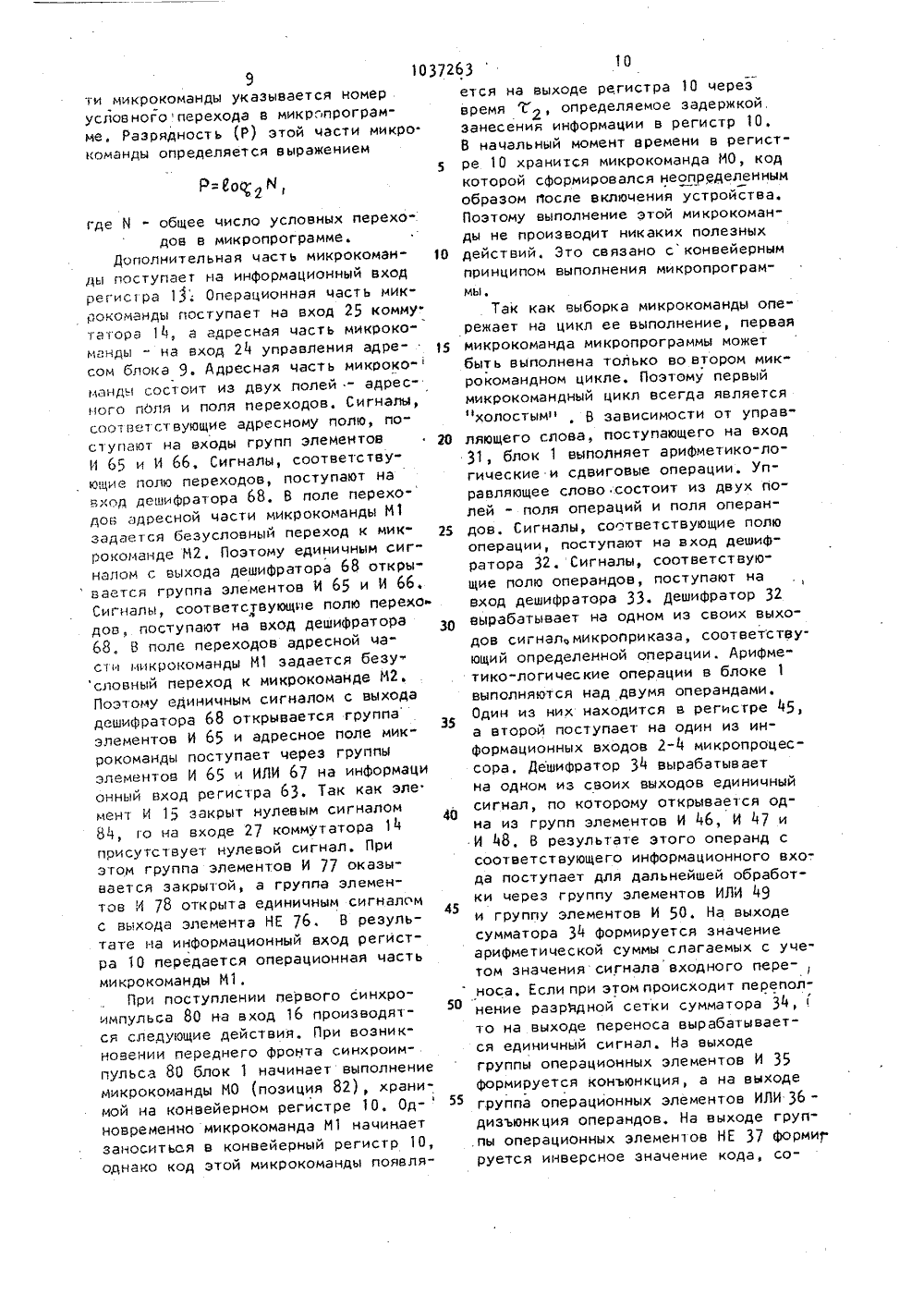

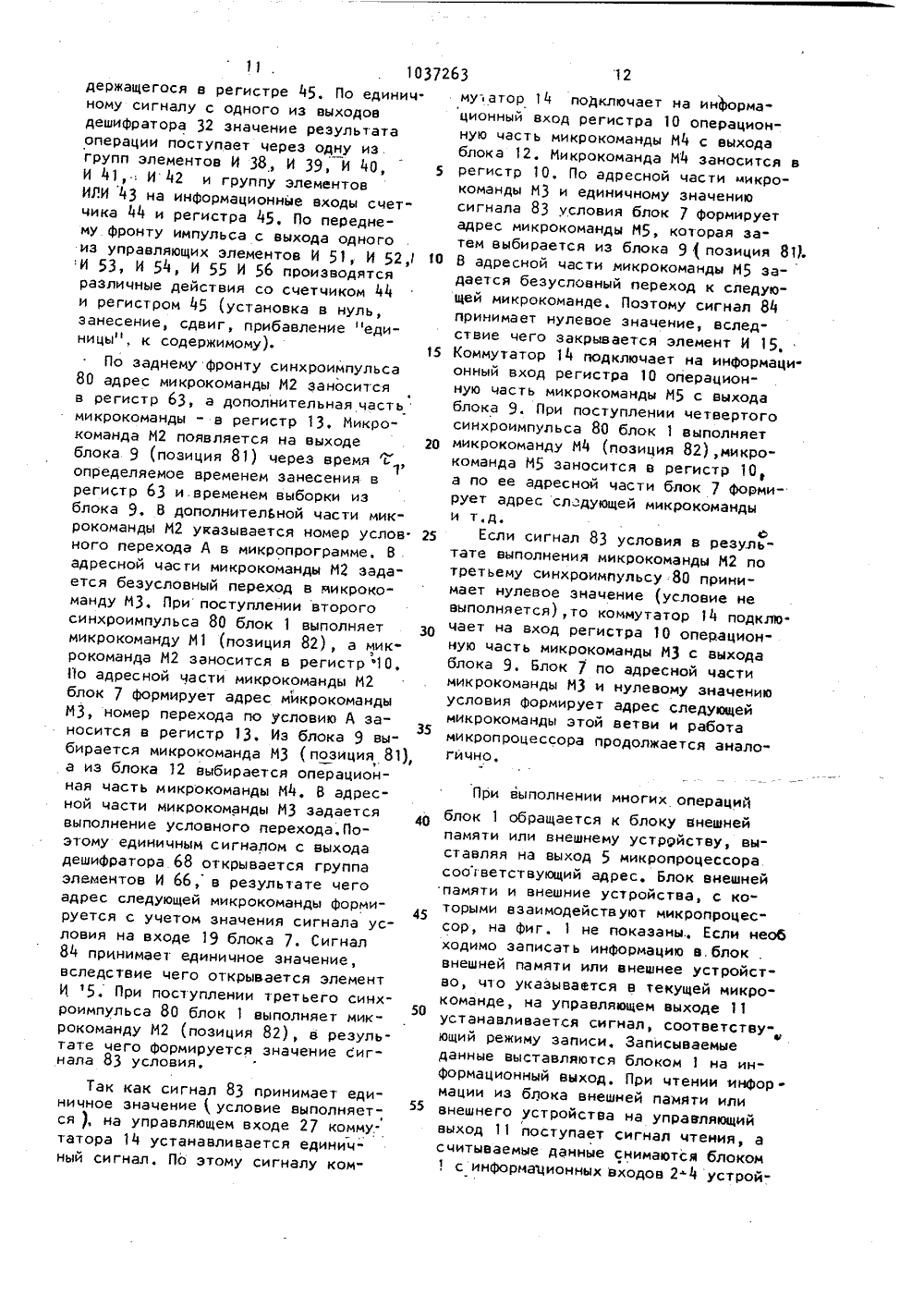

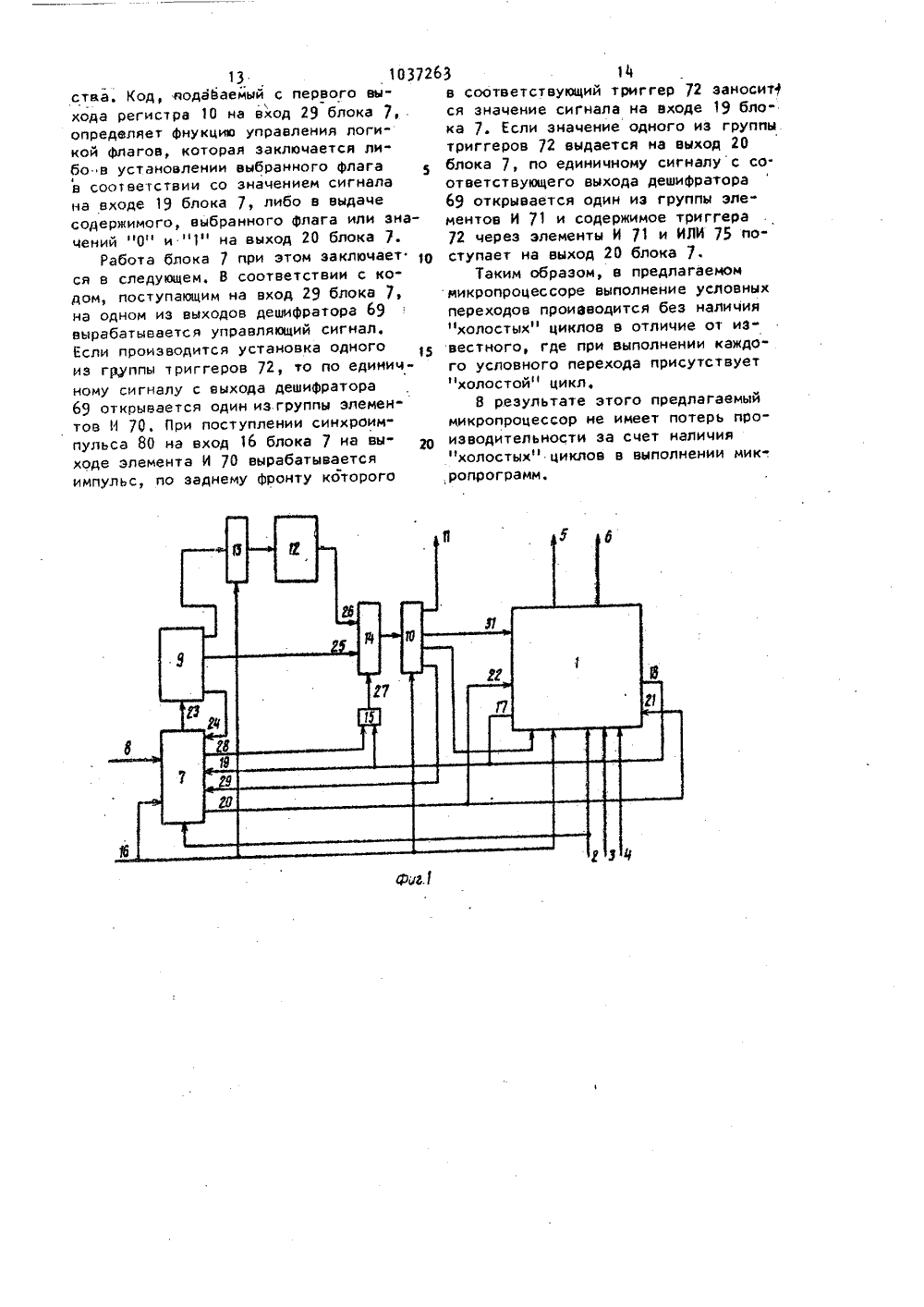

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСН ИХРЕСПУБЛИК 801037263 А ГОСУД АРСТВЕННЫИПо ДЕЛАМ ИЗОБ ОМИТЕТ СС ТЕНИЙ И ОТНРЫТИ(56) . Авторское свидетельство СССРИ 746532, кл. 6 06 Г 15/00, 1980.2. Прангишвили И.В Иикропроцес- лсоры и микро-ЭВМ. М., "Энергия",о1979, с. 9 (прототип). р(54)(57) 1. МИКРОПРОЦЕССОР, содержащий блок обработки данных, блок микропрограммного управления, блок ммикропрограммной памяти и конвейер- иный регистр, синхровход, первый, вто ррой, третий и четвертый выходы ко- рторого соединены соответственно ссинхровходом и управляющим выходом ммикропроцессора, входом кода микрокоманды и входом маскирования блокаобработки данных и входом дешифрации,.флагов блока микропрограммного управ дления, вход начальной установки, адресный выход, .вход управления пере"ходами, вход признаков, выход признаков, синхровход и информационныйбвход блока микропрограммного управления подключены соответственно квходу и первому выходу блока микропрограммной памяти, выходу переноса ли входу переноса блока обработки дан.ных,.синхровходу и информационномужвходу микропроцессора, синхровход,информационный вход, информационныйвыход, адресный выход, вход сдвигаи ОПИСАНИЕ ИЗОБРЕ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ и выход сдвига блока обработки данных соединены соответственно с синхровходом, информационным входом, информационным выходом и адреснымыходом микропроцессора, выходом признаков и входом признаков блока микропрограммного управления,. о тл и ч а ю щ и й с я тем, что, с цвыл повышения производительности,. н содержит блок памяти переходов, егистр номера перехода, коммутатор элемент И, первый и второй входы выход которого подключены соответтвенно к управляющему выходу блока икропрограммного управления, выходу ереноса блока микропрограммного уп-авления, выходу переноса блока об" аботки данных и управляющему входу оммутатора, первый и второй инфор" ационные входы и выход коммутатора оединены соответственно с вторым выодом блока микропрограммной памяти, с: ыходом блока памяти переходов, вхо" ом конвейерного регистра, а информа ионный вход, синхровход и выход реистра номера перехода подключены " :М оответственно к третьему выходу ф 3 лока микропрограммной памяти, синх 3 Я овходу микропроцессора и адресному 45 ходу блока памяти переходов.2. Микропроцессор по и. 1, о ти ч а ю щ и й с я тем, что, блок микропрограммного управления содерит регистр адреса, дешифратор Функий, пять групп элементов И, группу триггеров, три элемента ИЛИ групу элементов ИЛИ и дешифратор переходов, первый и вторЬй входы и выход первого элемента ИЛИ соединены соот" ветственно с входом начальной установки и синхровходом блока и синхрор Л.Бокша Ко ед Тираж 706И Государственног делам изобретений 1 осква, Ж, Рау аз 6012/5 НИИП л ППП "Патент Ужгород ул Прое Подписноета СССРьт иЙ1037263 входом регистра адреса, первый, второй и третий входы .и выхсд элементовИЛИ группы подключены соответственно к выходам элементов И первой, второй и третьей групп и информационному входу регистра адреса, выход которого соединен с адресным выходомблока, вход, первый, второй и третийвыходы дешифратора переходов подключены соответственн. к входу управления переходами блока, первомувходу второго элемента ИЛИ и первымвходам элементов И второй и третьейгрупп, вторые входы которых соединены с входом управления переходамблока, третий вход элементов И тре"тьей группы подключен к входу признаков блока, а третий выход дешифратора переходов соединен с управляющим выходом блока, второй вход второго элемента ИЛИ и инверсные входыэлементов И второй и третьей групп Изобретение относится к вычислительной технике и может быть использовано для обработки данных в системах управления,Известен микропроцессор, содержа"щий центральный блок обработки данных, блок микропрограммного управле.ния, блок микропрограммной памяти,конвейерный регистр, два регистра иэлемент НЕ1 1,Недостатком данного микропроцессора является низкая производительность вследствие того, что при выполнении каждого условного перехода непроизводительно тратится одинмикрокомандный цикл,1Наиболее близким к изобретениюпо технической сущности является микропроцессор, содержащий центральныйблок обработки данных, блок микропрограммного управления, конвейерныйрегистр и блок микропрограммной памяти28 известном микропроцессоре используется конвейерный принцип выполнения микрокоманд, который заключается в том, что в одном микрокомандном цикле одновременно с выполнением текушей микрокоманды, находящей-,5 10 15 25 подключены к входу начальной установки блока, а первый и второй входыэлементов И первой группы соединенысоответственно с информационным входом блока и выходом второго элемента ИЛИ, информационные входы, синхровходы и выходы триггеров группыподключены соответственно к входупризнаков блока, выходам соответствующих элементов И четвертой группысоединены с синхровходом блока, входи выходы дешифратора функций подключены соответственно к входу дешифрации флагов блока и вторым входамсоответствующих элементов И четвертой и пятой групп, входы третьегоэлемента ИЛИ соединены с одним извыходов дешифратора функций и выходами элементов И пятой группы, авыход третьего элемента ИЛИ подключен к выходу признаков блокася на конвейерном регистре, производится выборка следующей микрокоманды, При этом выборка микрокоманды опережает на цикл ее выполнение. Однако при выполнении условных переходов следующая после условного перехода микрокоманда выбирается раньше, чем формируется логическое условие, определяющее направление перехода, Поэтому при каждом условном переходе в микропрограмме предусматривается "холостая" микрокоманда, выполняющая функцию задержки на одии цикл, Наличие "холостых" циклов при выполнении микропрограмм снижает про изводительность микропроцессора,Цель изобретения - повышение производительности.ЛЦель достигается тем, что микропроцессор, содержащий блок обработки данных, блок микропрограммного управления, блок микропрограммной памяти и конвейерный регистр, синхровход, первый, второй, третий и четвертый выходы которого соединены соответственно с синхровходом и управляющим выходом микропроцессора, входом кода микрокоманды и входом маскирования блока обработки данных и вхо3 03726дом дешифрации флагов блока микропрограммного управления, вход начальной установки, адресный выход,вход уяравления переходами, входпризнаков, выход признаков, синхровход и информационный вход блокамикропрограммного управления подключены соответственно к входу и пер"вому выходу блока микропрограммнойпамяти, выходу переноса и входу пере Оноса блока обработки данных синхровходу и информационному входу микропроцессора, синхровход, информационный вход, информационный выход,адресный выход, вход сдвига и выходсдвига блока обработки данных соединены соответственно с синхровходом,информационным входом, информационным выходом и адресным выходом микропроцессора, выходом признаков ивходом признаков блока микропрограммного управления, содержит блок памяти переходов, регистр номера перехода, коммутатор и элемент И, первыйи второи входы и вод которого подключены соответственно к управляющему выходу блока микропрограммногоуправления, выходу переноса блокамикропрограммного управления, выходу переноса блока обработки данныхи управляющему входу коммутатора,первый и второй информационные в%одыи выход коммутатора соединены соот- .ветственно с вторым выходом блокамикропрограммной памяти, выходом бло.ка памяти переходов, входом конвейер.ного регистра, а информационный вход,синхровход и выход регистра номераперехода подключены соответственнок третьему выходу блока микропрограммной памяти синхровходу микропроцессора и адресному входу блока памятипереходов,Кроме того,блок микропрограммного управления содержит регистр адреса, дешифратор функций, пять группэлементов И, группу триггеров, триэлемента .ИЛИ, группу элементов ИЛИ, и дешифратор переходов, первый и вто.рой входы и выход первого элементаИЛИ соединены соответственно с входом .начальной, установки и синхровходом блока и синхровходом регистра адреса, первый, второй и третий входыи выход элементов ИЛИ группы подклю-,, чены соответственно к выходам элемен 55тов И первой, второй и третьей группи информационному входу регистра адреса, выход которого соединен с ад 3 4ресным выходом блока, вход, первыйвторой .и третий выходы дешифраторапереходов подключены соответственнок входу управления переходами блока,первому входу второго элемента ИЛИи первым входам элементов И второйи третьей групп, вторые входы которых соединены с входом управления переходами блока, третий вход элементов,И третьей группы подключен к входупризнаков блока, а третий выход де"шифратора переходов соединен с уп"равляющим выходом блока, второй вход.второго элемента ИЛИ и инверсныевходы элементов И второй и третьейгрупп подключены к входу начальнойустановки блока, а первый и второйвходы элементов И первой группы соединены соответственно с информацион"ным входом блока и выходом второгоэлемента ИЛИ, информационные входысинхровходы и выходы триггеров группы подключены соответственно к входупризнаков блока, выходам соответствующих элементов И четвертой группыи соединены с синхровходом блока,вход и выходы дешифратора Функцийподключены соответственно к входудешифрации флагов блока и вторымвходам соответствующих элементов Ичетвертой и пятой груйп входы тре-.тьего элемента ИЛИ соединены с одним из выходов дешифратора функцийи выходами элементов И пятой .группы, а выход третьего элемента ИЛИподключен к выходу признаков блока.Такое решение позволяет выпол"нять условные переходы в микропрограмме без "холостых" циклов, чтосокращает время выполнения микропрограмм и повышает производитель"ность микропроцессора,На Фиг.изображена функциональная схема микропроцессора; на Фиг.2 функциональная схема блока обработки данных; на Фиг. 3 " функциональная схема блока микропрограммногоуправления; на фиг, 1 - Функциональ.ная схема коммутатора; на фиг. 5 алгоритм микропрограммы; на фиг.беременная диаграмма выполнения микпрограммы,Иикропроцессор.содержит блокобработки данных, информационныевходы 2-1 которого являются информационными входами микропроцессора,а выходы 5 и 6 - соответственно адресным и информационным выходамимикропроцессора, блок 7 микропрограиу.37263. 30 35 40 3 10много управления, вход И начальнойустановки которого является входоммикропроцессора, блок 9 микропрограммной памяти, конвейерный регистр10, выход 11 которого. является уп"равляющим выходом микропроцессора,блок 12 памяти переходов, регистр13 номера перехода, коммутаторэлемент И 15, и вход 16 синхронизации процессора. Выход 17 переносаи выход 18 сдвига блока 1 соединеныс входом 19 признаков блока 7 и вхо.дом элемента И 15, Выход 20 признаков блока 7 соединен с входом 21переноса и входом 22 сдвига блокаВход команд блока 7 соединен.синФормационным входом 2 микропроцессора, а адресный выход 23 - с адрес-ньи входом блока 9, Первый выходблока 9 соединен с входом 24 управления адресом блока 7, второй выход.с информационным входом 25 коммута-тора 4 а третий выход - с информа.ционным входом регистра 13, Выходрегистра 13 соединен с адреснымвходом блока 12, выход которогосоединен с информационным входом 26коммутатора 14. Управляющий вход 27коммутатора 14 соединен с входомэлемента И 15, вход которого соеди .нен с управляющим выходом 28 блока7. Выход коммутатора 14 соединен синформационным входом регистра 10,первый выход которого соединен свходом 29 дешифрации флагов блока 7.Второй и третий выходы регистра 10соединены соответственно с входами30 маскирования и 31 кода микрокоманды блока 1. Выходы синхронизацииблоков 1 и 7, регистра 10 и регистра 13 соединены с входом 16 микропроцессора,Блок 1 (фиг. 2) содержит дешифратор 32 микроприказов, дешифратор 33операндов, сумматор 34, группы элементов И 35, ИЛИ 36 и НЕ 37, группы элементов И 38, И 39, И 40, И 41и И 42, группу элементов ИЛИ 43,счетчик 44 адреса, сдвиговый регистр45, группы элементов И 46, И 47,и И 48, группу элементов ИЛИ 49,группу элементов И 93, элементы И 51,И 52, И 53, И 54, И 55 и И 56, элементы ИЛИ 57 и ИЛИ 58, триггер 59,элемент НЕ 60 и буферные элементыИЛИ 57 и ИЛИ 58, триггер 59, элемент НЕ 60 и буферные элементы И 61,И 62, Вход дешифратора 32 являетсявходом 31 кода микрокоманды блока 1 и соединен с входом дешифратора 33.Выходы дешифратора 32 соединены свходами групп элементов И 38, И 39И 40 и И 42, с входами элементов5 И 51, И 52, И 53 ф И 54 и И 55 свходами элементов ИЛИ 57,ИЛИ 58,НЕ 60 и с входом элемента И 62,1Выходы дешифратора 33 соединены свходами групп элементов И 46, И 471 О и И 48. Выход элемента ИЛИ 57 соединен с входом элемента И 56. Выходыэлементов И 51, И 52 и И 53 соединены соответственно с входом установки в нуль, счетным входом и вхо 15 дом занесения счетчика 44. Выходыэлементов И 54, И 55 и И 56 соединены соответственно с входом установ.,ки в нуль, входом синхронизациисдвига и входом занесения регистра20 .-45 Выходы счетчика 44 и регистра 45являются соответственно адресным 5и информационным 6 выходами микропроцессора,Выходы групп элементов И 46, И 4725 и И 48 соединены с входами группыэлементов ИЛИ 49. Входы групп элементов И 46, И 47 и И 48 являются соответственно инФормационными входами 2-4 микропроцессора, Входы группы элементов И 50 соединены с выходом группы эле"ментов ИЛИ 49 и входом маскированияблока 1. Выход группы элементов И 50соединен с входом сумматора 34, свходами групп элементов И 35, ИЛИ 36и с входом группы элементов И 41.Выход регистра 45 соединен с входамигрупп элементов И 35, ИЛИ 36, НЕ 37и с входом сумматора 34, Вход переноса сумматора 34 является входом 21 переноса блока 1, а выход переноса сумматора 34 соединен с информационным входом триггера 59, Выходысумматора 34 и групп элементов И 35 45 ИЛИ 36 и НЕ 37 соединены соответственно с входами групп элементовИ 38, И 39, И 40 иИ 42.Выходы групп элементов И 38, И 39,И 40, И 41 и И 42 соединены с входами группы элементов ИЛИ 43, выход которой соединен с информационными входами счетчика 44 и регистра 45. Входсдвига регистра 45 является входом22 сдвига блока 1. Выход сдвига регистра 45 соединен с входом элемен та И 62. Синхронизирующий вход триггера 59 соединен с выходом элементаИ 56, а выход - с входом элементаИ 61. Выходы элементов И 61 и И 62И 78, ИЛИ 79. Первые входы группыэлементов И 78 являются информационным входом 25 коммутатора 14, Вторыевходы группы элементов И 78 соединенымежду собой и с выходом элемента .ИЕ 76, Первые входы группы элемен"тов И 77 являются информационным входом 26 коммутатора 14, Вторые входыгруппы элементов И 77 соединены меж О ду собой, соединены с входом элемента НЕ 76 и с управляющим входом 27коммутатора 14. Входы каждого эле,мента ИЛИ 79 соединены поразряднос выходами элементов И 77 и И 78.Выходы группы элементов ИЛИ 79 явля", ются выходом коммутатора 14.На фиг. 5 показан алгоритм микропрограммы, на примере выполнения которой поясняется принцип работы 20 микропроцессора (символы И - отдельные микрокоманды; символы А - проверяемое логическое условие).На Фиг. 6 показана временная диаграмма выполнения алгоритма микро программы, где: 80 - синхроимпульсына входе 16 процессора; 81 - кодымикрокоманд на выходе блока 9; 82коды микрокоманд на выходе регистра10; 83 - сигнал условия на входе19 блока 7; 84 - сигнал на .управляющем выходе 28 блока 7.Для более четкого понимания работы микропроцессора рассмотрим выполнение им алгоритма микропрограммы 35(фиг, 5), Действия в микропроцессоре производятся в соответствии свременной диаграммой (фиг, 6).Для приведения микропроцессора .висходное состояние на информационныйвход 2 подается начальный адрес микропрограммы (адрес микрокоманды И 1),в на вход 8 - сигнал начальной за"грузки, По сигналу начальной загрузки на выходах элементов ИЛИ 73 иИЛИ 74 в блоках 7 вырабатываются еди 45ничные сигналы, По единичному сигналу с выхода элемента ИЛИ 74 открывается группа элементов И 64, и адресмикрокоманды И 1 поступает с входаоманд блока 7 через группы элементовИ 64 и ИЛИ 67 на информационный входрегистра 63, По заднему фронту сигнала с выхода элемента ИЛИ 73 адресмикрокоманды И заносится в регистр63, По этому адресу из блока 9 выбирается микрокоманда И 1 (позиция 81), Каждая микросхема состоит из трех частей; адресной, операционной и до полнительной. В дополнительной час" 7 1037263 8являются соответственно выходом 17переноса и выходом 18 сдвига блока 1.Выход элемента ИЛИ .58 соединен с входом группы элементов И 4 1, Выход элемента НЕ 60 соединен с входом элемента И 61. Входы элементов И 51; И 52,И 53, И 54, И 55, И 56 соединены свходом синхронизации блока 1,Блок 7 ( Фиг. 3 7 содержит регистр63 адреса, группы элементов И 64,И 65, И 66 и ИЛИ 67, дешифратор 68переходов, дешифратор 69 Функций,группы элементов И 70 и Р 71, группу триггеров 72, элементы ИЛИ 73,-ИЛИ 74 и ИЛИ 75.Вход дешифратора 68 является входом24 блока 7 и соединен с входами группэлементов И 65 и И 66. Входы дешифра.тора.б 8 соединены с входамигруппэлементов И 65 И бб и входом элемента ИЛИ 74, Первый выход дешифратора 68 является выходом 28 блока 7Вход элемента ИЛИ 73 является входом 8 начальной установки микропроцессора и соединен с входом эле"мента ИЛИ 74 и инверсными входамигрупп элементов И 65 и,И 66, Выход,элемента ИЛИ 74 соединен с входом группы элементов И 64, Выходы групп элементов И 64, И 65 и И 66 соединены свходами группы элементов ИЛИ 67, выход которой соединен с информационным входом регистра 63.Вход занесения регистра 63 соеди"нен с выходом элемента ИЛИ 73, Выходрегистра 63 является адресным выходом 23 блока 7. Вход элемента ИЛИ 73является входом 16 синхронизации блока 7 и соединен с входами группы зле.ментов И 70. Выходы группы элементов И 70 соединены с входами занесения группы триггеров 72, выходы ко.торых соединены с входами группы эле.ментов И 71.Вход дешифратора 69 является входом 29 дешифрации флагов блока 7. Вы"ходы дешифратора 69 соединены с входами групп элементов И 70, И 71 и свходом элемента ИЛИ 75. Выходы группы элементов И 71 соединены с входами элемента ИЛИ 75, выход которогоявляется выходом 20 гризнаков. блока7, Вход 19 признаков блока 7 соединен с информационными входами группы триггеров 72 и входом одного изэлементов И группы элементов И 66.Вход группы элементов И 64 является 55входом команд блока 7.Коммутатор 14 (фиг, 4)содержитэлемент НЕ 76, группы элементов И 77, 1037ти микрокоманды указывается номер условного перехода в микропрограмме. Разрядность (Р) этой части микро- команды определяется выражением 1 э:Е ,Ы,где Н - общее число условных перехо"дов в микропрограмме.Дополнительная часть микрокоман Оды поступает на информационный входрегистра 13; Операционная часть микрокоианды поступает на вход 25 комму"татора 14, а адресная часть микрокоианды - на вход 24 управления адресом блока 9, Адресная часть микооко-ианды состоит из двух полей - адресного поля и поля переходов, Сигналы,соответствующие адресному полю, по" ступают на входы групп элементов 2 ри 65 и И бб, Сигналы, соответствующие поле переходов, поступают на вход дешифратора 68, В поле перехо" дов адресной части микрокоманды М задается безусловный переход к микрокоианде М 2, Поэтому единичным сиг" налом с выхода дешифратора 68 откры вается группа элементов И 65 и И 66. Сигналы, соответствующие полю перехо дов, поступают на вход дешифратора 68, В поле переходов адресной части иикрокоманды М 1 задается безу словный переход к микрокоманде М 2, Поэтому единичным сигналом с выхода дешифратора 68 открывается группа35 элементов И 65 и адресное поле микрокоманды поступает через группы элементов И 65 и ИЛИ 67 на информаци онный вход регистра 63, 1 ак как эле мент И 15 закрыт нулевым сигналом 84, о на входе 27 коммутатора 14 присутствует нулевой сигнал. Приэтом группа элементов И 77 оказывается закрытой, а группа элементов И 78 открыта единичным сигналом с вьхода элемента НЕ 76. В резульЯ 5тате на информационный вход регистра 10 передается операционная частьмикрокоманды М 1.При поступлении первого синхроимпульса 80 на вход 16 производятся следующие действия, При возникновении переднего фронта синхроимпульса 80 блок 1 начинает выполнениемикрокоманды МО (позиция 82), хранимой на конвейерном регистре 10, Од-новременно микрокоманда М 1 начинаетзаноситься в конвейерный регистр 10,однако код этой микрокоманды появля 50 263 10ется на выходе регистра 10 через время Т 2, определяемое задержкой. занесения информации в регистр 10, В начальный момент времени в регистре 10 хранится микрокоманда МО, код которой сформировался неопрЕделенным образом йосле включения устройства. Поэтому выполнение этой микрокоманды не производит никаких полезных действий. Это связано с конвейерным принципом выполнения микропрограммы.Так как выборка микрокоманды опережает на цикл ее выполнение первая Микрокоманда микропрограммы может быть выполнена только во втором микрокомандном цикле. Поэтому первый микрокомандный цикл всегда являетсяхолостым, В зависимости От управ ляющего слова, поступающего на вход 31, блок 1 выполняет арифметико-логические и сдвиговые операции. Управляющее слово состоит из двух полей - поля операций и поля операндов. Сигналы, со тветствующие полю операции, поступают на вход дешиф" ратора 32,Сигналы, соответствующие полю операндов, поступают на вход дешифратора 33. ДешиФратор 32 вырабатывает на одном из своих выходов сигнал, микроприказа, соответству. ющий определенной операции, Арифме" тико-логические операции в блоке 1 выполняются над двумя операндами, Один из них находится в регистре 45, а второй поступает на один из информационных входов 2-4 микропроцессора. Дешифратор 34 вырабатываетна одном из своих выходов единичныйсигнал, по которому открывается одна из групп элементов И 46, И 47 иИ 48, В результате этого операнд ссоответствующего информационного вхо-.да поступает для дальнейшей обработки через группу элементов ИЛИ 49и группу элементов И 50, На выходе сумматора 34 Формируется значение арифметической суммы слагаемых с уче" том значения сигнала входного пере-, носа. Если при этом происходит переполнение разрядной сетки сумматора 34,то на выходе переноса вырабатывается единичный сигнал, На выходе группы операционных элементов И 35 формируется конъюнкция, а на выходе группа операционных элементов ИЛИ 36- дизъюнкция операндов, На выходе груп,пы операционных элемен 1 ов НЕ 37 Форми. руется инверсное значение кода, со11 10372держащегося в регистре 45, По единичному сигналу с одного из выходовдешифратора 32 значение результатаоперации поступает через одну изгрупп элементов И 38, И 39, И 40,И 41,: И 42 и группу элементовИРИ 43 на информационные входы счетчика 44 и регистра 45, По переднему фронту импульса с выхода одногоиз управляющих элементов И 51, И 52, 10И 53, И 54) И 55 И 56 производятсяразличные действия со счетчиком 44и регистром 45 (установка в нуль,занесение, сдвиг, прибавление "единицы", к содержимому).15По заднему фронту синхроимпульса80 адрес микрокоманды М 2 заноситсяв регистр 63, а дополнительная частьмикрокоманды - в регистр 13, Микрокоманда М 2 появляется на выходе 20блока 9 (позиция 81) через время11определяемое временем занесения врегистр 63 и.временем выборки изблока 9, В дополнительной части микрокоманды М 2 указывается номер услов 25ного перехода А в микропрограмме. Вадресной части микрокоманды М 2 задается безусловный переход в яикрокоманду М 3, При поступлении второгосинхроимпульса 80 блок 1 выполняет З 0микрокоманду М 1 (позиция 82), а микрокоманда М 2 заносится в регистр 10,По адресной части микрокоманды М 2блок 7 формирует адрес микрокомандыМ 3, номер перехода по условию А заносится в регистр 13, Из блока 9 вы 35бирается микрокоманда М 3 (позиция 81),а из блока 12 выбирается операционная часть микрокоманды М 4. В адресной части микрокоманды М 3 задаетсявыполнение условного перехода,По 40этому единичным сигналом с выходадешифратора 68 открывается группаэлементов И 66, в результате чегоадрес следующей микрокоманды формируется с учетом значения сигнала ус 45ловия на входе 19 блока 7. Сигнал84 принимает единичное значение,вследствие чего открывается элементИ 5. При поступлении третьего синхроимпульса 80 блок 1 выполняет мик 50рокоманду М 2 (позиция 82), в результате чего формируется значение сигнала 83 условия,Так как сигнал 83 принимает единичное значение 1, условие выполняется ), на управляющем входе 27 коммутатора 14 устанавливается единичный сигнал, По этому сигналу ком 12му атор 14 поДключает на информационный вход регистра 10 операционную часть микрокоманды М 4 с выхода блока 12, Микрокоманда М 4 заносится в регистр 10, По адресной части микро- команды М 3 и единичному значению сигнала 83 условия блок 7 формирует адрес микрокоманды М 5, которая затем выбирается из блока 9 1, позиция 81). В адресной части микрокоманды М 5 задается безусловный переход к следующей микрокоманде. Поэтому сигнал 84 принимает нулевое значение, вследствие чего закрывается элемент И 15В Коммутатор 14 подключает на информационный вход регистра 10 операционную часть микрокоманды М 5 с выхода блока 9. При поступлении четвертого синхроимпульса 80 блок 1 выполняет микрокоманду М 4 (позиция 82),микро- команда М 5 заносится в регистр 1 ОФ а по ее адресной части блок 7 формирует адрес следующей микрокоманды и т.д.Если сигнал 83 условия в резуль 4 тате выполнения микрокоманды М 2 по третьему синхроимпульсу 80 принимает нулевое значение (условие не выполняется),то коммутатор 14 подклю. чает на вход регистра 10 операционную часть микрокоманды М 3 с выхода блока 9, Блок 7 по адресной части микрокоманды М 3 и нулевому значению условия формирует адрес следующей микрокоманды этой ветви и работа микропроцессора продолжается аналогично,При выполнении многих операций блок 1 обращается к блоку внешней памяти или внешнему устрдйству, выставляя на выход 5 микропроцессора соогветствующий адрес. Блок внешней памяти и внешние устройства, с которыми взаимодействуют микропроцессор, на фиг. 1 не показаны., Если необ ходимо записать информацию в.блок . внешней памяти или внешнее устройст" во, что указывается в текущей микрокоманде, на управляющем выходе 11 устанавливается сигнал, соответствующий режиму записи, Записываемые данные выставляются блоком 1 на информационный выход, При чтении информации из блока внешней памяти или внешнего устройства на управляющий выход 11 поступает сигнал чтения аФ считываемые данные снимаются блокомс информационных входов 2 4 устрой 13 10372 стаа. Код, яодаЬаемый с первого выхода регистра 10 на вход 29 блока 7, . определяет фнукцию управления логи" кой флагов, которая заключается ли" бо в установлении выбранного флага в соответствии со значением сигнала на входе 19 блока 7, либо в выдаче содержимого, выбранного флага или значений фОфф и н 1 н на выход 20 блока 7,Работа блока 7 при этом заключает ся в следующем, 8 соответствии с кодом, поступающим на вход 29 блока на одном из выходов дещифратора 69 вырабатывается управляющий сигнал, Если производится установка одного из группы триггеров 72, то по единичному сигналу свыхода дешифратора 69 открывается один из группы элементов И 70, При поступлении синхроимпульса 80 на вход 16 блока 7 на выходе элемента И 70 вырабатывается импульс, по заднему фронту которого 63в соответствующий триггер 72 заносит ся значение сигнала на входе 19 бло" ка 7. Если значение одного из группы триггеров 72 выдается на выход 20 блока 7, по единичному сигналу с со. ответствующего выхода дещифратора 69 открывается один из группы эле" ментов И 71 и содержимое триггера 72 через элементы И 71 и ИЛИ 75 поступает на выход 20 блока 7.Таким образом, в предлагаемом микропроцессоре выполнение условных переходов проивводится без наличия "холостых" циклов в отличие от известного, где при выполнении каждого условного перехода присутствует "холостой" цикл,8 результате этого предлагаемый микропроцессор не имеет потерь производительности за счет наличия "холостых" циклов в выполнении микропрограмм.

СмотретьЗаявка

3393600, 12.02.1982

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО ЮЖНОГО ГОЛОВНОГО МОНТАЖНОГО УПРАВЛЕНИЯ СРЕДСТВ СВЯЗИ ЦЕНТРАЛЬНОГО НАУЧНО ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КАСКАД"

ПУШКАРЕВ ЮРИЙ ЯКОВЛЕВИЧ, ПОЛОНСКИЙ ДМИТРИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: микропроцессор

Опубликовано: 23.08.1983

Код ссылки

<a href="https://patents.su/10-1037263-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Микропроцессор</a>

Предыдущий патент: Микропрограммный процессор

Следующий патент: Микропрограммный процессор

Случайный патент: Инерционный воздухоочиститель