Цифро-аналоговая система для регистрации и статистической обработки информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

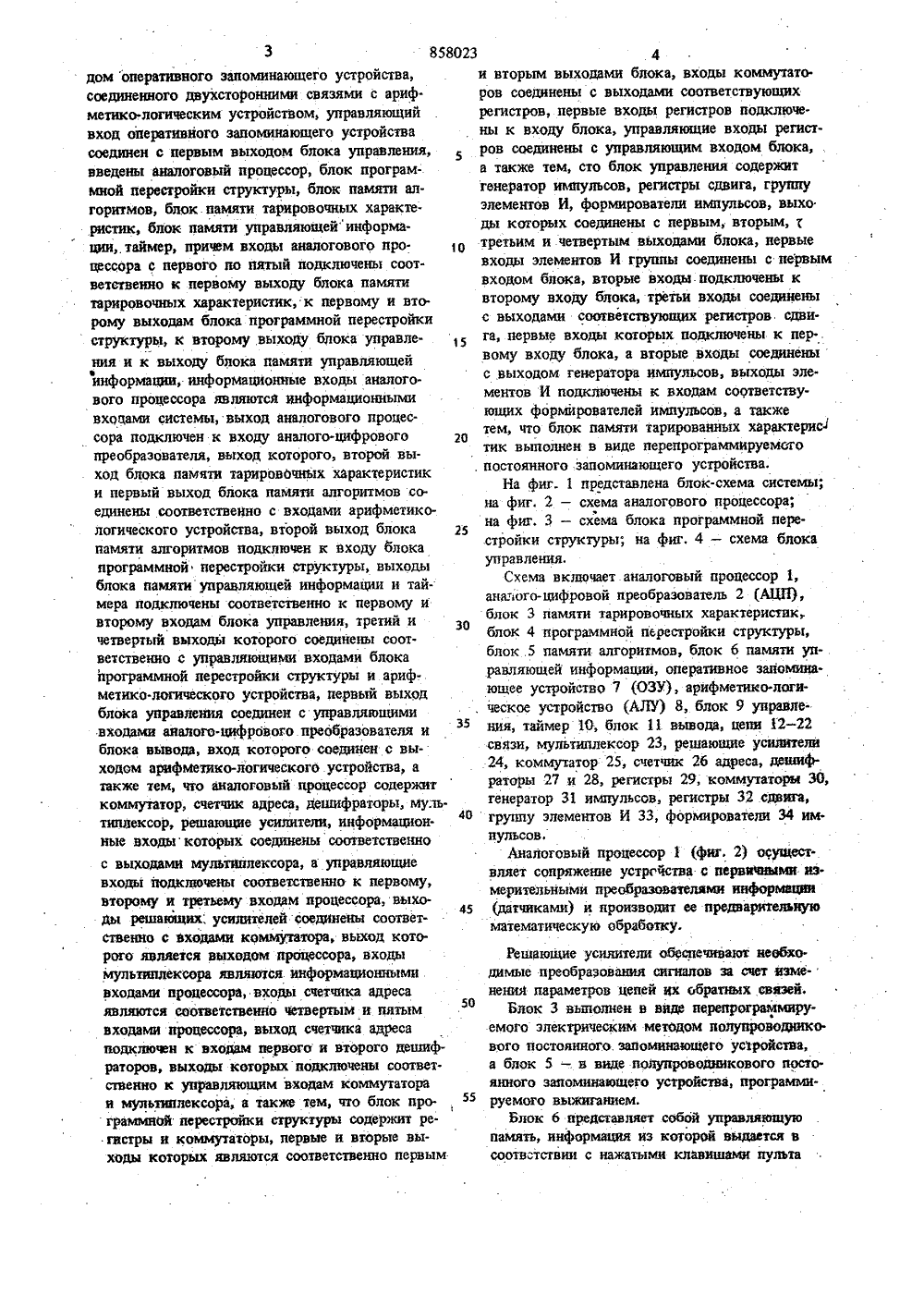

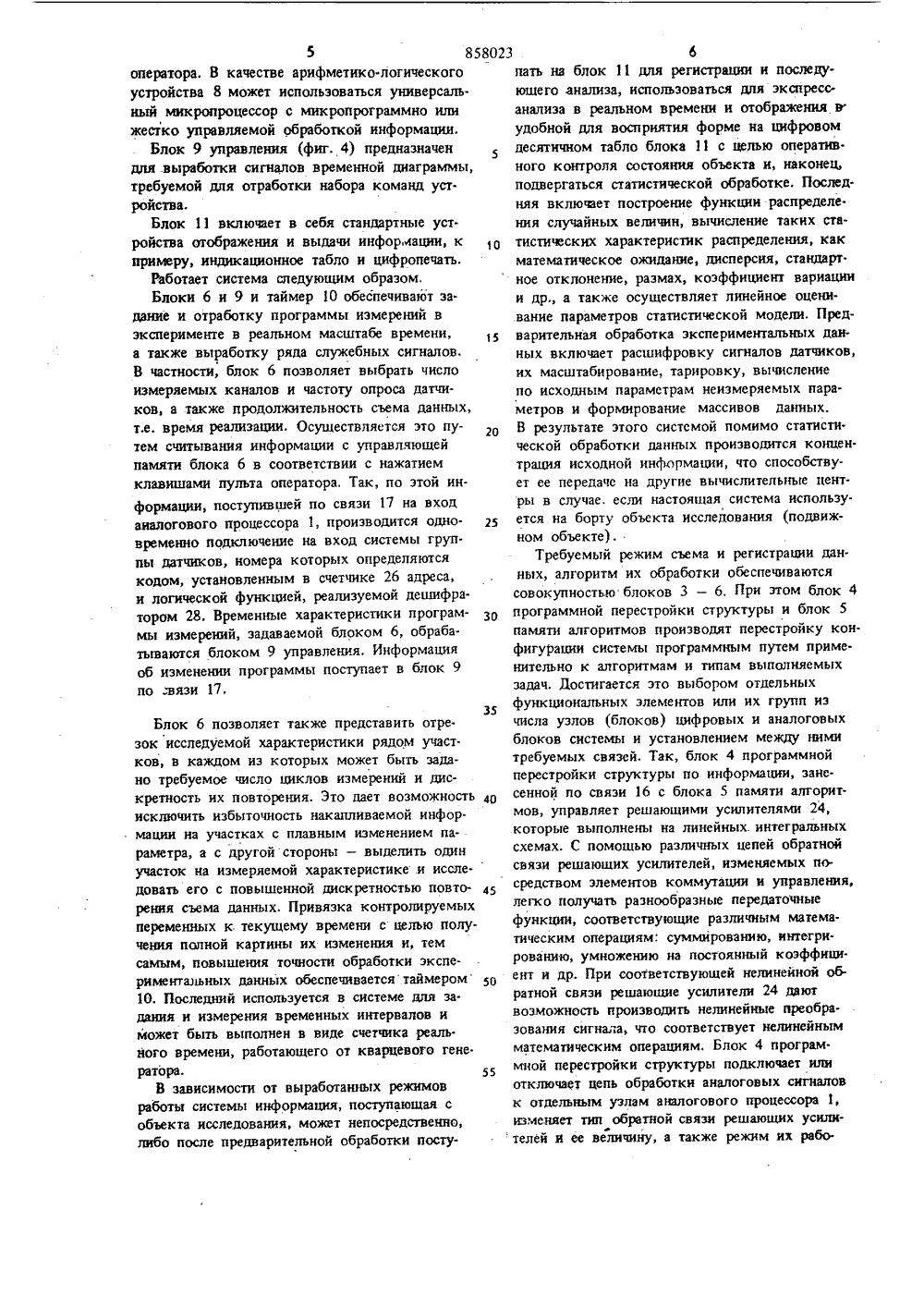

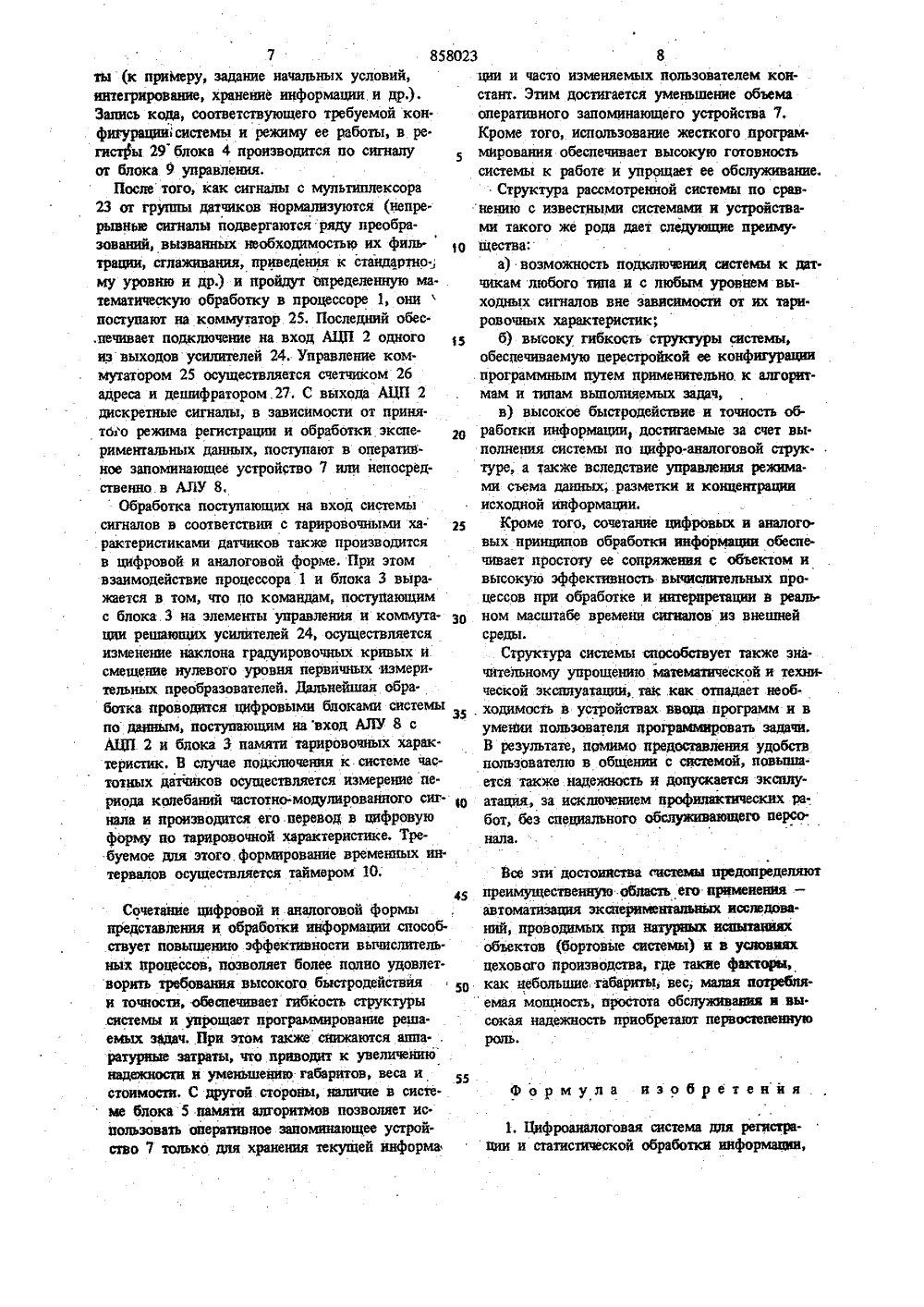

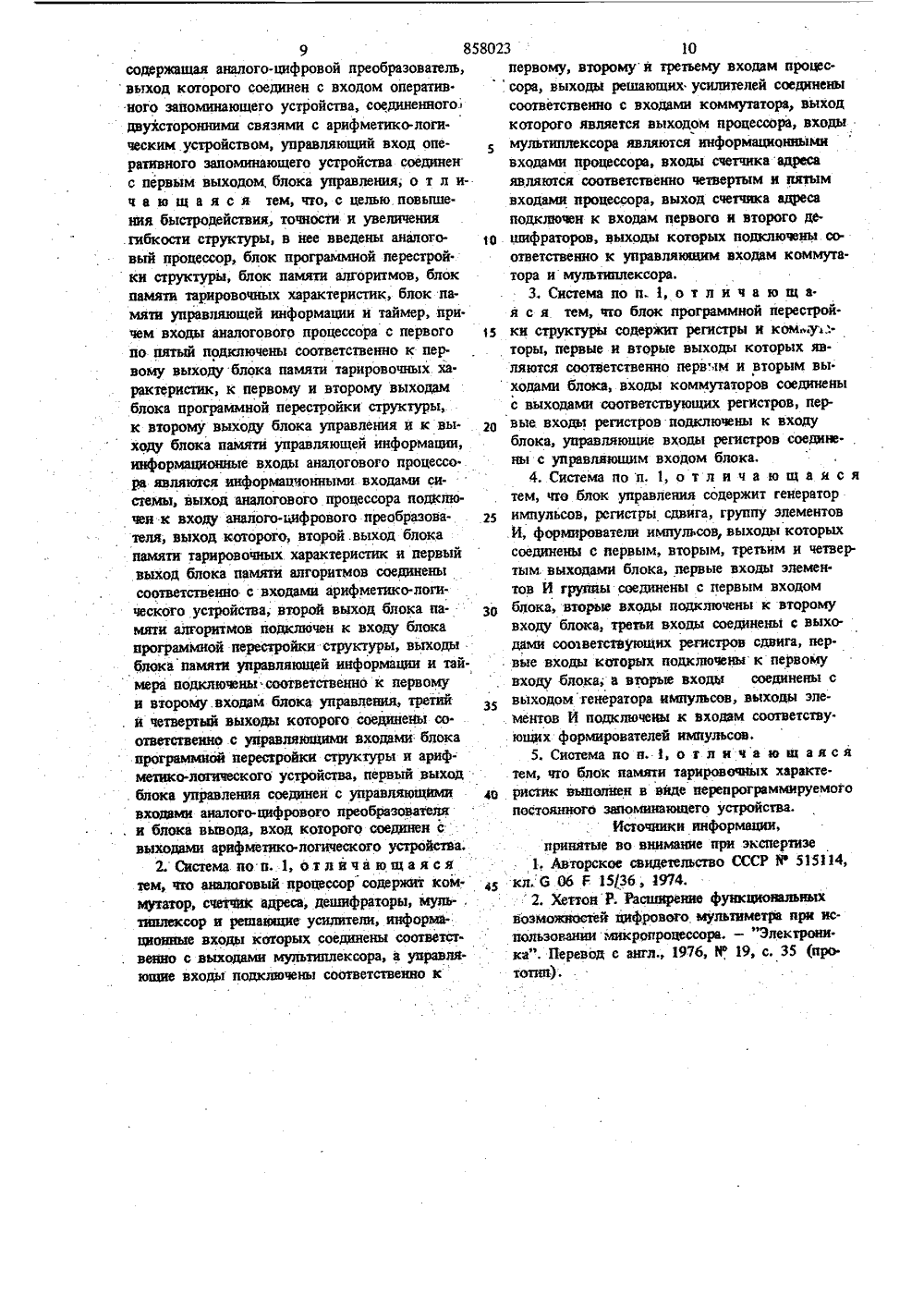

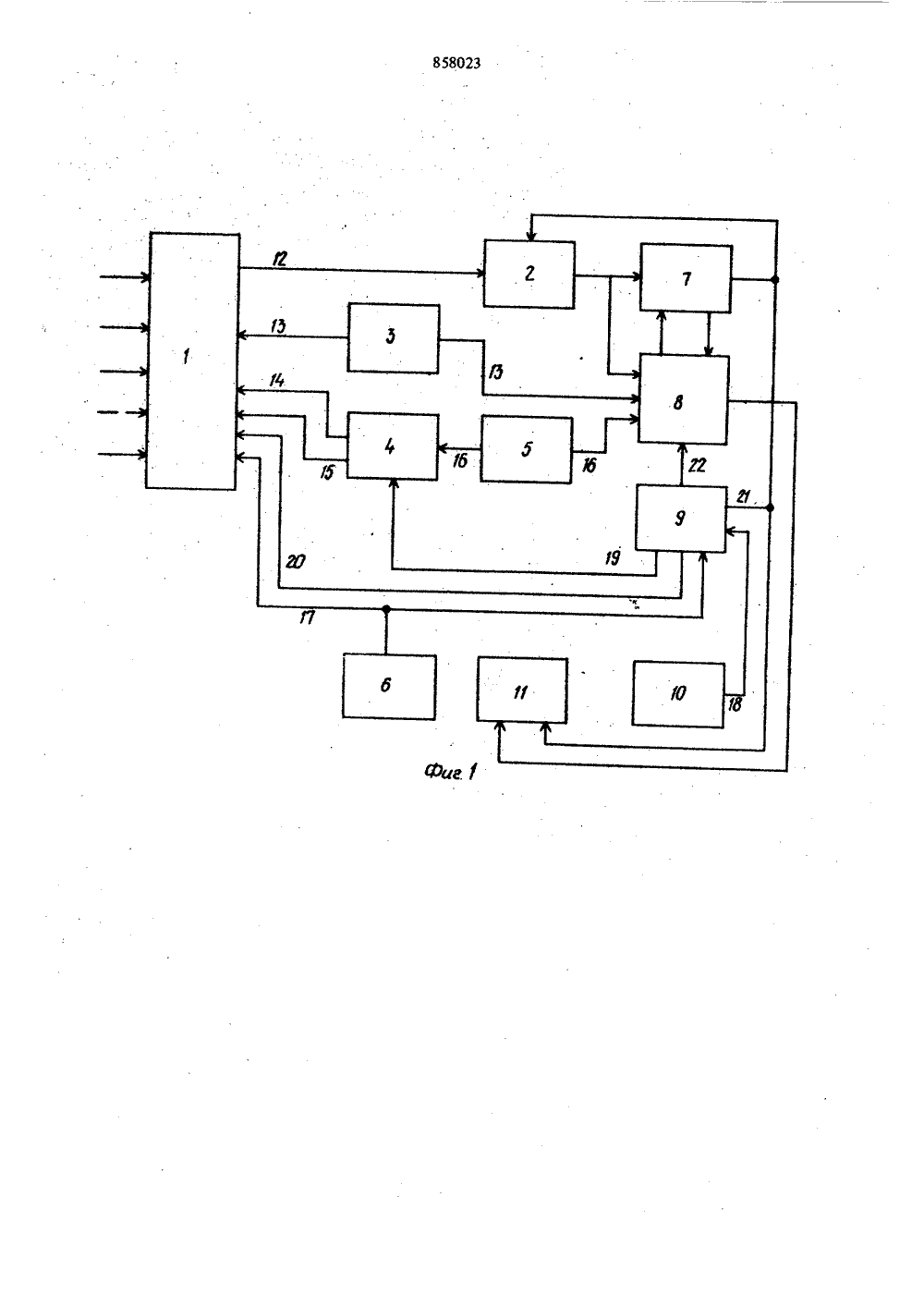

ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВ 1 ОРСКОМУ СВИДЕТЕЛЬСТВУ Сонэз СоветскихСецнапнстнческнхРеспублнк Г 111 858023(5 )М. Кл,6 Об З 3/006 06 Е 15/36 Геауйарстмкай кфмктат СССР в двяак вэовретевнк в вткрьпяк.22 (088,8) Дата опубликования описания 23.08.81.(54) ЦИФРОАНАЛОГОВАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ И СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ Изобретение относится к вычислительной технике и может быть использовано в любой области, где требуется производить сбор и статис. тическую обработку данных, в чзстности, при автоматизации экспериментальных исследований.Известно устройство для регистрации и ста. тистическои обработки информации, содержа. щее преобразователь информзции, подключенный выходом к оператгвному запоминающему устройству, цифровой вычислительный блок, связанный с оперативным запоминающим уст. ройством и соединенный с ними блок управлеюя, а также блок выходных устройств. Это устройство предназначено для регистрации раз. личных физических величин при эксперименталь. ных исследованиях и для их последующей статистической обработки в арифметическом устройстве по жесткой программе 11. Наиболее близкой к предлагаемому но технической сущности является система; содержа 20 щзя микропроцессор, связанный с оперативным упоминающим устройством и через аналогоцифровые преобразователи с датчиками входных величин, контролер и устройство вывода 12).Данную систему можно перестраивать дляразличного типа датчиков, однако перестронкапе является олерзтивной. Регистрация толькоунифицированных входных сигналов, связанныхс измеряемой величиной линейной зависимостью,сужает функциональные возможности и уменьшает эффективность использования системы,Необходимость запоминания для последующегоанализа всей входной информации, отсутствиеее разметки и привязки к условиям эксперимента снижают.быстродействи; системы и точность обработки данных. Быстродействие устройства.в неменьшей мере зависит также и отпринятого способа обработки информации.В известной системе информация обрабатывается только в цифровой форме.Целью изобретения является повышение быстродействия, точности и увеличение гибкостиструктуры,11 оставленная цель достигается тем, что всистему, содефжащую аналого.цифровоый преобразователь, выход которого соединен с вхо.858023 дом оперативного запоминающего устройства, соединенного двухсторонними связями с ариф.метико-логическим устройством, управляющий вход оперативного запоминающего устройства соединен с первым выходом блока управления, введены аналоговый процессор, блок программной пересгройки структуры, блок памяти алгоритмов, блок. памяти тарировочных характеристик, блок памяти управляющей информациитаймер, прищм входы аналогового процессора с первого по пятый подключены соответственно к первому выходу блока памяти тарировочных характеристик,:к первому и второму выходам блока программной перестройки структуры, к второму выходу бдока управления и к выходу блока памяти управляющей информации, информационные входы аналогового процессора являются информационными входами системы, выход аналогового процессора подключен к входу аналого-цифрового ро преобразователя, выход которого, второй вы.. ход блока памяти тарировочных характеристик и первый выход блока памяти алгоритмов соединены соответствеино с входами арифметикологического устройства, второй выход блока 25 памяти алгоритмов подключен к входу блока программной перестройки структуры, выходы блока памяти управляющей информации и таймера подключены соответственно к первому и второму входам блока управлении, третий и четвертый выходы которого соединены соответственно с управляющими входами блока программной перестройки структуры и арифметико.логического устройства, первый выход блока управления соединен с управлявшими входами аналого-цифрового преобразователя и блока вывода, вход которого соединен с выходом арифметико-логического устройства, а также тем, что аналоговый процессор содержит коммутатор, счетчике адресадешифраторы, муль.типлексор, решаннцие усилители, информационные входы которых соединены соответственно с выходами мультиплексора, а управляющие входы подключекы соответственно к первому, второму и третьему входам процессора, выхо 45ды решающих; усилителей соединены соответственно с входами коммутатора, выход которого является вьиодом процессора, входы мультипдексора являктгся информационными входами нродессора, входы счетчика адреса являются соответственно четвертым и пятым входами процессора, выход счетчика адреса подключен к входам первого и второго дещифраторов, выходы которых подключены соответственно к управляющим входам коммутатора н мультиплексора, а также тем, что блок программной перестройки структуры содержит регистры и коммутаторы, первые и вторые выходы которых являются соответственно первым.4и вторым выходами блока, входы коммутаторов соединены с выходами соответствующихрегистров, первые входы регистров подключены к входу блока, управляющие входы регистров соединены с управляющим входом блока,а также тем, сто блок управления содержитгенератор импульсов, регистры сдвига, группуэлементов И, формирователи импульсов, выходы которых соединены с первым, вторым, гтретьим и четвертым выходами блока, первыевходы злементов И группы соединены с первымвходом блока, вторые входы подключены квторому входу блока, третьи входы соединеныс выходами соответствующих регистров. сдвига, первые входы которых подключены к первому входу блока, а вторые входы соединеныс выходом генератора импульсов, выходы злементов И подключены к входам соответствующих формирователей импульсов, а такжетем, что блок памяти тарированных характеристик выполнен в виде перепрограммируемогопостоянного запоминающего устройства,На фиг. 1 представлена блок. схема системы;на фиг. 2 - схема аналогового процессора;на фиг, 3 - схема блока программной пер:стройки структуры; на фиг, 4 - схема блокауправления.Схема включает аналоговый процессор 1,аналого-цифровой преобразователь 2 (АЦП),блок 3 памяти тарировочных характеристик,блок 4 программной перестройки структуры,блок .5 памяти алгоритмов, блок б памяти управляющей информации, оперативное запоминающее устройство 7 (ОЗУ), арифметико-логическое устройство АРАЛУ) 8, блок 9 управления, таймер 10, блок 11 вывода, цепи 12-22связи, мультиплексор 23, решающие усилители24, коммутатор 25, счетчик 26 адреса, дещираторы 27 и 28, регистры 29, коммутаторы 30,генератор 31 импульсов, регистры 32 .сдвига,группу элементов И 33, формирователи 34 импульсов.Аналоговый процессор 1 (фиг. 2) осуществляет сопряжение устргчства с первичными из.мерительными преобразователями информации(датчиками) и производит ее предварительнуюматематическую обработку,Решающие усилители обеспечивают необхо.димые преобразования сигналов за счет изменения параметров цепей их обратюих связей,Блок 3 выполнен в вида нерепрограммиру.емого злектрическим методом полупроводнико.вого постоянного. запоминающего устройства,а блок 5 - в виде полупроводникового посто.яниого запоминающего устройства, программируемого выжиганием,Блок 6 аредставляет собой управляющуюпамять, информаея из которой выдается эсоотв;тствии с нажатыми клавишами пульта858023 5 15 20 25 30 1 О 40 45 50 5оператора, В качестве арифметико-логического устройства 8 может использоваться универсаль. иый микропроцессор с микропрограммно или жестко управляемой обработкой информации.Блок 9 управления (фиг, 4) предназначен для выработки сигналов временной диаграммы, требуемой для отработки набора команд устройства.Блок 11 включает в себя стандартные уст ройства отображения и выдачи информации, к примеру, индикационное табло и цнфропечать.Работает система следующим образом.Блоки 6 и 9 и таймер 10 обеспечивают задание и отработку программы измерений в эксперименте в реальном масштабе времени, а также выработку ряда служебных сигналов. В частности, блок 6 позволяет выбрать число измеряемых каналов и частоту опроса датчиков, а также продолжительность съема данных, т,е, время реализации. Осуществляется это путем считывания информации с управляющей памяти блока 6 в соответствии с нажатием клавишами пульта оператора, Так, по этой информации поступившей по связи 17 на вход аналогового процессора 1, производится одновременно подключение на вход системы группы датчиков, номера которых определяются кодом, установленным в счетчике 26 адреса, и логической функцией, реализуемой дешифратором 28. Временные характеристики программы измерений, задаваемой блоком 6, обрабатываются блоком 9 управления, Информация об изменении программы поступает в блок 9 по вязи 17. Блок 6 позволяет также представить отре. зок исследуемой характеристики рядом участ. ков, в каждом из которых может быть задано требуемое число циклов измерений и дискретность их повторения, Это дает возможность исключить избыточность накапливаемой информации на участках с плавным изменением параметра, а с другойстороны - выделить одинучасток на измеряемой характеристике .и исследовать его с повышенной дискретностью повторения съема данных. Привязка контролируемых переменных к текущему времени с целью получения полной картины их изменения и, тем самым повышения точности обработки экспериментальных данных обеспечиваетсятаймером 10. Последний используется в системе для за. дания и измерения временных интервалов и может быть выполнен в виде счетчика реаль. ного времени, работающего от кварцевого гене. ратора.В зависимости от выработанных режимов работы системы информация, поступающая с объекта исследования, может непосредственно, табо после предварительной обработки посту 6пать на блок 11 для регистрации и последующего анализа, использоваться для экспрессанализа в реальном времени и отображения в удобной для восприятия форме на цифровом десятичном табло блока 11 с целью оперативного контроля состояния объекта и, наконец, подвергаться статистической обработке. Послед.няя включает построение функции распределе.ння случайных величин, вычисление таких статистических характеристик распределения, как математическое ожидание, дисперсия, стандартное отклонение, размах, коэффициент вариации и др., а также осуществляет линейное оценнвание параметров статистической модели, Предварительная обработка экспериментальных данных включает расшифровку сигналов датчиков, их масштабирование, тарировку, вычисление по исходным параметрам неизмеряемых параметров и формирование массивов данных.В результате этого системой помимо статисти.ческой обработки данных производится концен.трация исходной информации, что способствует ее передаче на другие вычислительные цент ры в случае. если настоящая система испольэу.ется на борту объекта исследования (подвижном объекте).Требуемый режим съема и регистрации данных, алгоритм их обработки обеспечиваются совокупностью блоков 3 - 6. При этом блок 4 программной перестройки структуры и блок 5 памяти алгоритмов производят перестройку кон.фигурации системы программным путем приме.вительно к алгоритмам и типам выполняемых задач, Достигается это выбором отдельных функциональных элементов или их групп иэ числа узлов (блоков) цифровых и аналоговых блоков системы и установлением между ними требуемых связей. Так, блок 4 программной перестройки структуры по информации, занесенной по связи 16 с блока 5 памяти алгоритмов, управляет решающими усилителями 24, которые выполнены на линейных. интегральных схемах. С помощью различных цепей обратной связи решающих усилителей, изменяемых посредством элементов коммутации и управления, легко получать разнообразные передаточные функции, соответствующие различным математическим операциям: суммированию, интегри. рованию, умножению на постоянный коэффициент и др, При соответствующей нелинейной об.ратной связи решающие усилители 24 дают воэможность производить нелинейные преобразования сигнаи что соответствует нелинейным математическим операциям. Блок 4 програм.мной перестроики структуры подключает или отключает цепь обработки аналоговых сигналов к отдельным узлам аналогового процессора 1, изменяет тип обратной связи решающих усили телей н ее величину, а также режим их рабо.85802 7ты (к примеру, задание начальных условий,интегрирование, хранение информации. и др,).Запись кода, соответствующего требуемой кон.фнгурациисистемы и режиму ее работы, в регист 1 ы 29 блока 4 производится по сигналуот блока 9 управления.После того, как сигналы с мультиплексора23 от группы датчиков нормализуются (непре.рывные сигналы подвергаются ряду нреобразований, вызванных необходимостью их Филь- Отрации, сглаживания, приведения к стандартно;му уровню и др.) и пройдут определенную математическую обработку в процессоре 1, онипоступают на коммутатор 25. Последний обес.печивает подключение на вход АЦП 2 одногоиз выходов усилителей 24. Управление комМутатором 25 муществляется счетчиком 26адреса и дешифратором.27. С выхода АЦП 2дискретные сигналы, в зависимости от принята"о режима регистрации и обработки экспе.риментальных данных, поступают в операти 6 ное запоминающее устройство 7 или непосредственно. в АЛУ 8.Обработка поступающих на вход системысигналов в соответствии с тарировочнымн ха драктеристиками датчиков также производитсяв цифровой и аналоговой форме. При этомвзаимодействие процессора 1 и блока 3 выражается в том, что по командам, поступающимс блока,З на элементы управления и коммута- чоцяи решаияцих усилителей 24, осуществляетсяизменение наклона градуировочных кривых исмещение нулевого уровня первичных измерительных преобразователей. Дальнейшая обра.ботка проводится цифровыми блоками системыпо данным, поступающим навход АЛУ 8 сАЦП 2 и блока 3 памяти тарировочных харак.теристик, В случае подключения к системе частотных датчиков осуществляется измерение пе.риода колебаний частотно-модулированного сиг- онала и производится его.перевод в цифровуюформу по тарировочной характеристике, Тре.буемое для этого формирование временных ин.тервалов осуществляется таймером 1 О,45Сочетание цифровой и аналоговой формыпредставления и обработки информации способствует повыщешю эффективности вычислитель.ных процессов, позволяет более полно удовлетворить требования высокого быстродействияи точности, обеспечивает гибкость структуры.системы и упрощает програмьщрованне реша.емых задач. При этом также снижаются аппаратуриые затраты, что приводит к увеличейнюнадежности и уменьшению габаритов, веса истоимости. С другой стороны, наличие в системе блока 5 памяти алгоритмов позволяет ис.пользовать оперативное запоминающее устройство 7 только для хранения текущей информа ции и часто изменяемых пользователем констант. Этим достигается уменьшение объемаоперативного запоминающего устройства 7.Кроме того, использование жесткого дрограм.мирования обеспечивает высокую готовностьсистемы к работе н упрощает ее обслуживание,Структура рассмотренной системы по сравнению с известными системами и устройствами такого же рода дает следуилцие преимущества:а) возможность подключения системы к датчикам любого тяпа и с любым уровнем выходных сигналов вне зависимости от их тари.ровочных характеристик;б) вьгсоку гибкость структуры системы,обеспечиваемую перестройкой ее конфигурациипрограммным путем применительно. к алгоритмам и типам выполняемых задач,в) высокое быстродействие и точность об.работки информации, достигаемые за счет выполнения системы по цнфро аналоговой структуре, а также вследствие управления режима.мн съема данных, разметки и концентрацииисходной информации.Кроме того, сочетание цифровых и аналого.вых нринцилов обработки информации обеспечивает простоту ее сопряжения с объектом ивысокую эффективность вычислительных процессов при обработке и интерпретации в реальном масштабе времени сигналов из внешнейсреды.Структура системы способствует также эна.чительному упрощению математической и технической эксплуатации, так .как отпадает необ.ходимость в устройствах Ввода программ и вумейни пользователя программировать задачи.В результате, помимо предоставления удобствпользователю в общении с системой, повышается также надежность и допускается эксплуатация., за исключением профилактических работ, без специального обслуживающего перса.нала,Все зти достоинства системы предопредевпот преимущественную область его нримеиения - автоматизация эксйериментальных исследований, проводимых дри натурных испьггаииях объектов (бортовые системы) и в условиях цехового производства, где такие факторы, как небольшие. габариты, вес, малая потребляемая мощность, простота обслуживания и высокая надежность приобретают первостепенную роль.Формула изобретенйя1, Цифроаналоговая система для регистрации и статистической обработки информации,5 1 О 20 25за 35 выход которого соединен с входом оператив. ного заноминающего устройства, соединенного. дву)сторонними связями с арифметико-логическим устройством, управляющий вход оперативного запоминающего устройства соединен с первым выходом, блока управления, о т л ич а ю щ а я с я тем, что, с целью. повышения быстродействия, точности и увеличения .гибкости структуры, в нее введены аналоговый процессор, блок программной перестрой.ки структуры, блок памяти алгоритмов, блок памяти тарировочных характеристик, блок памяти управляющей информации и таймер, причем входы аналогового процессора с первого по пятый подключены соответственно к пер.вому выходу блока памяти тарировочных характеристик, к первому и второму выходам блока программной перестройки структуры, к второму выходу блока управления и к выходу блока памяти управляющей информации, информационные входы аналогового процессора являются информационными входами шстемы, выход аналогового процессора подключен к входу аналого-цифрового преобраэова.теля, выход которого, второй. выход блока памяти тарировочиых характеристик и первый выход блока памяти алгоритмов соединены соответственно с входами арифметико-логического устройства; второй выход блока памяти алгоритмов подключен к входу блока црограммпой нерестройки-структуры, выходы блока памяти управляющей информации и таймера подключены соответственно к первому и второму. входам блока управления, третий . и четвертый выходы которого соединены со.ответственно с управляяицими входами: блока программной перестройки структуры и арифметико-логического устройства, первый выход . блока управления соединен с управляющими входами аналого-цифрового преобразователя . и блока вывода, вход которого соединен с выходами арифметика-логического устройства,2. Система по п. 1, о т л и ч а ю щ а я с атем, что аналоговый процессор содержит коммутатор, счетчас адреса, дешифраторы, муль-, типлексор и рещааяцие усилители, информационные входы которых соединены соответст.венио с выходами мультиплексора, а управмющие входы подключены соответственно ксора, выходы решающих усилителей соединены соответственно с входами коммутатора, выход которого является выходом процессора, входы мультиплексора являются информационными входами процессора, входы счетчика адреса яв.лаются соответственно четвертым и пятым входами процессора, выход счетчика адреса подключен к входам первого и второго де. шифраторов, выходы которых подключены со ответственно к управляющим входам коммутатора и мультиплексора.3. Системз по п. 1, о т л и ч а ю щ а. я с я тем, что блок программной перестрой. ки структуры содержит регистры и ком;у;.- торы, первые и вторые выходы которых являются соотВетственно перв. м и вторым вы ходами блока, входы коммутаторов соединеныс выходами соответствующих регистров, первые входь 1 регистров подключены к входу блока, управляющие входы регистров соедииены с управляющим входом блока.4. Системз цо п, 1, о т л и ч а ю щ а я с я тем, что блок управления содержит генератор импульсов, регистры сдвига, группу элементов И, формирователи импульсов, выходы которых соединенЫ с первым, вторым, третьим и четвер тым. выходами блока, первые входы элемен. тов И группы соединены с первым входом блока, вторью входы подключены к второму входу блока, третьи входы соединены с выходами соответствующих регистров сдвига, первые входы которых подключены к первому входу блока; а вторые входы соединены с выходом генератора импульсов, выходы элементов И подключены к входам соответству. ющих формирователей импульсов.5. Система ло н. 1, о т л и ч а в щ а я с ятем, что блок памяти тарировочиых характе. рисшк выполнен в виде перепрограммируемого постоянного запоминающего устройства Источники информации, принятые во внимание при экспертизе1, Авторское свидетельство СССР Иф 515114,м кл. 6 Об Г 1536, 1974,2. Хеттон Р. Расширение функциональных возможностей цифрового мультиметра при использовании макропроцессора. - "Электроника". Перевод с англ., 1976, И 19, с. 35 (про.тотип).аж 745 Подписнсе филиал ППП фПатент", г, Ужгород, ув,ВНИИПК Заказ 7247 858023

СмотретьЗаявка

2839351, 13.11.1979

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ АН УКРССР, ВОЙСКОВАЯ ЧАСТЬ 13132

СКУРИХИН ВЛАДИМИР ИЛЬИЧ, МАКАРОВ ГЕНРИХ ТИМОФЕЕВИЧ, УРСАТЬЕВ АЛЕКСЕЙ АНДРЕЕВИЧ, НИКУЛИН ВИТАЛИЙ НИКОЛАЕВИЧ, ВЛАСЕНКО ВАЛЕРИАН МОИСЕЕВИЧ, КУДЕЛКО ОЛЕГ МАРКИЯНОВИЧ, СУВОРОВ АЛЕКСАНДР ИВАНОВИЧ, ТИХОНОВ ГЕОРГИЙ АФАНАСЬЕВИЧ, ТИТОВ ВИКТОР ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 17/18

Метки: информации, регистрации, статистической, цифро-аналоговая

Опубликовано: 23.08.1981

Код ссылки

<a href="https://patents.su/8-858023-cifro-analogovaya-sistema-dlya-registracii-i-statisticheskojj-obrabotki-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Цифро-аналоговая система для регистрации и статистической обработки информации</a>

Предыдущий патент: Устройство для сопряжения аналоговой и цифровой вычислительных машин

Следующий патент: Аналого-цифровой микропроцессор

Случайный патент: Устройство для обвязки пакета изделий