Устройство для умножения двух -разрядных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

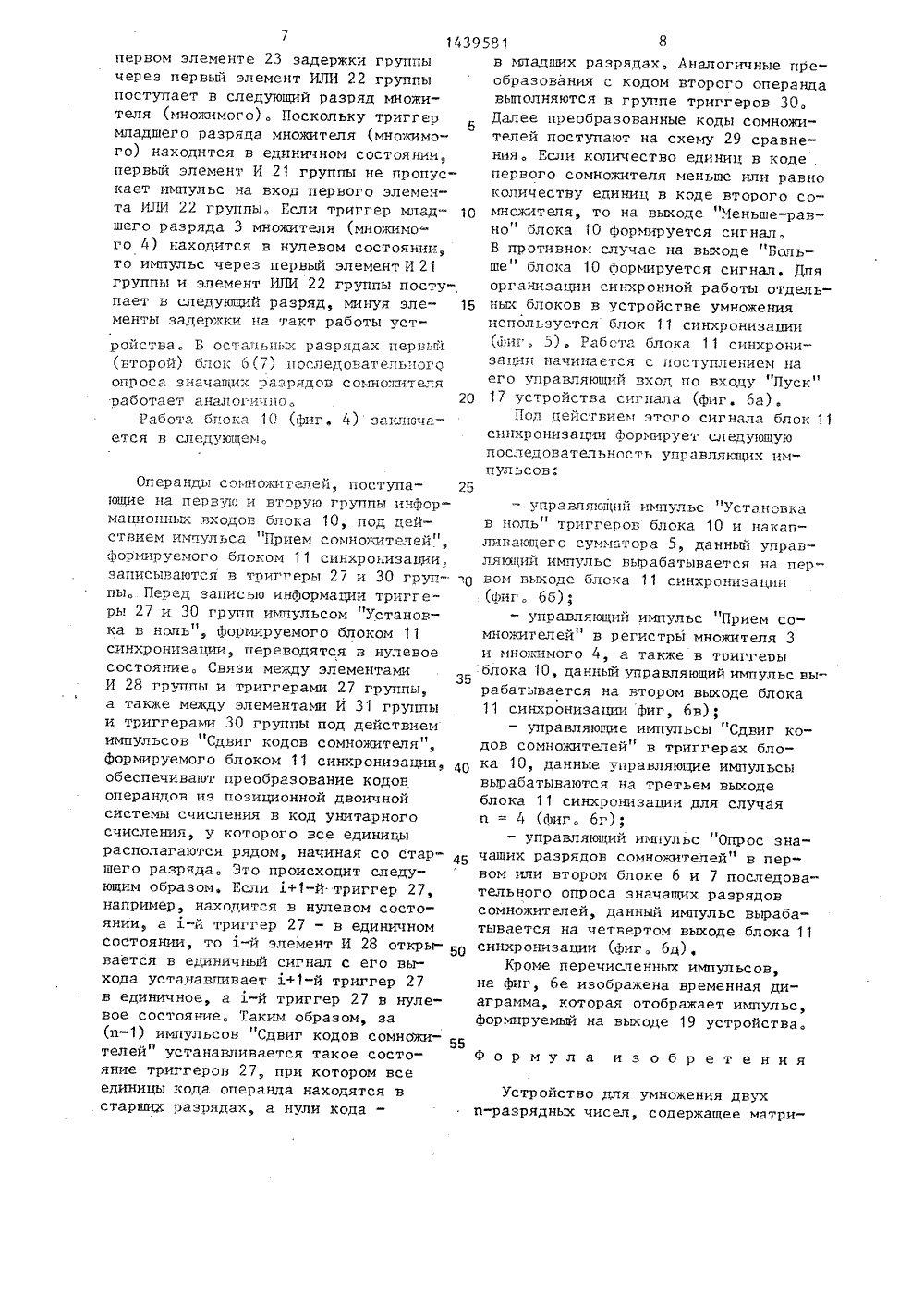

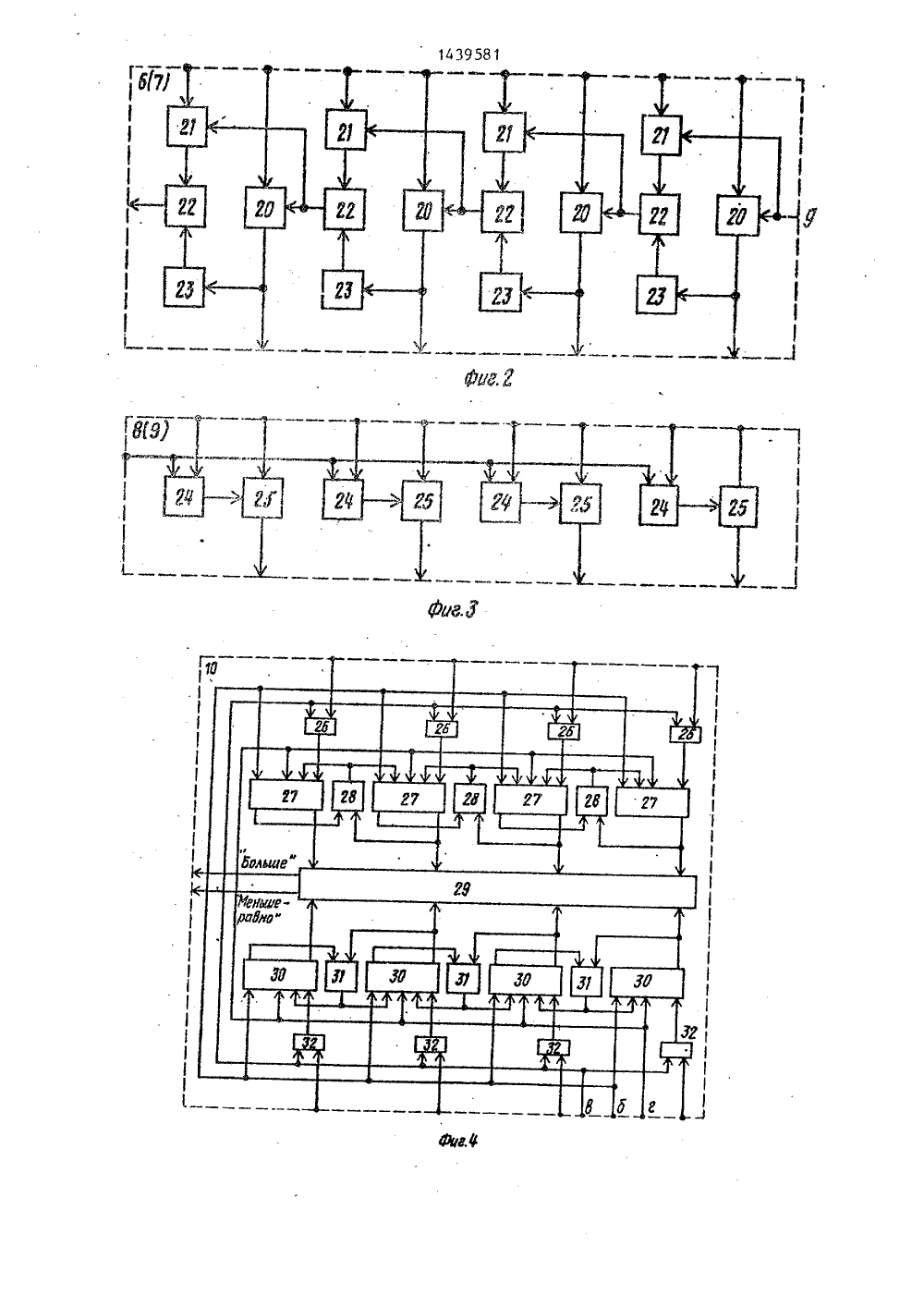

СОЮЗ СОНЕТСНИХСОЦИАЛИСТИЧЕСНИРЕСПУБЛИК 9) э)И) 1 4 1)4 С 06 Р 7 ласт быть на ОСУДАРСТНЕННЫЙ КОМИТЕТ СССРПОДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) Авторское свидетельство СССРВ 1103667. кл. С Об Р 7/52, 1982.Авторское свидетельство СССРР 991418, кл, С Об Р 7/52, 1981.(54) устРойство Для яйожениЯ Двухи "РАЗРЯДНЫХ ЧИСЕЛ(57) Изобретение относится к обвычислительной техники и можетиспользовано в быстродействующихустройствах цифровой обработки сиг лов асинхронного типа. Цель изобретения - повышение быстродействия. Дляэтого в устройство для умножения,содержащее матрицу иэ элементов И 1,блок 2 элементов ИЛИ, регистр 3 множителя, регистр 4 множимого, накапливающий сумматор 5, блок 6 последовательного опроса значащих разрядовсомножителя, блок 10 сравнения кодов,блок 11 синхронизации, элементы И 12,13 и элемент ИЛИ 14, введены блок 7последовательного опроса значащихразрядов сомножителя и входные коммутаторы 8, 9 с соответствующимисвязяж. 6 ил,Изобретение относится к вычислительной технике и может быть использовано в быстродействующих устройствах цифровой обработки сигналовасинхронного типа для получения произведения двух двоичных чисел, представленных параллельным кодом,Целью изобретения является повышение быстродействия. 10На фиг. 1 изображена схема устройства для умножения двух и-разрядныхчисел (длл и =: 4); на фиг. 2 - схемапервого (второго) блока последовательного опроса значащих разрядовсомножителя: на фиг, 3 - схема пер-"вого (второго) входного коммутатора;на фиг. 4 " схема блока сравнениякодов; на фиг. 5 - структурная схемаблока синхронизации; на фиг, б - 20временные диаграммы управляющих сигналов блока синхронизации (а - навходе блока синхронизации, б, в, г(2 и)".разрядный накапливающий сумматор 5, первый блок б последова 35тельного опроса значащих разрядовсомножителл, второй блок 7 последова: тельного опроса значащих разрядов со множителя, первый входной коммутатор8, второй входной коммутатор 9, блок10 сравнения кодов, блок 11 синхронизации, первый элемент И 12 второйэлемент И 13, элемент ИЛИ 14, вход 15первого сомножителя устройства, вход16 второго сомножителя устройства,вход 17 устройства, выход 18 произведения устройства и выход 19 "Конец"устройстваПервый (второй) блок б(7) последовательного опроса (фиг. 2) значащих50разрядов сомножителя содержит первукгруппу из и элементов И 20, вторуюгруппу из и элементов И 21, группуиз элементов ИЛИ 22 и группу из иэлементов 23 задержки, причем первыевходы элементов И 20 и 21 групп явллются соответственно первой и второй группами информационных входовблока б(7), выходы элементов И 20 являются выходами группы блока б(7) и соединены через соответствующие элементы 23 задержки группы с первыми входами соответствуюцщх элементов ИЛИ 22 группы, вторые входы которых соединены с выходами соответствующих элементов И 21 группы, вторые входы которых объединены с вторыми входами соответствующих элементов И 20 группы и подключены к входам предыдущих элементов ИЛИ 22 группы, управляющие вход и выход блока б(7) соединены соответственно с вторым входом младшего элемента И 20 группы и с выходом старшего элемента ИЛИ 22 группы.Гервый (второй) входной коммута. - тор 8(9) (фиг. 3) содержит группу из и элементов И 24 и группу из и элементов ИЛИ 25, причем первые входы элементов ИЛИ 25 группы образук 1 т соответственно перлу;о группу информациопных входов коммутатора Я(9), информационными выходами которого являются соответственно выходы элементов ИЛИ 25 группы вторые входь 1 элементов ИЛИ 25 которой соедине;.ы соответственно с выхоцами элеь ентав И 24 группы вторые входы которых образуют соответственно вторуо группу информационньсс входов коммутатора 8(9), первые вхоцы элементов И 24 группы соединены межцу собой и являются управляощим входам комутатора 8(9),Блок 10 сравнения коцов (фиг.4) содержит первую группу из и элементов И 26 первую группу из и триггеров 27, вторую группу из (и)-го элемента И 28, схему 29 сравнения, вторую группу из триггеров 30, третью группу из (и)-го элемента И 31, четвертую группу из и элементов И 32, причем первые входы элементов И 26 и 32 групп соответственно образуют первую и вторую группы информационных входов блока 10, выходами "Меньше-равно" и "Больше" которого являются соответственно первый и второй выходы схемы 29 сравнения, вторые входы элементов И 26 и 32 групп соединены между собой и являются вторым управляющим входом блока 10, выходы элементов И 26 и 32 групп соединены соответственно с асинхронными входами установки в единичное состояние триггеров 27 и 30 групп, входы синхронизации которых соединены между собой и являются третьим управля 3 14ющим входом блока 10, первым управляющим входом которого являются соединенные между собой асинхронныевходы установки в нулевое состояниетриггеров 27 и 30 групп, синхронныевходы установки в нулевое состояниетекущих триггеров 27 и 30 и синхронные входы установки в единичное состояние последующих триггеров 27 и30 групп, выходы, соответствующиекаждой паре триггеров, элементов И28 и 29 групп соединены соответственно между собой, первые входы элементов И 28 и 31 групп, соответствующие каждой паре триггеров, соединены соответственно с прямыми выходаьи текущих триггеров 27 и 30 групп,инверсные выходы последующих тригге,ров которых соединены соответственнос вторыми входами элементов И 28 и31 групп, соответствующие каждой паре триггеров, прямые выходы триггеров 28 и 31 групп соединены соответственно с первой и второй группамиинформационных входов схемы 29 сравнения.Блок 11 синхронизации содержитформирователь 33 импульса, элементНЕ 34, группу из (и+1) элементов 35задержки и элемент ИЛИ 36, причемвход блока 11 соединен с входом Формирователя 33 импульса, выход которого соединен с входами последовательно соединенных элементов 35 задержки, выход формирователя 33 импульса соединен с входом элементаНЕ 34, выход которого является первым выходом блока 11, вторым выходомкоторого является выход первого элемента 35 задержки группы, выходы свторого элемента 35 задержки по и-йэлемент 35 задержки которой соединены соответственно с входами элемента ИЛИ 36, выход которого являетсятретьим выходом блока 11, четвертымвыходом которого является выход последнего элемента 35 задержки группы.Работа устройства для умножениядвух и-разрядных чисел заключаетсяв следующем,Операнды сомножителей, поступамцие по входам 15 и 16 первого сомножителя и второго сомножителя устройства, одновременно записываются соответственно в регистры 3 и 4 множителя и множимого, а также в блок 10сравнения кодов. После записи операндов в блок 10 в последнем производит 39581 10 15 20 25 30 35 40 45 50 55 ся преобразование кодов операндов из позиционной двоичной системы счисления в код унитарного счисления, сравнение этих кодов и выработка соответствующих сигналов "Больше" или Меньше-равно", Если количество единиц в коде первого сомножителя, поступающего на вторую группу информационных входов блока 10 и на информационные входы регистра 3 множителя, меньше или равно количеству единиц в коде второго сомножителя, поступающего на первую группу информационных входов блока 10 и на информационные входы регистра 4 мнокимого, то на выходе "Меньше-равно" блока 10 формируется сигнал. Данный сигнал, поступая на управляющий вход второго входного коммутатора 9, обеспечивает коммутацию прямых информационных выходов регистра 4 множимого через второй входной коммутатор 9 с соответствующими диагональными элементамн матрицы элементов И 1.1 роме того, этот сигнал, поступая на первый вход первого двухвходового элемента И 12, обеспечивает прохождение импульса с четвертого выхода блока 11 синхронизации на управляющий вход первого блока 6 последовательного опроса значащих разрядов сомножителя. Этим самым обеспечивается последовательный, начиная с младшего разряда, опрос значащих разрядов первого сомножителя, хранимого в регистре 3 множителя. Если триггер младшего разряда регистра 3 множителя находится в единичном состоянии, то импульс, поступающий на управляющий вход первого блока 6 последовательного опроса значащих разрядов сомножителя появляется на информационном выходе младшего разряда блока б, Под действием этого импульса, открывающего по вторым входам элементы И первой строки матрицы, формируется первое частичное произведение. В этом случае, когда блок 10 вырабатывает управляющий сигнал "Меньше- равно" первое и следующие. частичные произведения прецставляют собой соответственно несдвинутый и сдвинутый на требуемое число разрядов влево код второго сомножителя, хранящийся в регистре 4 множимого, Сформированное таким образом первое частичное произведение через элементы ИЛИ блока 2 элементов ИЛИ поступает на вхо 143958125 35 Если количество единиц в коде первого сомножителя, поступающего навторую группу информационных входовблока 10 и на информационные входырегистра 3 множителя, больше коли"чества единиц, чем в коде второгосомножителя, поступающего на первуюгруппу информационных входов блока 10и на информапионные входы регистра 4множимого, то на выходе "Большеблока 10 формируется сигнал, Данныйсигнал, поступая на управляющий входпервого входного коммутатора 8, обеспечивает коммутацию прямых информационных выходов регистра 3 множителя,через первый входной коммутатор 8 ссоответствующими строками матрицыэлементов И 1,Кроме этого этот сигнал поступая на первьп 1 вход второго элементаИ 13, обеспечивает прохождение импульса с четвертого выхода блока 11синхронизации на управляющий вход ды накапливающего сумматора 5 длянакопления соответствующей суммычастичных произведений. После задержки на Один такт работы устройствав блоке б последовательного опросазначащих разрядов сомножителя импульс11 роизводит опрос следующего, болеестаршего, разряда регистра 3 множитепя. Длительность первого такта 10работы устройства так же, как и всехследующих, определяется с учетом времени выполнения операции суммирования в накапливающем сумматоре 5. Если триггер мпад 1 цего или любого другого разряда регистра 3 множителянаходится в нулевом состоянии, тоимпульс без задержки на один тактработы устройства в первом блоке бпоследовательного Опроса значащих 20разрядов сомножителей производит опрос следующего более старшего разряда регистра 3 множителя, Далее такимже образом, последовательно один задругим, производится анализ состоя 1 п 1 я остальньх, более старших разрядов регистра 3 множителя, и устройство работает аналогично, Появлениеимпульса па вьжоде 19 устройства"Конец", поступающего через элемент 30ИЗБ 14 с управляющего выхода блока бозначает, что процесс умножения закончен и в накапливающем сумматоре 5сформировалось соответствуюп 1 ее произведение,второго блока 7 последовательного опроса значащих разрядов сомножителя. Этим самым обеспечивается последовательный, начиная с младшего разряда, опрос значащих разрядов второго сомножителя, хранимого в регистре 4 множимого. Если триггер мпадшего раз,ряда регистра 4 множимого находится в единичном состоянии, то импульс, поступающий на управляющий вход второго блока 7 последовательного опроса значащих разрядов сомножителя появляется на информационном выходе мпадшего разряда блока 7. Под действием этого управляющего импульса, открывающего по первььм входам логические элементы И первой диагонали матрицы элементов И 1, формируется первое частичное произведение, 3 этом случае, когда блок 10 вырабатывает сигнал на выходе "Больше" первое и след ующис час тич ньье пр Оиз вед е 11 ия пр ед" ставляют собой соответственно несдвинутый и сдвинутые на требуемое число разрядов влево код первого сомножителя, хранящегося в регистре 3 инолжтеля. Сформированные таким образом первое частичное произведение как и при выработке блоком 10 сиге 1 ала. на выходе Меньше-равно", через элементы ИИ блока. 2 элементов ИЛИ поступает на входы накапливающего сумматора 5 для накопления соответствуюший суммы частичных произведений. Далее устройство работает, как и при вьработке блоком 10 сигнала на выходе "Меньше-равнои, однако при этом анализируются более старшие разряды регистра 4 мнслимого.Работа первого 6 (второго 7) блока последовательного опроса значащих разрядов сомножителя (фиг, 2) заключается в следующем.Импульс опроса значащих разрядов сомножителя, формируемый блоком 11 синхронизации через первый 12 (второй 13) элемент И, поступает на входы первых элементов И 20 и 22 групп элементов И, Если триггер младшего разряда регистра 3 множителя (множимого 4) находится в единичном состоянии, то импульс появляется на выходе первого элемента И 20 и разрешает суммирование первого частичного произведения на накапливающем сумматоре 5. Кроме этого, данный импульс, задержанный на один такт вкает импульс на вход первого элемента ИЛИ 22 группы. Если триггер младшего разряда 3 множителя (множимого 4) находится в нулевом состоянии, то импульс через первый элемент И 21группы и элемент ИЛИ 22 группы поступает в следующий разряд, минуя элементы задержки на такт работы устройства. В остальных разрядах первый (второй) блок б (7) последовательнога опроса значащих разрядов сомно:1 нтеля работает аналогично.Работа б 1 ока 10 (фиг, 4) заключается в следующем,10 20 7 1439первом элементе 23 задержки группы через первый элемент ИЛИ 22 группы поступает в следующий разряд множителя (множимого) . Поскольку триггер младшего разряда множителя (множимого) находится в единичном состояжи,первый элемент И 21 группы не пропус 581 8в младших разрядах, Аналогичные преобразования с кодом второго операнда выполняются в группе триггеров 30, Далее преобразованные коды сомножителей поступают на схему 29 сравнения. Если количество единиц в коде первого сомножителя меньше или равно количеству единиц в коде второго сомножителя, то на выходе Меньше-равно" блока 10 Формируется сигнал . В противном случае на выходе "Больше" блока 10 формируется сигнал. Для организации синхронной работы отдельных блоков в устройстве умножения используется блок 11 синхронизации (фиг, 5). Работа блока 11 синхрониза 1 ии 11 ачинается с поступлением на его управляющий вход по входу "Пуск" 17 устройства сигнала (Фиг. ба),Под действием этого сигнала блок 11 синхронизации формирует следующую последовательность управляющих импульсов:Операнды со 11 нож 11 тсле 1поступа ющие на первую и вторую группы информационных входов блока 10, под действием импульса "Прием сомножителейформируемого блоком 11 синхро 11 изаври. записываются в триггеры 27 и 30 группы, Перед записью информации триггеры 27 и 30 групп импульсом "Установка в ноль", формируемого блоком 11 синхронизации, переводятся в нулевое состояние. Связи между элементами И 28 группы и триггерами 27 группы,а также между элементами И 31 гру 11 пыи триггерами 30 группы под действием импульсов Сдвиг кодов сомножителя",Формируемого блоком 11 синхронизации, обеспечивают преобразование кодов операндов из позиционной двоичной системы счисления в код унитарного счисления, у которого все единицы располагаются рядом, начиная со старшего разряда. Это происходит следующим образом. Если .+1-й триггер 27, например, находится в нулевом состоянии, а 1.-й триггер 27 - в единичномсостоянии, то -и элемент И 28 открывается в единичный сигнал с его выхода устанавливает +1-Й триггер 27 в единичное, а .-й триггер 27 в нулевое состояние. Таким образом, за (и) им 11 ульсов "Сдвиг кодов сомножителей" устанавливается такое состояние триггеров 27, при котором все единицы кода операнда находятся в старших разрядах, а нули кода -управляю 11 ий импульс "Установкав ноль" триггеров блока 10 и накапливающего сумматора 5, данный управля 1 щий импульс вырабатывается на первом вььходе блока 11 синхронизации(фиг. бб)- управляющий импульс ППрием сомножителей" в регистры множителя 3и множимого 4, а также в триггепыблока 10, данный управляющий импульс вы 35рабатывается на втором выходе блока11 синхрониза 1 ц 1 и фиг, бв);- управляющие импульсы Сдвиг кодов сомножителей" в триггерах бло 40 ка 1 0 данные управляющие импульсывырабатываются на третьем выходеблока 11 синхронизации для случаяи = 4 (фиг. бг);- управляющий импульс Опрос зна 45 чащих разрядов сомножителей 11 в первом или втором блоке б и 7 последовательного опроса значащих разрядовсомножителей, данный импульс вырабатывается на четвертом выходе блока 11синхронизации (фиг. бд),Кроме перечисленных импульсов,на Фиг, бе изображена временная диаграмма, которая отображает импульс,формируемый на выходе 19 устройства.Формула из обр ет енияУстройство для умножения двух и-разрядных чисел, содержащее матри9 1439 цу из п элементов И, (2 п)-разрядный блок элементов ИЛИ, и-разрядный регистр множителя, и-разрядный регистр множимого, (2 п)-разрядный накапливающий сумматор, первый блок последовательного опроса значащих разрядов сомножителя, элемент ИЛИ, первый и второй элементы И, блок сравнения кодов и блок синхронизации, 10 причем прямые и инверсные выходы разрядов и-разрядного регистра множителя соединены соответственно с информационными входами первой и второй групп первого блока последова тельного опроса значащих разрядов сомножителя, входы первого и второго сомножителей устройства соединены соответственно с входами разрядов и-разрядных регистров множителя и множимо го, первая и вторая группы информационных входов блока сравнения кодов соединены соответственно с входами второго и первого сомножителей устройства вход Пуск которого соеди нен с входом запуска блока синхрони" зации, первый выход которого соединен с входом обнуления накапливающего сумматора и с первым управляющим входом блока сравнения кодов, выхо ды "Меньше-равно" и "Больше" которого соединены соответственно с первыми входами первого и второго элементов И, второй выход блока синхронизации соединен с вторым управляющим входом 35 блока сравнения кодов и с входами разрешения приема п-разрядных регистров множителя и множимого, третий выход блока синхронизации соединен с третьим управляющим входом блока сравнения кодов, четвертый выход блока синхронизации соединен с вторыми входами первого и второго элементов И выходы разрядов с второго по (2 п) -й матрицы из п 2 элементов И соединены 45 с соответствующими входами 2 п)-разрядного блока элементов ИЛИ, выходы которого соединены с соответствующими входами разрядов (2 п)-разрядного накапливающего сумматора, входы пер50 вого и (2 п) -го разрядов которого581 1 О соединены с выходами соответствующихразрядов матрицы из и элементов И,выходы разрядов (2 п)-разрядногонакапливающего сумматора являютсявыходом произведения устройства, о тл и ч а ю щ е е с я тем, что, сцелью повышения быстродействия, оносодержит второй блок последовательного опроса значащих разрядов сомножителя, первый и второй входные коммутаторы, причем выходы группы первогоблока последовательного опроса значащих разрядов сомножителя и прямые выходы разрядов и-разрядного регистрамножителя соединены соответственнос информационными входами первой ивторой групп первого входного коммутатора, выходы разрядов которого соединены с входами элементов И соответствуа 1 их строк матрицы из и элементов И, входы элементов И столбцов которой соединены с выходами со-ответствующих разрядов второго выходного коммутатора, первая и втораягруппы информационных входов которого соединены соответственно с выходами группы второго блока последовательного опроса значащих разрядовсомножителя и с прямыми выходами разрядов и-разрядного регистра множимого, прямые и инверсные выходы разрядов которого соединены соответственно с информационными входами первойи второй групп второго блокапоследовательного опроса значащих разрядовсомножителя, управляющие вход и выход которого соединены соответственно с выходом второго элемента И ис первым входом элемента ИЛИ, выходи второй вход которого соединены соответственно с выходом "Конец" устройства и с управляющим выходом первогоблока последовательного опроса значащих разрядов сомножителя, управляющий вход которого соединен с выходомпервого элемента И, первый вход которого и первый вход второго элемента Исоединены соответственно с управляющими входами второго и первого входных коммутаторов, 14395811439581 г Составитель А. Кл Техред М.Ходанич ор Н, Король Ред Воро т 8/48 Тираж 704ВНИИПИ Государственного копо делам изобретений и о 113035, Москва, Ж, Гаушска Подписнтета СССР аказ рытий наб., д Производственно-полиграфическое предприятие, г, Ужгород, ул, Проектна

СмотретьЗаявка

4240211, 05.05.1987

ПУШКИНСКОЕ ВЫСШЕЕ УЧИЛИЩЕ РАДИОЭЛЕКТРОНИКИ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ

РОМАНОВ АЛЕКСАНДР МИХАЙЛОВИЧ, ДЖУС ВЛАДИМИР ВСЕВОЛОДОВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: двух, разрядных, умножения, чисел

Опубликовано: 23.11.1988

Код ссылки

<a href="https://patents.su/8-1439581-ustrojjstvo-dlya-umnozheniya-dvukh-razryadnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения двух -разрядных чисел</a>

Предыдущий патент: Устройство для одновременного вычисления двух многочленов

Следующий патент: Устройство для деления переменной на целое число

Случайный патент: Водопонизительная скважина