Цифроаналоговая система сбора и обработки информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

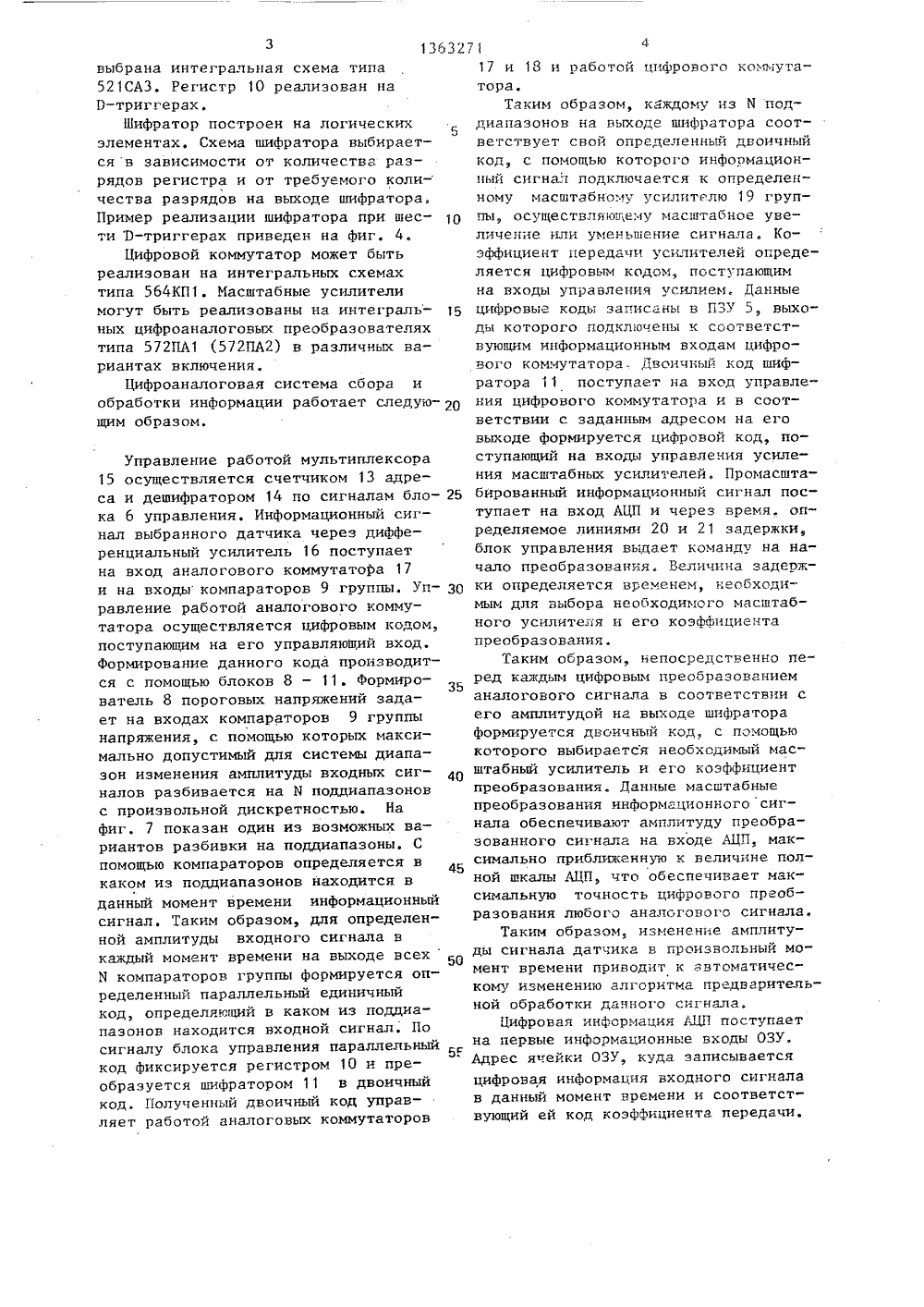

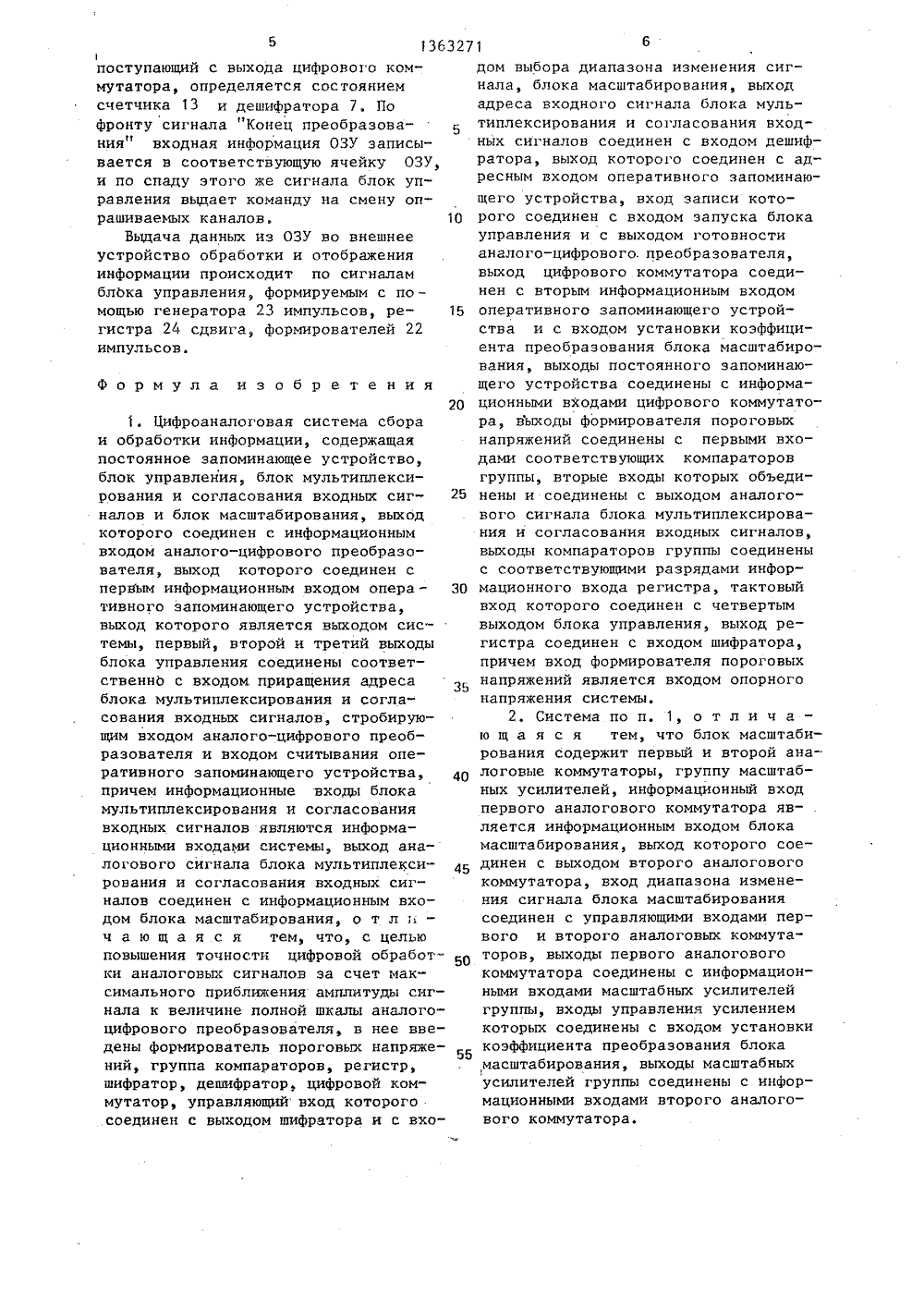

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 1 4 С 06 Л 3/ Фф ОБРЕТ ЕПЬСТВУ К АВТОРСКОМ ь ци нал ения о разов держащуюгласо 4 маси препоминаю И запоми- авления яроваруппатор, дер 1 з и ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОПИСАНИЕ(56) Авторское свидетельство СССР 9 858024, кл. С 06 3 3/00, 1981.Авторское свидетельство СССР В 858023, кл. С 06 д 3/00, 1981. (54) ЦИФРОАНАЛОГОВАЯ СИСТЕМА БОРА ОБРАБОТКИ ИНФОРМАЦИИ(57) Изобретение относится к вычислительной технике и может быть использовано при создании систем,производящих сбор и обработку аналоговых сигналов, например при обработк телеметрической информации. Изобрет ние позволяет повысить точнос ровой обработки аналоговых си за счет максимального приближ плитуды сигнала к величине по шкалы аналого-цифрового преоб теля. Для этого в систему, со блок мультиплексирования и со вания входных сигналов, блок штабирования, аналого-цифрово образователь 2, постоянное за щее устройство 5, оперативнонающее устройство 3, блок упр 6, дополнительно введены фор тель пороговых напряжений, г компараторов, регистр, шифра шифратор, цифровой коммутато ф-лы, 8 ил.Изобретение относится к вычислительной технике и может быть использовано при создании систем, производящих сбор и обработку аналоговых сигналов от многих датчиков, в частности обработку телеметрической инФормации.Целью изобретени является повышение точности цифровой обработки ана логовых сигналов за счет максимального приближения амплитуды сигнала к величине полной шкалы аналого-цифрового преобразователя.На фиг. 1 и 2 изображена блок схема предлагаемой системы, на фиг.3 - схема блока мультиплексирования и согласования входных сигналов; на фиг. 4 - схема блока масштабирования; на фиг. 5 - схема блока управ ления, на фиг. 6 - пример реализации схем блока регистров и шифратора; на фиг. 7 - пример дискретизации входного диапазона сигналов по уровням; на фиг. 8 - временные диа граммы работы блока управления.Цифроаналоговая система сбора и обработки информации содержит блок 1 мультиплексирования и согласования входных сигналов, аналого-цифровой 30 преобразователь 2, оперативное запоминающее устройство 3, блок 4 масштабирования, постоянное запоминающее устройство 5, блок 6 управления, дешифратор 7, формирователь 8 пороговых напряжений, группу компараторов 9, регистр 10, шифратор 11, цифровой коммутатор 12Блок мультиплексирования и согласования входных сигналов (Фиг. 3) 40 осуществляет сопряжение системы с первичными измерительными преобразователями информации (датчиками), Блок 1 содержит счетчик 13 адреса, дешифратор 14, мультиплексор 15, дифферен циальный усилитель 16, Блок 4 масштабирования содержит аналоговые коммутаторы 17 и 18, группу масштабных усилителей 19, Выходы счетчика 13 ац реса соединены с входами дешифратора 50 14 и являются выходом адреса входного сигнала мультиплексора, выходы которого соединены с входами дифференциального усилителя, выход которого является ВыхОдОм аналогоВого сигнала 55 блока 1 и соединен с информационным входом первого аналогового коммутатора блока масштабирования. Каждый выход первого аналогового коммутатора13632 выбрана интегральная схема типа521 САЗ, Регистр 10 реализован на П-триггерах.Шифратор построен на логических элементах, Схема шифратора выбирается в зависимости от количества разрядов регистра и от требуемого коли- чества разрядов на выходе шифратора. Пример реализации шифратора при шес ти 2-триггерах приведен на Фиг. 4.Цифровой коммутатор может быть реализован на интегральных схемах типа 564 КП 1. Масштабные усилители могут быть реализованы на интеграль ных цифроаналоговых преобразователях типа 572 ПА 1 (572 ПА 2) в различных вариантах включения.Цифроаналоговая система сбора и обработки информации работает следую щим образом. тора.Таким образом, каждому из И поддиапазонов на выходе шифратора соответствует свой определенный двоичный кад, с помощью которого информационный сигнал подключается к определенному масштабному усилитлю 19 группы, осуществляющему масштабное увеличение или уменьшение сигнала. Коэффициент передачи усилителей определяется циФровым кодом, псступающим на входы управления усилием, Данные циФровые коды записаны в ПЗУ 5 выходы которого подключены к соответствующим инфармацианньм входам цифрового коммутатора. Двоичный кад шифратора 11 поступает на вход управления цифрового коммутатора и в соответствии с заданным адресом на его выходе формируется цифровой код, поступающий на входы управлечия усиления масштабных усилителей, Промасштабированный информационный сигнал поступает на вход АЦП и через время определяемое линиями 20 и 21 задержки, блок управления выдает команду на начало преобразования. Величина задержки определяется временем, необходимым для выбора неабхадимага масштабного усилителя и его коэффициента преобразования.Таким образом, непосредственна перед каждым цифровым преобразованием аналогового сигнала в соответствии с его амплитудой на выходе шифратора формируется двсичный кад, с помощью каторога выбирается необходимый масштабный усилитель и ега коэффициент преобразования. Данные масштабные преобразования информационного сигнала обеспечивают амплитуду преобразованного сигнала на входе АЦП, максимальна приближенную к величине полной шкалы АЦП, что обеспечивает максимальную точность цифрового преобразования любого аналогового сигнала,Таким образом, изменение амплитуды сигнала датчика в произвольный момент времени приводит к автоматическому изменению алгоритма предварительной обработки дачного сигнала.Цифровая информация АЦП поступает на первые информационные входы ОЗУ, Адрес ячейки ОЗУ, куда записывается цифровая информация входного сигнала в данный момент времени и соответствующий ей кад коэффициента передачи,Управление работой мультиплексора 15 осуществляется счетчиком 13 адреса и дешифратором 14 по сигналам бло ка 6 управления. Информационный сигнал выбранного датчика через дифференциальный усилитель 16 поступает на вход аналогового коммутатора 17 и на входыкампараторов 9 группы. Уп- З 0 равление работой аналогового коммутатора осуществляется цифровым кадом, поступающим на его управляющий вход, Формирование данного кода производится с помощью блоков 8 - 11, Формиро 35 ватель 8 пороговых напряжений задает на входах компараторов 9 группы напряжения, с помощью которых максимальна допустимый для системы диапазон изменения амплитуды входных сиг налов разбивается на И ноддиапазонав с произвольной дискретностью. На фиг, 7 показан один из возможных вариантов разбивки на поддиапазоны. С помощью компараторов определяется в каком из поддиапазонов находится в данный момент времени информационный сигнал. Таким образом, для определенной амплитуды входного сигнала в каждый момент времени на выходе всех50 М кампараторов группы формируется определенный параллельный единичный код, определяющий в каком из поддиапазонав находится входной сигнал. Па сигналу блока управления параллельный кад фиксируется регистром 10 и преобразуется шифратором 11 в двоичный код. Полученный двоичный код управляет работой аналоговых коммутаторов 71 4 17 и 18 и работой цнфравага каммута5 136327 1поступающий с выхода цифрового коммутатора, определяется состоянием счетчика 13 и дешифратора 7, По фронту сигнала "Конец преобразования" входная информация ОЗУ записывается в соответствующую ячейку ОЗУ, и по спаду этого же сигнала блок управления выдает команду на смену опрашиваемых каналов. 10Выдача данных из ОЗУ во внешнее устройство обработки и отображения информации происходит по сигналам блЬка управления, формируемым с по - мощью генератора 23 импульсов, ре гистра 2 ч сдвига, формирователей 22 импульсов. формула изобретения201. Цифроаналоговая система сбора и обработки информации, содержащая постоянное запоминающее устройство, блок управления, блок мультиплексирования и согласования входных сиг налов и блок масштабирования, выход которого соединен с информационным входом аналого-цифрового преобразователя, выход которого соединен с первым информационным входом опера - 30 тивного запоминающего устройства, выход которого является выходом системы, первый, второй и третий выходы блока управления соединены соответ- ственнЬ с входом приращения адреса блока мультиплексирования и согласования входных сигналов, стробирующим входом аналого-цифрового преобразователя и входом считывания оперативного запоминающего устройства, 40 причем информационные входы блока мультиплексирования и согласования входных сигналов являются информационными входами системы, выход аналогового сигнала блока мультиплексирования и согласования входных сигналов соединен с информационным входом блока масштабирования, о т лч а ю щ а я с я тем, что, с целью повышения точности цифровой обработки аналоговых сигналов за счет максимального приближения амплитуды сигнала к величине полной шкалы аналогоцифрового преобразователя, в нее введены формирователь пороговых напряжений, группа компараторов, регистр, шифратор, дешифратор, цифровой коммутатор, управляющий вход которого .соединен с выходом шифратора и с входом выбора диапазона изменения сигнала, блока масштабирования, выход адреса входного сигнала блока мультиплексирования и согласования входных сигналов соединен с входом дешифратора, выход которого соединен с адресным входом оперативного запоминающего устройства, вход записи которого соединен с входом запуска блока управления и с выходом готовности аналого-цифрового. преобразователя, выход цифрового коммутатора соединен с вторым информационным входом оперативного запоминающего устройства и с входом установки коэффициента преобразования блока масштабирования, выходы постоянного запоминающего устройства соединены с информационными входами цифрового коммутатора, выходы формирователя пороговых напряжений соединены с первыми входами соответствующих компараторов группы, вторые входы которых объединены и соединены с выходом аналогового сигнала блока мультиплексирования и согласования входных сигналов, выходы компараторов группы соединены с соответствующими разрядами информационного входа регистра, тактовый вход которого соединен с четвертым выходом блока управления, выход регистра соединен с входом шифратора, причем вход формирователя пороговых напряжений является входом опорного напряжения системы.2, Система по п. 1, о т л и ч а - ю щ а я с я тем, что блок масштабирования содержит первый и второй аналоговые коммутаторы, группу масштабных усилителей, информационный вход первого аналогового коммутатора является информационным входом блока масштабирования, выход которого соединен с выходом второго аналогового коммутатора, вход диапазона изменения сигнала блока масштабирования соединен с управляющими входами первого и второго аналоговых коммутаторов, выходы первого аналогового коммутатора соединены с информационными входами масштабных усилителей группы, входы управления усилением которых соединены с входом установки коэффициента преобразования блока ,масштабирования, выходы масштабных усилителей группы соединены с информационными входами второго аналогового коммутатора.

СмотретьЗаявка

4090663, 16.05.1986

ПРЕДПРИЯТИЕ ПЯ Г-4149

СМИРНОВ СЕРГЕЙ ВАСИЛЬЕВИЧ, КОЛОМБЕТ ЕВГЕНИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 3/00

Метки: информации, сбора, цифроаналоговая

Опубликовано: 30.12.1987

Код ссылки

<a href="https://patents.su/8-1363271-cifroanalogovaya-sistema-sbora-i-obrabotki-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Цифроаналоговая система сбора и обработки информации</a>

Предыдущий патент: Устройство для моделирования тиристорно-диодной группы

Следующий патент: Устройство для идентификации магнитных жетонов

Случайный патент: Устройство для очистки скважин