Устройство для вычисления функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

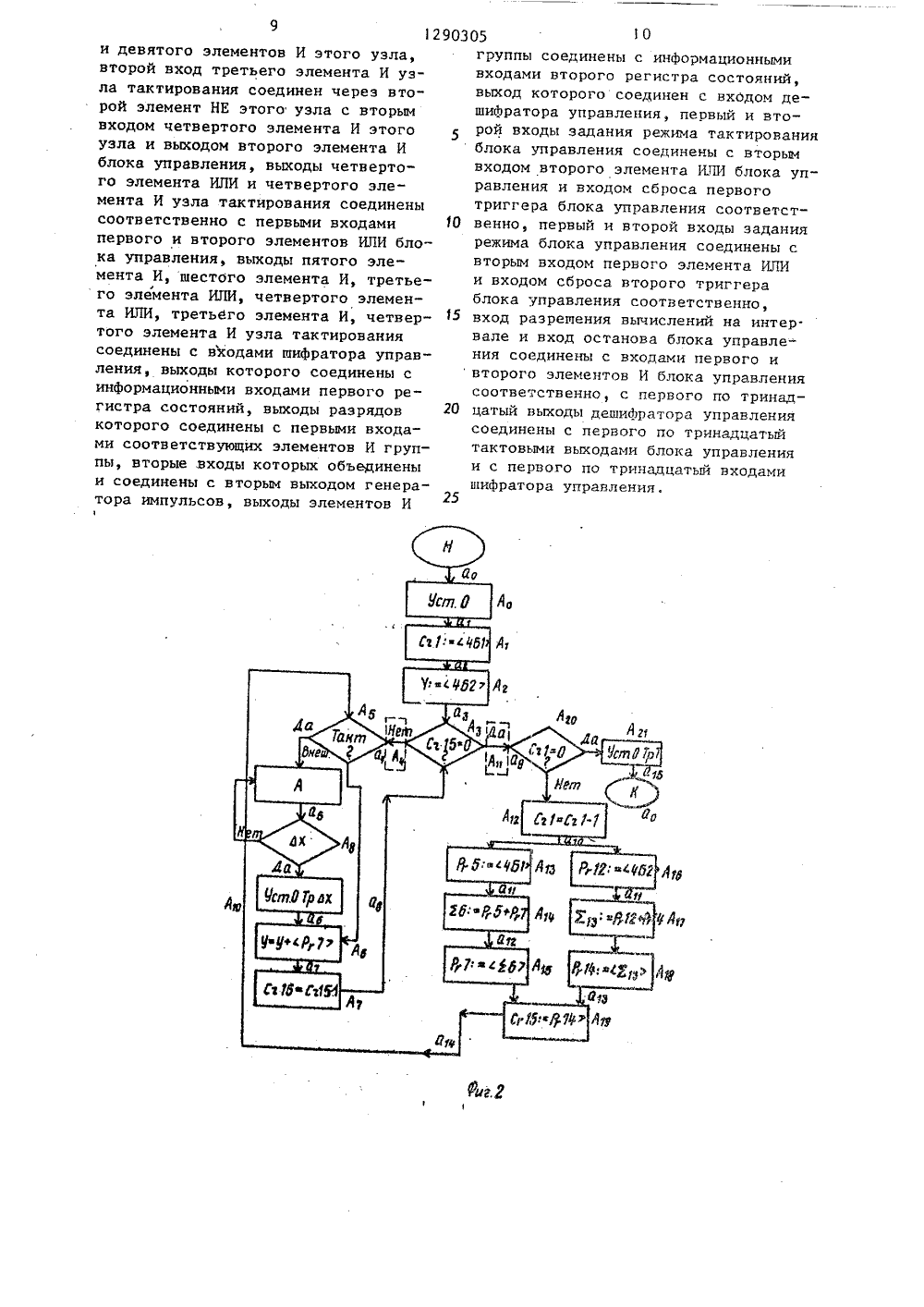

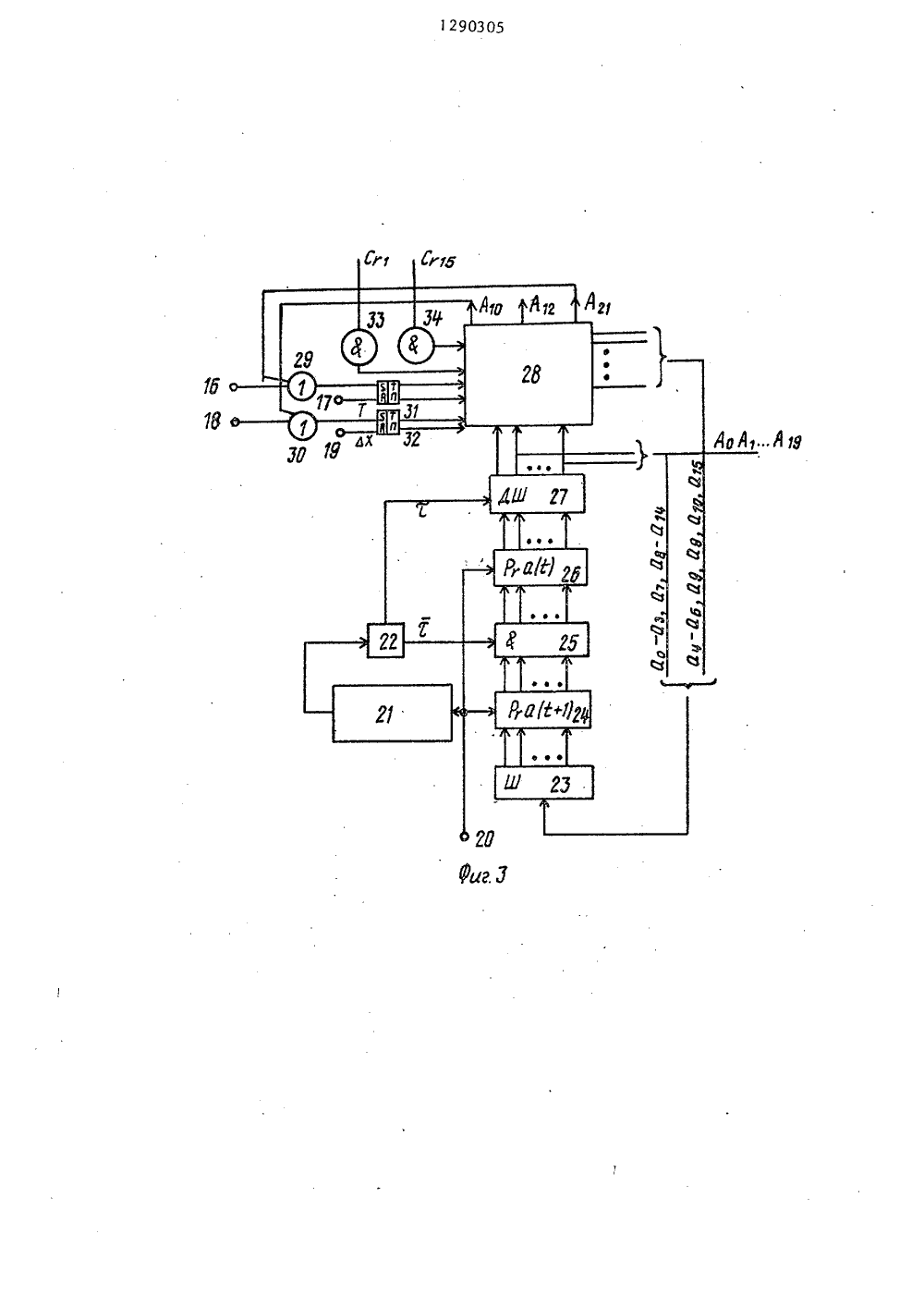

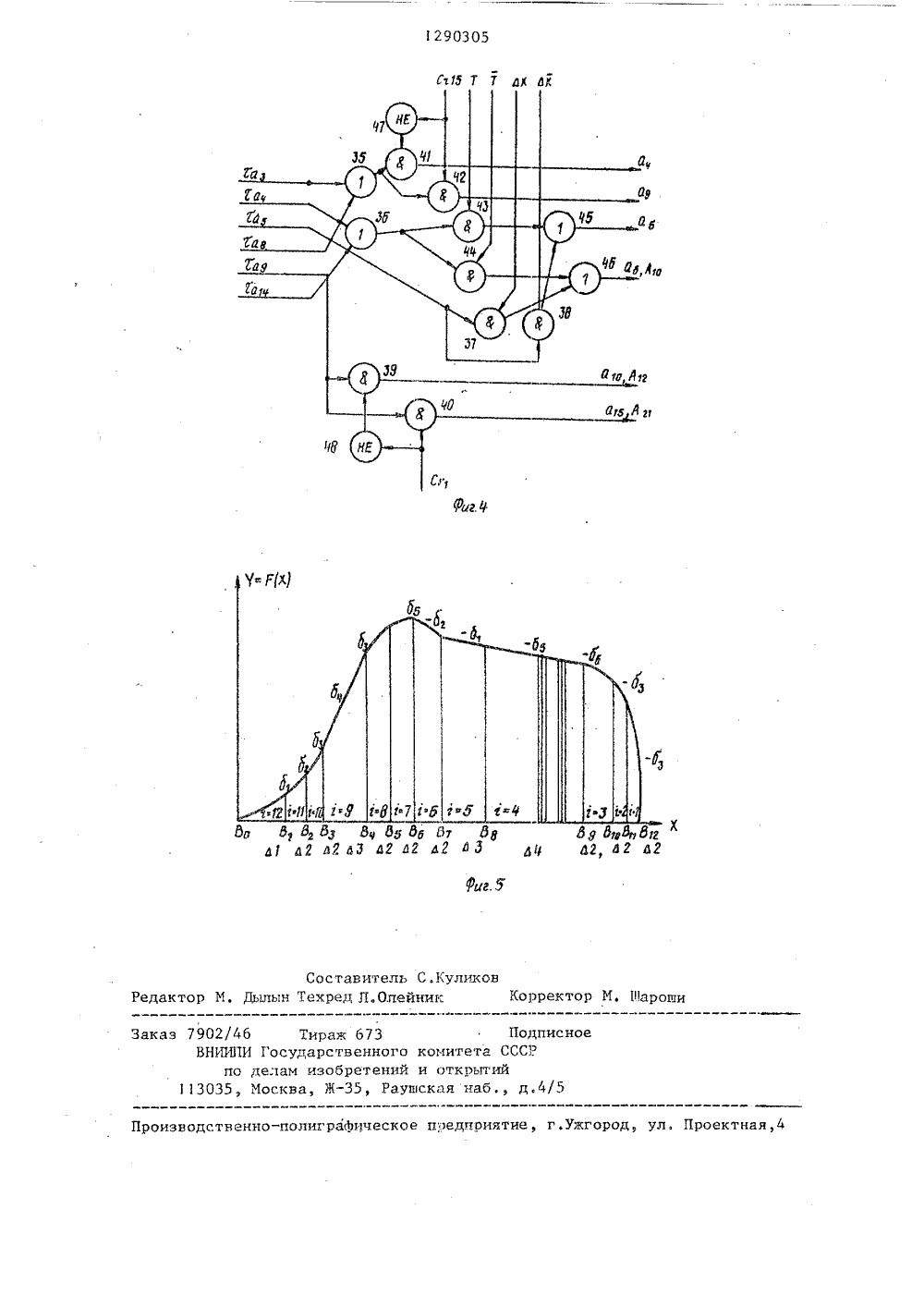

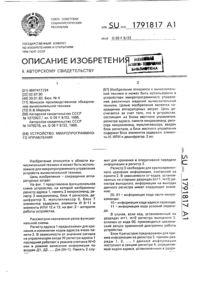

(5 4 С 0 ЕТЕНИЯ иг,7 ГОСУДАРСТВЕННОЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗ АВТОРСКОМУ СВИДЕТЕЛЬСТ(56) Авторское свидетельство СССР Р 579622, кл. С 06 Р 15/32, 1975.Мухопад Я.Ф. Нроектирование специализированных микропроцессорных вычислителей. - Новосибирск: Наука, 1981, с.37.(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ(57) Изобретение относится к области вычислительной техники и может быть использовано как функциональный преобразователь в реальном масштабе времени. Цельн изобретения является повышение точности воспроизведевл. В ббирский технологичесния значений Функции при заданных объемах памяти за счет увеличения числа узловых точек значением функции. Устройство для вычисления функции содержит счетчик 1 интервалов, дешифратор 2, первый шифратор 3, блок 4 памяти приращения функции, первый буферный регистр 5, первый сумматор б, первый регистр 7 итерации, регистр 8 результатов, блок 9 управления, второй шифратор 10, блок 1 памяти приращения аргумента, второй буферный регистр 12, второй сум 1 матор 3, второй регистр 14 итерации, счетчик 15 адреса. В блоках 4 и 11 памяти хранятся принципиально различные значения приращения функции и аргумента. Восстановление значения Функции происходит суммированием величин приращения и предыдущего значения Функции. 5 нл.129Изобретение относится к вычислительной технике и может быть исполь зонано в инФормационно-измерительных и управляющих системах при выполнении функциональных преобразований в реальном масштабе времени.Цель изобретения - повьппение точности воспроизведения функции при заданных объемах памяти за счет увеличения числа узловых точек значений функции.На Фиг. представлена функциональная схема устройства для вычисления функции; на фиг.2 - алгоритм Функционирования устройства; на Фиг.3 - схема блока управления; на Фиг.4 - схема узла тактирования; на фиг.5 - пример задания функции у = Р (х).Устройство для вычисления функции содержит счетчик 1 интервалов, дешифратор 2, первый шифратор 3 адреса блок 4 памяти приращений функции, первый буферный регистр 5, первый сумматор 6, первый регистр 7 итераций, регистр 8 результата, блок 9 управления, второй шифратор 10 адреса, блок 11 памяти приращений аргумента, второй буферный регистр 12, второй сумматор 13, второй регистр 14 итерации, счетчик 15 адреса.Блок 9 управления содержит первый 16 и второй 17 входы задания режима тактирования, первый 18 и второй 19 входы задания режима приращения аргумента, вход 20 запуска, элемент 21 задержки, генератор 22 импульсов, шифратор 23 управления, первый регистр 24 состояния, группу элементов И 25, второй .регистр 26 состояния, дешифратор 27 управления, узел 28 тактирования, второй 29 и первый 30 элементы ИЛИ, первый 31 и второй 32 триггеры, второй 33 и первый 34 элементы И.Узел 28 тактиронания содержит первый 35 и второй 36 элементы ИЛИ, первый 37 и второй 38 элементы И, третий 39 и четвертый 40 элементы И, пятыи 41, шестой 42, седьмой 43, восьмой 44 элементы И, третий 45 и четвертый 46 элементы ИЛИ, первый 47 и второй 48 элементы НЕ.Устройство Функционирует следующим образом.1На Аиг.5 представлен пример графика воспроизводимой Функции у = = Р(х),где обозначено:о , д0305 5 10 15 20 25 30 35 40 45 8 - значения постоянных приращений, которым соответствуют приращения адресоя В В В, (г=9,1ш=12);- разность приращений Функций у на-м и .-1-м интервале,т.е. 1, = 1: - 5 ; и. - приращение ад 1 фресов при смене о, ; В., - разностьприращений адресов на-м и -1-минтернале, т. е. К, = (й, - ,ь)Эти номера 1. = ш,пт 2, 1, 0являются содержимым счетчика 1 интервалов, причемпри переходек новомуинтервалу блока 9 управления выдает сигнал вычитания единицы из содержимогосчетчика 1 интервалов. Величины К;,состанпяют содержимое блока 11 памяти приращений аргумента, причем адресом для этого блока памяти является унитарный код (порядковый номерполученный после дешиАратора 2) .Для сокращения объема блока 11 памя -ти приращений аргумента н нем хранятся только различные Б., (не равныедруг другу , поэтому вьгходы дешифра-тора 2 б адресуемые к одному итому же значению В объединяютсявторым шиАратором О,Аналогично в блоке 4 памяти приращения Аункции хранятся различные значения 1 езностей от приращений Аункций 33 б, т,е. ц,=6,Хотя закон смени приращений адресови изменения заданной Функции определяется видом самой Функции Г(х) величины изменения значения Аункции иизменения адреса практически всегдане совпадают по значениям ,(совпадения могут быть лищь на тех участках,где производная Функции равна величине изменения адресов аргумента),поэтому выходы дешиАратора 2 первымшифратором 3 рбъединяются по свое-му правилу, в общем случае отличному от правила второго шийратора 10для заданной Аункции реального времени.1Работа устройства осуществляется в строгой алгоритмической последовательности (Аиг,2). После сигнала "Пуск" по входу 20 блок 9 управления производит установку всех регистров Рг 5,7,8,12 и 14 и счетчиков Сч, Сч 15 в исходное (нулевое)Гсостояние оператор А ). Затем избчислового блока 4 памяти приращений Функции производится считывание содержимого нулевого адреса (операто3 1290305 ра А ) и запись в счетчик 1. В нулевом адресе блока 4 памяти приращений функции. хранится увеличенное на 1 количество интервалов функции Р(х), а в нулевом адресе блока 11 памяти приращений аргумента - начальное значение у, котврое,направляется в регистр 8 результата (оператор А,1, Далее осуществляется проверка содержимого счетчика 15 адреса. Если.содер- О жимое Сч 5 равно нулю (это бывает только в начале работы или в конце очередного интервала Р(х) , то из содержимого счетчика 1 интервалов вычитается 1 (оператор А и осуще ствляется параллельное считывание из блоков 4 и 11 памяти с соответствующим выводом значений ц и К. в1 1 буферные регистры 5 и 12 и затем также параллельно производится сумми рование значений Рг 5 + Рг 7 и Рг 2 + + Рг 14 и вьвод результатов в Рг 7 и Рг 14 (операторы А - А и А - А1 Э 15 16 1 Я Содержимое Рг 14 (количество отсчетов на данном 1-м интервале) записы) вается в Сч 15,после чего производится проверка, поотупил ли запрос на выдачу очередного значения Р(х) (оператор А, . Если запрос поступил, то производится вычисление значения 30 У = у .5; (оператор А), значение счетчика, хранящего количество отсчетов на 1,-м интервале, уменьшается на 1,Сч 5 = Сч 15-1) и производится сорос в нулевое состояние 35 второго триггера блока 9 управления (оператор А ), после чего весь алгоритм повторяется с проверки содержимого счетчика 15 адреса. 40 Предлагаемое устройство может работать как с внутренним, так и с . внешним тактированием за счет нали.чия специальных входов 16 и 17. При работе с внутренним тактированием 45 сигнал "1" на вход не подается, следовательно, первый триггер 3 устройства управления остается в нулевом состоянии и работа устройства управления осуществляется по алгоритму 50 с прямым переходом от состояния аз к состоянию а . Если устройство для5вычисления тактов предполагается использовать с внешним тактированием, перед командой "Пуск" по входу 17 подается команда установки первого триггера 31 блока управления в состояние В последнем случае устройство может работать с переменным интервалом (шагом вычисления . Устройство управления имеет дополнительный вход 16 для внешнего сброса первого триггера 31 в "0" (внутреннийсброс оператором производится автоматически в конце работы, А ,), чтопозволяет, используя входы 16, 17и 19 работать также в режиме внешнего пуска, приостановки и продолжения счета с автоматическим тактированием, начиная с любой промежуточнойточки значения Р (х),Устройство вычисления функций ра- ботает в соответствии с алгоритмом ( фиг.2), согласно которому блок 9 управления находится в ожидании сигнала внешнего тактирования (в данном случае временной метки, частота поступления которой может быть на несколько порядков ниже тактовой частоты работы блока управления), после его получения из счетчика адреса 15 производится вычитание 1. Если при этом расчет производится внутри 1-го интервала (содержимое счетчика отлично от нуля), то производится считьвание приращенияалгебраическое сложение его (сложение или вычитание) с предыдущим значением функции, хранящимся в первом регистре 7 итерации, и запись полученного значенияв регистр 8 результата. В случае конца 1 -го интервала одновременно с процессом нахождения значения функции находится величина очередного +1-го интервала, для этого также производятся операции, что и для У с блоком памяти приращений аргумента, вторым сумматором 13 и вторым регистром 14 итерации, после чего новое значение интервала в параллельном коде записьвается на счетчик 15 адреса, а из счетчика 1 интервалов вычитается 1 для изменения номера интервала. Затем в блоке управления производит ся проверка не появился ли сигнал окончания и является ли этот сигнал окончания признаком завершения программы расчета всех значений функции, тогда производится начальная установка триггера внешнего тактирования, Если прерывание является внешним сигналом, устройство переходит в режим ожидания следующего поступления сигнала дх, сохраняя содержимое всех регистров памяти и счетчиков.10 15 20 25 30 с 5 5055 7 1 г управления, первый и второй входы задания режима тактирования устройства соединены с одноименными входами блока управления, первый и второй входы задания режима приращения аргумента устройства соединены с одноименными входами блока управления, первый тактовый выход блока управления соединен с входами сброса счетчика интервалов, счетчика адреса, первогои второго буферных регистров, первого и второго регистров итерации и регистра результата, второй тактовый выход блока управления соединен с входом разрешения записи счетчика интервалов, третий тактовый выход блока управления соединен с входом разрешения записи регистра результата, четвертый тактовый выход которого соединен со стробирующим входом первого регистра итераций, пятый тактовый выход блока управления соединен с входом . вычитания счетчика адреса, шестой тактовый выход блока управления соединен с входом вычитания счетчика интервалов, седьмой и восьмой тактовые выходы блока управления соединены со стробирующими входами соответственно первого и второго буферных регистров, девятый и десятый тактовые выходы блока управления соединены со стробирующими входами соответственно первого и второго сумматоров, одиннадцатый и двенадцатый тактовые выходы блока управления соединены с входами разрешения записи соответственно первого и второго регистров итерации, тринадцатый тактовый выход блока управления соединен с входом разрешения записи счетчика адреса, причем блок управления содержит два регистра состояния, дешийратор управления, шифратор управления, группу элементов И, элемент задержки, генератор импульсов,два ,элемента ИЛИ, два элемента И, два триггера и узел тактирования, содержащий четыре элемента ИЛИ, восемь элементов И и два элемента НЕ, причем вход запуска блока управления соединен с входами сброса первого и второго регистров состояния и через элемент задержки - с входом запуска генератора импульсов, первый выход которого соединен со стробирующим входом дешийратора управления, выход признака сброса устройст 90305 Я ва которого соединен с первым тактовым выходом блока управления, первыйи второй выходы признака начальнойустановки дещийратора управления соединены соответственно с вторым итретьим тактовыми выходами блокауправления, выход признака разрешения вычислений на интервале дешийратора управления соединен с первымвходом первого элемента ИЛИ узла тактирования, выход признака внешнеготактирования дешийратора управлениясоединен с первым входом второго элемента., ИЛИ узла тактирования, выходпризнака переменного шага приращенийдешифратора управления соединен спервыми входами первого и второгоэлементов И узла тактирования,выходпризнака разрешения вычислений наинтервале дешифратора управлениясоединен с вторым входом первого элемента ИЛИ узла тактирования, выходпризнака останова вычислений дешифратора управления соединен с первымвходом третьего элемента И и с первым входом четвертого элемента Иузла тактирования, выход признакавнещнего тактирования дешийраторауправления соединен с вторым входомвторого элемента ИЛИ узла тактирования, выход первого элемента ИЛИ узлатактирования соединен с первыми входами пятого и шестого элементов Иэтого узла, второй вход пятого элемента И узла тактирования соединенчерез первый элемент НЕ этого узла с выходом первого элемента И блока управления и вторым входом шестого элемента И узла тактирования, выходвторого элемента ИЛИ узла тактирования соединен с первыми входами седьмого и восьмого элементов И этого узла, вторые входы седьмого и восьмого элементов И соединены соответственно с прямым и инверсным выходами первого триггера блока управления, вторые входы первого и второгоэлементов И узла тактирования соединены соответственно с прямым и инверсным выходами второго триггераблока управления, выходы седьмого ивосьмого элементов И узла тактирования соединены с первыми входамитретьего и четвертого элементов ИЛИэтого узла соответственно, вторыевходы третьего и четвертого элементов ИЛИ узла тактирования соединенысоответственно с выходами восьмого12903и девятого элементов И этого узла, второй вход третьего элемента И узла тактирования соединен через вто" рой элемент НЕ этого узла с вторым входом четвертого элемента И этого узла и выходом второго элемента И блока управления, выходы четвертого элемента ИЛИ и четвертого элемента И узла тактирования соединены соответственно с первыми входами Ю первого и второго элементов ИЛИ блока управления, выходы пятого элемента И, шестого элемента И, третьего элемента ИЛИ, четвертого элемента ИЛИ, третьего элемента И, четвертого элемента И узла тактирования соединены с входами шифратора управления, выходы которого соединены с информационными входами первого регистра состояний, выходы разрядов которого соединены с первыми входами соответствующих элементов И группы, вторые входы которых объединены и соединены с вторым выходом генера 25 тора импульсов, выходы элементов И 1 05 0группы соединены с информационными входами второго регистра состояний, выход которого соединен с вхОдом дешифратора управления, первый и второй входы задания режима тактирования блока управления соединены с вторым входом второго элемента ИЛИ блока управления и входом сброса первого триггера блока управления соответственно, первый и второй входы задания режима блока управления соединены с вторым входом первого элемента ИЛИ и входом сброса второго триггера блока управления соответственно, вход разрешения вычислений на интер. вале и вход останова блока управления соединены с входами первого ивторого элементов И блока управления соответственно, с первого по тринадцатый выходы дешифратора управления соединены с первого по тринадцатый тактовыми выходами блока управления и с первого по тринадцатый входами шифратора управления.1290305 Ст 15 Т Т аХ И Ьч Ъбо 8 ду ддодай 2 д 2 Ю 23 11 Д 2 ЙГ йЯ Составитель С.КуликовДылын Техред Л.Олейник Коррект 1 паропи дакто ак Производственно-полиграФическое предпринтие, г.ужгород, ул. Проектна 7902/46 Тираж б 73ВНИИПИ Государственногопо делам изобретений13035, Москва, Ж, Рау Подписноекомитета ССС 1и от к рътГ ийскан наб д,4/5

СмотретьЗаявка

3931257, 17.07.1985

ВОСТОЧНО-СИБИРСКИЙ ТЕХНОЛОГИЧЕСКИЙ ИНСТИТУТ

МУХОПАД ЮРИЙ ФЕДОРОВИЧ, СМОЛОВ ВЛАДИМИР БОРИСОВИЧ

МПК / Метки

МПК: G06F 7/544

Метки: вычисления, функции

Опубликовано: 15.02.1987

Код ссылки

<a href="https://patents.su/8-1290305-ustrojjstvo-dlya-vychisleniya-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления функции</a>

Предыдущий патент: Устройство для умножения

Следующий патент: Устройство для реализации алгоритма волдера

Случайный патент: Способ очистки фосфорной кислоты