Процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

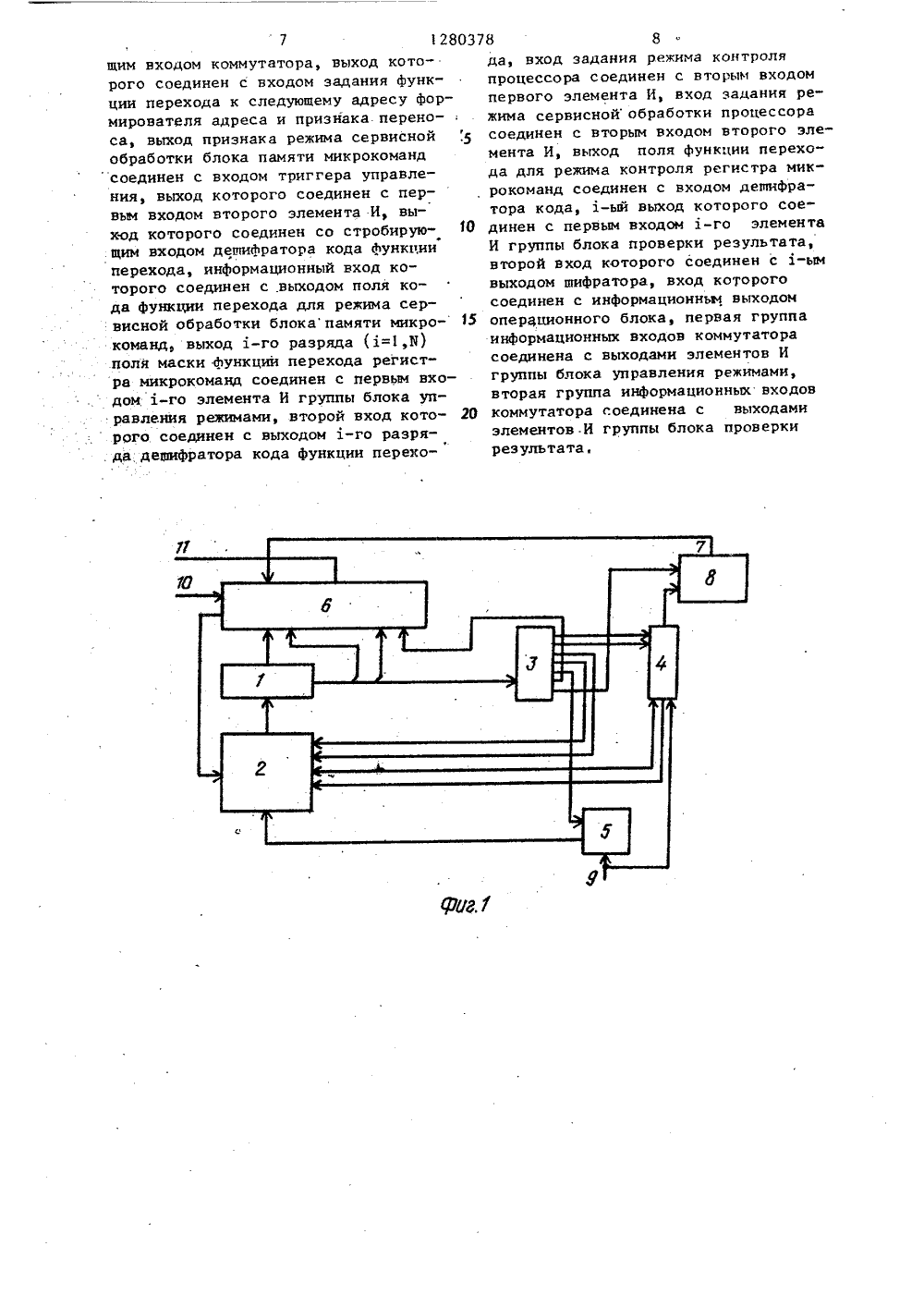

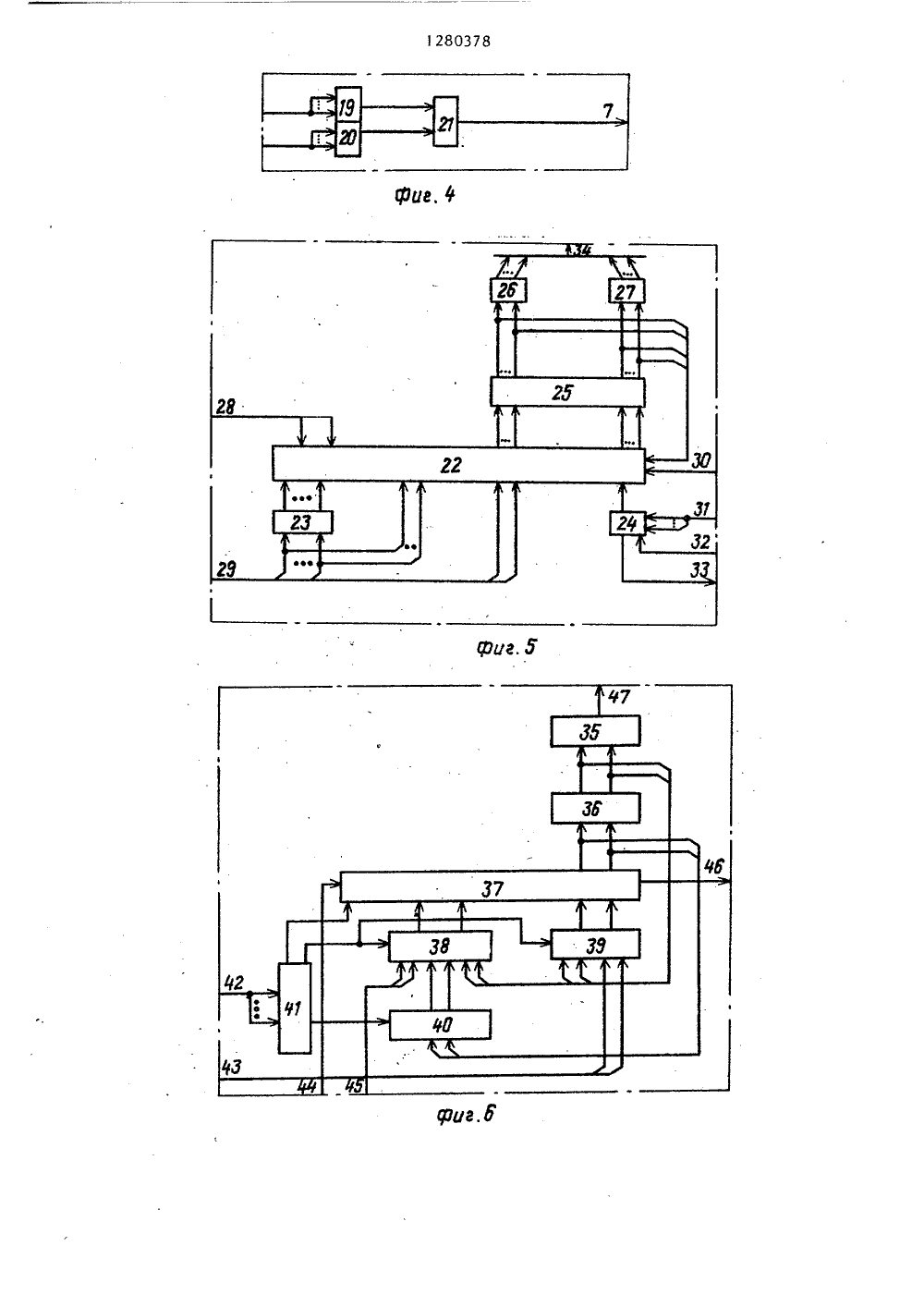

ем тег раей.Вь,о00 с 1 981 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ АВТОРСКОМУ СВИДЕТЕЛЬСТВ(.57) Изобретение относится к вычислительной технике и может быть использовано при построении специализированных микроЭВМ малого объема .и большого быстродействия. Цепьизобретения - увеличение быстродействия. Процессор содержит формирователь 2 адреса и признака переноса,блок 1 памяти микрокоманд, регистр3 микрокоманд, операционный блок 4,блок 5 маскирования кода операции,блок 8 проверки результата, блок 6управления режимами. За счет введения блока проверки результата и блока управления режимами достигаетсяцель изобретения. 8 ил.40 45 5012Изобретение относится к вычислительной технике и может быть использовано при построении специализированных микроЭВМ малого объема и высокой надежности.Цель, изобретения - увеличение быстродействия,На фиг. 1 приведена структурнаясхема процессора, на фиг. 2 - функциональная схема блока управлениярежимами, на фиг. 3 - алгоритм контроля процессора, на фиг. 4 - функциональная схема блока проверки результатаф на фиг. 5 - схема формиро"вателя адреса и признака переноса;на фиг, 6 - схема одной секции операционного блока, на фиг. 7 - схемаблока маскирования кода операции 1 нафиг, 8 - таблица истинности шифратораПроцессор содержит блок 1 памятимикрокоманд, формирователь 2 адресаи признака переноса, регистр .3 микрокоманд, операционный блок 4, блок5 маскирования кода операции, блок6 управления режимами, выход 7 блока 8 проверки результата, вход 9данных, вход 10 задания режима контроля, вход 11 задания режима сервисной обработки,Блок 9 управления режимами состоит из коммутатора 12, груйпы 13 элементов И, первого элемента И 14,триггера 15 контроля, триггера 16 управления, второго элемента И 17 и дешифратора 18 кода функции перехода,Блок 8 проверки результата образуютдешифратор 19 кода, шифратор 20 игруппа 21 элементов И.формирователь 2 адреса и признакапереноса выполнен в виде одной БИС(например, 589 ИК 01) и содержит коммутатор 22 адреса микрокоманд, регистр 23 команд, коммутатор 24 состояний, регистр 25 адреса микроко-манд, первый 26 и второй 27 формирователи адреса микрокоманд, вход28 задания функции перехода к следующему адресу, вход 29 задания.адреса начала микропрограммы, вход 30признака прямой адресации, вход 31установки признака условнОго перехода, вход 32 признака условного перехода, выход 33 признака переноса иадресный выход 34,Операционный блок 4 состоит изсекций, например 589 ИКО 2, каждая изкоторых содержит выходной регистр35, накапливающий регистр 36, сум 80378 г матор 37, первый 38 и второй 39 входные мультиплексоры, регистровую сверхоперативную память 40, дешифратор 41 микроопераций, вход 42 кода операции операционного блока, вход 43 кода маски операционного блока, вход 44 переноса, информационный вход 45, выход 46 переноса и информационный выход 47Блок 5 маскирования кода операции .содержит дешифратор 48, элементы И 49, информационный вход 50, вход 5 управления маскированием и выход 52.Процессор работает следующим образом.При выполнении управляющей программы первый и второй управляющие входы находятся в нулевом состоянии, нулевое состояние на выходеэлемента И 14 разрешает работу коммутатора 12 по вторым его входам.Нулевое состояние на выходе элемента И 17 устанавливает выходы дешифратора 18 в единичное состояние,разрешая передачу через группы 3элементов И и коммутатор 12 информации с выхода блока 1 памяти микрокоманд,Микрокоманды, управляющие работой процессора на каждом такте, хранятся в блоке 1 памяти микрокоманд исчитываются на регистр 3 микрокоманд.Адресная часть микрокоманды, участЗ 5,вующая в формировании адреса следующей микрокоманды, поступает кроме регистра 3 через открытую группу 13 элементов И и коммушатор 12 по входу 28 блока 2 на вход коммутатора 22 адреса микропрограмм.Формирование адреса следующей микрокоманды производится коммутатором 22 из семиразрядйого входного кода УО-У 6, адреса текущей микрокоманды МО-М 8, поступающей с выхода регистра 25 и кода состоянийтриггеров коммутатора 24 (ш,С,Е)Регистр 3 микрокоманд имеет несколько полей, коды которых задают режимработы блоков процессора. Для управления блоком 4 используются кодыпервого (операционное поле регистрамикрокоманд) и второго (кода. маскиоперационного поля)выходов регистра 3 микрокоманд, которые поступаютсоответственно на вход дешифратора4 микроопераций и мультиплексора39. Код с третьего выхода -(признак условного перехода) регистра 33 1280 микрокомацд управляет процессом обме- на информацией между блоком 2 микропрограммного управления и операционным блоком 4 (запись через вход переноса блока 2 в коммутатор 24 состояний сигналов переноса из блока 4 и выдача сигнала с выхода коммутатора 24 состояний на вход 44 блока 4). Блок 4 получает информацию с входа 9 процессора через мультиплек- Ю сор 38 и производит ее обработку в сумматоре 37. Результаты с выхода регистра 35 поступают на выход 47 данных блока 4 и чераз блок 8 выдаются на блок управления режима (пер вые входы коммутатора 12) и на выход данных блока 4. В процессоре используется метод конвейерной обработки информации, поэтому цикл выполнения текущей микрокоманды в бло ке 4 совмещается с формированием адреса следующей микрокоманды в блоке 2 и ее выборкой из блока 1 памяти микропрограмм. Для обращения к началу микропрограммь 1 операции использу ется код операции КО-К 7, поступающий из внешней памяти команд на вход 9 и далее через блок 5 маскирования кода операции в блок 2 (вход 29). При наличии в микрокоманде признака пря О мой операции, поступающего с четвертого выхода регистра 3 микрокоманд через вход 30 блока 2 на вход коммутатора 22, Формирование адреса следующей микрокоманды производится только по коду операции. При этом количество разрядов, участвующих в формировании адреса, зависит от кода управления, поступающего с пятого выхода (код маски поля операции) регистра 3 микрокоманд на вход 51 де. - шифратора 48 блока маскирования кода операции. Так при наличии сигнала на первом выходе дешифратора 48 на вход коммутатора 22 блока 2 с элементов И 49 поступают только шесть младших разрядов кода операции, а на двух старших устанавливаются принудительно нули, При наличии сигнала на втором выходе дешифратора 48, на 50 оборот, нули устанавливаются в шести младших разрядах кода операции, Таким образом, появляется возможность разветвления управляющей микропрограммы,: 178 Информация с выхода 47 поступаетна вход блока анализа прохождения 55 рабочей программы (не приведен),в некотором данные на выходе 47 сравниваются по сигналу с блока 1 памяти микропрограмм (поле пользователя не показано) с эталонным значением. При необходимости работы с сервисными программами на вход 11 подается уровень 1", поступающий на вход элемента 17 И, В последней микрокоманде команды управляющей про -граммы записан признак перехода насервисную подпрограмму (например,считывание внутренних регистров операционного блока), который по соответствующему входу блока 6 управления режимами записывается в триггер16 и через элемент 17 И поступаетна стробирующий вход дешифратора 18.На информационные входы дешифратора18 поступает информация с шестоговыхода (поле маски функции перехода) регистра 3 микрокоманд, указывающая маску управления коммутацией,т.е. с выхода дешифратора 18 маскируются на элементе И 13 некоторыеразряды адреса следующей микрооперации, т,е, Формируется переход на сервисную программу,Алгоритм контроля процессора приведен ца фиг, 3. При выполнении управляющей программы происходит анализусловия 11. В зависимости от признака условия процесс вычисления осуществляется за время , или. Приусловии , ) ь время (в) можно исг 4пользовать для программы контроляработы процессора. Контроль осуществляется следующим образом. В конце программы 2 вычисления результатвычисления записывается в ОЗУ управляющей микроЧВМ (не показацо). После этого устанавливается в единичное состояние признак контроля результата вычисления (вход 10 процессора), Начинается выполнение программы проверки процессора на уровне микропрограмм (в системе командуправляющей микроЭВМ может быть специальная команда "Контроль процессора ). Микропрограмма осуществляетнад этой информацией разные операции (запись во внутренние регистры,сложение, сдвиги, вычитания, выдачасодержимого регистров на выход операционного блока и др,). В зависимости от состояния выхода операционного блока, скорректированная информация на блоке 8 режима проверкирезультата служит для управления коммутацией (УАО-УА 6) блока микропрограммного управления.5 1280378 6Так как время выполнения управля- операционный блок, формирователь адющей программы ограничено временем реса и признака переноса, блок мас- ( -) контроль работы процессора кирования кода операции, причем вход2должен выполняться по частям. При данных процессора соединен с информаэтом таблица истинности шифратора 20 5 ционным входом операционного блока может иметь вид, приведенный на фиг.8 и информационным входом блока масгде в зависимости ат диапазона по- кирования кода операций, выход коступившей информации а 1-а на выходе торого соединен с входом задания адформируется адно из значений Ьр, ко- реса начала микропрограммы формироторое вместе с информацией на вьжо вателя адреса и признака переноса, де дешифратора 19 формирует на гРУп- адресный выход которого соединен с пе элементов И 21 адрес следующей адресным входом блока памяти микромикрокоманды. Разбитие на группы обу- команд, выход признака переноса словлено тем, что в зависимости от формирователя адреса и признака пере- значения на входе шифратора 20 мож- ,15 носа соединен с входом переноса опе-. но создать оптимальную программу кон- рационного блока, выход операционнотроля процессора в диапазоне чисел, го поля регистра микрокоманд соедивычисленных в рабочей программе, - нен с входом кода операции операционШифратор 20 преобразует и разря- ного блока, выход кода маски операдав шины данных (выход 47 операцион ционного поля регистра микрокоманд ного блока 4) в семь разрядов УАО- , соединен с входом кода маски операУА 6 (вход 28 блока 2). ционного блока, выход признака пряВ режиме контроля на управляющий мой адресации регистра микрокоманд вход 10 поступает уровень "1". На соединен с входом признака прямой шифраторе кода 20 происходит преоб адресации формирователя адреса и разование выхода информации, вход ка- признака переноса, выход признака усторой. вместе с дешифрированными раз-, ловного перехода регистра микрокорядами (на дешифраторе 19) с седьмых манд соединен с входом установки, выходов поля кода функции переходапризнака условного перехода формиродля режима контроля регистра 3 микро вателя адреса и признака переноса, команд служат для формирования адре- вьдход кода маски поля операции ре са следующей микропрограммы (на груп- гистра микрокоманд соединен с входом пе элементов И 21). управления маскированим блока масВ этом режиме в последней микро- кирования кода операции, выход прикоманде команды управляющей програм- знака переноса операционного блока мы записан признак контроля операци- соединен с входом признака условноонного блока, который записывается го перехода формирователя адресаив триггер 15 и через элемент И 14 по- признака перейоса, выход блока памяступает на управляющий вход коммута- ти микрокоманд соединен .с информацитора 12, открывая его по первым вхо онным входом регистра микрокоманд, дам, вследствие чего на вход управ- а т л и ч а ю щ и й с я тем, что,ления коммутацией блока 2 поступает с целью увеличения быстродействия,адрес следующей микрокоманды, сформи- он дополнительно содержит блок упрованный в блоке 8 режима проверки равления режимами, блок проверки результата. 45 результата, причем блок управленияСигналы на входах 10 и 11 зада- режимами содержит коммутатор, группу ются из блока анализа прохождения Б элементов И (где И - разрядностьуправляющей программы (не показан). поля функции перехода в микрокоманТакой принцип построения позволяет . де) триггер контроля, первый элементобрабатывать быстрые участки про- И триггер управления вторОй эле 1 1грамм без сервисной и .;Онтрольной мент И дешифратор кода функции пеФпроверки, а на медленных участках, рехода а блок проверки результата.Эпозволяющих выполнять команды за боль- одержит дешифратор кода, шифратор,шее время, к основным микрокомандам группу Я элементов И, выход признакоманды добавляются микрокоманды сер- ка режима коктроля блока памяти мик 55висной обработки или контроля. рокоманд соединен с входом триггера Ф о р м у л а и з о б р е т е н и я контроля, выход которого соединен сПроцессор, содержащий блок памя- первым входом первого элемента И, ти микрокоманд, регистр микрокоманд, выход которого соединен с управляю 12803щим входом коммутатора, выход которого соединен с входом задания функции перехода к следующему адресу формирователя адреса и признака переноса, выход признака режима сервисной обработки блока памяти микрокомандсоединен с входом триггера управления, выход которого соединен с первым входом второго элемента И, выход которого соединен со стробирую О щим входом дешифратора кода функции перехода, информационный вход которого соединен с .выходом поля кода функции перехода для режима сер. висной обработки блокапамяти микро команд, выход 1-го разряда (1=1,5) поля маски функции перехода регистра микрокоманд соединен с первым входом 1-го элемента И группы блока управления режимами, второй вход кото рого соединен с выходом 1-го разря. да. дешифратора кода функции перехо 78 8да, вход задания режима контроляпроцессора соединен с вторым входомпервого элемента И, вход задания режима сервисной обработки процессорасоединен с вторым входом второго элемента И, выход поля функции перехода для режима контроля регистра микрокоманд соединен с входом дешифратора кода, 1-ый выход которого соединен с первым входом 1-го элементаИ группы блока проверки результата,второй вход которого соединен с 1-ымвыходом шиФратора, вход коТорогосоединен с информационньи выходомоперационного блока, первая группаинформационных входов коммутаторасоединена с выходами элементов Игруппы блока управления режимами,вторая группа информационных входовкоммутатора соединена с выходамиэлементов.И группы блока проверкирезультата,

СмотретьЗаявка

3860980, 14.01.1985

ПРЕДПРИЯТИЕ ПЯ В-8751

ВАВРУК ЕВГЕНИЙ ЯРОСЛАВОВИЧ, ЗАХАРКО ЮРИЙ МИХАЙЛОВИЧ, МЕЛЬНИК АНАТОЛИЙ АЛЕКСЕЕВИЧ, ЦМОЦЬ ИВАН ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: процессор

Опубликовано: 30.12.1986

Код ссылки

<a href="https://patents.su/8-1280378-processor.html" target="_blank" rel="follow" title="База патентов СССР">Процессор</a>

Предыдущий патент: Стенд для определения точностных характеристик цепного конвейера кромкооблицовочного станка

Следующий патент: Устройство для сопряжения эвм в однородной вычислительной системе

Случайный патент: Машина для заготовки пневой древесины