Устройство для контроля микропроцессорных программных блоков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1267424

Авторы: Галуза, Донских, Лисинецкая, Стальнова

Текст

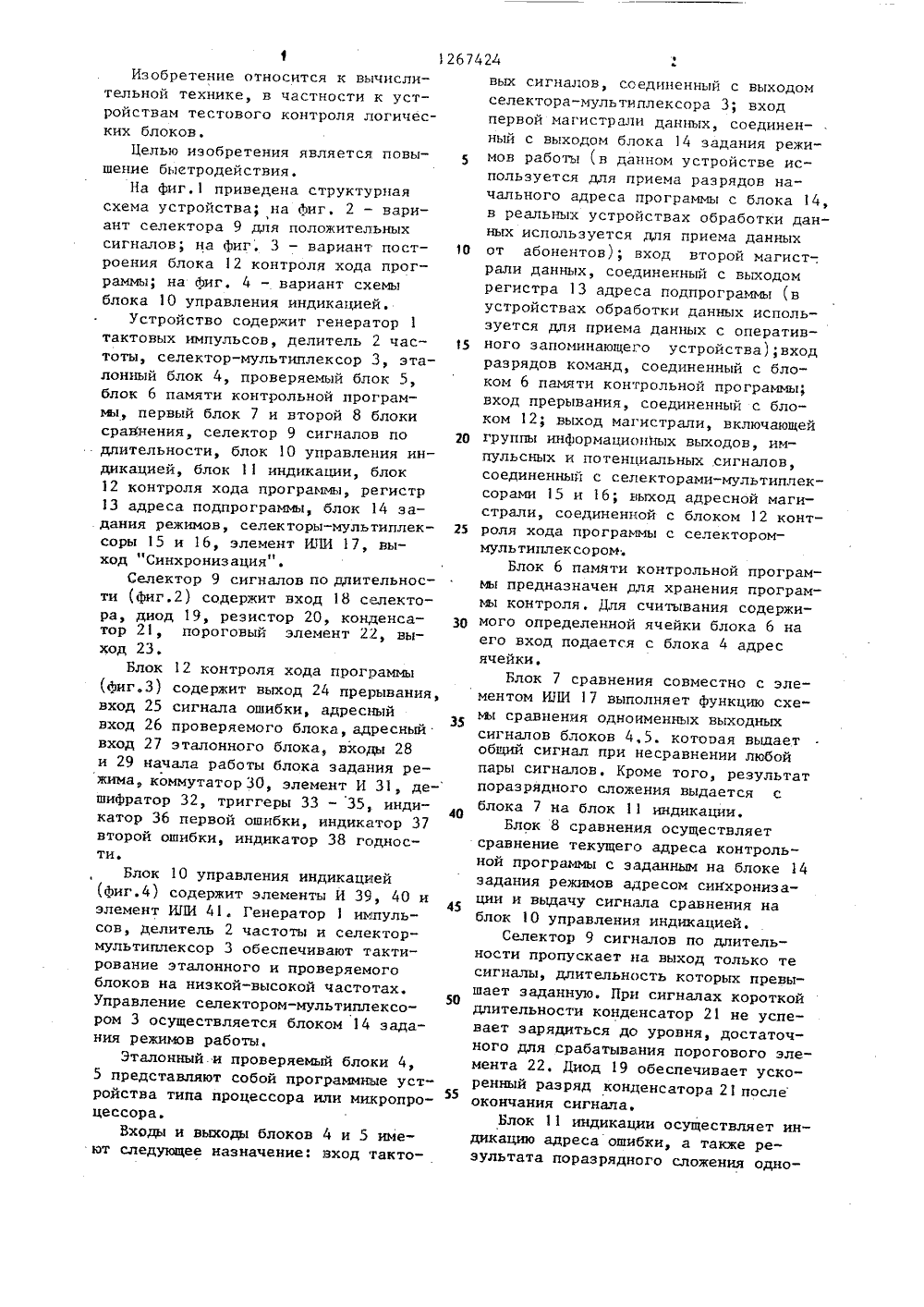

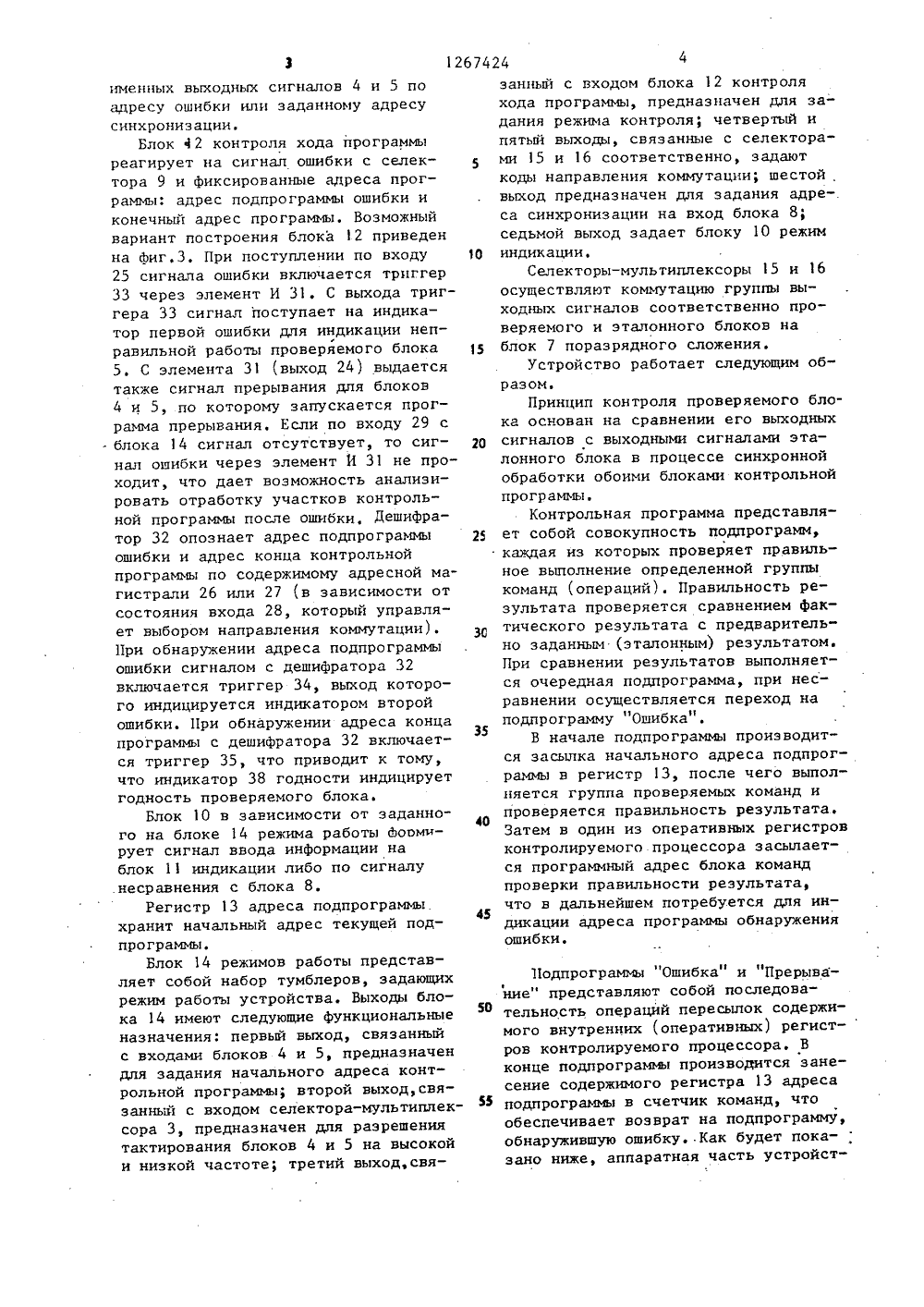

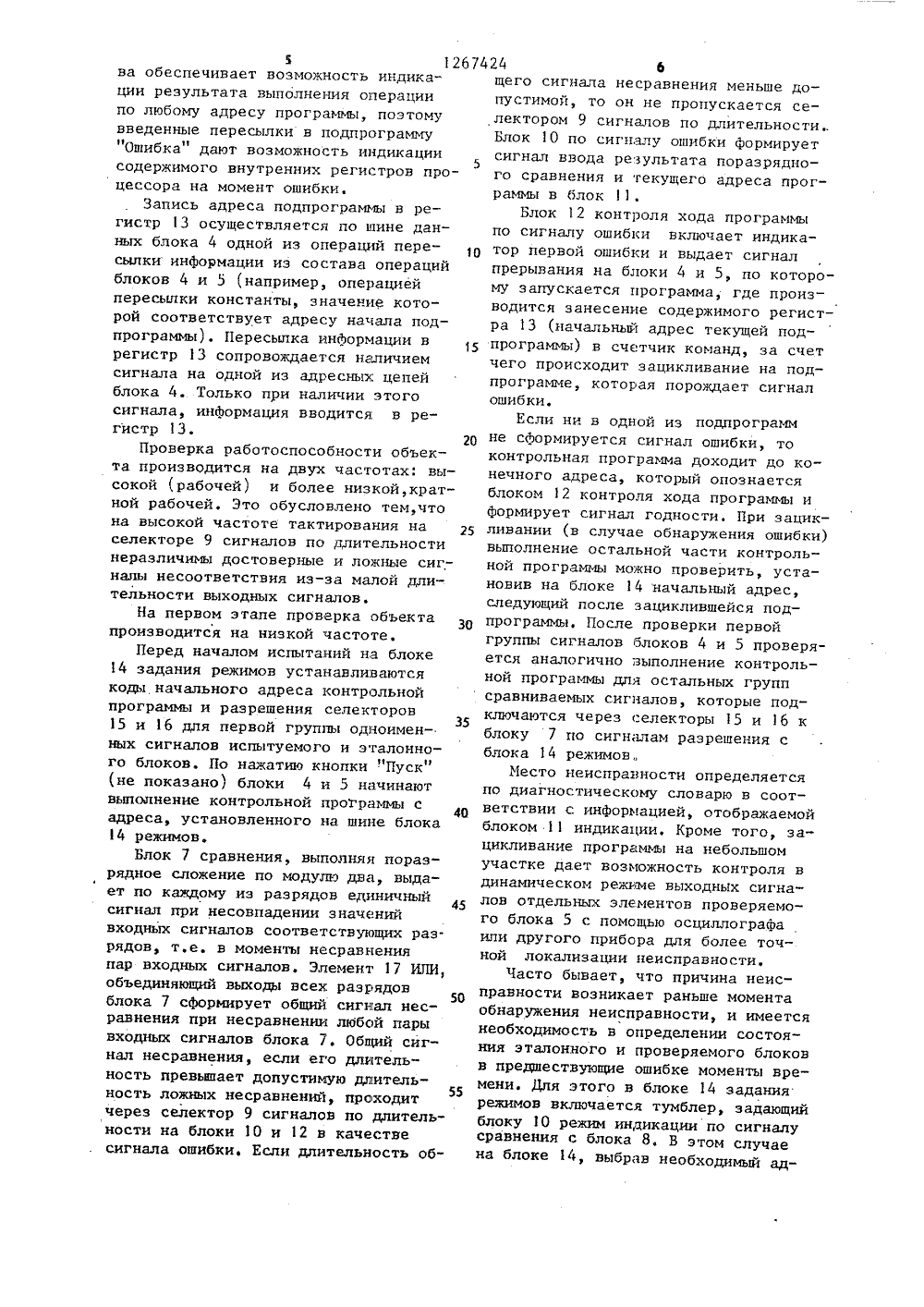

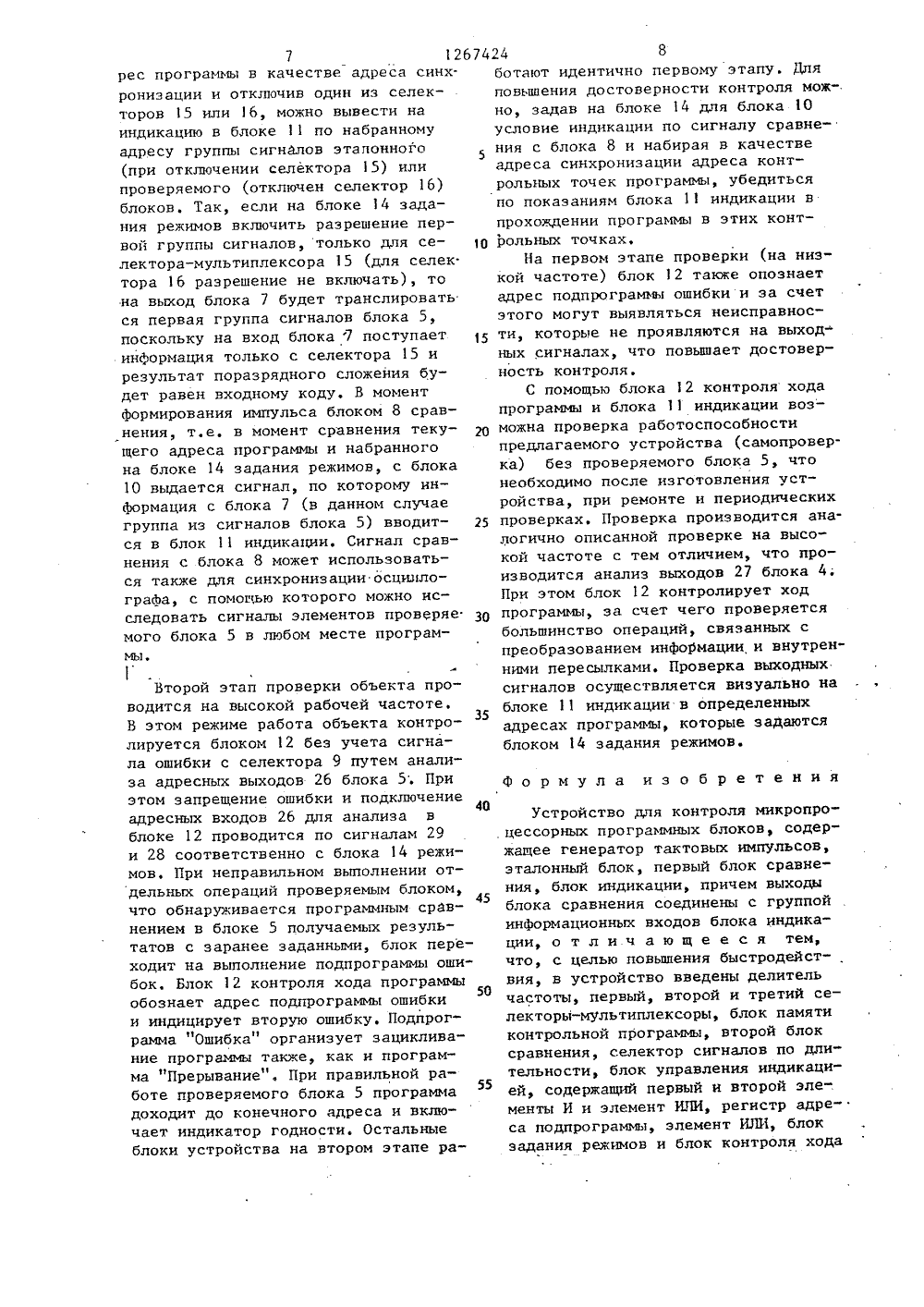

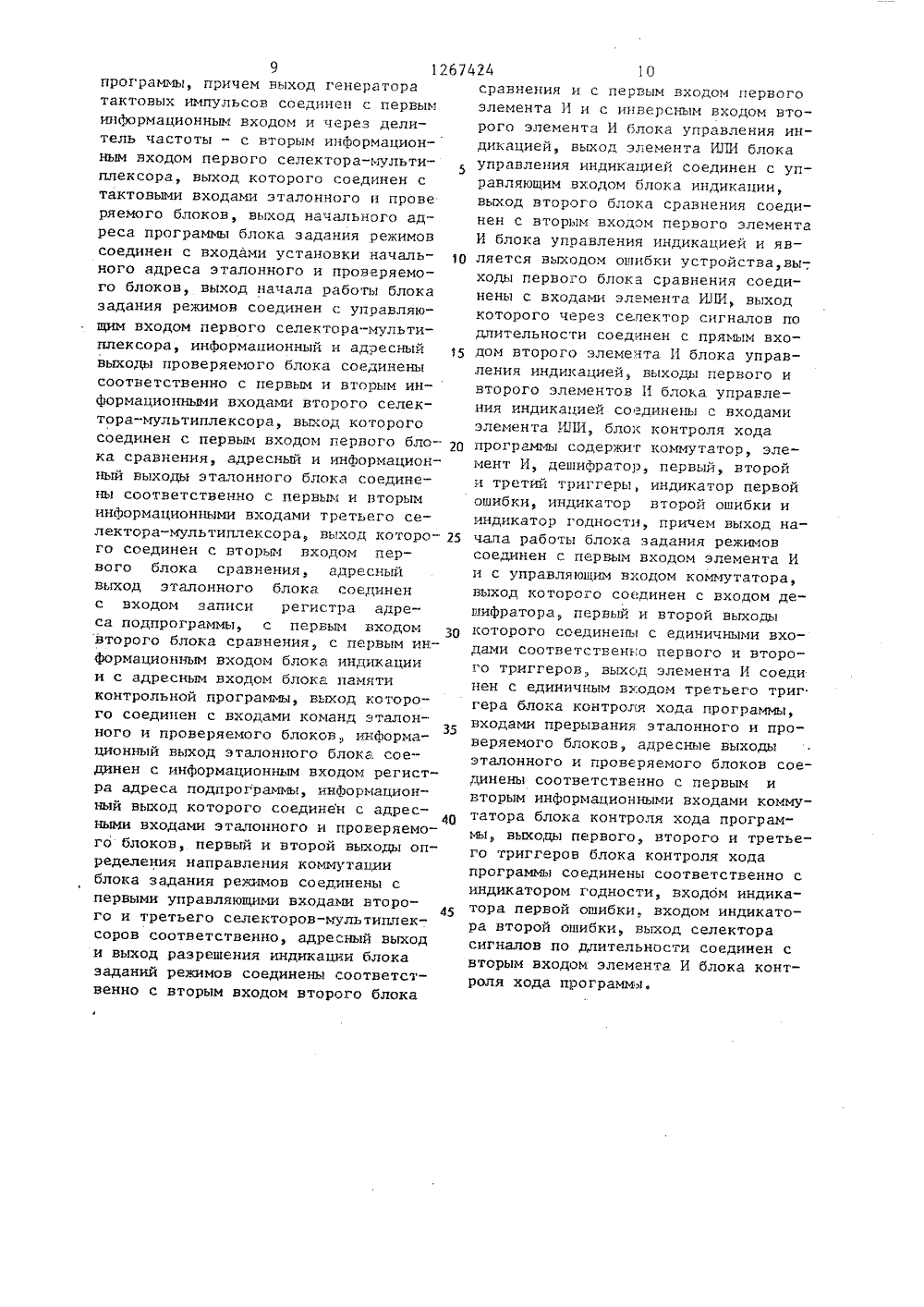

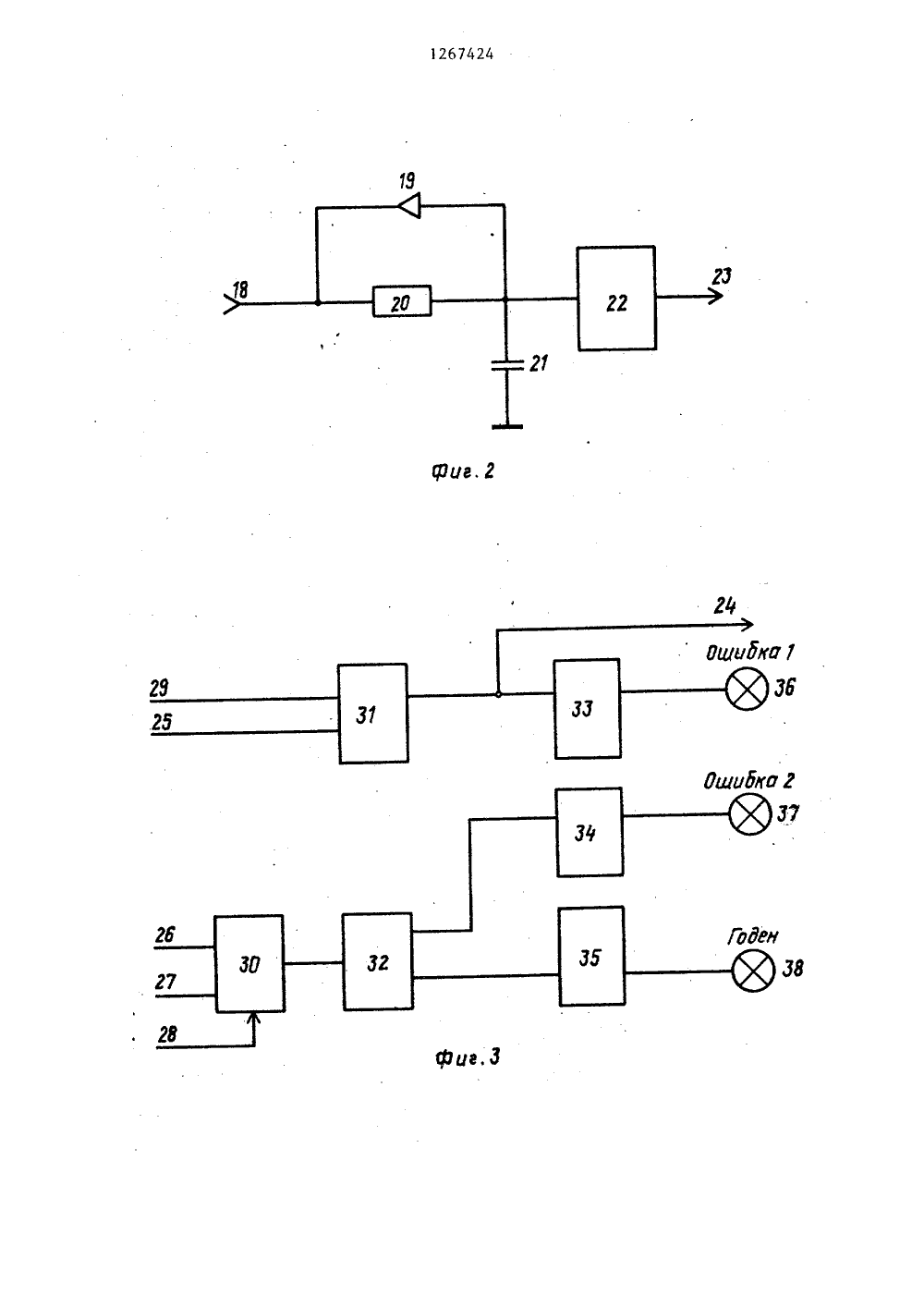

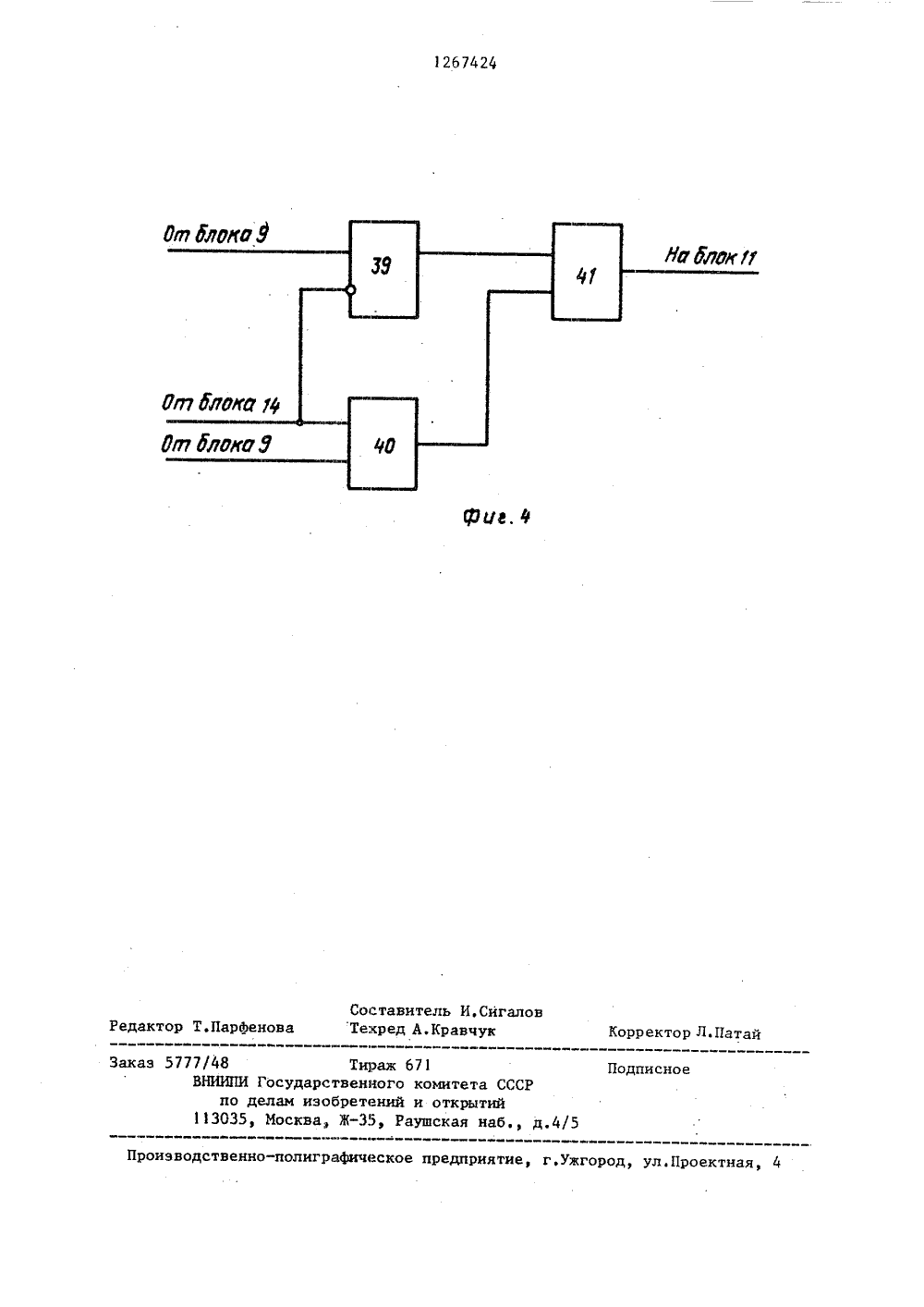

.йннрсицзсцця". Фиг ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ МУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРВ 605216, кл. О 06 У 11/00, 1975.Авторское свидетельство СССРУ 661552, кл. О 06 Р 11/00, 1976.Авторское свидетельство СССРИ 633019, кл. С 06 Р 11/00, 1975.(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ МИКРОПРОЦЕССОРНЫХ ПРОГРАММНЫХ БЛОКОВ(57) Изобретение относится к вычислительной технике, в частности к устроиствам тестового контроля логических блоков. Целью изобретения яв-ляется поввпвение быстродействия.Устройство содержит генератор тактовыхимпульсов 1, делитель 2 частоты, селектор-мультиплексор 3, эталонныйблок 4, проверяемый блок 5, блок 6памяти контрольной программы, первыйблок 7 сравнения, второй блок 8 сравнения, селектор 9 сигналов по длительности, блок 10 управления индикацией, блок 11 индикации, блок 12контроля хода программы, регистр 13адреса подпрограммы, блок 14 задания режимов, два селектора-мульти- дплексора 15,16, элемент ИЛИ 17.4 ил, 1930 Изобретение относится к вычислительной технике, в частности к устройствам тестового контроля логических блоков.Целью изобретения является повышение быетродействия,На фиг.1 приведена структурнаясхема устройства; на Фиг. 2 - вариант селектора 9 для положительныхсигналов; на Фиг. 3 - вариант пост- Ороения блока 12 контроля хода программы; на фиг, 4 - вариант схемыблока 10 управления индикацией.Устройство содержит генератор 1тактовых импульсов, делитель 2 частоты, селектор-мультиплексор 3, эталонный блок 4, проверяемый блок 5,блок 6 памяти контрольной программи, первый блок 7 и второй 8 блокисравнения, селектор 9 сигналов по 20длительности, блок 10 управления индикацией, блок 11 индикации, блок12 контроля хода программы, регистр13 адреса подпрограммы, блок 14 за.дания режимов, селекторы-мультиплексоры 15 и 16, элемент ИЛИ 17, выход "Синхронизация".Селектор 9 сигналов по длительности (Фиг.2) содержит вход 18 селектора, диод 19, резистор 20, конденсатор 21, пороговый элемент 22, выход 23.Блок 12 контроля хода программы(Фиг.З) содержит выход 24 прерывания,вход 25 сигнала ошибки, адресныйвход 26 проверяемого блока, адресныйвход 27 эталонного блока входы 28и 29 начала работы блока задания режима, коммутатор 30, элемент И 31, де-шифратор 32, триггеры 33 - 35, индикатор 36 первой ошибки, индикатор 37второй ошибки, индикатор 38 годности.Блок 10 управления индикацией(Фиг.4) содержит элементы И 39, 40 и 4элемент ИЛИ 41, Генератор 1 импульсов, делитель 2 частоты и селектормультиплексор 3 обеспечивают тактирование эталонного и проверяемогоблоков на низкой-высокой частотах,50Управление селектором-мультиплексором 3 осуществляется блоком 14 задания режимов работы.Эталонный и проверяемый блоки 4,5 представляют собой программные устройства типа процессора или микропроцессора,Входы и выходы блоков 4 и 5 имеют следующее назначение: вход тактовых сигналов, соединенный с выходом селектора-мультиплексора 3; вход первой магистрали данных, соединенный с выходом блока 14 задания режимов работы (в данном устройстве используется для приема разрядов начального адреса программы с блока 14, в реальных устройствах обработки данных используется для приема данных от абонентов); вход второй магист-, рали данных, соединенный с выходом регистра 13 адреса подпрограммы (в устройствах обработки данных используется для приема данных с оперативного запоминающего устройства);вход разрядов команд, соединенный с блоком 6 памяти контрольной программы; вход прерывания, соединенный с блоком 12; выход магистрали, включающей группы информационных выходов, импульсных и потенциальных сигналов, соединенный с селекторами-мультиплексорами 15 и 16; выход адресной магистрали, соединенной с блоком 12 контроля хода программы с селектором- мультиплексором.Блок 6 памяти контрольной программы предназначен для хранения программы контроля, Для считывания содержимого определенной ячейки блока 6 на его вход подается с блока 4 адрес ячейки.Блок 7 сравнения совместно с элементом ИЛИ 17 выполняет функцию схемы сравнения одноименных выходных сигналов блоков 4,5. котоэая выдает общий сигнал при несравнении любой пары сигналовКроме того, результат поразрядного сложения выдается с блока 7 на блок 11 индикации.Блок 8 сравнения осуществляет сравнение текущего адреса контрольной программы с заданным на блоке 14 задания режимов адресом сиихронизации и выдачу сигнала сравнения на блок 10 управления индикациейСелектор 9 сигналов по длительности пропускает на выход только те сигналы, длительность которых превышает заданную. При сигналах короткой длительности конденсатор 2 не успевает зарядиться до уровня, достаточного для срабатывания порогового элемента 22. Диод 19 обеспечивает ускоренный разряд конденсатора 2 после окончания сигнала.Блок 11 индикации осуществляет индикацию адреса ошибки, а также результата поразрядного сложения одно 1267424именных выходных сигналов 4 и 5 по адресу ошибки или заданному адресу синхронизации.Блок 4 2 контроля хода программы реагирует на сигнал ошибки с селектора 9 и фиксированные адреса программы: адрес подпрограммы ошибки и конечный адрес программы, Возможный вариант построения блока 12 приведенна фиг.3. При поступлении по входу25 сигнала ошибки включается триггер33 через элемент И 31, С выхода триггера 33 сигнал поступает на индикатор первой ошибки для индикации непФравильной работы проверяемого блока5, С элемента 31 (выход 24) выдаетсятакже сигнал прерывания для блоков4 и 5, по которому запускается программа прерывания. Если по входу 29 с- блока 14 сигнал отсутствует, то сигнал ошибки через элемент И 31 не проходит, что дает возможность анализировать отработку участков контрольной программы после ошибки, Дешифратор 32 опознает адрес подпрограммы ошибки и адрес конца контрольнойпрограммы по содержимому адресной магистрали 26 или 27 (в зависимости от состояния входа 28, который управляет выбором направления коммутации). При обнаружении адреса подпрограммы ошибки сигналом с дешифратора 32 включается триггер 34, выход которого индицируется индикатором второйошибки. При обнаружении адреса конца программы с дешифратора 32 включается триггер 35, что приводит к тому, что индикатор 38 годности индицирует годность проверяемого блока.Блок 10 в зависимости от заданного на блоке 14 режима работы йоомирует сигнал ввода информации на блок 11 индикации либо по сигналу .несравнения с блока 8.Регистр 13 адреса подпрограммы хранит начальный адрес текущей подпрограммы.Блок 14 режимов работы представляет собой набор тумблеров, задающих режим работы устройства, Выходы блока 14 имеют следующие функциональные назначения: первый выход, связанный с входами блоков 4 и 5, предназначен для задания начального адреса контрольной программы; второй выход,связанный с входом селектора-мультиплексора 3, предназначен для разрешения тактирования блоков 4 и 5 на высокой и низкой частоте; третий выход,свя 50 55 11 одпрограммы "Ошибка" и "Прерывание" представляют собой последовательность операций пересылок содержимого внутренних (оперативных) регист-ров контролируемого процессора. В конце подпрограммы производятся занесение содержимого регистра 13 адреса подпрограющ в счетчик команд, что обеспечивает возврат на подпрограмму, обнаружившую ошибкуКак будет показано ниже, аппаратная часть устройст 0 15 20 25 30 35 40 45 занный с входом блока 12 контроля хода программы, предназначен для задания режима контроля; четвертый и пятый выходы, связанные с селекторами 15 и 16 соответственно, задают коды направления коммутации; шестой, выход предназначен для задания адре-. са синхронизации на вход блока 8; седьмой выход задает блоку 10 режим индикации.Селекторы-мультиплексоры 15 и 16 осуществляют коммутацию группы выходных сигналов соответственно проверяемого и эталонного блоков на блок 7 поразрядного сложения.Устройство работает следующим образом.Принцип контроля проверяемого блока основан на сравнении его выходных сигналов с выходными сигналами эталонного блока в процессе синхронной обработки обоими блоками контрольной программы.Контрольная программа представляет собой совокупность подпрограмм, каждая из которых проверяет правильное выполнение определенной группы команд (операций). Правильность результата проверяется сравнением фактического результата с предварительно заданным (эталонным) результатом. При сравнении результатов выполняется очередная подпрограмма, при несравнении осуществляется переход на подпрограмму "Ошибка".В начале подпрограммы производится засылка начального адреса подпрограммы в регистр 13, после чего выполняется группа проверяемых команд и проверяется правильность результата. Затем в один из оперативных регистров контролируемого. процессора засылается программный адрес блока команд проверки правильности результата, что в дальнейшем потребуется для индикации адреса программы обнаружения ошибки.5 12674ва обеспечивает возможность индика.ции результата выполнения операциипо любому адресу программы, поэтомувведенные пересылки в подпрограмму"Ошибка" дают возможность индикации5содержимого внутренних регистров процессора на момент ошибки,Запись адреса подпрограммы в регистр 13 осуществляется по шине данных блока 4 одной из операций пересылки инФормации из состава операцийблоков 4 и 5 (например, операциейпересылки константы, значение которой соответствует адресу начала подпрограммы). Пересылка инФормации врегистр 13 сопровождается наличиемсигнала на одной из адресных цепейблока 4. Только при наличии этогосигнала, инФормация вводится: в регистр 13.20Проверка работоспособности объекта производится на двух частотах: высокой (рабочей) и более низкой, кратной рабочей, Это обусловлено тем,чтона высокой частоте тактирования населекторе 9 сигналов по длительностинеразличимы достоверные и ложные сигналы несоответствия из-за малой длительности выходных сигналов.На первом этапе проверка объектапроизводится на низкой частоте.Перед началом испытаний на блоке14 задания режимов устанавливаютсякоды начального адреса контрольнойпрограммы и разрешения селекторов3515 и 16 для первой группы одноименных сигналов испытуемого и эталонного блоков. По нажатию кнопки Пуск"(не показано) блоки 4 и 5 начинаютвыполнение контрольной программы садреса, установленного на шине блока4 режимов.Блок 7 сравнения, выполняя поразрядное сложение по модулю два, выдает по каждому из разрядов единичныйсигнал при несовпадении значенийвходных сигналов соответствующих раз.рядов, т.е. в моменты несравненияпар входных сигналов. Элемент 17 ИЛИ,объединяющий выходы всех разрядовблока 7 сФормирует общий сигнал несравнения при несравнении любой парывходных сигналов блока 7, Общий сигнал несравнения, если его длительность превышает допустимую длитель 55ность ложных несравнений, проходитчерез селектор 9 сигналов по длительности на блоки 10 и 12 в качествесигнала ошибки. Если длительность об 24 Ьщего сигнала несравнения меньше допустимой, то он не пропускается селектором 9 сигналов по длительности.,Блок 10 по сигналу ошибки Формируетсигнал ввода результата поразрядного сравнения и текущего адреса программы в блок 11,Блок 12 контроля хода программыпо сигналу ошибки включает индикатор первой ошибки и выдает сигналпрерывания на блоки 4 и 5, по которому запускается программа, где производится занесение содержимого регистра 13 (начальный адрес текущей подпрограммы) в счетчик команд, за счетчего происходит зацикливание на подпрограмме, которая порождает сигналошибки,Если ни в одной из подпРогРаммне сФормируется сигнал ошибки, токонтрольная программа доходит до конечного адреса, который опознаетсяблоком 12 контроля хода программы иФормирует сигнал годности. При зацикливании (в случае обнаружения ошибки)выполнение остальной части контрольной программы можно проверить, установив на блоке 4 начальный адрес,следующий после зациклившейся подпрограммы, После проверки первойгруппы сигналов блоков 4 и 5 проверяется аналогично выполнение контрольной программы для остальных группсравниваемых сигналов, которые подключаются через селекторы 15 и 16 кблоку 7 по сигналам разрешения сблока 14 режимовМесто неисправности определяетсяпо диагностическому словарю в соответствии с инФормацией, отображаемойблоком 11 индикации, Кроме того, зацикливание програмж на небольшомучастке дает возможность контроля вдинамическом режиме выходных сигналов отдельных элементов проверяемого блока 5 с помощью осциллографаили другого прибора для более точной локализации неисправности.Часто бывает, что причина неисправности возникает раньше моментаобнаружения неисправности, и имеетсянеобходимость в определении состояния эталонного и проверяемого блоковв предшествующие ошибке моменты времени. Дпя этого в блоке 14 заданиярежимов включается тумблер, задающийблоку 1 О режим индикации по сигналусравнения с блока 8, В этом случаена блоке 14, выбрав необходимый ад0 7 12674рес программы в качестве адреса синхронизации и отключив один из селекторов 15 или 16, можно вывести наиндикацию в блоке 11 по набранномуадресу группы сигналов эталонного(при отключении селектора 15) илипроверяемого (отключен селектор 16)блоков. Так, если на блоке 14 задания режимов включить разрешение первой группы сигналов, только для селектора-мультиплексора 15 (для селек. тора 16 разрешение не включать), то на выход блока 7 будет транслировать ся первая группа сигналов блока 5, поскольку на вход блока 7 поступает информация только с селектора 15 и результат поразрядного сложения будет равен входному коду, В момент Формирования импульса блоком 8 сравнения, т.е, в момент сравнения теку щего адреса программы и набранного на блоке 14 задания режимов, с блока 10 выдается сигнал, по которому инФормация с блока 7 (в данном случае группа из сигналов блока 5) вводит ся в блок 11 индикации. Сигнал сравнения с блока 8 может использоваться также для синхронизации осциилограФа, с помошью которого можно исследовать сигналы элементов проверяе мого блока 5 в любом месте программы е.Второй этап проверки объекта проводится на высокой рабочей частоте, В этом режиме работа объекта контролируется блоком 12 без учета сигнала ошибки с селектора 9 путем анализа адресных выходов 26 блока 5. При этом запрещение ошибки и подключение40 адресных входов 26 для анализа в блоке 12 проводится по сигналам 29 и 28 соответственно с блока 14 режимов. При неправильном выполнении отдельных операций проверяемым блоком,45 что обнаруживается программным сравнением в блоке 5 получаемых результатов с заранее заданными, блок переходит на выполнение подпрограммы ошибок, Блок 12 контроля хода программы обознает адрес подпрограммы ошибки50 и индицирует вторую ошибку. Подпрограмма "Ошибка" организует зацикливание программы также, как и программа "Прерывание". При правильной работе проверяемого блока 5 программа доходит до конечного адреса и включает индикатор годности. Остальные блоки устройства на втором этапе ра 24 8ботают идентично первому этапу. Дляповышения достоверности контроля можно, задав на блоке 14 для блока 10условие индикации по сигналу сравнения с блока 8 и набирая в качествеадреса синхронизации адреса контрольных точек программы, убедитьсяпо показаниям блока 11 индикации в прохождении программы в этих контрольных точках,На первом этапе проверки (на низкой частоте) блок 12 также опознает адрес подпрограммы ошибки и за счет этого могут выявляться неисправности, которь 1 е не проявляются на выход- ных сигналах, что повышает достоверность контроля.С помощью блока 12 контроля хода программы и блока 11 индикации возможна проверка работоспособности предлагаемого устройства (самопроверка) без проверяемого блока 5, что необходимо после изготовления устройства, при ремонте и периодических проверках. Проверка производится аналогично описанной проверке на высокой частоте с тем отличием, что производится анализ выходов 27 блока 4. При этом блок 12 контролирует ход программы, за счет чего проверяется большинство операций, связанных с преобразованием информации и внутренними пересылками. Проверка выходных сигналов осуществляется визуально на блоке 11 индикации в определенных адресах программы, которые задаются блоком 14 задания режимов. формула изобретения Устройство для контроля микропроцессорных программных блоков, содержащее генератор тактовых импульсов, эталонный блок, первый блок сравнения, блок индикации, причем выходы блока сравнения соединены с группой инФормационных входов блока индикации, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в устройство введены делитель частоты, первый, второй и третий селекторы-мультиплексоры, блок памяти контрольной программы, второй блок сравнения, селектор сигналов по длительности, блок управления индикацией, содержащий первый и второй элементы И и элемент ИЛИ, регистр адре" са подпрограммы, элемент ИЛИ, блок задания режимов и блок контроля ходапрограммы, причем выход генератора тактовых импульсов соединен с первым информационным входом и через делитель частоты - с вторым информационным входом первого селектора-культи 5 плексора, выход которого соецинен с тактовыми входами эталонного и прове ряемого блоков, выход начального адреса программы блока задания режимов соединен с входами установки началь ного адреса эталонного и проверяемого блоков, выход начала работы блока задания режимов соединен с управляющим входом первого селектора-мультиплексора, информационный и адресный выходы проверяемого блока соединены соответственно с первым и вторым ин-формационными входами второго селектора-мультиплексора, выход которого соединен с первым входом первого бло- о ка сравнения, адресный и информационный выходы эталонного блока соединены соответственно с первым и вторым информационными входами третьего селектора-мультиплексора, выход которо го соединен с вторым входом первого блока сравнения, адресный выход эталонного блока соединен с входом записи регистра адреса подпрограммы, с первым входом второго блока сравнения, с первым ин. - Формационным входом блока индикации и с адресным входом блока памяти контрольной программы, выход которого соединен с входами команд эталон 35 ного и проверяемого блоков иформационный выход эталонного блока соединен с информационным входом регистра адреса подпрограммы, информационный выход которого соединен с адресными входами эталонного и проверяемого блоков, первый и второй выходы определения направления коммутации блока задания режимов соединены с первыми управляющими входами второ 45 го и третьего селекторов-мультиплексоров соответственно, адресный выход и выход разрешения индикации блока заданий режимов соединены соответственно с вторым входом второго блока сравнения и с первым входом первогоэлемента И и с инверсным входом второго элемента И блока управления индикацией, выход элемента ИЛИ блокауправления индикацией соединен с управляющим входом блока индикации,выход второго блока сравнения соединен с вторым входом первого элементаИ блока управления индикацией и является выходом ошибки устройства,вы-,ходы первого блока сравнения соединены с входами элемента ИЛИ, выходкоторого через селектор сигналов подлительности соединен с прямым входом второго элемента И блока управления индикацией, выходы первого ивторого элементов И блока управления индикацией со динены с входамиэлемента ИЛИ, блок контроля ходапрограммы содержиг коммутатор, элемент И, дешифратор, первый, второйи третий триггеры, индикатор первойошибки, индикатор второй ошибки ииндикатор гоцности, причем выход начала работы блока задания режимовсоединен с первым входом элемента Ии с управляющим входом коммутатора,выход которого соединен с входом дешифратора, первый и второй выходыкоторого соединены с единичными входами соответственно первого и второго триггеров выход элемента И соединен с единичным входом третьего триггера блока контроля хода программы,входами прерывания эталонного и проверяемого блоков, адресные выходыэталонного и проверяемого блоков соединены соответственно с первым ивторым информационными входами коммутатора блока контроля хода программы, выхоцы первого, второго и третьего триггеров блока контроля ходапрограммы соединены соответственно синдикатором годности, входбм индикатора первой ошибки, входом индикатора второй ошибки, выход селекторасигналов по длительности соединен свторым входом элемента И блока контроля хода програмил./ 8 Тираж б 71НИИПИ Государственного комитета СССРпо делам изобретений и открытий13035, Москва, Ж, Раушская наб., д.4/5 писное Проиэводственн лигра 4 жческое предприятие, г.ужгород, ул.Проектная

СмотретьЗаявка

3569506, 30.03.1983

ПРЕДПРИЯТИЕ ПЯ А-3327

ГАЛУЗА АЛЕКСЕЙ СЕРГЕЕВИЧ, СТАЛЬНОВА ТАТЬЯНА ВАСИЛЬЕВНА, ДОНСКИХ БОРИС ИВАНОВИЧ, ЛИСИНЕЦКАЯ ВАЛЕНТИНА ПАВЛОВНА

МПК / Метки

МПК: G06F 11/26

Метки: блоков, микропроцессорных, программных

Опубликовано: 30.10.1986

Код ссылки

<a href="https://patents.su/8-1267424-ustrojjstvo-dlya-kontrolya-mikroprocessornykh-programmnykh-blokov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для контроля микропроцессорных программных блоков</a>

Предыдущий патент: Устройство контроля объектов дискретного действия

Следующий патент: Микропрограммное устройство формирования тестовой последовательности

Случайный патент: Устройство для определения статистических характеристик