Микропрограммное устройство формирования тестовой последовательности

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

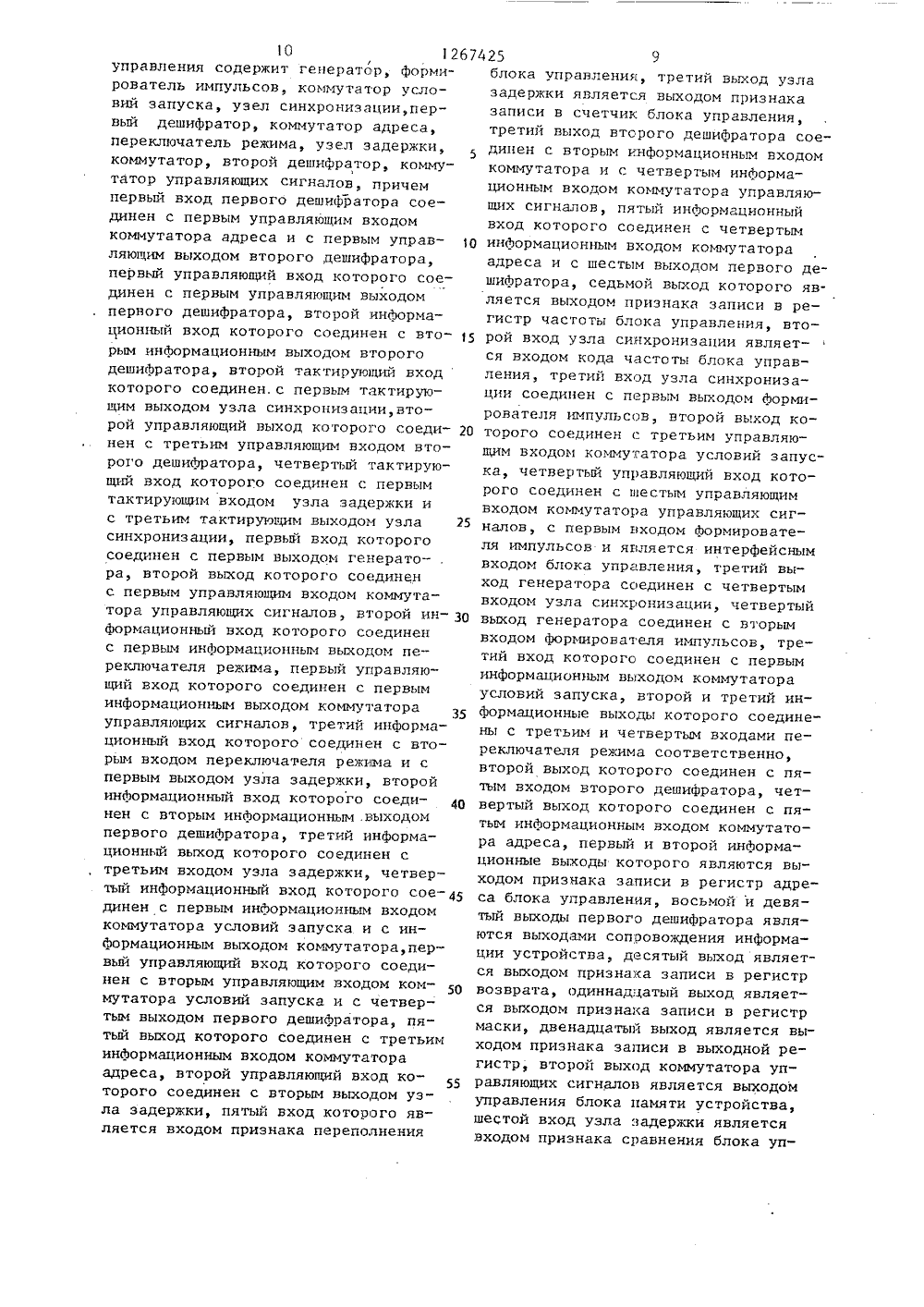

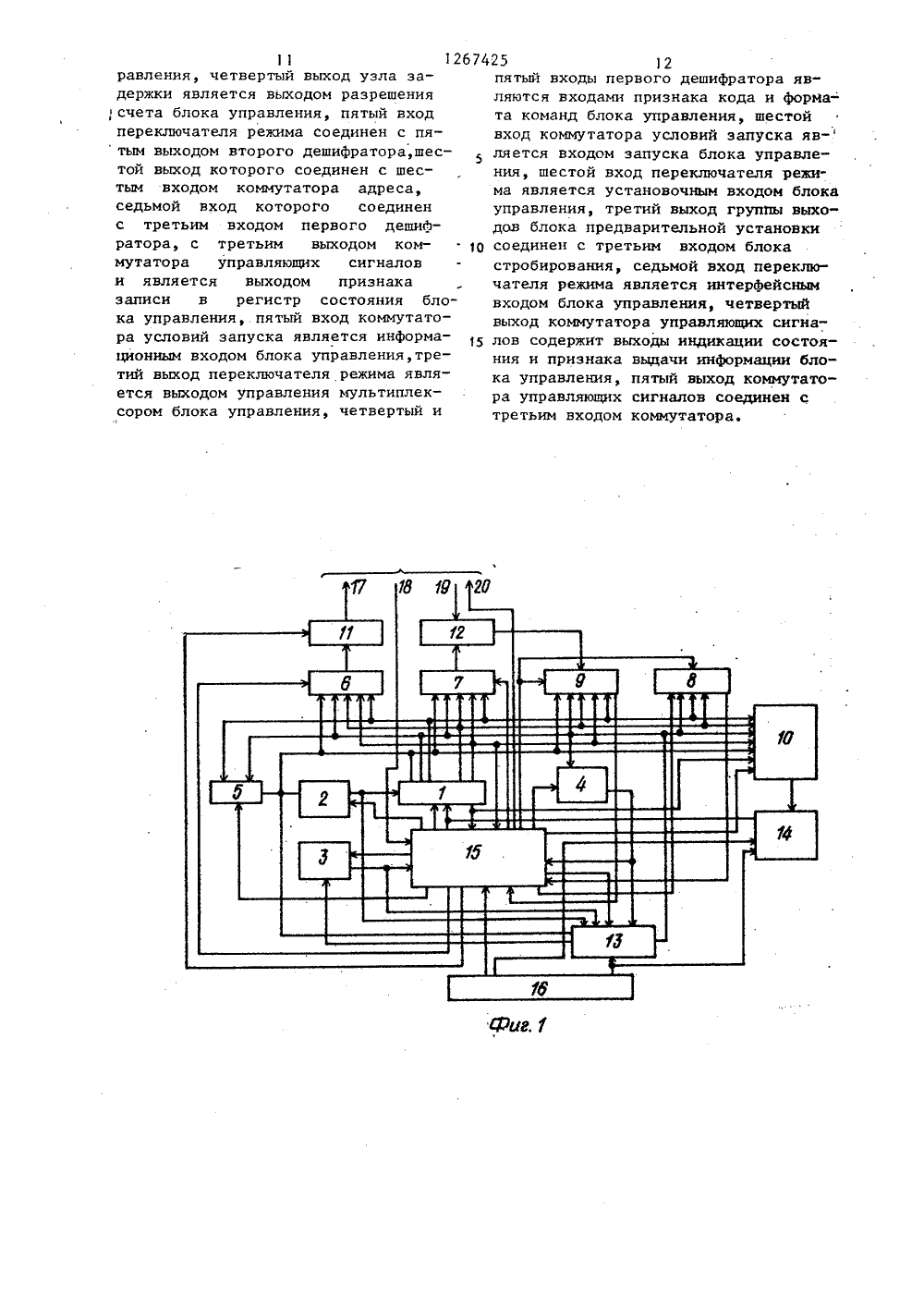

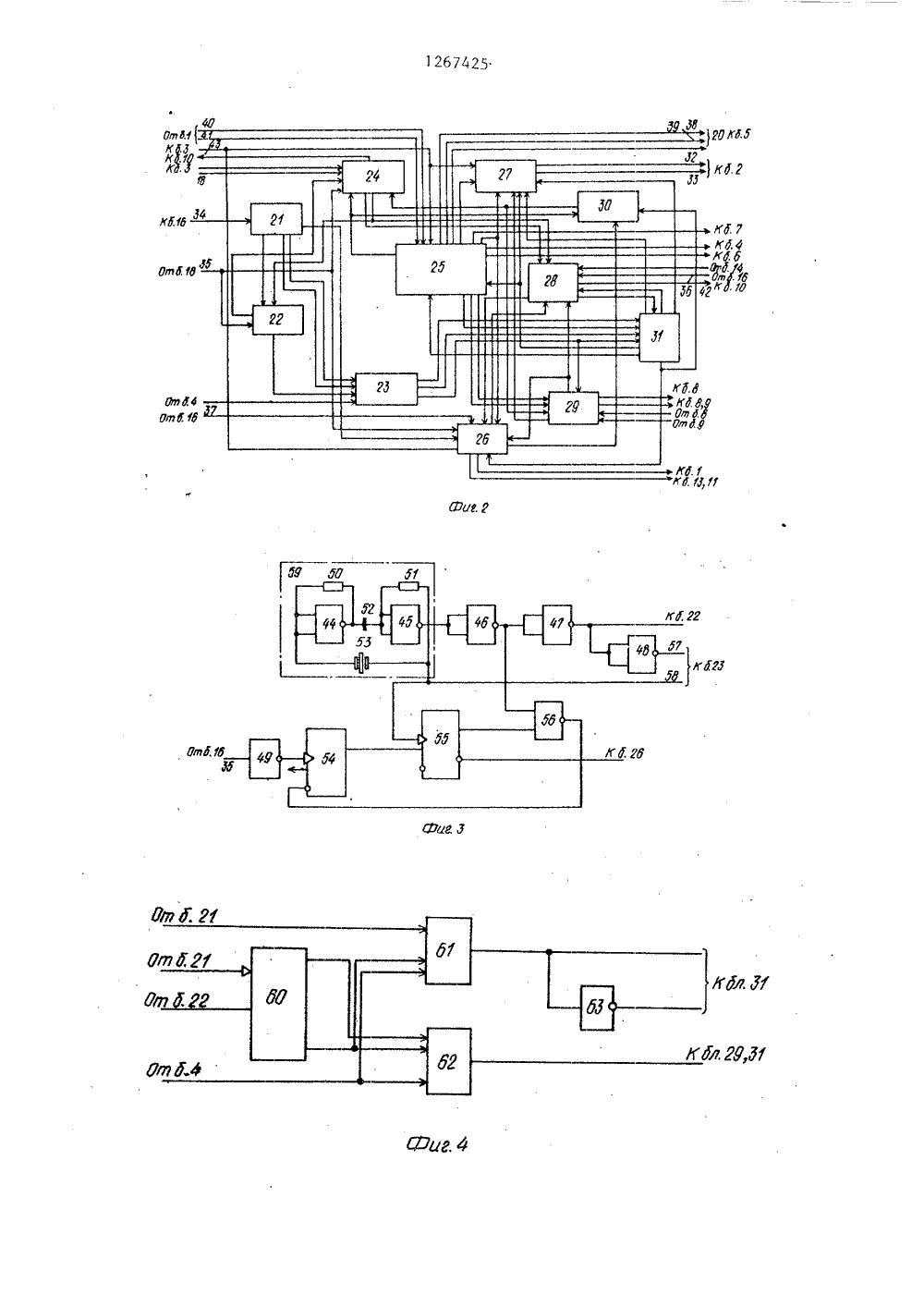

) МИКРОПРОГРАММНОЕ УСТРОЙСТВО ФОРОВАНИЯ ТЕСТОВОЙ ПОСЛЕДОВАТЕЛЬНОС(57) Изобретение отнолительной технике. Целявляется повышение ко я к вычис- изобретени чнев ьев,ования оборудо одержит блок п по ние реса, состоя ия, аск о СССР26, 1983 рупп еств е тес ых последова чных типов про.и. Ь-лы, 25 ил. ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ У СВИДЕТЕЛЬСТВУ(56) Патент Японии У 54кл. С 06 Р 11/00, 1979.Авторское свидетельс9 1045230, кл, С 06 Р 1 та, выходнои, мсчетчик, компаблоки ключей,Устройство осущкое формирован тельностей дляверяемых блоко эффициента исния. Изобретеяти, регистрыстоты, возвраблок управления,мультиплексор,элементов И.ет автоматичес12 б 742 Отй Уббл. РФ ФР дщдл Ра 9 КЖ. /ГЙЯ ЖРУ О 14 71267425 11151811 ЮР 87 бР 45210 РС РЧСРцг, 17 15 14 О 12 11 Ю Р д 7 Ю Р 4 У 2 1 Р Ю 1 О О гд 27 ж а М Я 22 21 Я Ю Ч 17 т ПАМ 1ЯЩЩРог. Ю- ъ - -фПА/У 2 ПАМ 33 ЛАМ 12 l7 АМХ 1Х1 0 Х сРорюапг 0 О 1 Х Р Ю 1 -4 Рорпю 1 а а а -аюрпааг О 1 И И 1 цЮщбдцию Пол а Р"Юад 7 О /АМИ,р,рррРсриав 1 Микрвсперация Псле Оаннюк 1 Помбанех 2 пдммтлчсг г 5 ати ааа-.ссСРОрмам 2 Микрсолерациа Псле 2 Пшщ 3 IЗюе 1Изобретение относится к вычислительной технике, а именно к устройствам автоматического синтеза тестовдля контроля работоспособности и диагностики неисправностей сложных цифровых объектов,Целью изобретения является повышение коэФАициента использования оборудования,На фиг. 1 изображена Аункциональная схема предлагаемого устройства;на фиг. 2 - Функциональная схемаблока управления; на Фиг. 3 в . схема. генератора; на Фиг. 4 - схема узласинхронизации; на Ьиг. 5 - схемаформирователя импульсов; на Аиг. 6схема коммутатора условий запуска;на фиг. 7 - схема коммутатора адреса; на Фиг. 8 - схема первого дешифратора; на фиг, 9 - схема коммутатора управляющих сигналов; на Фиг.10 схема второго дешиАратора; наАиг,11 схема узла задержки; на фиг, 12схема коммутатора; на Аиг, 13 - схема переключателя; на Фиг, 14 - схема второго и третьего блоков ключей;на фиг, 15, 16 - схемы блоков предварительной установки начальных условий," на Аиг. 17 - Формат регистраадреса, регистра частоты и регистрасостояния; на Аиг. 18 - Аормат блока памяти; на Аиг. 19 - кодл форматов 0,1,2; на Аиг. 20 - кодировкаслов блока памяти в форматах 01,2;на Фиг, 21 - расшиАровка слов памяти по микрооперациям в форматах О,1,2; на Аиг. 22 - временная диаграмма работы регистра адреса," наФиг. 23 - временная диаграмма работы дешифратора; на фиг. 24 - временная диаграмма режима генерированиятестовой последовательности; наАиг, 25 - временная диаграмма режима предварительной подготовки (загрузки).Предложенное устройство (Фиг,1)содержит блок 1 памяти, регистр 2адреса, регистр 3 состояния, регистр4 частоты, регистр 5 возврата, регистр 6 выходной, регистр 7 маски,счетчик 8, циАровой компаратор 9,мультиплексор 10, первый блбк 11 ключей, группу И 12, второй блок 13ключей третий блок 14 ключей, блок15 управления, блок 16 предварительной установки, выходную информационную шину 17, входную управляющую шину 18, входную информационную шину19, выходную управляющую шину 20.Блок управления (Аиг,2) содержит генератор 21, Формирователь 22 импульсов, узел 23 синхронизации, ком-. мутатор 24 условий запуска, первый дешиАратор 25, коммутатор 26 управляющих сигналов, коммутатор 27 адреса, переключатель 28 режима, узел 29 задержки, коммутатор 30, второй дешифратор 31, выходы 32-43 блока управленияГенератор 21 (Фиг,3) содержит блок 59, включающий инверторы 44-45, резисторы 50 и 51, конденсатор 52, кварцевый резонатор 53. Кроме того генератор содержит инверторы 46-49.Р-триггеры 54 и 55, элемент И-НЕ 56, выходы 57,58 генератора,Узел синхронизации (фиг.4) содержит двоичный счетчик 60, два мультиплексора "Один из 11" 61,62 и инвертор 63.Формирователь импульсов (Фиг,5) содержит элемент И 64, триггеры 65 20 и 66,Коммутатор условий запуска (фиг.6)содержит инверторы 67 и 68, элементыИ-НЕ 69-71, И 2, два Р-триггера 73и 74, элементы И 75,76. 30 3540 И-НЕ 136-140, инвертора 141, элемента 142 задержки. Узел задержки (Фиг.11) содержитР-триггер 143, элементы И-НЕ 144-146,элемент И 147, инвертор 48.Коммутатор (Фиг,12) содержит элементы И-НЕ 149, И 150.Переключатель (Фиг.13) содержитдва Р-триггера 151152 и элементыИ-НЕ 153, 154,Второй и третий блоки ключей(Фиг.14) содержат два блока двунаправленных усилителей 155,156. Коммутатор адреса (Фиг,7) содержит элементы И-НЕ 77-79, элементыИ 80,81, инверторы 83 и 84.Первый дешифратор (фиг.8) содержит элемент И-НЕ 85-91, и 92-95,ИЛИ-НЕ 96, инверторы 97-100, дешифратор 101, выходы 102-109 первого дешиАратора.Коммутатор управляющих сигналов3 12Блок предварительной установки начальных условий (фиг,15,16) содержит ряд информационных тумблеров 157-161, ряд ключей 162-166, элемент И-НЕ 167, ряд светодиодов 168-172, ряд сопротивлений 173-177, ряд тумблеров управления 178-184, кнопку управления 185, выходы 186,187 блока предварительной установки начальных условий.Устройство работает следующим образом.Микропрограммное устройство формирования тестовой последовательности (Фиг.1) имеет два основных режима работы; предварительная загрузка в регистры и память исходной информации (фиг. 25), генерирование тестовой последовательности (фиг,24).В режиме предварительной загрузки в регистры и память исходной инФормации, устройство может находиться в состоянии Останов", а в режиме генерирования тестовой последовательности сначала в состоянии Пред- запуск", затем "Пуск"Состояние Предзапуск" может отсутствовать,При наличии на линии 35 "Режим работы" (Фиг,16) сигнала "0" устройство находится в состоянии "Останов", В этом состоянии обеспечиваются режимы записи и чтения, временные диаграммы которых приведены на фиг,25, Запись информации в регистр 2 адреса, регистр 3 состояния и регистр 4 частоты (Фиг.1) осуществляется согласно алгоритму, приведенному на Фиг.25, Информация задается значениями сигналов на выходах блока 16 предварительной установки (фиг.15), которая поступает на группу входов-выходов второго блока 13 ключей. Сигнал "0" тумблером ЗПРС,РЧ,РА в бло,ке 16 предварительной установки (Фиг. 16) подается в блок 15 управления, где в результате формируются стробы записи в регистры 2-4 адреса, состояния и частоты соответст" венно (Фиг. 1).Блок 1 памяти представляет собой накопитель емкостью, например, 1024 х х 34 разрядных слов, причем запись иэ блока 16 предварительной установки осуществляется поблочно по шестнадцать разрядов ПАМО, ПАМ 1,ПАМ 2 (фиг.18). Идентификация блока памяти осуществляется подачей на одну из управляющих линий ЗППО, ЗПП 1, ЗПП 2 (фиг. 16) сигнала "0". При изменении67425 4 состояния регистра 2 адреса информация адресуется к другой ячейке блока 1 памяти. Запись в младший разрядрегистра 3 состояния значения "0или "1" (фиг.17) определяет условиезапуска устройства. Переход устройства из состояния Останов в состояние "Пуск" осуществляется двумя способами, в зависимости от значения 10 младшего раэрядарегистра 3 состояния(Фиг,17), При значении "1" разрешен переход устройства всостояние Пуск по сигналу на линии35 работы (Фиг,1), при значении "0"по внешнему сигналу на линии 18(фиг. 1), Устройство имеет третьесостояние Предзапуск, которое определяется, как промежуточное состояние между "Остановом" и 11 Пуском 11. Вэтом состоянии устройство будет находиться после того, как на линии 35"Режим работы" произошло переключение сигнала иэ значения 10" в значение "1" (в регистре 3 состояния разряд, определяющий условие запуска,имеет значение 0), а внешний запускающий сигнал по линии 18 с объекта 30 жимах - автоматическом и пошаговом.В автоматическом режиме выполнение команд производится без вмешательства оператора по программе, которая предварительно заложена в блок 1 памяти.В пошаговом режиме необходима постоянная инициация со стороны оператора на выполнение каждой команды.Инициация выполнения очередной команды устройства осуществляется процедурой чтения блока ПАМ 2 (Фиг18).Генерирование тестовой последовательности в режиме "Шаг" или "Автомата" определяется разрядом 34 блока . памяти ПАМ 2 (Фиг.18). В режиме генерирования тестовой последовательности из блока 1 памяти выбирается слово, адрес которого соответствует значению регистра 2 адре са (Фиг,1). Три старшие разряда этого слова определяют формат команды, Устройство имеет три формата команд (Фиг.19). 35 40 45 50 диагностирования еще не появился.Переход устройства в состояние "Пуск" означает переход в режим генерирования тестовой последовательности (выполнение тестовой диагностической программы, записанной в блоке 1 памяти). Он осуществляется в двух ре-.5 1674В Формате 0 предусмотрены следующие команды устройства: запись поляданных (фиг.20) в выходной регистрб; запись поля данкых (фиг.20) в регистр 7 маски; ожидание событий, в5котором блок 15 управления (Фиг.2)вырабатывает сигналы, которые Фиксируют память 1 на выбранном слсве,запускают счетчик 8, на четвертыйвход которого подаются синхросигналы с блока 15 управления (Фиг.1),а на пятый сигнал разрешения счетауровня "1" с этого же блока. Регистр2 адреса находится в ожидании одного иэ двух событий сравнения содержимого поля данных (разряды ПАМс 3100) со значениями сигналовна входных каналах 9 устройство(фиг.20) с учетом маскирования разрядов в регистре 7 маски в соответствии с выражениемГ:=(К, (31 00Ь РМс 31 000+К),где К - к-й входной канал устройства;К - поле данньгл, разрядыПАМ 3100)25переполнение счетчика 8, запуск которого осуществляется микрооперациейОжидание событий",При первом событии значение регистра 2 адреса (РЛ) увеличиваетсяна два (РА : = РА + 2), при второмсобытии значение РЛ увеличивается наединицу (РА : = РА + 1),После отслеживания одного иэ двухуказанных событий, реализуемых при35Формате 0 (микрооперация ожидания),.устрокство переходит к разбору следующей команды, выбрАнной из блока 1памяти. По команде 1 Запись поля данных в выходной регистр" производится запись выбранного словаПАМ 3100 в регистр 6 выходной,а в регистр 2 адреса добавляетс,яединица (РА : = РА + 1), и из блока1 памяти выбирается следующее сло 45во, По команде "Запись поля данныхв регистр маски (ЗПРМ) производится запись слова ПАМ 3100 в регистр 7 маски, а в РА добавляетсяединица и выбирается следующее сло 50во иэ блока 1 памяти.В Формате 1 (Фиг.21) выполняютсяследующие команды: запись поля данных в регистр 2 адреса, запись поляданных в регистр 5 возврата, После55выполнения любой из команд значениерегистра РА 2 увеличивается на единицу (РА : = РА + 1), из блока 1 памяти выбирается следующее слово. В формате 2 (фиг,21) выполняются следующие команды: выдача радиального запроса 38 останова (фиг.2) на объект диагностирования, передача значения регистра 5 возврата в регистр 2 адреса, запись поля данных в счетчик 8, выдача радиального запроса 38 остакова (Фиг.2) и останов устройства. В этом Формате 2 возможны комбинации иэ приведенных команд при условии: эалиси поля данных регистра частоты и поля данных счетчика не следует выполнять, когда код, заносимый в регистр частоты, совпадает (или ке имеет существенного зкачения для данного состояния регистра частоты) с кодом, заносимым в три младших разряда счетчика 8 (см.перекрытие полей 2 и 3 фиг, 20). Сигнал радиального запроса 38 устройства (фиг2) вырабатывается при работе устройства в режиме генерирования последовательности и выполняет команды Формата 2 в двух случаях: при выполнении операции выдачи радиального запроса 38 останова объекта диагностирования и останова устройства, ПАМ 1 (30= 0; при выполнении команды выдачи радиальнсго запроса 38 останова объекта диагностированияПАМ 126 = О.Формула изобретения1, Микропрограммное устройство Формирования тестовой последовательности, содержащее блок памяти, регистр адреса, выходы которого соединены с адресным входом блока памяти, выходной регистр, группу элементов И, первые входы которых подключены к выходам об.ьекта диагностирования, блок предварительной установки, счетчик и блок управления, о т л и ч а ющ е е с я тем, что, с целью повышения коэффициента использования обору дования, оно содержит регистр маски, регистр возврата, регистр частоты, регистр состояния, три блока ключей, цифровой компаратор мультиплексор, причем адресная группа выходов блока памяти соединена с первыми входами данных выходного регистра, регистра маски, цифрового компаратора, мультиплексора, с информационными входами регистра адреса, с адресной группой выходов второго блока ключей и выходами регистра возврата, группа выходов признака кода частоты блока25 7 12 б 74 памяти соединена с вторыми входами данных выходного регистра, регистра маски, мультиплексора, цифрового компаратора, с первыми входами данных счетчика, регистра возврата;регистра частоты, с группой выходов признака частоты второго блока ключей, группа выходов признака кода возврата блока памяти соединена с третьими входами данных выходного регистра, регистра маски, цифрового компаратора, мультиплексора, с вторыми входами данных регистра возврата, счетчика, группа выходов признака кода счетчика соединена с четвертыми входами данных выходного регистра, регистра маски, цифрового компаратора, мультиплексора и третьими входами данных счетчика, группа выходов признака кода команд блока памяти соединена с пятыми входами данных вы. ходного регистра, регистра маски, цифрового компаратора, мультиплексора, с входами признака кода команд блока управления, группа выходов признака формата команд блока памяти соединена с входами признака Формата команд блока управления, с шестыми входами данных мультиплексора, адресная группа входов которого сое- ЗО динена с группой выходов управления мультиплексором блока управления, вторая группа управляющих выходов блока предварительной установки соединена с группой управляющих входов третьего блока ключей, группа информационных входов которого соединена с группой выходов мультиплексора, выход индикации состояния блока управ.ления соединен с входом индикации 4 О состояния второго блока ключей, информационная группа выходов которого соединена с информационными входами регистра состояния, тактирующий вход которого сое 45 динен с выходом признака записи в регистр состояния блока управления, группа выходов признака записи в регистр адреса которого соединена с тактирующими входами регистра адреса, группа выходов которого соедине 50 на с группой адресных входов второго блока ключей, группа входов кода частоты которого соединена с одноименной группой входов блока управления и с группой выходов регистра частоты, тактирующий вход которого соединен с выходом признака записи в регистр частоты блока управле 25 8ния, установочная группа входов которого соединена с информационной группой входов блока памяти и с группой выходов третьего блока ключей, группа входов-выходов "Адрес-данные которого соединена с группой входов- выходов "Адрес-данные" второго блока ключей, с группой входов-выходов "Адрес-данныеблока предварительной "установки, интерфейсная группа выходов которого соединена с интерфейсной группой входов блока управления, вход признака переполнения которого соединен с выходом переполнения счетчика, тактирующий вход которого соединен с выходом признака записи в счетчик блока управления, выход признака записи в регистр маски блока управления соединен с тактирующим входом регистра маски, группа выходов которого соединена с вторыми входами элементов И группы, выходы кото- рых соединены с шестой группой входов данных цифрового компаратора, выход признака сравнения которого соединен с входом признака сравнения блока управления, выход разрешения счета которого соединен с управляющим входом цифрового компаратора и с входом разрешения счета счетчика, выход признака выдачи информации блока управления соединен с входом разрешения выдачи информации первого блока ключей, информационные входы которого соединены с выходами выходного регистра, а выход - с выходами данных устройства, тактирующий вход выходного регистра соединен с выходом признака записи в выходной регистр блока управления, группа выходов признака записи в регистр возврата которого соединена с группой тактирующих входов регистра возврата, выходы регистра состояния соединены с информационной группой входов блока управления и с информационной группой входов второго блока ключей, группа выходов управления блоком памяти блока управления соединена с группой входов выборки кристалла и записи-чтения блока памяти, группа выходов сопровождения информации блока управления соединена с управляющими выходами устройства, а вход запуска блока управления соединен с управляющим входом устройства.2. Устройство по п.1, о т л и -ч а ю щ е е с я тем, что, блок;10 12674 управления содержит генератор, формирователь импульсов, коммутатор условий запуска, узел синхронизации,первый дешифратор, коммутатор адреса, переключатель режима, узел задержки, коммутатор, второй дешифратор, коммутатор управляющих сигналов, причем первый вход первого дешифратора соединен с первым управляющим входом коммутатора адреса и с первым управ ляющим выходом второго,цешифратора, первый управляющий вход которого соединен с первым управляющим выходом первого дешифратора, второй информапионный вход которого соединен с вто рым информационным выходом второго дешифратора, второй тактирующий вход которого соединен, с первым тактирующим выходом узла синхрониэации,второй управляющий выход которого соеди нен с третьим управляющим входом второго дешифратора, четвертый тактирующий вход которого соединен с первым тактирующим входом узла задержки и с третьим тактирующим выходом узла 25 синхронизации, первый вход которого соединен с первым выходом генератора, второй выход которого соединен с первым управляющим входом коммутатора управляющих сигналов, второй ин- ЗО формационный вход которого соединен с первым информационным выходом пе - реключателя режима, первый управляющий вход которого соединен с первым информационным выходом коммутатора управляющих сигналов, третий информационный вход которого соединен с вторым входом переключателя режима и с первым выходом узла задержки, второй информационный вход которого соединен с вторым информационным выходом первого дешифратора, третий информационный выход которого соединен с третьим входом узла задержки, четвертый информационный вход которого соединен с первым информационным входом коммутатора условий запуска и с информационным выходом коммутатора,первый управляющий вход которого соединен с вторым управляющим вхоцом коммутатора условий запуска и с четвертым выходом первого дешифратора, пятый выход которого соединен с третьим информационным входом коммутатора адреса, второй управляющий вход которого соединен с вторым выхоцом узла задержки, пятый вход которого является входом признака переполнения 25 9блока управления, третий выход узлазадержки является выходом признаказаписи в счетчик блока управления,третий выход втсрого дешифратора соединен с вторым информационным входомкоммутатора и с четвертым информационным входом коммутатора управляющих сигналов, пятый информационныйвход которого соединен с четвертыминформационным входом коммутатораадреса и с шестым выходом первого дешифратора, седьмой выход которого является выходом признака записи в регистр частоты блока управления, второй вход узла синхронизации является входом кода частоты блока управления, третий вход узла синхронизации соединен с первым выходом формирователя импульсов, второй выход которого соединен с третьим управляющим входом коммутатора условий запуска, четвертый управляющий вход которого соединен с шестым управляющимвходом коммутатора управляющих сигналов, с первым входом формирователя импульсов и является интерфейснымвходом блока управления, третий выход генератора соединен с четвертымвходом узла синхронизации, четвертыйвыход генератора соединен с вторымвходом формирователя импульсов, третий вход которого соединен с первыминформационным выходом коммутатораусловий запуска, второй и третий информационные выходы которого соединены с третьим и четвертым входами переключателя режима соответственно,второй выход которого соединен с пя -тым входом второго дешифратора, четвертый выход которого соединен с пятым информационным входом коммутатора адреса, первый и второй информационные выходы которого являются выходом признака записи в регистр адреса блока управления, восьмой и девятый выходы первого дешифратора являются выходами сопровождения информации устройства, десятый выход является выходом признака записи в регистрвозврата, одиннадцатый выход является выходом признака записи в регистрмаски, двенадцатый выход является выходом признака записи в выходной регистр, второй выход коммутатора управляющих сигналов является выходомуправления блока памяти устройства,шестой вход узла задержки являетсявходом признака сравнения блока уп 11 12674 равления, четвертый выход узла задержки является выходом разрешения ,счета блока управления, пятый вход переключателя режима соединен с пя тым выходом второго дешифратора,шестой выход которого соединен с шестым входом коммутатора адреса, седьмой вход которого соединен с третьим входом первого дешифратора, с третьим выходом коммутатора управляющих сигналов и является выходом признака записи в регистр состояния блока управления, пятый вход коммутатора условий запуска является информационным входом блока управления,третий выход переключателя режима является выходом управления мультиплексором блока управления, четвертый и 25 12пятый входы первого дешифратора являются входами признака кода и форма-та команд блока управления, шестойвход коммутатора условий запуска яв-ляется входом запуска блока управления, шестой вход переключателя режима является установочным входом блокауправления, третий выход группы выходов блока предварительной установкисоединен с третьим входом блокастробирования, седьмой вход переключателя режима является интерфейснымвходом блока управления, четвертыйвыход коммутатора управляющих сигналов содержит выходы индикации состояния и признака выдачи информации блока управления, пятый выход коммутатора управляющих сигналов соединен стретьим входом коммутатора.1267 А 25 0 щЬ.2 ГМ ОлдлЮ длйЮ СРидю 2

СмотретьЗаявка

3756334, 25.06.1984

ПРЕДПРИЯТИЕ ПЯ Р-6429

КАРПУНИН ЕВГЕНИЙ ИВАНОВИЧ, БУЧНЕВ АЛЕКСАНДР НИКОЛАЕВИЧ, АБРОСИМОВ ЛЕОНИД НИКОЛАЕВИЧ, ВАСИЛЬЕВ НИКОЛАЙ ПЕТРОВИЧ, ГОРОВОЙ ВЛАДИМИР РОДИОНОВИЧ, КРЫЛАТЫХ ЮРИЙ ПЕТРОВИЧ, МАТАЗОВ АНАТОЛИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/26

Метки: микропрограммное, последовательности, тестовой, формирования

Опубликовано: 30.10.1986

Код ссылки

<a href="https://patents.su/15-1267425-mikroprogrammnoe-ustrojjstvo-formirovaniya-testovojj-posledovatelnosti.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство формирования тестовой последовательности</a>

Предыдущий патент: Устройство для контроля микропроцессорных программных блоков

Следующий патент: Устройство для ввода информации от двухпозиционных датчиков

Случайный патент: Устройство для приема акустических колебаний