Устройство для вычисления логических функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 942002

Автор: Ресслер

Текст

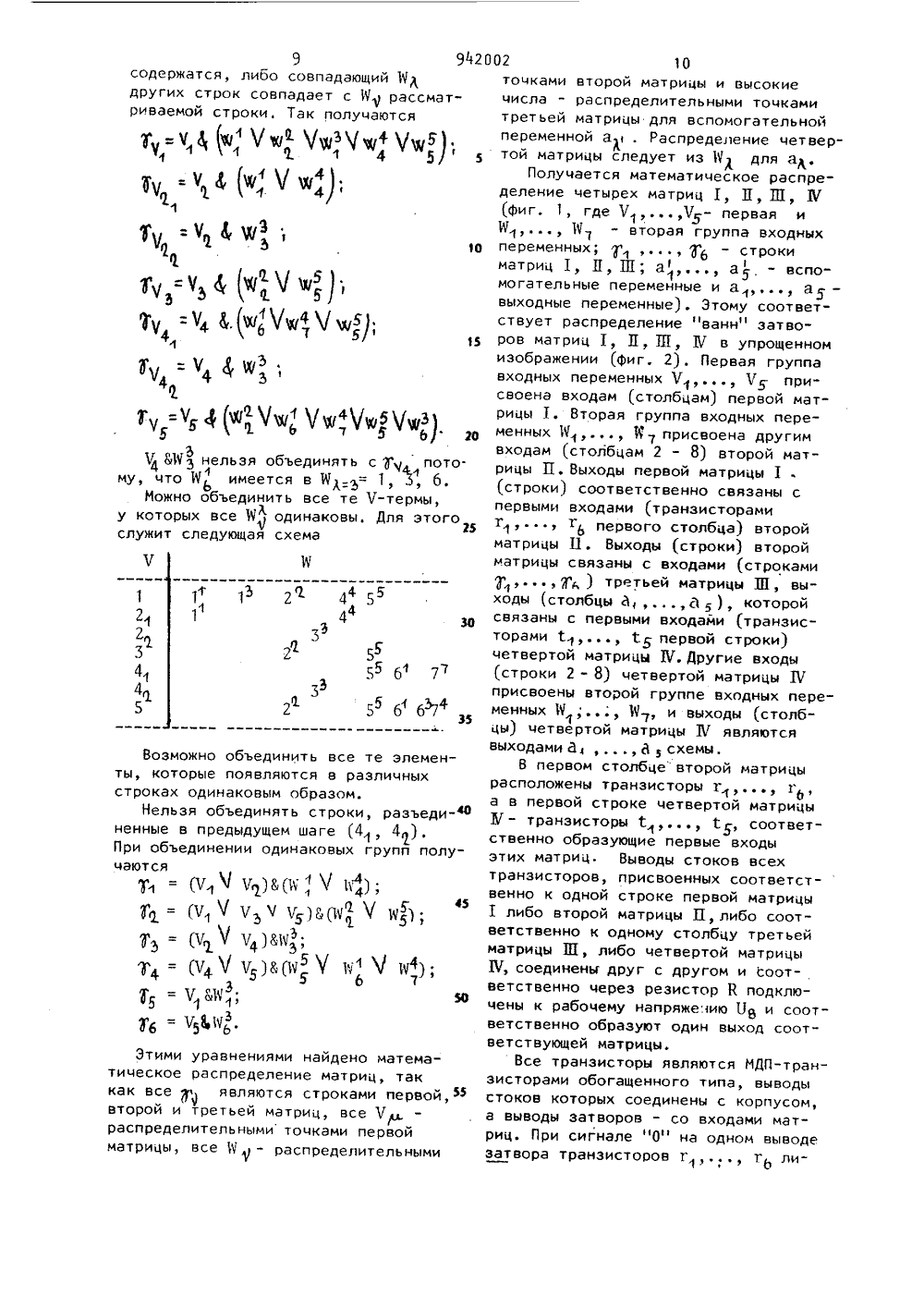

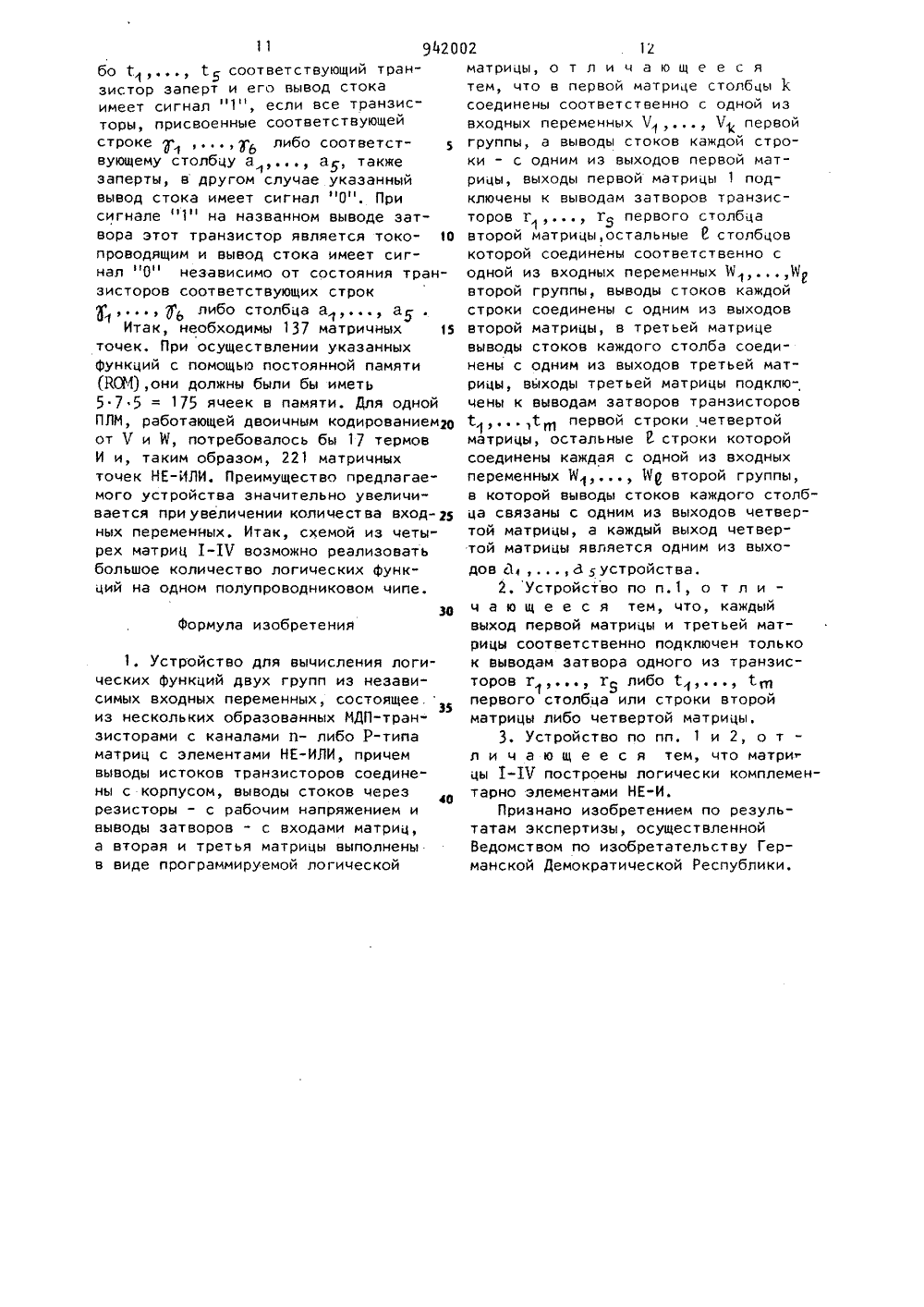

ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспублик(51) М, Кл 32) 11,03,77 С Оь 6 11 7/3811/40 Гввударстввкай квкктвт СССР кв дввам кзвбрвтвкк н вткркткй) МР 611 С/197791 (331 ГД ДК 681.3 (088. 8) 82 Ятоллетень % 25 описания 07,07.82 икован Дата опубликования остранецсслер фр(72) Автор изобретения ностранно редприятиефурт", 50 Эрфу 71) Заявител ФЕБ Функве4) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ. ЛОГИЧЕСКИХ ФУНКЦИЙ логиупСедт 4 ии Изобретение относится к устройстваи в. интегрированной МДП-технике для вычисления большого количестваческих Функций двух групп независимвх входных переменных, например для программных управлений,Предполагается, что входными переменными первой группы являются Ч , Чь, второй группы - М,1Мр В каждой из групп одна переменная имеет логическое состояние "1",все остальные - логическое состояние "0". Из входных переменных обеих групп определяются в выходные переменные а, а ,Индексы 1 с, С и в имеют значения относительно большие (около 20-40).Известно устройство для образова ния каждой из желаемых выходных переменных а агоотдельными логическими элементами из входных ,функций Ч Ч, и ИЮр(Реппеу Х е.а.МБ 3. а 1 ей стсидйя, чап Иозйтапй Кепйо 1 й Сотпрапу, Иеы дотК,1972 МНстоватх 4500; 1 пй.е 1 КцпйяеЬац, 22, 1968, 12, Я. 322).При многих входных переменных в эти устройства становятся очень слож. ными и требуют больших поверхностейчипа, Вследствие высоких затрат наэлектромонтар дан верхнийпредел дляколичества связей. Разработка тре- О бует больших затрат, потому что нужно проектировать каждый логическийэлемент в отдельности.Известно устройство для формирования п 1 выходных переменных из 1 с+1 5 входных переменных, представляющее собой постоянную память (Кпс 1 таб В1 тйедтет 1 е На 1 ЫеСетресЬет. -Е 1 еИтопИс МОпсЬеп 22, 1973, 5,Б. 174; 1,е 1 ЬЬтапй й. Йа 1 Ь 1 еет 20 Резйыетйяресйет - ТесЬпЖ и. АпъепйцпР, - Е 1 еИтопЖ МОпспеп 19, 1970,9, Я. 293-296) .Для каждой любой входной комбинаЧ 1фЧ 1 и М.1,Ир програм 3 94200 мированием может быть присвоено каж- дому из и выходов состояние "0 или, так что любая функция может быть задана программированием. Матрица имеет 1 строк и Г столбцов в каждом из щ блоков, В точке пересечения строк и столбцов матрицы в соответствии с реализуемой функцией включаются интегрированные ИДП-транзисторы в процессе изготовления изме- о нением (программированием) шаблона (это соответствует "0" или ). При вызове одной из 1 строк и одного из 1 столбцов на выходах аа возникает информация, которая запоминается в точке пересечения строки столбцов, Необходимо всего щ 1ячеек в памяти. Так, например, дляи= 15, 1= 40 и 1 = 30 необходимо всего 8000 ячеек в пямяти.20Количество блоков информации этого порядка известными средствами неможет быть интегрировано совместнос добавочно требуемой логикой управления на одном чипе, 25Известно также устройство для образования большого количества логических связей - программируемая логическая матрица ПЛИ (Тйе 1 п 1 ега 1 ес 1с 1 гсц 1 М са 1 а 1 оре Еог Йезцп ещдпеегя. - Техас 1 пзйгцщеп 1 з, 1971,ди 1 у).ПЛИ состоит из двух матриц с элементами НЕ-ИЛИ. Первая матрица управляется инвертированной входной пе 35ременной, а вторая - выходами первойматрицы. Выходы второй матрицы образуют инвертированные выходные переменные аа . При этом на выходахпервой матрицы появляетсяР, = ЕЧ Ип = ЕаЛ,Е.Входные переменные 6 6 п, входящие в выходной сигнал Р , определяются в зависимости от того, имеется45ли в точке пересечения между строкойи столбцом МДП-транзистор или нетпрограммирование).Первая матрица образует таким образом г различныхсвязей И из п входных переменных5 ВПоэтому она называетсяматрицей И,Выходами второй матрицы являютсяа = РЧФ.ЧРпа = РЧР (1) причем опять образованием или пропусканием ИДП-транзисторов в точках 2 4пересечения определяется, какой терм Р входит в выходную связь ИЛИ. Поэтому вторая матрица называется матрицей ИЛИ.Чтобы получать меньше избыточности целесообразно группы входных переменных Ч и Ю бинарно кодировать к входным сигналам 0 6 п. При этоми = бйс + Й 1) 2 Коэффициент 2 определяется необходимостью применения 0,и 1 и. Для указанного случая п = 22. Практические примеры требуют 000 и больше И-термов Р . Таким образом, для указанного примера (Рг = 1200) необходимо всего 44400 точки пересечения, которые практически не интегрируемы на одном чипе.Известные решения имеют тот недостаток, что для осуществления требуемой выходной функции из групп входных переменных затраты на логику и поверхности чипа увеличиваются таким образом, что схема неинтегрируема на одном чипе.Цель изобретения - обеспечение возможности расположения большого количества логических связей двух групп независимых входных переменных в интегрируемой МДП"технике на одном чипе путем минимизации количества логических элементов для большого количества логических связей двух групп независимых входных переменных с исключением некоторых комбинаций.Поставленная цель достигается тем, что в устройстве для вычисления логических функций двух групп из независимых входных переменных в интегрированной ИДП-технике, состоящем из нескольких образованных МДП- транзисторами с каналами п- либо Р-типа матриц с элементами НЕ-ИЛИ, причем выводы истоков транзисторов соединены с корпусом, выводы стоков через резистор - с рабочим напряжением и выводы затворов - с входами матриц, а вторая и третья матрицы выполнены в виде ПЛМ, в первой матрице столбцы 1 соединены соответственно с одной из входных переменных ЧЧ первой группы, а выводы стоков каждой строки - с одним из выходов первой матрицы, выходы первой матрицы подключены к выводам затворов трэнзисторов гг первого столбца второй матрицы, остальные 2 стогбцов которой соединены соответственно с9420 бо С С соответствующий транзистор заперт и его вывод стока имеет сигнал "1", если все транзисторы, присвоенные соответствующей строке у у либо соответствующему столбцу а а, также заперты, в другом случае указанный вывод стока имеет сигнал "0". При сигнале "1" на названном выводе затвора этот транзистор является токо О проводящим и вывод стока имеет сигнал "0" независимо от состояния транзисторов соответствующих строк.либо столбца а, аИтак, необходимы 137 матричных 15 точек. При осуществлении указанных функций с помощью постоянной памяти (КОМ),они должны были бы иметь 5 7 5 = 175 ячеек в памяти. Для одной ПЛМ, работающей двоичным кодированием 2 О от Ч и И, потребовалось бы 17 термов И и, таким образом, 221 матричных точек НЕ-ИЛИ, Преимущество предлагаемого устройства значительно увеличивается приувеличении количества вход-щ ных переменных. Итак, схемой из четырех матриц 1-1 Ч возможно реализовать большое количество логических Функций на одном полупроводниковом чипе.3Формула изобретения 1. Устройство для вычисления логических функций двух групп из независимых входных переменных, состоящее. из нескольких образованных ИДП-транзисторами с каналами п- либо Р-типа матриц с элементами НЕ-ИЛИ, причем выводы истоков транзисторов соединены с корпусом, выводы стоков через резисторы - с рабочим напряжением и выводы затворов - с входами матриц, а вторая и третья матрицы выполнены в виде программируемой логической 02матрицы, о т л и ч а ю щ е е с я тем, что в первой матрице столбцы 1 с соединены соответственно с одной из входных переменных Ч 1 Ч первой группы, а выводы стоков каждой строки - с одним из выходов первой матрицы, выходы первой матрицы 1 подключены к выводам затворов транзисторов г т первого столбца второй матрицы, остальные 1 столбцов которой соединены соответственно с одной из входных переменных Ж , ,Ю второй группы, выводы стоков каждой строки соединены с одним из выходов второй матрицы, в третьей матрице выводы стоков каждого столба соединены с одним из выходов третьей матрицы, выходы третьей матрицы подключены к выводам затворов транзисторовпервой строки четвертой матрицы, остальные Р строки которой соединены каждая с одной из входных переменных М,1 Ир второй группы, в которой выводы стоков каждого столбца связаны с одним из выходов четвертой матрицы, а каждый выход четвертой матрицы является одним из выходов Й, В 5 устроиства.2. Устройство по п.1, о т л и ц а ю щ е е с я тем, что, каждый выход первой матрицы и третьей матрицы соответственно подключен только к выводам затвора одного из транзисторов г 1 т либо С Сп первого столбца или строки второй матрицы либо четвертой матрицы.3. Устройство по пп. 1 и 2, о т л и ч а ю щ е е с я тем, что матриц цы 1-1 Ч построены логически комплементарно элементами НЕ-И.Признано изобретением по результатам экспертизы, осуществленной Ведомством по изобретательству Германской Демократической Республики./ / Тираж 731 Подписно илиал ППП "Патент Ужгород, ул. Проектн Ут5 ВНИИП каз М 8 9 Й 2002 Ю Ю О 4

СмотретьЗаявка

7770099, 21.02.1978

ФЕБ ФУНКВЕРК ЭРФУРТ

РЕССЛЕР ФРАНЦ

МПК / Метки

МПК: G06F 7/38

Метки: вычисления, логических, функций

Опубликовано: 07.07.1982

Код ссылки

<a href="https://patents.su/7-942002-ustrojjstvo-dlya-vychisleniya-logicheskikh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логических функций</a>

Предыдущий патент: Устройство для сортировки чисел

Следующий патент: Матричное множительное устройство

Случайный патент: Способ бурения скважин