Микропрограммный процессор с контролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

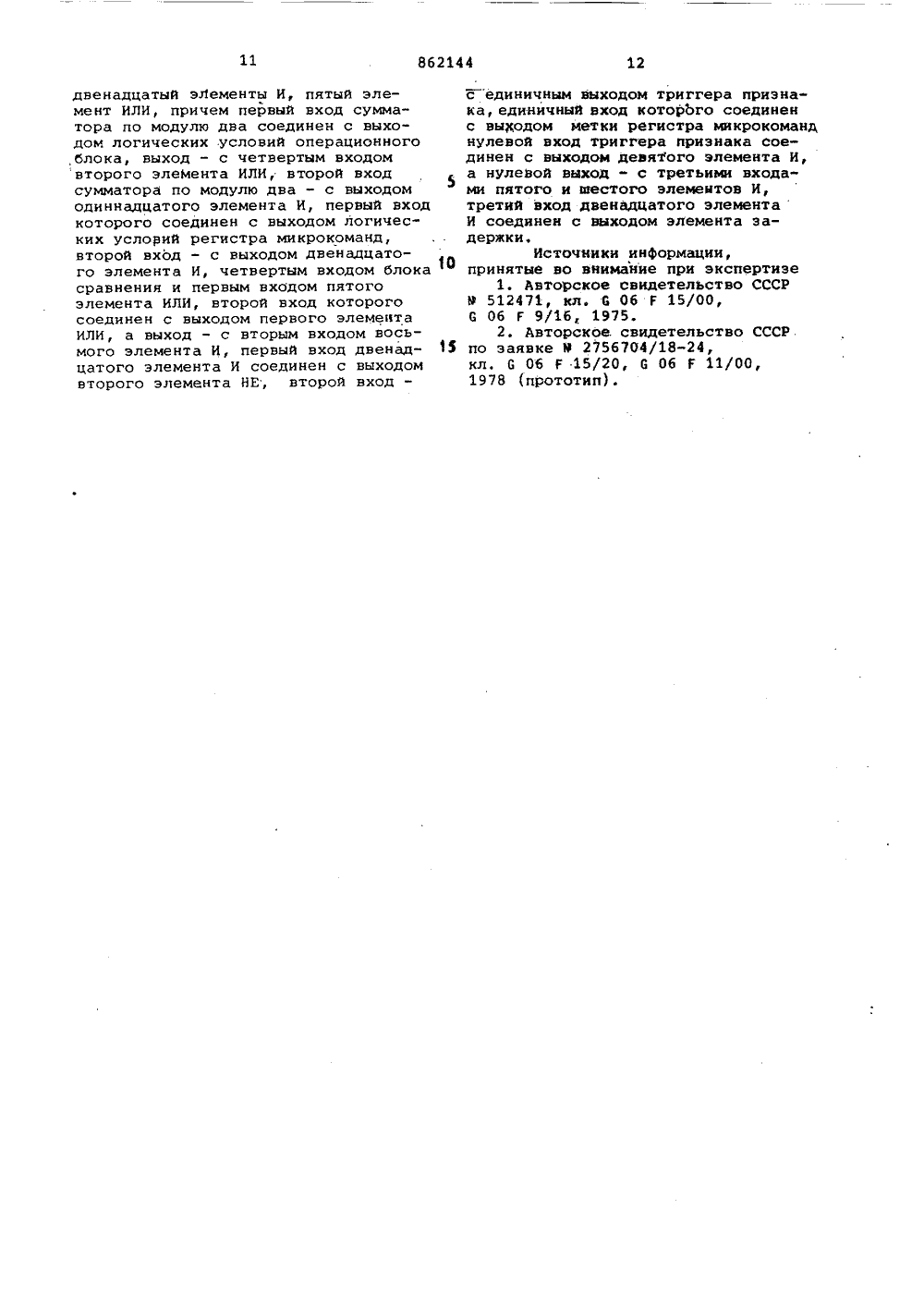

ОПИСАНИЕ ИЗОВРЕТЕНИЯ Сфеэ СаеатскикСфцмеаист ниэскиз(51)М. Кд,6 06 Г 15/00 8 06. Г 11/00 3 осулврственнмй комитет СССР ве ледам изобретений . н открытмйДата опубликование аеисаинл 070981 и.с. харченко, и.и. самарский, с.и. акачение, г.н. Ииманькин и и.и. Иаринм(72) Авторы ОПРОГРАК 4 НЫЙ ПР У С КОНТ 1 2Микропрограммный процессор с кднт которово соединен с выходом начала ролем относится к области цифровой операции Опарационного блоха и пер.- вычкслительной техники н может. бьггь вым входом первого элемента ИЛИ. Выиспользован в ЭВМ с микропрограммнымхбд первого эламента И соединен с управлением. первым входом первого регистра адреИзвестен микропрограммный процес- са, второй вход которого соединен сор с контролем, содержащий операци- с выходом второго элемента И, а выонный блок, регистры адресов микро- ХОД - С пЕРЗЫвв вхоДаьв блока. паКОМаиц И СОбетВЕННО МИКрОКОМатид, ИХО. ЗЕЕтн, трЕтЬЕтО И ЧЕтВЕртОГО ЭЛЕМЕН- блок:памяти микрокоманд, узел.срав- тов . Второй.вход третьего элемента кения, триггер фиксации сбоя и И соединен с эывсщом чтения микро- логические элементы и, или, не 11. команд операционного блока,:вторымНедостатком устройства являются входом блока камяти микрокоманд, низкая достоверность функциойирова- а также через элемент задержки с ння и низкая оперативность контроля. 1. первъв Входом пятого элемента" и,Наиболее близким по технической Выход .третьего элемейта Исоединен сущности н достигаемому эФФекту из с нервьв входом второго орегистра известных устройств к изобретению адреса, Заод блока памяти мнкрокоявляется микропрограммный процессор, манд соединен с входом регистра содержащий операционный блок, блок 2 и мнкрокоманд, аход мкрокоманд соепамяти мнкрокоманд, регистр ьвткро-, . динеи с йераеа входом операцноннокоманд, два регистра адреса, регистр го блока, адресный выход - с вторым кода операций, блок сравнения, триг- входом операционного блока и.первым гер фиксации сбоя, десять элементоввХОЮОм второго элемента И, выход И, четыре элемента ИЛИ, два элемента логлческих условий - с первым входом не, элемент задержки. Выход кода опе- юестоге адемента и. Второй вход вторации операционного блока соединен .рого элемекта И через первый элемент с входом регистра кода операции, НЖ соединен.с выходом первого злемейвыход которого соединен с первым вхо- та ЮВ; зторой вход которого соединендом первого элемента И, второй вход ф с выйодом конца операции операционно 862144го блока, первым входом седьмого элемента И, третьим входом первого регистра адреса, вторым входом второго регистра адреса, выход которого соединен с вторым входом пятого элемента И. Второй вход седьмого элемента И соединен с адресным выходом регистра микрокоманд, выход - с первым входом второго элемента ИЛИ, выход которого соединен с первым входом блока сравнения, Второй вход второго элемента ИЛИ соединен с выходом шестого элемента И, второй вход которого соединен с выходом элемента задержки и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента ИЛИ и вторым входом четвертого элемента И, выход которого соединен стретьим входом второго. элемента ИЛИ. Первый вход восьмого элемента И соединен с выходом регистра кода операций, а выход - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, а выход - с вторым входом блока сравнения, третий вход которого соединен с выходом девятого элемента И, первый вход которого соединен с выходом третьего элемента ИЛИ, Второй вход девятого элемента И через второй элемент НЕ соединен с выходом метки ре" гисРра микрокоманд и первым входом десятого элемента И, второй вход которого соединен с выходом логических условий регистра микрокоманд, а третий вход - с выходом логических условий операционного блока, третий вхоД которого соединен с выходом триггера фиксации сбоя, вход которого соединен с выходом блока сравнения. Выход десятого элемента И соединен с четвертым входом первого регистра адреса Г 23Недостатком устройства является низкая оперативность контроля соответствия выполняемой микропрограммы той микропрограмме, код которой записан в регистре кода операции.Целью изобретения является повышение оперативности контроля и достоверности функционирования микропрограммного процессора.Поставленная цель достигается тем, что в микропрограммный процессор с контролем дополнительно введены триггер признака, сумматор по модулю два, одиннадцатый и двенадцатый элементы И, пятый элемент ИЛИ, . Первый вход сумматора по модулю два соединен с выходом логических условий операционного блока, выход - с четвертым входом второго элемента ИЛИ, второй вход сумматора по модулю два - с выходом одиннадцатого элемента И,первый вход которого соединен с выходом логических условий регистра микрокоманд, второй вход одиннадцатого элемента И - с выходом двенадцатого элемента И, четвертымвходом блока сравненйя и первым входом пятого элемента ИЛИ, второй входкоторого соединен с выходом первогоэлемента ИЛИ, а выход - с вторым входом восьмого элемента И. Первыйвход двенадцатого элемента И соединен с выходом второго элемента НЕ,второй вход - с единичным выходомтриггера признака, единичный входкоторого соединен с выходом метки1 регистра микрокоманд. Нулевой входтриггера признака соединен с выходом девятого элемента И, а нулевойвыход - с третьими входами пятогои шестого элементов И, третий вход15 двенадцатого элемента И соединенс выходом элемента задержки.Сущность изобретения состоит вповышении оперативности контроля засчет увеличения числа проверок соответствия выполняемой микропрограмма .заданному коду операции, а такжев повышении достоверности функционирования за счет осуществления контроля правильности ветвления иикро 15 программыПри этом контроль соответствиявыполняемой микропрограмм заданномукоду операции и контроль правильности выполнения ветвлений в микропрограиме осуществляются одновременноЗ общиии средствами проверки. Однаковременный контроль реализуется после считывания первой микрокоманды,следующей за очередным ветвлениеми в микропрограмме. Это позволяетЗЗ повысить оперативность контроля соответствия заданного кода операции вы"полняемой микропрограмме и довестиее до среднего времени между ветвлениями, а также повысить достоверность40 функционирования за счет органиэацииконтроля ветвлений.На чертеже приведена функциональная схема микропрограммного процессора с контролем,На чертеже использованы следующиеобозначения."операционный блок 1, выходы логических условий, начала операции,конца операции, кода операции ичтения мнкрокоманд 2-6 соответственно, первый элемент ИЛИ 7, и регистркода операций 8, первый элемент НЕ 9,первый элемент Й 10, второй элементИ 11, десятый элемент И 12, первыйрегистр адреса 13, блок памяти микИ рокоманд 14, регистр иикрокоманд 15с полями адресными 16, микрокоманд17, логических условий 18, метки 19,седьмой элемент И 20, второй элементНЖ 21, одиннадцатый элемент И 22,щ сумматор по модулю два 23, триггерпризнака 24, двенадцатый элементИ 25, элемент задержки 26, шестойэлемент И 27, второй элемент ИЛИ 28,третий элемент И 29, второй регистрадреса ЗО, пятый элемент И 31, четЧерез четвертый элемент ИЛИ 33 адрес, записанный во второй регистр адреса 30, поступает на второй вход 41 блока сравнения 39.С выхода элемента задержки 26 через времяфГ сигнал считывания микрокоманд поступает на первый вход девятого элемента И 35 через третий эЛемент ИЛИ 34, на второй вход которого поступает разрешающий сигнал с выхода метки 19 регистра микрокоманд 15. Сформированный сигнал с выхода девятого элемента И 35 поступает на третий вход 42 блока сравнения 39. При этом контролируется правильность считывания микрокоманды путем сравнения поступивших на его первые 50 55 66 65 вертый элемент И 32, четвертый элемент ИЛИ 33, третий элемент ИЛИ , 34 девятый элемент И 35, пятый элемент ИЛИ 36, восьмой элемент И 37, триггер фиксации сбоя 38, блок сравнения 39, первый - четвертый входы 40- 43 блока сравнения соответственно, выход 44 блока сравнения.Первый регистр адреса 13 предназначен для хранения адреса очередной микрокоманды во время выполнения текущей микрокоманды.Второй регистр адреса 30 предназначен для хранения кода адреса, поступившего с первого регистра адреса 13 на время считывания микрокоманды из блока памяти микрокоманд 14. Микропрограммный процессор работает следующим образом,Выполнение каждой команды разделе-.но на два цикла: цикл выборки команды и цикл ее исполнения в соответствии с кодом операции, Первый циклявляется общим для всех команд, в товремя как цикл исполнения состоитиз различных микропрограмм для различных команд.В конце цикла выборки команды иадресных преобразований код операций поступает в регистр кода операций 8; и операционный блок 1 формирует сигнал начала операции. По этому сигналу код операции поступаетчерез первый элемент И 10 в первыйрегистр адреса 13.Правильность записи кода опера-ции в регистр адреса 13 контролируется путем сравнения его содержимогос содержимым регистра кода операций8 по сигналу начала операции, пос- .тупающего из операционного блоха 1,По этому сигналу адрес первоймикрокоманды с выхода первого регистра адреса 13 поступает через четвер"тый элемент И 32 на третий вход второго элемента ИЛИ 28 и далее на первый вход 40 блока сравнения 39.Одновременно с этим сигнал начала операции с выхода первого элемента ИЛИ 7 поступает через пятый элемент ИЛИ 36 на второй вход восьмогоэлемента И 37, Разрешая прохождениекода операции с выхода регистра кодаоперации .8 через четвертый элементИЛИ 33 на второй вход блока сравнения 39. Далее происходит сравнениеуказанных кодов по сигналу началаоперации, который поступает с выходапервого элемента ИЛИ 7 через третийэлемент ИЛИ 34 и открытый девятыйэлемент И 35 на третий вход 42 блокасравнения 39. Если коды йе совпадают,то на выходе 44 блока сравнения 39формируется сигнал, который поступает на вход триггера фиксации сбоя38 и запрещает дальнейшую работуоперационного блока 1. Если кодысовпадают, то работа процессора про-должается. На выходе чтения микро 5 Я 15 20 25 ЗО 35 40 У 45комаид 6 операцгэнного блока 1 формируется сигнал, по которому происходит считывание микрокоманды по соответствующему адресу из блока памяти ьгкрокоманд 14. Этот же сигнал поступает на второй вход третьего элемента И 29, и адрес микрокоманды записывается во второй регистр адреса 30. Через время Г (время счнты 9вания одной микрокоманды из блока памяти микрокоманд 14) в адресном поле 16 регистра микрокоманд 15 формируется адрес следующей микрокоманды, который поступает на первый вход второго элемента И 11, открытый элементом НЕ 9.(во время выполнения яюкропрограюи сигнала на выходах начала и конца операции и выходе элемента ИЛИ 7 отсутствуют), и на второй вход операционного блока 1. Проходя через элемент И 11, адрес записывается в первый регистр адреса 13.На первый вход операционного блока 1 поступает операционная часть считанной микрокоманды с поля микро- команд 17 регистра микрокоманд 15.С поля логических условий 18 регистра микрокоманд 15 считывается адрес исполняемой микрокоманды, который поступает на первый вход шестого элемента И 27. В это время на его второй вход. поступает сигнал с выхода чтения микрокоманд 6 через элемент задержки 26, а на третий вход - единичный сигнал с нулевого выхода триггера признака 24. Адрес выполняемой микрокоманды через второй элемент ИЛИ 28 поступает на первый вход 40 блока сравнения 39. После записи адреса выполняемой микро- команды во второй регистр адреса 30 через время 7 на первый вход пятого элемента И 31 поступит сигнал, разрешающий передачу адреса, записанного во втором регистре адреса, на второй вход четвертого элемента ИЛИ 33. Передача адреса возможна, поскольку на третий вход пятого элемента И 31 поступает единичный сигнал с нулевого выхода.триггера признака 24два входа кодов, В зависимости отрезультатов сравнения кодов адресовработа процессора аналогична описанной выше. В дальнейшем при считываниимикрокоманд из блока памяти микрокоманд 14 контроль порядка и правильности их считывания осуществляетсяаналогично,При выполнении микрокоманды ветвления в поле логических условий,18 регистра.микрокоманд 15 записывается код проверяемого логическогоусловия. Он поступает на второй входдесятого элемента И 12, на первый еговход поступает единичное значение свыхода метки 19 регистра микрокоманд15, а на третий - значение проверяемого логического условия. В результате формируется (модифицируется)адрес следующей микрокоманды. Единичным сигналом с выхода метки 19регистра микрокоманд 15 триггер признака 24 устанавливается в единичноесостояние, и на его единичном выходепоявляется разрешающий сигнал, который поступает на второй вход двенадцатого элемента И 25,При этом .не происходит сравнениязначений кодов, записанных в полелогических условий 1 р регистра микрокоманд 15, и содержимого второгорегистра адреса 30, поскольку на второйовход девятого элемента И 35 поступает нулевое значение с выходаметки 19 регистра микрокоманд 15 исигнал на разрешение сравнения отсутствует, На третий вход шестогоэлемента И 27 поступает нулевой сигнал с нулевого выхода триггера признака 24, запрещая передачу информации в блок сравнения 39. После считывания первой мнкрокоманды послеветвления в поле метки 19 регистрамикрокоманд 15 появляется нулевойсигнал, который инвертируется вторым элементом НЕ 21 и поступает напервый вход двенадцатого элементаИ 25, на второй вход которого поступает единичный сигнал с выходатриггера признака 24 и с выхода чтения микрокоманд 6.,На выходе формируется сигнал разрешения, который,поступает на второй вход одиннадцатого элемента И 22На первый входэлемента И 22 поступает контрольныйпризнак, записанный в поле логических условий 18 первой микрокомандыпосле ветвлений. В качестве контрольного признака выступает код операции,модифицированный значением проверяемого. логического условия. Модифицированный таким образом код поступаетна второй вход сумматора по модулюдва 23, на первый вход которого поступает значение проверяемого логического условия. На выходе сумматораПо-модулю два 23 в результате форми-.руется фактическое значение кодаоперации, которое поступает на четвертый вход второго элемента ИЛИ 28и далее на первый вход 40 блока сравнения 39.Сигнал разрешения с выхода двенадцатого элемента И .25 поступаеттакже на первый вход пятого элементаИЛИ 36 и с его выхода на второй входвосьмого элемента И 37. В результатедействительное значение кода операции с выхода регистра кода операции8 через четвертый, элемент ИЛИ ЗЗ поступает на второй вход 41 блока сравнения 39. Одновременно с этим на четвертый его вход 43 поступает сигнална разрешение сравнения кодов с выхода элемента И 35, а затем сигналомс выхода элемента Й 35 триггер признака 24 устанавливается в нуль. Далее работа процессора аналогичнаописанной выше.Одновременно с контролем соответ ствия выполняемой микропрограммызаданному коду операции осуществляется контроль правильности ветвлений.При ошибочном переходе поюьученный в результате суммирования контрольного. признака и значения проверяемого логического условия код несовпадает с требуемюм кодом операциии на выходе 44 блока сравнения 39формируется сигнал отказа.В дальнейшем процессор реализуетоставшуюся часть микропрограммою,осуществляя контроль правильностисчитывания и порядка следования микрокоманд и проверяя принадлежностьмикрокоманд заданной микропрограммепо описанным .выше алгоритмам.При считывании последней микрокоманды в поле логических условий 18регистра ьыкрокоманд 15 записывается 40 адрес считанной микрокоманды, а вадресном поле 16 - код выполняемойоперации, По сигналу считывания,задержанному элементом задержки 26,блок сравнения 39, аналогично описанному выше, осуществляет сравнениекодов, поступивших из поля логических условий 18 регистра микрокоманд15 и второго регистра адреса 30.. По сигналу конца операции первыйи второй регистры адреса 13 и 30соответственно обнуляются, а блоксравнения 39 сравнивает содержимоеадресного поля 16 регистра микрокоманд 15 и регистра кода операций 8.При этом на первый вход 40 блокасравнения 39 через второй элементИЛИ 28 а выхода седьмого элементаИ 20 поступает .фактическое значе-.ние кода.операции, а на второй вход41 - требуемое значение кода опера ции с выхода регистра кода операции8 Кроме того, на первый вход блокасравнения. 30 поступает код через четвертый элемент И 32, Если суммарныйкод первого регистра адреса 13 и Я адресного поля 16 регистра микрокоманд 15 равен коду, записанному в регистре кода операции 8,. это означает, что микропрограмма выполнена в соответствии с заданным кодом операции, а первый регистр адреса 13 работоепособен и находится в нулевом состоянии. В этом случае процессор переходит к выполнению цикЛа выборки следующей команды.ВЕсли сравниваемые коды не равны, блок сравнения 39 Формирует сигнал, 10 который триггер Фиксации сбоя 38, передает в операционный блок 1. Й результате операционный блок 1 инициирует повторение участка микропрограммы или выполнение диагностическойми кропрограмьа.В процессоре проверяются такжесредства контроля его Функционирова-. 5 ния. При их отказе коды, сравниваемые 40 формула изобретения Микропрограммный процессор с контролем, содержащий операционный. блок, 45блок памяти микрокоманд, регистр микрокоманд, два регистра адреса, регистр кода операций, блок сравнения,триггер Фиксации сбоя, десять элементов И, четыре элемента ИЛИ, два элемента НЕ, элемент задержки, причем выход кода операции операционного блока соединен с входом регистра.кода операции, выход которого соединенпервым входом первого элемента И 55 второй вход которого соединен с выходом начала операции операционного блока и первым входом первого элемента. ИЛИ, выход первого элемента И соединен с первым входом первого регистра адреса, второй вход которого 40 соединен с выходом второго элемента И, а выход - с первыми входами блока памяти, третьего и четвертого элементов И, второй вход третьего элемента И соединен с выходом чтения блоком сравнения 39, будут отличать ся, что приведет к срабатыванию триг гера Фиксации сбоя 38.Таким образом, введение новых элементов и связей позволяет существенно повысить достоверность Функционирования микропрограммного процес сора за счет повышения полноты контроля всех этапов выполнения микро-. програюн. При этом также увеличивается оперативность контроля соответствия выполняемой микропрограммы заданному коду операции. Это, в свою очередь, позвоЛяет более эффективно решать задачу восстановления искаженной информации и задачу локализации отказавших элементов, поскольку момент обнаружения отказа (начало, конец операции, линейный участок, ветвление) дает возможность значительно уменьшить количество подозреваемых элементов. микрокоманд операционного блока, вторым входом блока памяти микрокоманд,а также через элемент задержки с первым входом пятого элемента И, выход третьего элемента И соединен с первым входом второго регистра адреса, выход блока памяти микрокоманд соединен с входом регистра микрокоманд, выход микрокоманд которого соединен с первым входом операционногоблока, адресный выход - с вторым входом операционного блока и первым входом второго элемента И, выход логических условий - с первым входом шестого элемента И, второй вход второго элемента И через первый элемент НЕ соединен с выходом первого элемента ИЛИ, второй вход которого соединен с выходом конца операции операционного блока, первым входом седьмого элемента И, третьим входом первого регистра адреса, вторым входом второго регистра адреса, выход которого. соединен с вторым входом пятого элемента И, второй вход седьмого элемента И соединен с адресным выходомрегистра микрокоманд, выход седьмого элемента И соединенс первым входом:второго элемента ИЛИ,выход которого соединен с первым входом блока сравнения, второй вхоп второго элемента ИЛИ соединен с выходом шестого элемента И, второй входкоторого соединен с выходом элемента задержки и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элементаЛИ и вторым входом четвертого элеента И, выход которого соединен с ретьим. входом второго элемента ИЛИ, первый вход восьмого элемента И соединен с выходом регистра кода операций, а выход - с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, а выход - с вторым входом блокИ сравнения, третий вход которого соединен.с выходом девятого элемента И, первый вход которого соединен с выходом третьего элеменТа ИЛИ, второй Вход девятого элемента И через второй элемент НЕ соединен с выходом метки регистра микрокоманд и первым. входом десятого элемента И,.второй вход которого соединен с выходом логических условий регистра микрокоманд, а третий вход - с выходом логических условий операционного блока, третий вход которого соединен с выходом триггера фиксации сбоя, вход которого соединен с выходом блока сравнения, выход десятого элемента И соедйнен с четвертым входом первого регистра адреса, о т л ич а ю щ и й с я тем, что., с целью повышения достоверности Функционирования и оперативности контроля, в него введены триггерпризнака, сумматор по модулю два, одиннадцатый ндвенадцатый эЛементы И, пятый элемент ИЛИ, причем первый вход сумматора по модулю два соединен с выходом логических .условий операционного,блока, выход - с четвертым входомвторого элеМента ИЛИ, второй входсумматора по модулю два - с выходомодиннадцатого элемента И, первый входкоторого соединен с выходом логических условий регистра микрокоманд,второй вход - с выходом двенадцатого элемента И, четвертым входом блокасравнения и первым входом пятогоэлемента ИЛИ, второй вход которогосоединен с выходом первого элементаИЛИ, а выход - с вторым входом восьмого элемента И, первый вход двенадцатого элемента И соединен с выходомвторого элемента НЕ, второй вход -с единичным выходом триггера признака, единичный вход которЬго соединенс выходом метки регистра микрокоманднулевой вход триггера признака соединен с выходом девятого элемента И,а нулевой выход - с третьими входами пятого и шестого элементов И,третий вход двенадцатого элементаИ соединен с выходом элемента задержки,Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 512471, кл. 6 06 Г 15/00,6 06 Г 9/16, 1975.2. Авторское. свидетельство СССР.по заявке 9 2756704/18-24,кл. С Об Г 15/20, О Об Г 11/00,1978 (прототип).

СмотретьЗаявка

2869691, 15.01.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ

МПК / Метки

МПК: G06F 11/20

Метки: контролем, микропрограммный, процессор

Опубликовано: 07.09.1981

Код ссылки

<a href="https://patents.su/7-862144-mikroprogrammnyjj-processor-s-kontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор с контролем</a>

Предыдущий патент: Устройство для обнаружения и исправления ошибок в системе остаточных классов

Следующий патент: Устройство для определения максимальных путей в графах

Случайный патент: Шихта для изготовления керамического материала