Устройство для обнаружения ошибокв параллельном -разрядном кодес постоянным becom

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

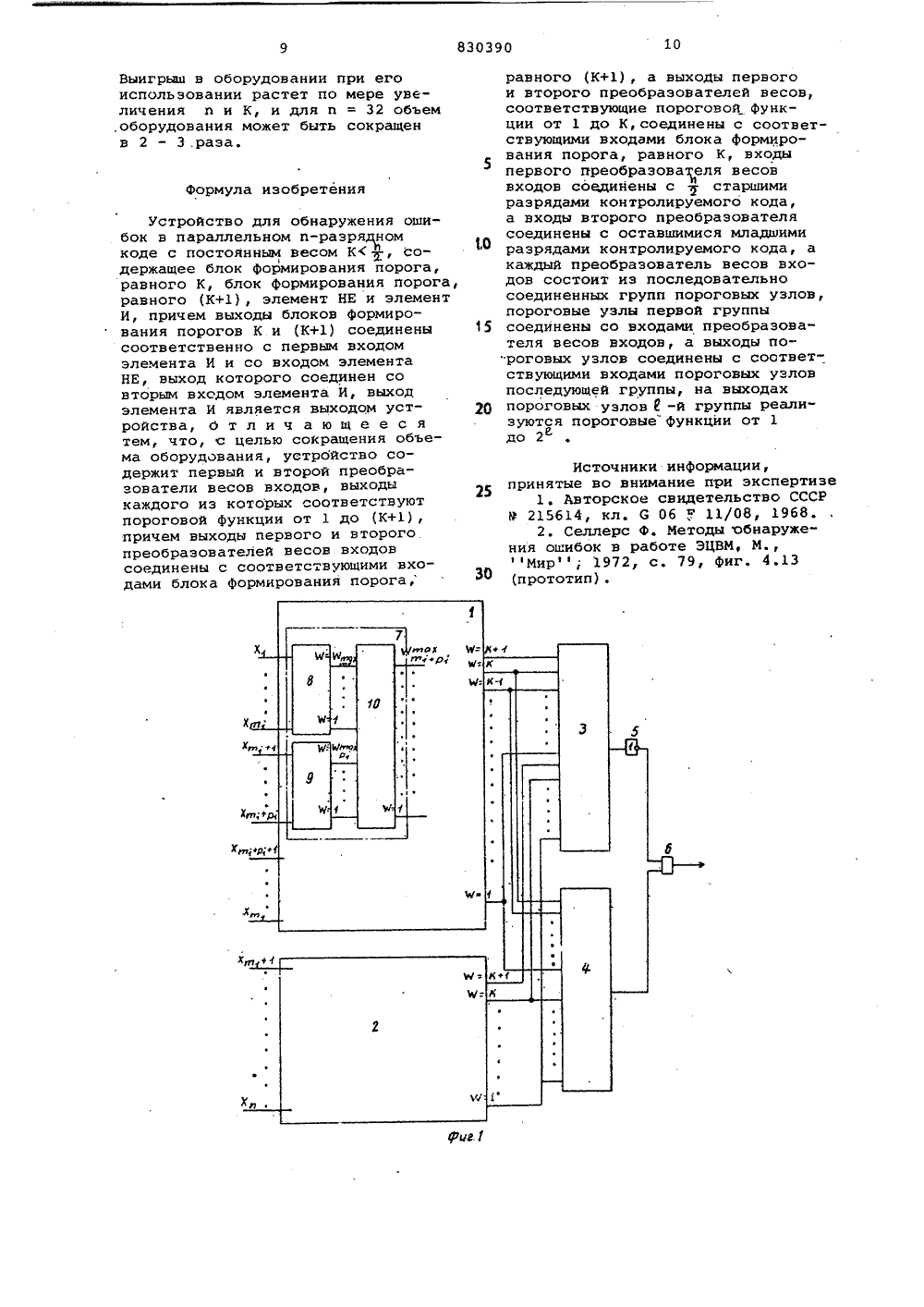

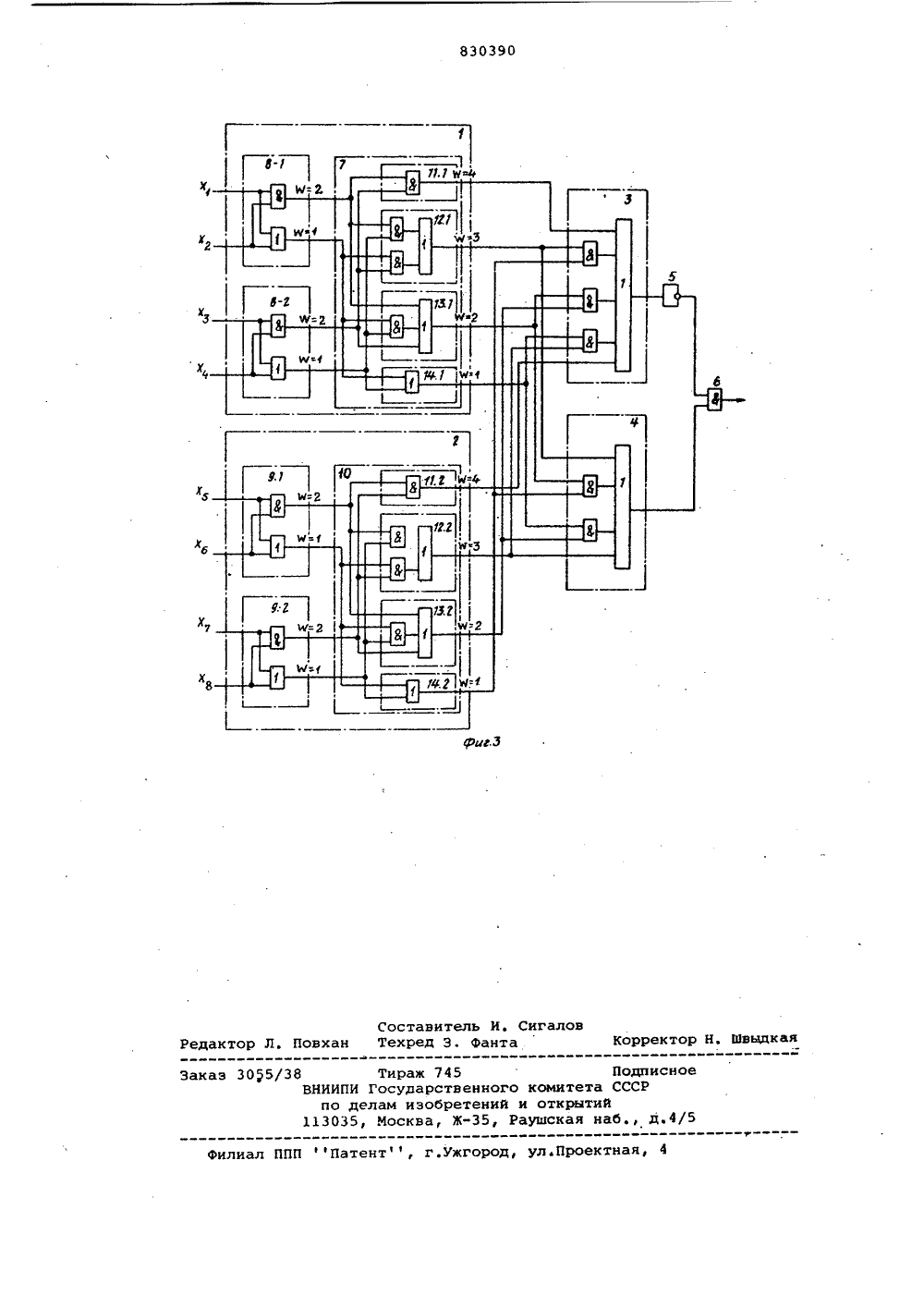

Союз Советскик Социалистических Республик(5)м. кл.з с присоединениемзаявки Ио 6 06 Р 11/08 Государственный комитет ССОР о делам изобретений и открытийР 2) Авторы иэобретеии инградскнй ордена Красного Знамени механический институт) УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В ПАРАЛЛЕЛЬНОМ И-РАЗРЩНОИ КОДЕ С ПОСТОЯННЫИ ВЕСОИ К-в" них факторов,и вреработы устройства, обходнмостью перемаг ечников, не обеспеной надежности фуниз-за не ентичности к автоманике ипостроебработки-Однако ввозможныхэывается оединицамихарактерисков и изме этом устройств ходов практиче раниченным нес з-за неидентнч ик магни 1 ных с ения их параме число 2 ки окаолькнми ости рдечниров под Изобретение относитсятике и вычислительной техможет использоваться дляния различных устройств одискретной информации.Известно устройство для обнаружения ошибок в параллельном и-раз- рядном коде с постоянным весом ь, содержащее 2 п входных и два выходных сердечника, диоды и схемы совпадения, при этом выходные парафаэные обмотки входного сердечника через диоды последовательно соединены с соответствующими данному разряду входными обмотками записи или запрета двух выходных сердечников, параллельные ветви обмоток всех разрядов соединены последовательно и замкйуты в кольцо через резистор, выходные обмотки выходных сердечников соединены со схемой совпадения, выход которой соот ветствует результату контроля 1 1,действием внешмени. Принципсвязанный с неннчивания сердчивает достатокционирования идих параметров,Кроме того это устройствоимеет импульсные входные и выходныесигналы и требует для работы подачи целого ряда сннхронизирующих сигналов, из-за чего оно плохо согласуется с логическими узлами современных цифровых устройств, имеющихпотенциальные входные и выходныесигналы.Наиболее близким к предлагаемому.является устройство для обнаружения ошибок в параллельном и-разрядном коде с постоянным весом К, содержащее два пороговых элемента спорогами (К+1) и К, причем выходпервого соединен со входом инвертора, соединенного выходом со входомвыходного элемента И, второй входкоторого соединен с выходом порогового элемента с порогом К 2),Однако. данное устройство имеетбольшой объем оборудования, так кактребует для своей реализации два попороговая функция в+Р, а еговходы соединены с выходами пороговв и Р; пороговых узлов предыдущегоуровня. Каждый пороговый узел 12)в, Р ) состоит из двух входовых элементов И, соединенных входами с выходами групп 8 и 9 пороговых узлов, образуя на входах всенеповторяющиеся комбинации весовпар их входов, сумма которых одинакова и равна весу выхода узла,выходы элементов И соединены совходами элемента ИЛИ, выход которого является выходом пороговогоузла соответствующего порога.Каждый пороговый узел 13, реализующий пороговую функцию )(2) с щ2( Р 1), состоит из элементов И,входы которых соединены с выходами групп пороговых узлов 8 и 9 предыдущего уровня аналогично пороговым узлам 12, выходы элементов Исоединены со входами элемента ИЛИ,дополнительные входы которого соединены с выходами групп пороговыхузлов 8 и 9, реализующих пороговуюфункцию. Узел 14 формирования веса1 состоит из элемента 14 ИЛИ, входы которого соединены с выходамигрупп 8 и 9 пороговых узлов предыдущих уровней,соответствующихединичным весам.Функционирование предлагаемого устройства для обнаружения ошибок в параллельном и-разрядномкоде с постоянным весом происходит следующим образом,Пусть на его входы подано д единичных потенциалов (Фиг.1). Из,них О на входы преобразователя1 и Она входы преобразователя 2весов входов, Так как каждый преобразователь реализует на своихвыходах пороговые функции с порогом, равным весу выхода, то навсех выходах преобразователя 1весов входов с весами, не превышающими д, и на всех выходахпреобразователя 2 весов входовс весами, не превышающими д появляются единичные потенциалы,которые поступают на входы блоков 3 и 4 формирования порогов. Навыходе блока 3 формирования порога, равного (К+1), соединенноговходами с выходами преобразователей 1 и 2, реализуется пороговаяфункция с порогом (К+1), а на выходе блока 4 формирования порога -пороговая функция с порогом К.Если величина К равна д, то единичный потенциал появляется на выходе блока 4 фррмирования порога,а на выходе блока 3 формированияпорога при этом появляется нулевой потенциал, что вызывает на выходе элемента И б единичный потенциал. Если бК, то единичный по 0 15 20 25 30 35 45 50 60 тенциал появляется на выходах обоих блоков 3 и 4 формирования порога.При этом на входе элемента И б,соединенном с выходом инвертора 5,появляется нулевой потенциал, чтовызывает нулевой потенциал на еговыходе. Если дс К, то нулевой потенциал появляется на выходах обоихблоков 3 и 4 формирования порога,что вызывает на выходе элемента И бнулевой потенциал, так как на еговходе, соединенном с выходом блока4 Формирования порога, нулевой потенциал, Таким образом, каждый раз,когда число единичных потенциаловЙ на входах устройства равно К, наего выходе единичный потенциал,если 0К или дК К , то на выходеустройства нулевой потенциал.Рассмотрим более подробно функционирование предлагаемого устройства для .обнаружения ошибок в параллельном п-разрядном коде с постоянным весом К 1 на примере его реа 2лизации для случая п=8 и К=З.Устройство состоит из преобразователя 1 весов 4-х входов х 1+ х 4и преобразователя 2 весов 4-х входов х+ х 1, которые соединены выходами с входами каскада 3 формирования порога, равного 4, и каскада 4 формирования порога, равного 3.Выход каскада 3 формирования порога соединен с входом инвертора 5,выход которого соединен с однимвходом выходного элемента И б,другой вход которого соединен с выходом каскада 4 формирования порога. Каскад 3 формирования порогасостоит из трех элементов И, соединенных выходами со входами элемента ИЛИ, четвертый и пятый входыкоторого соединены с выходами преобразователей 1 и 2 с весами и=4.Входы элементов И соединены с выходами преобразователей 1 и 2 с весами 3 и 1, 2 и 2, 1 и 3 соответственно, Каскад 4 формирования порога состоит из двух элементов И,соединенных выходами со входамиэлемента ИЛИ, третий и четвертыйвходы которого соединены с выходами преобразователей 1 и 2 с весами ы=З. Входы элементов И соединены с выходами преобразователей 1и 2 с весами 2 и 1, 1 и 2 соответственно.Преобразователь 1 весов 4-х вхо дов состоит из групп 7 - 10 пороговых узлов. Пороговые узлы первогоуровня 8,1, 8.2, 9.1 и 9.2 Формируют на своих выходах пороговые функции от 1 до 2, каждый пороговыйузел первого уровня состоит из элементов И и ИЛИ, входы которых попарно объединены, а выходы образуют пороговую функцию 2 и 1 соответственно. Пороговый узел 11 Формированияпорога, равного 4, выполнен на элементе И. Пороговый узел 12 Формиро 830390вания порога, равного 3, состоитиз двух элементов И и элемента ИЛИ,На входы элементов И поступают выходы групп 8 и 9 пороговых узлов предыдущих уровней, с порогом 2 и 1на первый элемент И и 1 и 2 на второй. Пороговый узел формированияпорога 2 состоит из элемента И, соединенного входами с выходами группыпороговых узлов предыдущего уровня 8.1, 8,2 (9,1, 9.2) на выходахкоторых реализуется пороговая функ Оция, равная единице, и элементаИЛИ, соединенного одним выходом свыходом элемента ИЛИ, а двумя дополнительными входами с выходамигруппы пороговых узлов, реализующих пороговую функцию 2. Пороговыйузел 14 формирования порога, равного 1, выполнен на элементе ИЛИ,вхОды которого соединены с выходами пороговых узлов предыдущей группы 8.1, 8,2 (9.1, 9.2), реализующих порог, равный 1. На выходахпреобразователей весов двух входовреализуются функцйи И и ИЛИ, являющиеся пороговыми функциями от двухпеременных с порогами, равными 2 и 1 25соответственно, т.е. с порогами,равными весам выходов. На выходахпреобразователя 1.и 2, например навыходе преобразователя 1, реализуются функции:Й (х 1 ч х Д ч(ХЧ х 4) - ЯЯи Б х - 1АГ - (Хч х 1) (хЧ х 4)ч ххчхх, =Я 9 и фх Й (х.У х 2) ( хчх 4) ч (х ъч 4)(х 1 х 2) БЯи Йх 3Е 4 = (х 4 х ) (хх 4 ) = Яуи р х -4 ,которые являются порогбвыми функциями 4-х переменных с порогами 1 - 4, 35т.е. с порогами, равными весам выходов,Пусть на входы преобразователя1 подано 2 единичных потенциала,при этом единичные потенциалы появляются на его выходах с весами и=1и и=2которые поступают на входыэлементов И блоков 3 и 4. Однако навторых входах всех элементов Иуказанных блоков, а также на входах элементов ИЛИ, соединенных 45с выходами преобразователей 1 и 2,имеются нулевые потенциалы, приэтом нулевые потенциалы появляются на выходах блков 3 и 4, а следовательно, и на выходе элемента И б, являющемся выходом устройства.При подаче единичного потенциала на один из входов преобразователя 2 единичный потенциал появляется на его выходе с единичнымвесом и поступает на входы элементов И блоков 3 и 4, При этом навходах элемента И блока 4, соединенного входами с выходами преобразователей 1 и 2 с весами и=2 и 60ы=1 соответственно, появляютсяединичные потенциалы, что вызываетединичный потенциал на его выходе ина выходе элемента ИЛИ, являющемсявыходом блока 4, При этом на обоих б 5 входах элемента И 6 появляются еди- ничныепотенциалы, что вызывает единичный потенциал на его выходе, являющемся выходом устройства.Пусть на вход преобразователя 1 подан еще один единичный потенциал, при этом единичный потенциал по-является на его выходе с весом я=3. Единичный потенциал с данного выхода преобразователя 1 поступает на вход элемента ИЛИ блока 4, подтверждая единичный потенциал на его выходе, а также на вход элемента И блока 3, второй вход которого соединен с выходом преобразователя 2 с единичным весом, При этом на выходе данного элемента И появляется единичный потенциал, который вызывает единичный потенциал на выходе элемента ИЛИ, являющемся выходом блока 3. При этом на выходе инвертора5 появляется нулевой потенциал, который вызывает нулевой потенциал на выходе элемента. И б , являющемся выходом устройства. Таким образом, единичный потенциал на выходе устройства появляется только втех случаях, когда на его входах точно 3 единичных потенциала, независимо от того, на какие входы они поданы.Построение устройства для обнаружения ошибок в параллельном и-разрядном коде с постоянным весом КИ/2 предлагаемой структуры позволяет сократить объем оборудования для его реализации, Так для реализации известного и предлагаемого устройства при К 2 требуется элементов И и ИЛИ (без учета ограничений по числу входов) для и = 8 - 40 и 26 соответственно, для и = 16 - 81 и 58, для и = 32 164 и 122, для и = 64 - 299 и 250. Однако более точным показателем сложности является количество двухвходовых элементов И и ИЛИ, которое составляет для известного и предлагаемого устройства соответственно: для и = 8 - 53 и 31, и = 16 51 и 71, и = 32 - 489 и 151, и 64 - 1547 и 309. Следовательно, выигрыш в оборудовании при использовании предлагаемого устройства составляет по количеству элементов, без учета реальных ограничений на число входов: для и = 8 - в 1,54 раза, для и = 16 - в 1,4 раза, для и = 32 - в 1,35 раза, для и = 64 - в 1,17 раза. А по объему оборудования (по числу двухвходовых элементов) для и = 8 в 1,7 раза, для и = 16 - в 2,13раза, для и = 32 - в 3,15 раза, дляи = 64 - в 5 раз.Таким образом, предлагаемоеустройство требует для реализациисущественно меньшего объема оборудования по сравнению с известным .0 15 20 25 ЗО Выигрыш в оборудовании при егоиспользовании растет по мере увеличения и и К, и для и = 32 объем,оборудования может быть сокращенв 2 - 3 .раза. формула изобретения Устройство для обнаружения ошибок в параллельном п-разрядном коде с постоянным весом К( , содержащее блок формирования порога, равного К, блок формирования порога, равного (К+1), элемент НЕ и элемент И, причем выходы блоков формирования порогов К и (К+1) соединены соответственно с первым входом элемента И и со входом элемента НЕ, выход которого соединен со вторым входом элемента И, выход элемента И является выходом устройства, О т л и ч а ю щ е е с я тем, что, а целью сокращения объема оборудования, устрбйство содержит первый и второй преобразователи весов входов, выходы каждого из которых соответствуют пороговой функции от 1 до (К+1), причем выходы первого и второго преобразователей весов входов соединены с соответствующими входами блока формирования порога,равного (К+1), а выходы первого и второго преобразователей весов, соответствующие пороговой функции от 1 до К,соединены с соответствующими входами блока формирования порога, равного К, входы первого преобразователя весов входов соЕдинены сстаршими разрядами контролируемого кода, а входы второго преобразователя соединены с оставшимися младшими разрядами контролируемого кода, а каждый преобразователь весов входов состоит из последовательно соединенных групп пороговых узлов, пороговые узлы первой группы соединены со входами преобразователя весов входов, а выходы по"роговых узлов соединены с соответствующими входами пороговых узлов последующей группы, на выходах пороговых узлов 1 -й группы реализуются пороговые функции от 1 до 2 Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 215614, кл. 6 06 " 11/08, 1968.2. Селлерс ф. Методы обнаружения ошибок в работе ЭЦВМ, М.,Мир; 1972, с. 79, фиг. 4.13830390 Г Составитель И. Сигаловактор Л. Повхан Техред 3. фанта Коррект Заказ 305/38ВН сно д.4 5 113 филиал ППП Патент, г.ужгород, ул.Проектная,Тираж 745 ПИ Государственн делам изобретен 35, Москва, ЖПодпго комитета СССй и открытийРаушская наб.,

СмотретьЗаявка

2755476, 19.04.1979

ЛЕНИНГРАДСКИЙ ОРДЕНА КРАСНОГО ЗНА-МЕНИ МЕХАНИЧЕСКИЙ ИНСТИТУТ

МУЗЫЧЕНКО ОЛЕГ НИКОЛАЕВИЧ, ЛУКОЯНОВ ВИТАЛИЙ ПАВЛОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: becom, кодес, обнаружения, ошибокв, параллельном, постоянным, разрядном

Опубликовано: 15.05.1981

Код ссылки

<a href="https://patents.su/7-830390-ustrojjstvo-dlya-obnaruzheniya-oshibokv-parallelnom-razryadnom-kodes-postoyannym-becom.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения ошибокв параллельном -разрядном кодес постоянным becom</a>

Предыдущий патент: Устройство для контроля времени выпол-нения программ

Следующий патент: Устройство для функционально-парамет-рического контроля логическихэлементов

Случайный патент: Струйный преобразователь перемещения в код