Цифровой интегратор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 661572

Автор: Тарануха

Текст

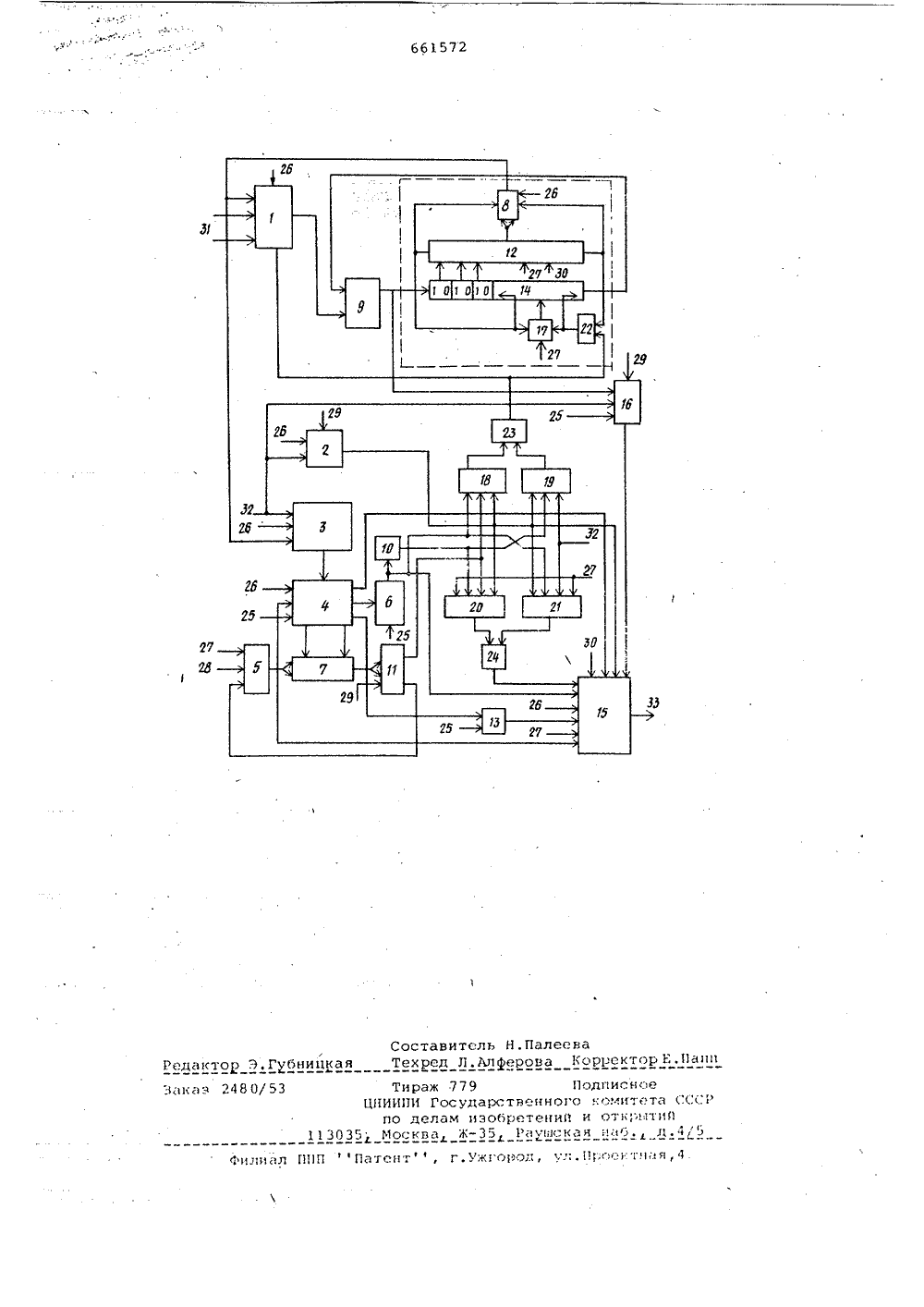

(р :;,оеарпц 66 ППУ ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(61) Дополнительное к авт. сеид-ву Союз Советских Социалистических Республик(22) Заявлено 0 Ц 27 5 (21) 2195245/18-24 с присоединением заявки Йо Государственный комитет СС,СР по делам изобретений н открытийДата опубликования описания 05.05.79(72) Автор изобретения В.М.Тарануха Таганрогский радиотехнический институт им.В.Д.Калмыкова(54 ) ЦИФРОВОЙ ИНТЕГРАТОР Изобретение относится к облаСтивычислительной техники, а именно.к циФровым интегрирующим машинами может быть использовано в однородных вычислительных средах,Известно устройство,. состоящееиэ сумматоров, умножителя, комму"татора, блока синхронизации, блокапреобразования приращений, блокастирания йачального импульса 1) .К недостаткам этого цифровогоинтегратора следует отнести то; чтов процессе программирования приходится производить масштабирование пеРеменных.Наиболее близким к данному изобретению является цифровой интегратор, содержащий сумматор приращений,сумматор подынтегральной Функции ирегистр сдвига 21.Недостатком известного устройстваявляется необходимос ть предварйтельного масштабирования переменных, чтоувеличивает время решения задачи.Цель настоящего изобретения,- повышение быстродействия,Поставленная цель достигается тем,что в устройство введены, блок суммирования порядков, блок вычитания йоряд- ЗОков,первый и второй счетчики,триг-гер, первый и второй дешифраторы,квантователь, первый и второй блокформирования тактовых импульсов, преобразователь чисел в дополнительныйкод, элементы И, ИЛИ, НЕ, И-НЕ,причем выход сумматора. приращенийсоединен с первым. входом сумматораподынтегральной функции, выход которого соединен со входом старшего разряда регистра сдвига и с первым входом преобразователя чисел в дополнительный код, выходы первых трех старших разрядов,регистра сдвига подключенны соответственно к первым тремвходам первого,дешифратора, выходмладшего разряда.регис.тра сдвига соединен со вторым входом сумматора подынтегральной функции, пер-.вый выход первого дешифратора соединен с первым входом первого счетчика,с первым входом первого элемента.И й со вторым входом регистра сдвига, второй выход - со вторым входомпервого счетчика и с первым входомйервого элементаИЛИ, третий выходс третьим и четвертым входами первого счетчика, выход которого соединен с первым входом сумматора приращений и с первым входом блока суммирования порядков, выход первогоэлемента ИЛИ соединен с третьимвходом регистра сдвига и со вторымвходом первого элемента И, выход которого подключен к четвертому входурегистра сдвига, выход блока суммирования порядков соединен с первымвходом блока вычитания порядков, первый и второй выходы которого подключены соответственно к первому и второму входам второго счетчика, третий выход блока вычитания порядковсоединен с первым входом второго дешифратора, выход которого соединенс первым входом квантователя, четвертый выход блока вычитания порядков соединен с первым входом перво-.го блока формирования тактовых им- (5пульсов, выход которого соединен совходом элемента НЕ, с первыми входами второго и третьего элементов И исо вторым входом квантователя, выходэлемента НЕ соединен с первыми входами четвертого и пятого элемента И,выход второго блока формированиятактовых импульсов соединен с третьими четвертым входами второго счетчика,выход которого соединен с первым ивторым входами триггера, первый выход триггера соединен со вторыми входами второго и пятого элементов И,второй выход триггера соединен с перВым входом второго блока формирования тактовых импульсов, пятый выход 30блокавычитания порядков соединенс третьим входом квантователя, первый выход которого соединен со вто-рзм входом блока Вычитания порядков,выход элемента И-НЕ соединен с третьими входами второго и пятого элементов И, со вторыми входами третьего и четвертого элементов И и счетвертым входом квантователя, пятый вход которого соединен с выходом преобразователя чисел в дополнительный код, выходы второго ичетвертого элементов И соединенысоответственно с первым и вторымВходами В торо го элемента ИЛИ Вы 45ход которого соединен со вторымвходом сумматора приращений и совторым входом первого элемента ИЛИ,Выходы третьего и пятого элементовИ соединены соответственно с первьми Вторым входами третьего элементаИЛИ;ВВйод которого"подклЮчен кшестому входу квантователя, Й входовсумматора приращений, второй входблока суммирования порядкон, первый вход элемента И-НЕ и второй 55вход преобразователя чисел в дополнительный код являются информационными входами устройства, второййцход квантователя является информационным выходом устройства, третий вход сумматора приращений, третий и четвертый входы преобразовате ля чисел в дополнительный код; второй и третий входы элемента И-НЕ, ", третьи входы третьего и четвертого элементов И, четвертые входы третьего и пятого элементов И, седьмой,восьмой и девятый входы квантонателя, третий вход триггера, второйнход первого, второй и третийнходы нторого блоков выделениятактовых импульсов, третий вход блокасуммирования порядков, третий и чет-вертый входы блока нычитания порядковявляются управляющими входами устройства.На чертеже приведена блок-схемацифрового интегратора, Цифровой интегратор содержит сумматор 1 приращений, элемент И-НЕ 2, блок 3 сУммирования порядков, блок 4 вычитанияпорядков, блоки 5, 6 выделения тактовых импульсов, счетчики 7, 8, сумматор 9 подынтегральной функции, эле ,мент НЕ 10, триггер 11, дешифраторы12, 13 регистр 14 сдвига, квантователь 15, преобразователь 16 чисел вдополнительный код, элементы И 17,18, 19, 20, 21, элементы ИЛИ 22, 23,24, управляющие входы 35, 26, 27, 28,29, 30, информационные входы 31, 32,информационный выход 33 устройства,Устройство работает следующимобразом.На управляющий вход 26 сумматора1, на входы элемента И-НЕ 2, блоков3, 4, квантователя 15, счетчика 8поступает из устройства управлениясигнал выделения кода приращения.На информационные входы 31 поступаюткоды приращений с выходов цифровыхинтеграторов, на вход 32 поступаеткод приращений переменной интегрирования. При этом начинается подготовительный этап операции интегриро"вания. Счетчик 8 и квантонатель 15переходят из режима хранения в режим выдачи порядков, В сумматоре1 вычитается разность порядковм -н(ПМк(-) "Пацци )а н блоках 3 и4 вычйсляется сумма порядковн -нцк) Пикк и разность порядн н , +-мМк) хк ( ) "ПО 1 )соответственно,Зк -1) ОрядОК ПОдЫНтЕГраЛЬнной Функции в к-том интеграторе на (1-1)-ишаге интегрирования. П" - порядок подынтегральной функции на ( -м шаге интегрирования.П" , - порядок подынтеграль кк(н)ной функции на (+1)-мшаге интегрирования.П це, - порядок ос татка приращения к-го интеграторана( -м шаге.В элементе 2 анализируются единичные и нулевые разряды порядка приращения П;, ) до знакового разряда.10 5 20 28 ЗО 45 55 При наличии в порядке единиц и нулей элементом 2 вырабатывается сигнал разрешения, который поступает на входы элементов И 18, 19, 20, 21 и квантователя 15 и длится до окончания интегрирования, а при наличии только единиц вырабатывается сигнал запрета. По знаковому разряду входного прирашения из устройства управления подается сигнал выделения знакового разряда приращения на вход 25 блока б, дешифратора 13, блока 4, преобразователя 16. По этому сигналу перезаписывается из блока 4 в счетчик 7 вычисленная разностьпорядков. В блоке б анализируетсязнак разности порядков и в зависимости от него вырабатываются сигналы для управления элементами И 18,19, 20, 21.Дешифратором 13 вырабатываетсясигнал для управления квантователем15, если модуль разности порядковнн(П ук -1) -Пчх к (ф 1) П ов к( ) Равен нулю,Кроме того, если знаковый разрядвходного прирашения переменной интегрирования отрицательный, вкл(очаЕтся преобразователь 16, если положительный, преобразователь кода неиспользуется. Одновременно по знаковому разряду входного прирашения снимается сигнал на выделение кода приращения и из устройства подается потенциал работы по входу 28 на блок 5, при этом начинается операция интегрирования, и когда знак разностин-нпорядков (П ук ( (-1) +Пчк к(1+1) Поэк( положительный, блоком б выдается сигнал, который подготавливает элемент И 18 и открывает элемент 21, ранее подготовленный потенциалом выделения остатка по входу 32 (потенциалвыделения остатка поступает из устройства управления в началеоперацииинтегрирования и длится до выделениязнакового разряда выходного приращения). Через элемент И 21 тактовыеимпульсы поступают на вход квантователя 15, в котором осушествляетсяпродвижение младшими разрядами вперед мантиссы остатка и суммированиеее с нулевыми разрядами до поступления мантиссы приращения. Одновременно по потенциалу работы открывается блок 5, подготовленный сигнал с нулевого выхода триггера 11 поступает на блок 5.Через открытый блок 5 так товые импульсы пос тупают со . входа 27 на счетный вход счетчика 7. В счетчике вычитаются тактовые импульсы до записи в нем ну"левого кода. В момент записи в счетчике 7 нулевого кода с выхода последнего выдается сигнал, по которомупереключается триггер 11 в единичное состояние. Потенциал с единичного выхода триггера 11 подается наэлементы И 18, 19, т,к. элемент 19 закрыт, а элемент 18 открыт сигналом поступаюшим с выхода блока б, то по потенциалу, поступающему с единично-, го выхода триггера 1, элементом И 18, выдается сигнал, обеспечивающий сдвиг вправо кода мантиссы подынтегральной Функции в регистре 14 и одновременно разрешаюший суммирование входных приращений в сумматоре 1. Сдвиг мантиссы подынтегральной функции в регистре 14 осуществляется следукщим образом, По сигналу, поступающему из выхода элемента И 18 настраивается регистр 14 на сдвиг информации вправо иодновременно открывается элемент И 17, через который тактовые импульсы поступают на синхронизируяций вход регистра 14, который переходит из режима хранения в режим выдачи мантиссы подынтегральной функции. Мантисса с выхода регистра 14 и суммарный поток приращений, приведенный к младшему разряду подынтегральной функции из выхода сумматора 1 поступает на входы сумматора 9, в котором вычисляется новое значение мантиссын подынтегральной Функции М у к (=Мук-+ +2 "Е к, . Вычисленная мантисса перезаписывается в регистре 14 и одно- в реме н но пос тупает через преоб разо- ватель 16 на информационный вход квантователя 15 с задержкой наПн +Пнк) чхк (+1) оэк тактов относительно мантиссы остатка М В преобразователе 16 произведенйю присваивается знак приращения переменной интегрирования.В квантователе 15 мантисса прирацения суммируется с мантиссой остатка.В случае, когда знак разности порядков отрицательный, блок б совместно с элементом НЕ 10 вырабатывает сигнал, по которому подготавливается элемент И 19 и открывается элемент И 20,подготовленный потенциалом выделения остатка по входу 27,Далее вычисления проводятся как и в случае положительного знака разности порядков до записи в счетчике 7 нулевого кода. В этот момент триггер 11 переключается в единичное состояние сигналом, поступающим с выхода счетчика 7. Потенциал с единичного выхода этого триггера открывает элемент И 19, через него тактовые импульсы поступают на вход квантователя 15, который переходит из режима хранения в режим продвижения мантиссы остатка. Мантисса остатка при этом задерживается на) ук -1) ох к ф 1) - П оэк 1 такП +Птов относительно мантиссы подынтегральной функции.В квантователе 15 осуществляется суммирование мантисс остатка и вычисленного приращения, По окончанию процесса суммирования снимается потенциал выделения остатка (по661572 10 9которого соединен с первым входомквантователя, четвертый выход блока вычитания порядков соединен с первым входом первого блока формирования тактовых импульсов, выход которого соединен со входом элемента НЕ, с первыми входами второго и третьего элементов И и со вторым входом квантователя, выход элемента НЕ соединен с первыми входами четвертого и пятого элемента И, выход второго блока формирования тактовых импульсов соединен с третьим и четвертым , входами второго счетчика, выход которого соединен с первым и вторым входами триггера, первый выход триггера соединен со вторыми входами второго и пятого элементов И, второй выход триггера соединен с первым входом второго блока формирования тактовых импульсов, пятый выход блока вычитания порядков соединен с третьим входом квантователя, первый выход которого соединен со вторым входом блока вычитания порядков, выход элемента И-НЕ соединен с третьими входами второго и пятого элементов И, со вторыми входами третьего и четвертого элементов И и с четвертым входом квантователя, пятый вход которого соединен с выходом преобразователя чисел в дополнительный код, выходы второго и четвертого элемеи" тов Исоединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен совторым входом сумматора приращенийи со вторым входом первого элемента ИЛИ, выходы третьего и пятого элементов И соединены соответственно спервым и вторым входами третьегоэлемента ИЛИ, выход которого подклю 5 чен к шестому входу квантователя,Я входов сумматора приращений, второй вход блока суммирования порядков,первый вход элемента И-НЕ и второйвход преобразователя чисел в допол 10 нительный код являются информационными входами устройства, второй выход квантователя является информационным выходом устройства, третий входсумматора приращения, третий и четвертый входы преобразователя чиселв дополнительный код, второй и третий входы элемента И-НЕ, третьи вхо"ды третьего и четвертого элементовИ, четвертые входы третьего и пятого элементов И, седьмой, восьмойи девятый входы квантователя, третий вход триггера, второй вход первого,второй и третий входы второгоблоков выделения тактовых импульсов,третий вход блока суммирования порядков, третий и четвертый входыблока вычитания порядков являются,управляющими входами устройства.Источники информации, принятыево внимание при экспертизе30 1. Авторское свидетельство СССРР 355631, кл. С 06 7 1/02, 1969.2. Патент США М 3249743,кл. 235-150, 1962.,П1. ч 5 цлиал ццц цатен фф, у .ужгород, ул,цроектпав Тираж ЦНИИЦИ Г по дел 113035 Москватель Н Л. псе ударств иэобре ж

СмотретьЗаявка

2195245, 02.12.1975

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ТАРАНУХА ВИТАЛИЙ МОДЕСТОВИЧ

МПК / Метки

МПК: G06J 1/02

Метки: интегратор, цифровой

Опубликовано: 05.05.1979

Код ссылки

<a href="https://patents.su/6-661572-cifrovojj-integrator.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой интегратор</a>

Предыдущий патент: Фотоэлектрическое устройство для умножения электрических сигналов на гармонические функции

Следующий патент: Устройство для считывания информации с подвижных объектов

Случайный патент: Способ измерения скорости распространения акустических колебаний и устройство для его осуществления