Система для обработки данныхпараметров сканируемых изображений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 805329

Автор: Митрофанов

Текст

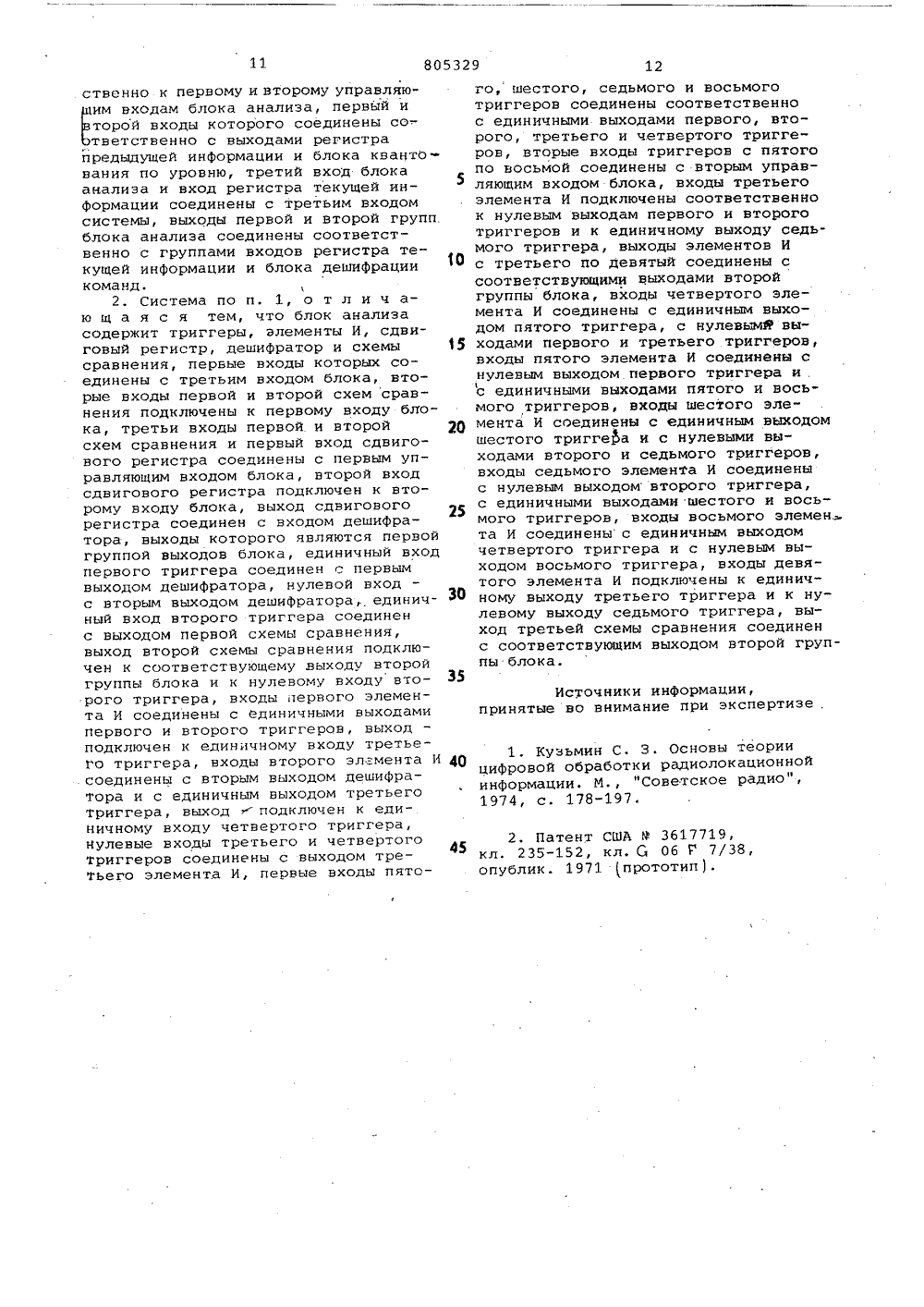

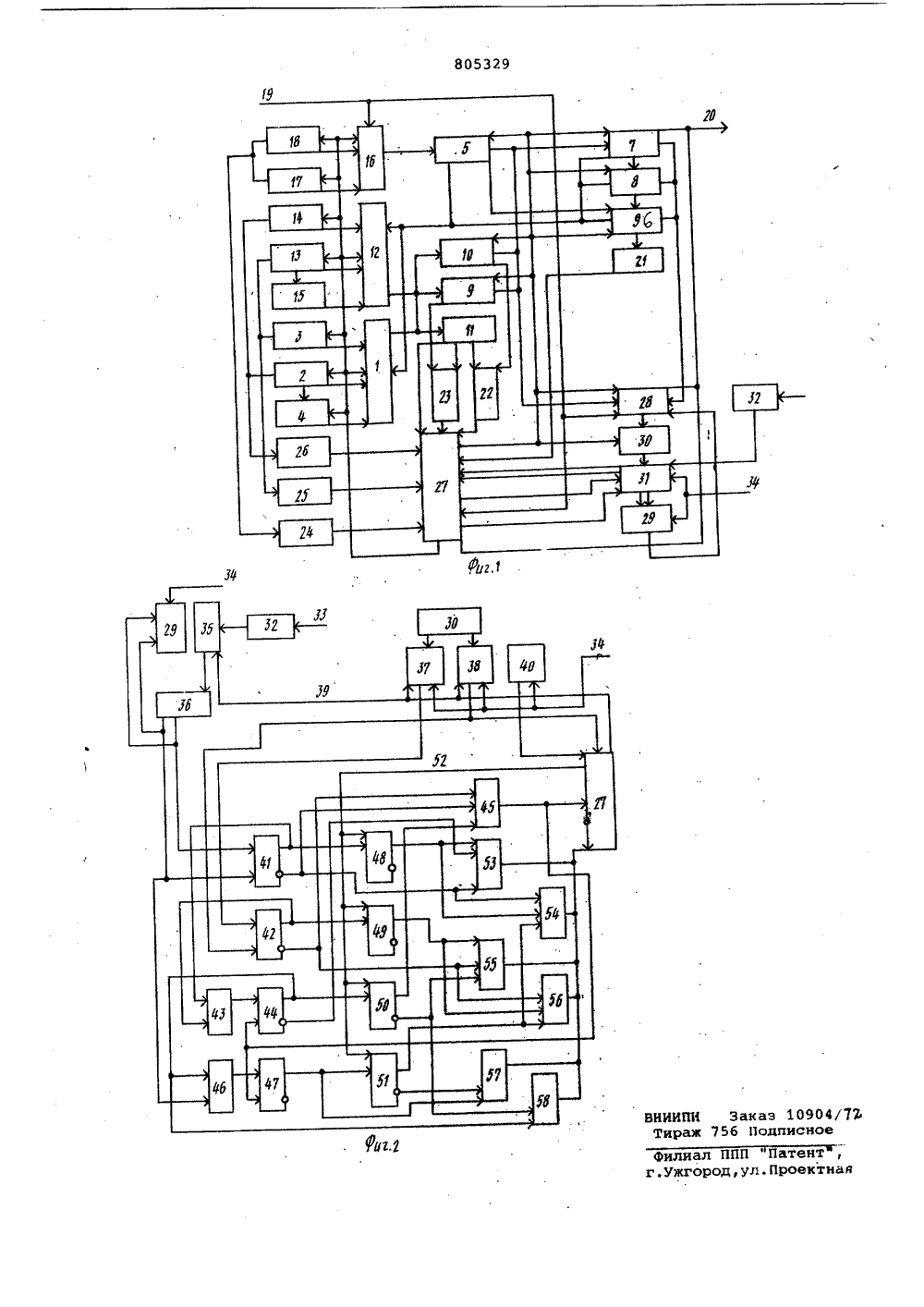

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ВОЛЬСКУ Союз СоаетсиикСоциалистическихРеспублик(22) Заявлено 27.1278 (21) 27045 бО/18-24 с лрисоедииением заявки И 9 С) Об Г 15/20 Государственник комятет СССР оо делам язобретеяий я открытая(23) При орите Опубликоеаио 1502,81, Бюллетень Йо б Дата опубликоаайия описания 170281(71) заявитель 54 СИСТЕМА ДЛЯ ОБРАБОТКИ ДАННЫХ ПАРАМЕТРОВ СКАНИРУЕМЫХ ИЗОБРАЖЕНИЙ Изобретение относится к вычислительной технике и может быть использована для первичной обработки радиолокационной и другой развертываемой во времени информации.Известно устройство первичной обработки радиолокационной информации, которое содержит блок квантования сигналов по уровню, блок кодирования 1 О временных задержек и цифровую вычислительную машину, содержащую буферное запоминающее устройство, оперативное запоминающее устройство, арифметическое устройство и устройство управления 11.Однако значимую часть информации хранит только один цикл, группирование информации в пачки при слиянии целей (изображений) и при наличии помехи может содержать ошибку, быстро О действие устройства ограничено .быстродействием арифметического устройства.Наиболее близкой по технической сущности к изобретению является система, которая содержит ЭВМ, буферное запоминающее устройство, связанное с основным запоминающим устройством, в которое записываются как входные данные, так и результаты предваритель о ных вычислений в схеме для перемножения векторов. Входные аналоговые сигналы преобразуются в цифровой код с помощью аналого-цифрового преобразователя. Система предназначена для обработки сигналов, образованных при радиолокационных измерениях 2.Недостатки системы состоят в,том, что значимую информацию она хранит только один цикл. Подборка информации в пачки при слиянии целей (изображений) и нри наличии помехи может содержать ошибку. Общее быстродействие ограничивается быстродействием узлов арифметической обработки.Йель изобретения - повышение быстродействия и достоверности работы.Поставленная цель достигается тем, что в,систему, содержащую регистры текущей информации и предыдущей информации, блок квантования по уровню, вход которого является первым входом системы, оперативное запоминающее устройство и блок дешифрации команд, введены запоминающие устройства, счетчики адреса записи, счетчики адреса считывания, буферные регистры, счетчики корректировки, регистр признака наложения, схемы сравнения, регистры адреса и блок анализа, при45 чем адресные входы каждого запоминающего .устройства соединены с первымивыходами соответствующих счетчика адреса записи и счетчика адреса считывания, второй выход каждого счетчика,адреса записи, кроме первого, черезбуферный регистр соединен с адреснымвходом запоминающего устройства,вход первого запоминающего устройства, первые входы оперативного запоминающего устройства и блока дешифрации команд подключены к второму входу системы, управляющие входы счетчиков адреса записи, адреса считывания,буферных регистров и запоминающихустройств соединены.с первым выходомблока дешифрации команд, выходы запоминающих устройств, кроме первого,подключены к входам первого и второго счетчиков корректировки и к входу.регистра признака наложения, выходпервого запоминающего устройства со Оединен с входом третьего счетчика корректировки, входы запоминающих устройств, кроме первого, соединены спервыми выходами третьего и четвертого счетчиков корректировки, первого и второго регистров адреса, входыпервого регистра адреса соединены соответственно с первыми выходами первого и второго счетчиков корректировки, с вторым выходом третьего счетчика корректировки и с вторым входомоперативного запоминающего устройства, второй выход первого регистра адреса, первый выход оперативного запоминающего устройства и второй выходблока дешифрации команд соединены свыходом системы, вход второго регистра адреса соединен с третьим выходомпервого регистра адреса, четвертыйвыход которого и вторые выходы второго регистра адреса и четвертого счет Очика корректировки подключены к третьему входу оперативного запоминающего устройства, четвертый вход которого соединен с выходом регистратекущей информации, второй выходподключен к входу регистра предыдущей информации, третий выход третьегосчетчика корректировки подключен кпервому входу четвертого счетчика корректировки, второй вход которогоподключен к третьему выходу второгорегистра адреса, первые входы первой,второй и третьей схем сравнения подключены соответственно к первому ивторому выходам регистра признака наложения и к третьему выходу четвертого счетчика корректировки, вторые,входы первой и второй схем сравненияподключены соответственно к вторымвыходам второго и первого счетчиковкорректировки, третий выход регистрапризнака наложения соединен с вторымвходом блока дешифрации команд, входы которого, начиная с третьего, подключены соответственно к выходам схемсравнения с первой по шестую, входы. четвертой схемы сравнения соединены с вторыми выходами первых счетчиков адреса записи и адреса считывания, входы пятой схемы сравнения соединены с третьим выходом второго счетчика адреса записи и с вторым выходом тре-. тьего счетчика адреса считывания, входы шестой схемы сравнения соединены с вторым выходом второго счетчика адреса считывания и с третьим выходом третьего счетчика адреса записи, управляющие входы счетчиков корректировки, регистров адреса, оперативного запоминающего устройства и регистра предыдущей информации соединены с третьим выходом блока дешифраций команд, четвертый и пятый выходы которого подключены соответственно к первому и второму управляющим входам блока анализа, первый и второй входы которого соединены соответственно с выходами регистра предыдущей информации и блока квантования по уровню, третий вход блока анализа и вход регистра текущей информации соединены с третьим входом системы, выходы первой и второй групп блока анализа соединены соответственно с группами входом регистра текущей информации и блока дешифрации команд.Кроме того, в системе блок анализа содержит триггеры, элементы И, сдвиговый регистр, дешифратор и схемы сравнения, первые входы которых соединены с третьим входом блока, вторые входы первой и второй схем сравнения подключены к первому входу блока, третьи входы первой и второй схем сравнения и первый вход сдвигового регистра соединены с первым управляющим входом блока, второй вход сдвигового регистра подключен к второму входу блока, выход сдвигового регистра соединен с входом дешифратора, выходы которого являются первой группой выходов блока, единичный вход первого триггера соединен с первым выходом дешифратора, нулевой вход - с вторым выходом дешифратора, единичный вход второго триггера соединен с выходом первой схемы сравнения, выход второй схемы сравнения подключен к соответствующемувыходу второй группы блока и к нулевому входу второго триггера, входы первого элемента И соединены с единичными выходами первого и второго триггеров, выход подключен к единичному входу третьего триггера, входы второго элемента И соединены с вторым выходом дешифратора и с единичным выходом третьего триггера, выход - подключен к единичному входу .четвертого триггера, нулевые входы третьего и чет-. вертого триггеров соединены с выходом третьего элемента И, первые входы пятого, шестого, седьмого и восьмого триггеров соединены соответственно с единичными выходами первого,второго, третьего и четвертого триг-. ных цепей связи с ЭВМ, входных цепейгеров, вторые входы триггеров с пя- параметров сканирования входных цетого по восьмой ссединЕны с вторым пей воспринятого сигнала одного запоуправляющим входом блока,входы тре- минающего устройства.тьего элемента И подключены соответ- Система работает следующим образом.ствеино к нулевым выходам первого . В начальный момент все счетчики наи второго триггеров и к единичному вы- .ходятся в нулевом состоянии. По вход,фходу седьмого триггера, выходы эле-ным цепям связи с ЭВМ на вход 19 поментов И а третьего по девятый ао- ступает адрес. начала записи информацииедииены с соответствующими выходами и запрос иа его запись. По этому завторой группы блока, входы четверто- просу блок 27 записывает адрес началаго элеМеита К соединены О единичнымзаписи информации в устройство 16.выходом пятого триггера, с нулевыми После этого блок 27 подает на входвыходами первого и третьего тригге- счетчика 17 адреса записи сигнал счеров, входы пятого элемента. В аоеди- та, таким образом записывает в ЭУ 116нены с нулевым выходом первого триг" все адреса начала записи информации,гера и с единичныжи выходами пятого 15 далее поступает сигнал начала раи восьмого триггеров, вааы шестого боты, по которому блок 27 считываетэлемента И соединены с едииичйым из ЭУ 16 по адресу в счетчике 18 ввыходом шестого триггера и с нулевыми счетчик 5 корректировки адрес началавыходами второго и седьмого тригге- записи информации. далее поступаетров, входы седьмого элемента И соеди- Що сигнал на вход счетчика 18.невы с нулевым выходом второго триг- Воспринятый сигнал поступает нагера, с единичными выходами шестоговход 33 и с него на вход блокаи восьмого триггеров, входы восьмогоквантования по уровню, Далее квантоэлемента И соединены с единичным вы ванный сигнал поступает на вход сдвиходом четвертого тРиггеРа и с нуле гового регистра 35, Сдвиг информациивым выходом восьмого триггера, входы производится по сигналу, поступающедевятого элемента И подключены к еди- му на вход сдвигового регистра 35ничному выходу третьего триггера ипо связи 39 из блока 27. При нахождек нУлевомУ выходу седьмого тРИггеРа,. нии в двух старших разрядах сдвигововыход третьей схемы сРавнения соеди- ЗО го регистра комбинации 01, что соотнен с соответствующим выходом второй ветствует переднему Фронту кван"огруппы блока.ванного сигнала дешифратор 36 выраНа фиг. 1 представлена блок-схема батывает сигнал на первом выходе; при0 еши ато 36нахожденин комбинации 10 дешифраторсистемы; на фиг. 2 - схема лона анавырабатывает сигнал на своем второмапоминающее уст- выходе, что соответствует заднемуСистема содержит запоминающее устф онту квантованного сигнала. По сигналам дешифратора Зб принимаются энаписи, счетчик 3 адреса считывания,т 4 счетчики 5 и б чения параметров сканирования с входа 34 в регистр 29. Схема 37 сравнекорректировки, регистры 7 и 8 адректировкиния вырабатывает сигнал при раса .счетчики 9 и 10 корректировки,венстве значения дальности переднегорегистр 11 признака наложения, запоминаю ее ст ойство 12, счетчик 13 Фронта сигнала в Регистре 30 предыдущей информации, схема 38 сравненияадреса записи, счетчик 14 адреса счи- , душе ин Ртывания, регистр адреса, з45 ве значения дальности заднего фронтанающее устройство 16, счетчик 17 адреса записи, счетчик 18 адреса считы- сигнала в регистре 30 значению текувания, вход 19 и д 20и выход 20 системы для щего сканирования, которое поступаетподключения ЭВИ, схемы - р21-26 с анне- по входу . хемставляет сигнал "1" по приходу максиния блок 27 дешифрации команд, опе) мально принятого значения сканироваративное запоминающее устройство ОЭУ)5 О р"1"28, регистр 29 текущей информации, ния. Триггер 41 установится во эа 36 в "0-егист 30 предыдущей информации, первым выходом дешифратора , вблок 31 анализа, блок 32 квантования42 "1" сигналом схе"вхо ы 33 и 34 системы, гер 42 установится впо уровню, входы и и37 с а ения в "0" - сигналомемы 38 с авнения Т игге 44 установится в "1" сигналом элемента И 43п авления, схему 40 сравнения,. тригуправления, с е44 т.е. при наличии наложения сигналовге ы 41 и 42, элемент И 43, триггер 4текущего и предыдущего циклов поэлементы И 45 и 46, триггерыи установится в "0" посвязь 52 управления, элемент Иы 53-58. дальности, и уст н всигналу элемента И . РиггерПри съеме информации в нескольких установится в "1" сигналом с выходауровнях пропорционально возрастает элемента И 46, т.е. при первой выдасостав оборудования, за исключением че при наличии наложения, и устанавоперативного запоминающего устройст- ливается в "0" сигналом элемента,ва, блока управления входных и выход И 45. Состояния триггеров 41, 42,44 и 47 переписываются соответственно в триггеры 48-51 по сигналу синхронизации, поступающему по связи 52 Элементы И 45, 53-58 вырабатывают сигналы наложения. По сигналу элеента И 53 блок 27 по адресу в счетике 5 корректировки записывает в ОЗУ 28 содержимое регистра 29.Далее по адресу в счетчике 2 адреса записи записывает в ЗУ 1 содержимое счетчика 5 корректировки, подает на вход счетчика 2 счетный сигнал, Далее по адресу в счетчике 18 считывает из ЗУ 16 адрес начала записи информации в счетчик 5 корректировки, подает на вход счетчика 18 счетный сигнал. По сигналу схемы сравнения 40 блок 27 меняет четность цикла. Устанавливается четный цикл, При этом установятся в "0" счетчик 3 и счетчик 13. По ад.ресу в счетчике 3 считывается из ЗУ 1 в счетчик 9 корректировки, счетчик 10 корректировки, регистр 11 признака наложения. Далее прибавляется единицы в счетчик 3, считывается из ОЗУ 28 по адресу в счетчике 9 информация в регистр 30. При равенстве нулю содержимого регистра 11 признака наложения прибавляется единица к содержимому счетчика 9 корректировки и выдается в регистр 7, Прн равенстве единице регистра 11 признака наложения прибавляется единица к содержимому счетчика 10 корректировки и выдается в регистр 7 адреса. Схема 23 сравнения выставит сигнал единица, если содержимое младших, разрядов счетчика 9 корректировки равно максимуму за вычетом единицы и содержимое регистра 11 признака наложения равно "0". Схема 22 сравнения выставит сигнал единица, если содержимое младших разрядов счетчика 10 корректировки равно максимуму за вычетом единицы, а содержимое регистра 11 признака наложения равно единице. Далее по сигналу единица схемы 23 сравнения блок 27 прибавит единицу к содержимому счетчика 9 корректирОвки. По полученному адресу в ОЗУ 28 записывается содержимое счетчика 5 корректировки и признак зависимости из блока 27. Далее записывается по адресу в счетчике 5 корректировки содержимое счетчика 9 корректировки и признака зависимости из блока 27. Затем прибавляется единица к содержимому счетчика 5 корректировки и передается его содержимое в регистр 7 адреса. Аналогично обрабатывается единичный сигнал схемы 22 сравнения. По сигналу элемента И 58 блок .27 передает содержимое регистра 7 адреса в регистр 8 адреса. По сигналу элемента И 57 блок 27 по адресу в регистре 8 записывает в ОЗУ 28 содержимое регистра 29 текущей информации передает содержимое регистра 8 адреса э счетчик б корректировки, записывает в ЗУ 12 по адресу в счетчике 13 содержимое регистра 8 адреса, передаетсодержимое счетчика 13 в буферныйрегистр 15; прибавляет единицу к содержимому счетчика 13," выдает следующую информацию за предыдущий цикл врегистр 7 адреса и регистр 30 предыдущей информации, По сигналу элементаИ 56 в присутствии сигнала схемы 38сравнения блок 27 прибавляет единицук содержимому счетчика б корректиров ки, по полученному адресу записывает содержимое регистра 7 адреса ипризнака зависимости из блока 27 вОЗУ 28, далее записывает по адресу врегистре 7 адреса содержимое сЖтчи ка 6 корректировки и признак зависимости из блока 27 в ОЗУ 28. Схема 21сравнения выставит сигнал единица,если обнаружит в младших разрядахномер, равный максимуму. минус едини ца. По этому сигналу блок 27 прибавляет единицу в счетчик б корректировки, по полученному адресу записывает содержимое счетчика 5 корректировки в ОЗУ 28 и признак зависимостииз блока 27, далее по адресу в счетчике 5 корректировки записывает содержимое счетчика б корректировкии признак зависимости из блока 27 вОЗУ 28. Содержимое счетчика 5 корректировки затем пересылается в счет чик б корректировки,.считывается следующий адрес начала записи информации из ЗУ 16 в счетчик 5 корректировки. По сигналу элемента И 54 блок 27прибавляет единицу к содержимому счетЗ 5 чика б корректировки; производит запись взаимной зависимости содержимого счетчика б корректировки и счетчика 5 корректировки в ОЗУ 28, далееприбавляет единицу к содержимомусчетчика 5 корректировки, по полученному адресу записывает в ОЗУ 28содержимое регистра 29, записывает вЗУ 12 очередность поступления адресаиз счетчика 5 корректировки, Далееиз ЗУ 16 считывается следующий адресанализа в счетчик 5 корректировки.По сигналу элемента И 55 блок 27 выставляет запрос на обслуживание отЭВМ и выдает на выходные цепи связис ЭВМ содержимое регистра 7 адреса. ф Далее блок 27 засылает в регистр 7адреса и регистр 30 очередную информацию, По сигналу схемы 38 сравнениязасылается очередная информация врегистр 7 адреса и в регистр 30. По 55 сигналу элемента И 45 блок 27 записывает по адресу в буферном регистре 15 в ЗУ 12 содержимое регистра 8адреса, счетчика б корректировки ипризнак зависимости из блока 27. Приравенстве содержимого счетчика 3 исчетчика 13 схема 25 сравнения посылает сигнал в блок 27. Этим сигналамзапрещается дальнейшее считывание изЗУ 1 в четный цикл. При равенствесодержимого счетчика 2 содержимомсчетчика 14 схема 26 сравнения вы- ставляет сигнал в блок 27. Этим сигналом запрещается дальнейшее считывание из ЗУ 12 в нечетный цикл. При равенстве содержимого счетчика 17 со держимому счетчика 18 схема 24 сравнения выставляет сигнал, который служит информационным .сигналом переполнения ОЗУ 28, ЭВМ считывает информацию из ОЗУ 28 по цепям связи с ЭВМ выход 20) . Адрес информации в ОЭУ 28 и запрос на считывание в блок 27 поступает с ЭВМ по входу 19.В случае прихода нескольких сигна лов устанавливается приоритет на обработку.При съеме информации в нескольких 33 уровнях сигнал элемента И 58 П -го уровня обрабатывается аналогично сигналу элемента И 54.Применение изобретения для обработ ки сигналов радиолокационной инфор- ЗО мации позволяет увеличить скорость обработки сигналов, исключить потери информации при анализе наложения и в присутствии помехи, вести съем параметров местных предметов. Примене ние изобретения в качестве внешнего устройства ЭВМ позволяет производить непосредственный ввод информации с документов, что исключит операцию подготовки информации на машинных но- ЗО сителях и сократит машинное время ввода информации.Формула изобретения1. Система для обработки данных параметров сканируемых изображений, содержащая регистры текущей информации и предыдущей информации, блок Квантования по уровню, вход которого является первым входом системы, оперативное запоминающее устройство и блок дешифрации команд, о т л и ч, а ю щ а я с я тем, что, с целью повышения быстродействия и достоверности работы, в нее введены запоминающие устройства, счетчики адреса записи, счетчики адреса считывания, буферные фЯ регистры, счетчики корректировки, регистр признака наложения, схемы сравнения, регистры адреса и блок анализа, причем адресные входы каждого запоминающего устройства соеди- уф нены с первыми выходами соответствующих счетчика адреса записи и счетчика адреса считывания, второй выход каждого счетчика адреса записи, кроме, первогочерез буферный регистр соединен с адресным входом запоминающего устройства, вход первого запоминающего устройства, первые входы оперативного запоминающего устройства и блока дешифрации команд подключены к второму входу системы, управляющие бо входы счетчиков адреса записи, адреса считывания, буферных регистров и запоминающих устройств соединены спервым выходом блока дешифрации команд, выходы запоминающих устройств кроме первого, подключены к входампервого и второго счетчиков корректировки и к входу регистра признаканаложения, выход первого запоминающего устройства соединен с входомтретьего счетчика корректировки, входы запоминающих устройств кромепервого, соединены с первыми выходами третьего и четвертого счетчиков корректировки, первого и второго регистров адреса, входы первого регистра адреса соединены соответственно с первыми выходами первого и второго счетчиков корректировкис вторымвыходом третьего счетчика корректировки и с вторым входом оперативногозапоминающего устройства, второй выход первого регистра адреса, первыйвыход оперативного запоминающего устройства и второй выход блока дешифрации команд соединены с выходом системы, вход второго регистра адреса со-.единен с третьим выходом первого регистра адреса, четвертый выход которого и вторые выходы второго регистра адреса и четвертого счетчика корректировки подключены к третьему входу оперативного запоминающего устройства, четвертый вход которого соединен с выходом регистра текущей информации, второй выход - подключен к входу регистра предыдущей информации,третий выход третьего счетчика корректировки подключен к первому входучетвертого счетчика корректировки,второй вход которого подключен к третьему выходу второго регистра адреса,первые входы первой, второй и третьей схем сравнения подключены соответственно к первому и второму выходамрегистра признака наложения и к третьему выходу четвертого счетчика корректировки, вторые входы первой ивторой схем сравнения подключены соответственно к вторым выходам второго и первого счетчиков корректировки, третий выход регистра признаканаложения соединен с вторым входомблока дешифрации команд, входы котоого, начиная С третьего, подключены"оответственно к выходам схем сравнения с первой по шестую, входы четвертой схемы сравнения соединены свторыми выходами первых счетчиковадреса записи и адреса считывания,входы пятой схемы сравнения соединены с третьим выходом второго счетчикаадреса, записи и с вторым выходом третьего счетчика адреса считывания,входы шестой схемы сравнения соединены с вторым выходом второго счетчика адреса считывания и с третьимвыходом третьего счетчика адреса записи, управляющие входы счетчиковкорректировки, регистров адреса,оперативного запоминающего устройст-.ва и регистра предыдущей информации.соединены с третьим выходом блокадешифрации команд, четвертый и пятыйвыходы которого подключены соответственно к первому и второму управляюим входам блока анализа, первйй иторой входы которого соединены сответственно с выходами регистра предыдущей информации и блока квантования по уровню, третий вход блока анализа и вход регистра текущей информации соединены с третьим входом системы, выходы первой и второй групп блока анализа соединены соответственно с группами входов регистра текущей информации и блока дешифрации команд.2. Система по и, 1, о т л и ч аю щ а я с я тем, что блок анализа содержит триггеры, элементы И, сдвиговый регистр, дешифратор и схемы сравнения, первые входы которых соединены с третьим входом блока, вторые входы первой и второй схем сравнения подключены к первому входу блока, третьи входы первой.и второй схем сравнения и первый вход сдвигового регистра соединены с первым управляющим входом блока, второй вход сдвигового регистра подключен к второму входу блока, выход сдвигового регистра соединен с входом дешифратора, выходы которого являются первой группой выходов блока, единичный вход первого триггера соединен с первым выходом дешифратора, нулевой вход с вторым выходом дешифратора, единичный вход второго триггера соединен с выходом первой схемы сравнения, выход второй схемы сравнения подключен к соответствующему выходу второй группы блока и к нулевому входу второго триггера, входы первого элемента И соединены с единичными выходами первого и второго триггеров, выход подключен к единичному входу третьеГо триггера, входы второго эл=мента И соединены с вторым выходом дешифратора и с единичным выходом третьего триггера, выход подключен к единичному входу четвертого триггера, Нулевые входы третьего и четвертого триггеров соединены с выходом третьего элемента И, первые входы пятого, шестого, седьмого и восьмоготриггеров соединены соответственнос единичными выходами первого, второго, третьего и четвертого тригге"ров, вторые входы триггеров с пятогопо восьмой соединены с вторым управляющим входом блока, входы третьегоэлемента И подключены соответственнок нулевым выходам первого и второготриггеров и к единичному выходу седьмого триггера, выходы элементов И10 с третьего по девятый соединены ссоответствующими выходами второйгруппы блока, входы четвертого элемента И соединены с единичным выходом пятого триггера, с нулевьэ 4 й вы 15 ходами первого и третьего триггеров,входы пятого элемента И соединены снулевым выходом первого триггера ис единичными выходами пятого и восьмого триггеров, входы шестого эле 2 О мента И соединены с единичным выходомшестого триггера и с нулевыми выходами второго и седьмого триггеров,входы седьмого элемента И соединеныс нулевым выходом второго триггера,25мого триггеров, входы восьмого элемента И соединены с единичным выходомчетвертого триггера и с нулевым выходом восьмого триггера, входы девятого элемента И подключены к единичЗО ному выходу третьего триггера и к нулевому выходу седьмого триггера, выход третьей схемы сравнения соединенс соответствующим выходом второй группы блока,Источники информации,принятые во внимание при экспертизе1, Кузьмин С. 3. Основы теориицифровой обработки радиолокационнойинформации. М "Советское радио",1974, с. 178-197,2, Патент США М Зб 17719,кл, 235-152, кл. С 1 Об Р 7/38,опублик. 1971 прототип.

СмотретьЗаявка

2704560, 27.12.1978

МИТРОФАНОВ ВАЛЕРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06T 1/00

Метки: данныхпараметров, изображений, сканируемых

Опубликовано: 15.02.1981

Код ссылки

<a href="https://patents.su/7-805329-sistema-dlya-obrabotki-dannykhparametrov-skaniruemykh-izobrazhenijj.html" target="_blank" rel="follow" title="База патентов СССР">Система для обработки данныхпараметров сканируемых изображений</a>

Предыдущий патент: Устройство для статистическогомоделирования процессов эксплу-атации систем управления

Следующий патент: Устройство для моделирования вибра-ционных процессов

Случайный патент: Двухпозиционный распределитель