Устройство для деления п-разрядных десятичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

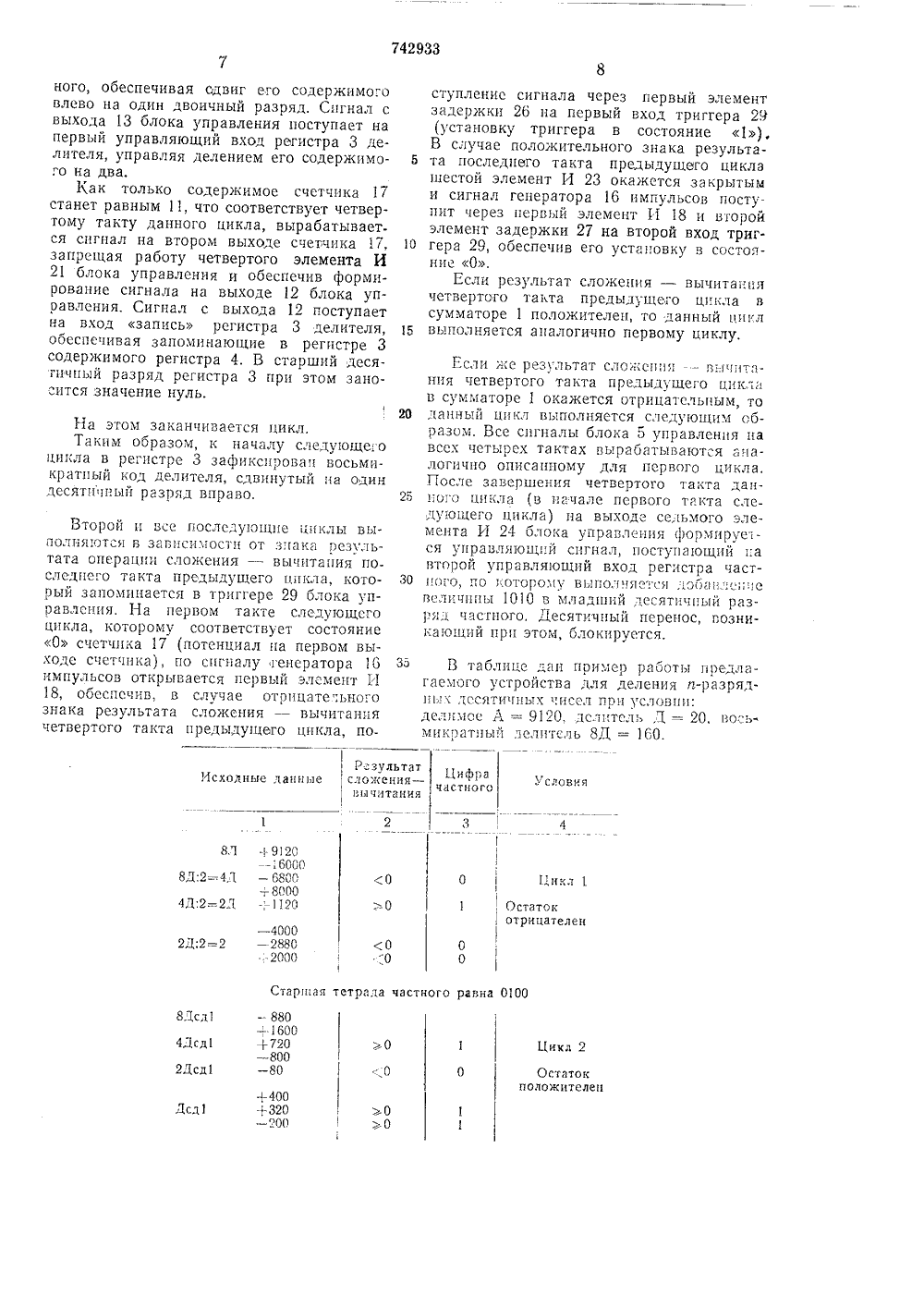

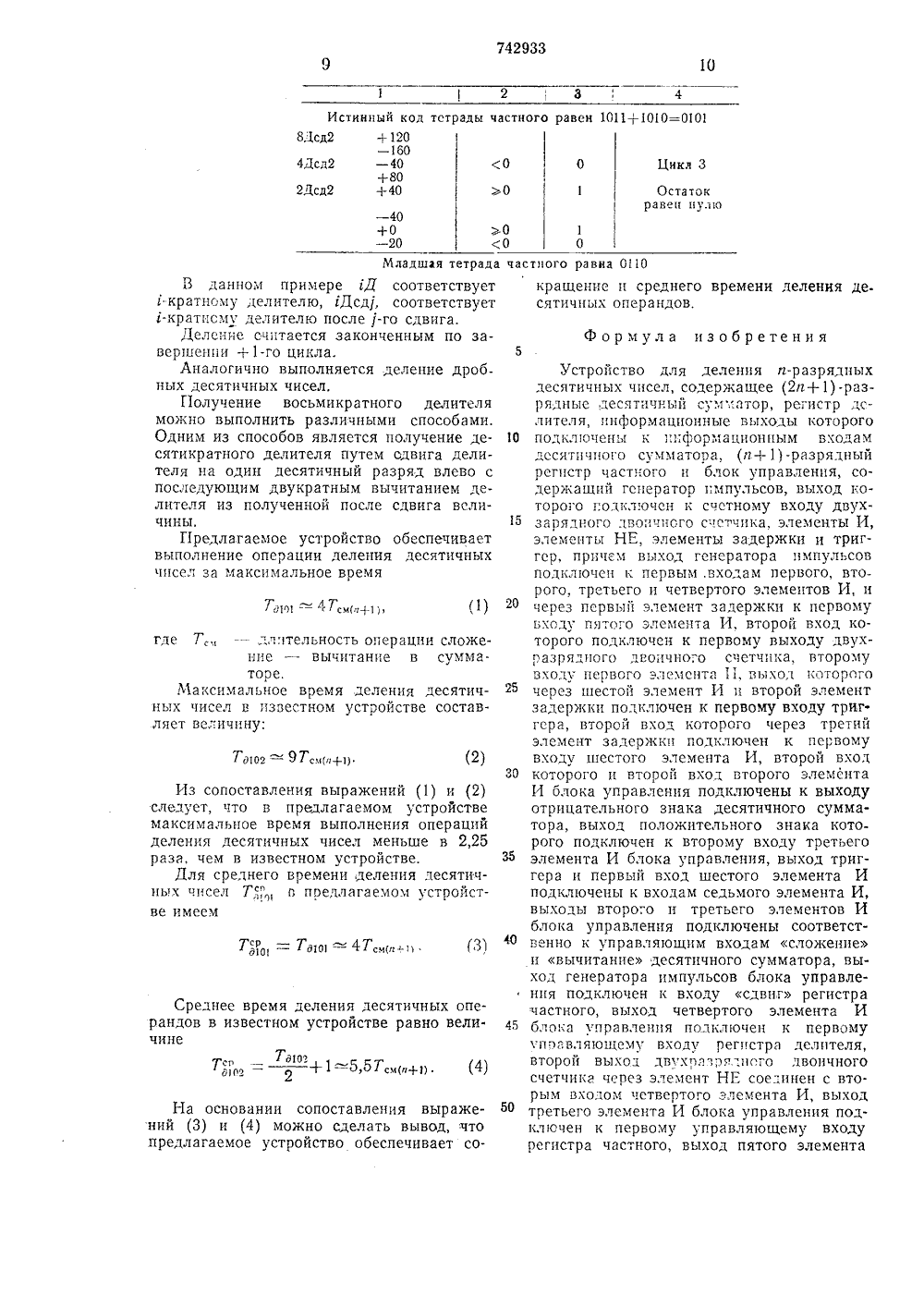

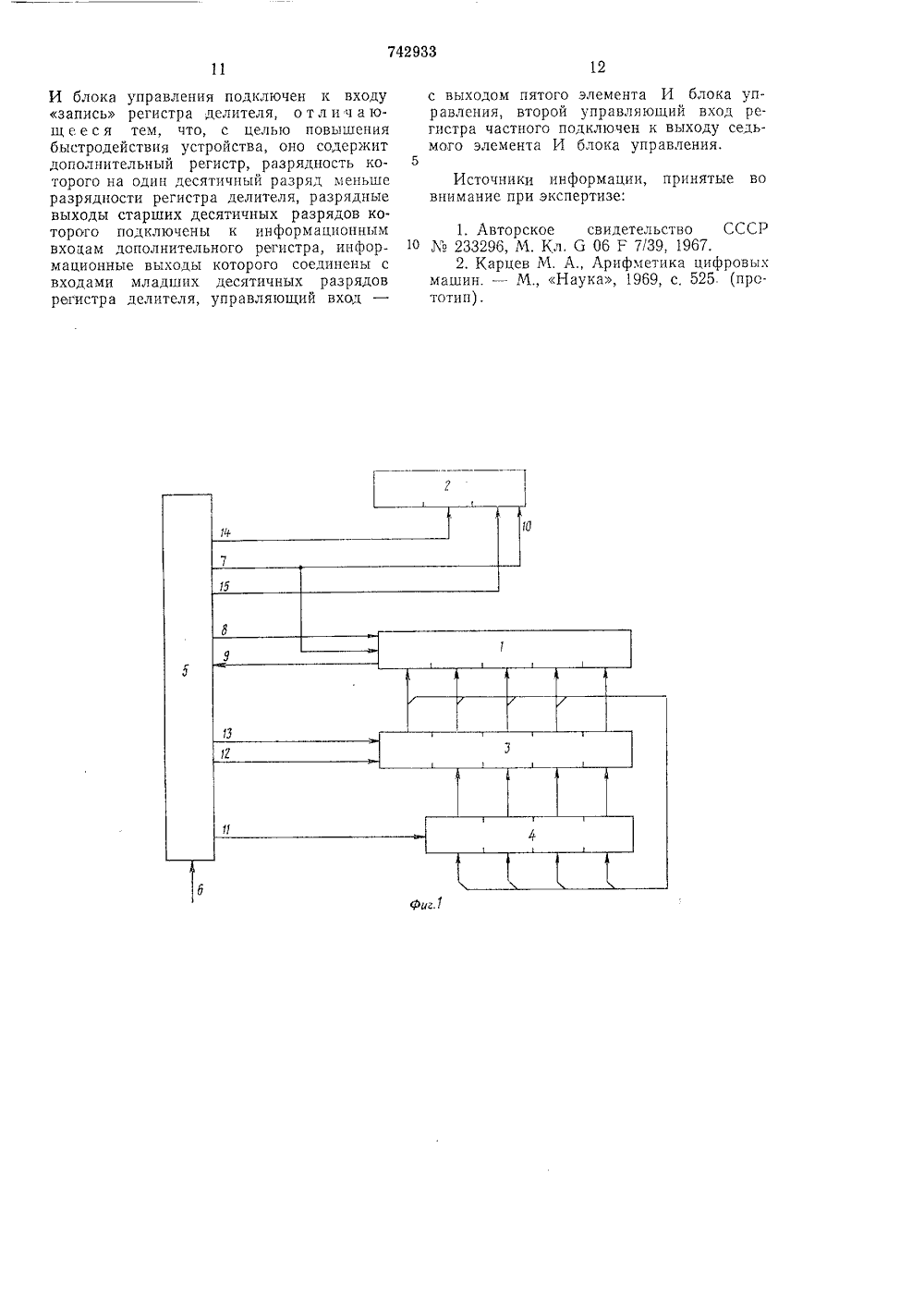

(22) 3 с присое инением заявки нныи иомитеСР(43) 0 бликовано 23.0 а опубликован по делам изобретени и открытий(45 я описания 07.12.81 2) Авторыизобретения А. Т. Пешков и Л хов 71) Заявитель 54) УСТРОЙСТВОДЛЯ ДЕЛЕНЗЯ и-РАЗРЯД ДЕСЯТИЧНЫХ ЧИСЕЛ Изобретение относится к области вычислительной техники и может применяться в арифметических устройствах, обрабатывающих как двоичную, так и десятичную информацию.Известно десятичное вычислительное устройство последовательного действия, состоящее из преобразователей фазоим пульсного представления чисел в пространственно-импульсное, преобразователей пространственно-импульсного представления чисел в фазоимпульсное представление чисел суммирующего и множительного блоков, логической схемы и блока микропрограммного управления, причем выходы входного преобразователя фазоимпульсного представления чисел в пространственно- импульсное подключены к входам преобразователей пространственно-импульсного представления чисел в фазоимпульсное представление чисел суммирующего и множительного блоков и через схемы И к входу декодирующей схемы блока микропрограммного управления 11.Недостатком такого устройства является то, что прп значительной сложности устройства оно выполняет лишь операции сложения и умножения десятичных чисел.Наиболее близким к предлагаемому по технической сущности является устройство для деления п-разрядных десятичных чисел, содержащее (2 п+1)-разрядные десятичный сумматор и регистр делителя, информационные выходы которого подключе ны к информационным входам сумматора,регистр частного и блок управления, содержащий генератор импульсов, выход которого подключен к счетному входу двух- разрядного двоичного счетчика, элементы И, элементы НЕ, элементы задержки и триггер, причем выход генератора импульсов подключен к первым входам первого, второго, третьего, четвертого и пятого элементов И, второй вход которого подключен к первому выходу двухразрядного двоичного счетчика, второму входу первого элемента И, выход которого через шестой элемент И и первый элемент задержки подключен к первому входу триггера, второй 20 вход которого через второй элемент задержки подключен к первому входу шестого элемента И, второй вход которого и второй вход второго элемента И блока управления подключены к выходу отрицатель ного знака десятичного сумматора, выходположительного знака которого подключен к второму входу третьего элемента И блока управления, выход триггера и первый вход шестого элемента И через третий элезо мент задержки подключены к входам седь 74293310 мого элемента И, выходы второго и третьего элементов И блока управления подключены соответственно к управляющимвходам сложение и вычитание десятичного сумматора, выход генератора импульсов блока управления подключен к входусдвиг регистра частного, выход четвертого элемента И блока управления подключен к первому управляющему входу регистра делителя, второй выход двухразрядного двоичного счетчика соединен с входом запись регистра делителя и черезэлемент НЕ с вторым входом четвертогоэлемента И, выход третьего элемента Иолока управления подключен к первомууправляющему входу регистра частного 12.Известное устройство выполняет операцию деления десятичных чисел за счет отработки отдельных десятичных разрядовчастного, причем при отработке каждогоразряда в младшую тетраду регистра частного добавляется столько единиц, сколькоможно выполнить сложений - вычитанийделителя от садержимаго сумматора безизменения его знака, и далее выполняетсясдвиг содержимого регистра частного и регистра делителя на четыре разряда.1-1 едостатком данного устройства является то, что в нем затрачивается большоевремя на выполнение операции делениядесятичных чисел.Целью изобретения является повышение быстродействия устройства,Это достигается тем, что в устройстводля деления п-разрядных десятичных чисел введен дополнительный регистр, разрядность которого на один десятичныйразряд меньше разрядности регистра делителя, разрядные выходы старших десятичных разрядов которого подключены кинформационным входам дополнительногорегистра, информационные выходы которого соединены с входами младших десятичных разрядов регистра делителя, управляющий вход - с выходом пятого элемента И блока управления, второй управляющий вход регистра частного подключен квыходу седьмого элемента И блока управления.На фиг. 1 приведена структурная схе.ма устройства для деления разрядных десятичных чисел; на фиг, 2 - схема блокауправления,Устройство состоит из следующих элементов;- десятичный сумматор 1, содержащий(2 п+1) десятичный разряд, имеющий информационные разрядные входы, управляющие входы сложение и вычитаниеи парафазный выход знака;- регистр 2 частного, содержащий(и+1) десятичный разряд и имеющий входсдвиг, первый управляющий вход, поступление сигнала на который обеспечиает установку единицы в младшем двоич 5 15 15 25 30 35 40 45 50 55 бО б 5 ном разряде регистра частного, и второй управляющий вход, сигнал на котором обеспечивает преобразование обратного десятичного кода, находящегося в младшем десятичном разряде регистра частного, в пр,ямой код;- регистр 3 делителя, содержащий (2 п+1) десятичный разряд, предназначенный для хранения десятичных цифр восьмикратного делителя и получения путем деления на два других его кратных, имеющий цепи деления на два, информационные разрядные выходы, соединенные с информационными входами соответствующих десятичных разрядов сумматора 1, информационные входы для младших 2 п десятичных разрядов, первый управляющий вход и управляющий вход,запись;- дополнительный регистр 4, содержащий 2 п десятичных разрядов и предназначенный для хранения восьмикратного делителя, имеющий информационные разрядные входы и выходы и управляющие входы, причем информационные входы дополнительного регистра соединены с соответствующими информационными выходами (1 - 2 п) -х десятичных разрядов регистра 3 делителя, входы младших десятичных разрядов которого подключены к соответствующим информационным выходам ре. гистра 4;- блок управления 5, имеющий вход 6 пуска, выходы 7 и 8, соедппсппыс с входами вычитание и сложение сумматора 1 соответственно, парафазный вход 9 знака, подключенный к выходу знака десятичного сумматора, выход 7, подсоединенный к первому управляющему входу 10 рссгистра 2 частного, выход 11 и 12, соединенные соответственно с управляющим входом регистра 4 и управляющим входом запись регистра 3, выход 13 соединенный с первым управляющим входом регистра 3, выход 14 и 15, подсоединенные соответственно к входу сдвиг и второму управляющему входу регистра 2 частного.Схема блока управления 5, обеспечивающая выполнение отдельных циклов деления, состоит из следующих элементов:- генератор 16 импульсов, выход которого соединен с выходом 14 блока управления;- двухразрядный двоичный счетчик 17, имеющий счетный вход, подключенный к выходу генератора 16 импульсов, и два выхода;- первый - седьмой элементы И 18 - 24, причем первые входы первого, второго, третьего, четвертого и пятого элементов И подключены к выходу генератора импульсов 16, вторые входы первого и пятого элементов И соединены с первым выходом счетчика 17, вторые вхады второго и ше ст ого и второй вход третьего элементов И подсоединены соответственно к парафаз 742933ному входу 9 отрицательного и положительного знака блока управления, выход первого элемента И подключен к первому входу шестого элемента И, выходы второ. го, третьего, четверто.о, пятого и седьмого элементов И соединены соответственно с выходами 8, 7, 13, 11 и 15 блока управления;- элемент НЕ 25, вход которого соединен с вторым выходом счетчика 17 и выходом 12 блока управления, а выход - с вторым входом четвертого элемента И;- первый - третий элементы задержки 26 - 28, причем вход первого элемента задержки соединен с выходом шестого элемента И, вхсды второго и третьего элементов задержки подключены к выходу первого элемента И, выход третьего элемента задержки соединен с первым входом седьмого элемента И;- триггер 29, первый и второй входы которого подключены соответственно к выходам первого и второго элементов задержки, а выход - к второму входу седьмого элемента И.Устройство (см. фиг. 1) обрабатывает десятичную информацию, представленную в коде 8 - 4 - 2 - 1.Деление в устройстве выполняется за (и+ 1) циклов. Каждый цикл состоит из четырех тактов. На каждом такте определяется соответствующий двоичный разряд двоична-десятинного изображения текущей десятичной цифры частотного. Деление выполняется методом без восстановления остатков.Устройство работает следующим образом, В исходном состоянии в сумматоре (десятичных разрядах 2 - (о+1) находится делимое, в старших (п+ 1) десятичных разрядах регистра делителя 3 помещен восьмикратный код делителя, первый десятичный разряд сумматора, разряды регистров 2 и 4 и младшие и десятичных разрядов регистра 3 установлены в нуль. Счетчик 17 и триггер 29 блока управления также установлены в нуль.На первом цикле определяется старший десятичный разряд частного.Первому такту соответствует нулевоесостояние счетчика 17 (потенциал на первом выходе счетчика). Поэтому по сигна.лу генератора 16 импульсов формируются сигналы на выходах 7 и 11 блока управления, Сигнал с выхода 7 поступает на вход вычитание десятичного сумматора .1, обеспечивая вычитание из делимого кода восьмикратного делителя. Знак результата вычитания поступает на парафазный вход 9 знака блока управления. Сигнал с выхода 11 поступает на управляющий вход дополнительного регистра, управляя запоминанием в регистре 4 содержимого 2 п старших десятичных разрядов регистра 3 (кода восьмикратного делителя). Кроме то-,о, сигнал с выхода 7 блокау : влепи: поступает на первый управляю 1 цп 1: вход регистра 2 частотного, выполняязапсссш;с единицы в младший разряд ре 5 г стра 2. Данная единица гасится во время первого такта первого цикла и сохраняется во всех остальных случаях.Одновременно по сигналу генератора 16импульсов формируется сигнал на выходе10 14 блока управления, Кроме того, срабатывает элемент НЕ 25 и четвертый элемент И 21, обеспечивая формирование сигнала на выходе 13 блока управления, Сигнал с выхода 13 поступает на первый уп 15 равляющпй вход регистра 3 делителя, обеспечивая деление его содержимого на два,Сигнал с выхода 14 блока управления поступает на управляющий вход сдвиг регистра 2 частного, выполняя сдвиг сго со 20 держимаго влево на один двоичный разряд.Кроме того, сигнал генератора 16 импульсов, поступая на счетный вход двухразрядного двоичного счетчика 17 блока25 управления, обеспечивает установку в немкода 01, На этом выполнение первого такта заканчивается.Второй, третий, и четвертый такты первого цикла выполняются следующим образом:- если знак результата вычитания всумматоре 1 положителен, то сигнал с выхода положительного знака сумматора поступает на вход 9 блока управления, обес 35 печивая срабатывание по очередному сигналу генератора .16 импульсов, элементаИ 20, сигнал с выхода которого поступаетна первый управляющий вход регистра 2частного и на управляющий вход вычита 40 ние десятичного сумматора 1, обеспечиваяустановку единицы в младший разряд регистра 2 частного и вычитание из содержимого сумматора 1 содержимого регистра 3;45 - если знак результата вычитания всумматоре 1 отрицателен, то сигнал с выхода отрицательного знака сумматора поступает на вход 9 блока управления и открывает, по очередному сигналу тенерато 50 раимпульсов, второй элемент И 19 бло.ка управления, сигнал с выхода которотопоступает на вход сложение сумматора1, обеспечивая добавление к содержимомусумматора 1 содержимого регистра 3.55 Знак результата сложепия - вычитанияпоступает на парафазный вход 9 блока управления,Одновременно с выполнением операциисложения - вычитания в сумматоре 1 по60 очередному сигналу генератора 16 импульсов добавляется единица к содержимомудвухразрядного двоичного счетчика 17 иформируются сигналы на выходах 13 и 14блока управления. Сигнал с выхода 14 поступает на вход сдвиг регистра 2 част742933 7 Р: аультат Исходные данные сложения -в я нтания+8000- ,-1120 0 0 0 1 ии8 Д:2= 4 Д 4 Д:2=2 Д сО Остатокотрицателен- 4000 - 2880 .-2000 сО .;0 2 Д:2=2 Старпая тетрада частного равна 0100- 880 +1600 + 720 - 800 - 80 8 Дсд 1 4 Дсд 1 2 Дсд 1 Цикл 2 О Остатокположителен-1-400 +320 - 200 О О Дсд ного, обеспечивая сдвиг его содержимого влево на один двоичный разряд, Сигнал с выхода 13 блока управления поступает на первый управляющий вход регистра 3 делигеля, управляя делением его содержимого на два,Как только содержимое счетчика 17 станет равным 11, что соответствует четвертому такту данного цикла, вырабатывается сигнал на втором выходе счетчика 17, запрещая работу четвертого элемента И 21 блока управления и обеспечив формирование сигнала на выходе 12 блока управления. Сигнал с выхода 12 поступает на вход запись регистра 3 делителя, обеспечивая запоминающие в регистре 3 содержимого регистра 4. В старший десятичный разряд регистра 3 при этом заносится значение нуль. На этом заканчивается цикл.Таким образом, к началу следующего цикла в регистре 3 зафиксирован восьмикратпый код делителя, сдвинутый на один десятичный разряд вправо. Второй и все последующие циклы вы- ПО:1115 ОТС 51 В ЗаГИСИХОСТП ОТ 3;ана РЕЗгЛЬ. тата операции сложения - вычитания по следнего такта предыдущего цикла, который запоминается в триггере 29 блока управления, На первом такте следующего цикла, которому соответствует состояние О счетгшка 17 (потенциал па первом выходе счетчика), по сигналу генератора 10 импульсов открывается первый элсмегт И 18, обеспечив, в случае отрицательного знака результата сложения - вычитания четвертого такта предыдущего цикла, поступление сигнала через первый элемент задержки 26 на первый вход триггера 29 (установку триггера в состояние 1), В случае положительного знака результа та последнего такта предыдущего циклашестой элемент И 23 окажется закрытым и сигнал генератора 16 импульсов поступит через первый элемент И 18 и второй элемент задержки 27 на второй вход триг гера 29, обеспечив его установку в состояние О.Если результат слоакепия - вычита иячетвертого такта предыдущего цкла и сумматоре 1 положителен, то данный ц 51 л 16 выполняется аналогично первому циклу,ЕСЛИ жЕ рЕЗЛЬтат СЛОжецпя - ВЬг 11 ТОния четвертого такта предыдущего цикл в сумматоре 1 окажется отрицательным, то 20 данныи цикл выполняется следующим образом. Все сигналы блока 5 управления на всех четырех тактах вырабатываются аналогично описанному для первого цикла.После завершения четвертого такта дан ного цикла (в начале первого такта следующего цикла) на выходе се;ьмого элемента И 24 блока управлегшя формируе ся управляющий сигнал, поступающийа второй управляющий вход регистра част- ЗО ПОГО ПО 1.ОТОрОГгГГ ВЫПО,Н 5 ЕТС 5 дэба В,10111 свеличины 1010 в младший;тесятичпый разряд частного. Десятггчный переос, гозникаоций прп этом, блокируется. З 6 В таблице дап пример работы прсдлагаемого устройства для деления а-разряд- Ы; ДССЯТ 5 гг 5111 ггИСЕЛ ПРИ УС гОВПИ делимое А =- 9120 г делитель Д =- 20, во-ьмикратный делитель ЯД = 100.)О О Младшая тетрада часВ данном примере гД соответствует г кратному делителю, гДсдг, соответствует г-кратному делителю после 1-го сдвига.Деление считается законченным по завершении +1-го цикла.5Аналогично выполняется деление дробных десятичных чисел,Г 1 олучение восьмикратного делителя можно выполнить различными способами. Одним из способов является получение де О сятикратного делителя путем сдвига делителя на один десятичный разряд влево с последующим двукратным вычитанием делителя из полученной после сдвига величины. 5Г 1 редлагаемое устройство обеспечивает выполнение операции деления десятичных чисел за максимальное время тного равна О 10 кращение и среднего времени деления це.сятичных операндов,Формула изобретения Устройство для деления гг-разрядных десятичных чисел, содержащее (211+1) -разрядные,десятичный сумматор, регистр дслителя, информационные выходы которого подключень к )п;формационным входам десяти:шого сумматора, (и+ 1) -разрядный регистр частного н блок управления, содержащий генератор импульсов, выход которого годключен к счетному входу двух- зарядного двоичного счетчика, элементы 1 Л, элементы НЕ, элементы задержки и триггер, причем выход генератора импульсов подключен к первым .входам первого, второго, третьего и четвертого элементов И, и через первьш элемент задержки к первому входу пятого элемента И, второй вход которого подключен к первому выходу двух- разрядного двоичного счетчика, второму входу первого элемента 11, выход которого через шестой элемент И и второй элемент задержки подключен к первому входу триггера, второй вход которого через третий элемент задержки подключен к первому входу шестого элемента И, второй вход которого и второи вход второго элемента И блока управления подключены к выходу отрицательного знака десятичного сумматора, выход положительного знака которого подключен к второму входу третьего элемента И блока управления, выход триггера и первый вход шестого элемента И подключены к входам седьмого элемента И, выходы второго и третьего элементов И блока управления подключены соответственно к управляющим входам сложенне и вычитание десятичного сумматора, выход генератора импульсов блока управления подключен к входу сдвиг регистра частного, выход четвертого элемента И блока управления подключен к первомупоавляющему входу регистра делителя, второй выход дв, хразряпного двоичного счетчика через элемент НЕ соединен с вторым входом четвертого элемента И, выход третьего элемента И блока управления подкл)очен к первому управляющему входу регистра частного, выход пятого элемента 11) 20 ТгиШ - 4 Тсигл+1 )где Т - "и;)тельность операции сложение - вычитание в сумматоре.Максимальное время деления десятичных чисел в известном устройстве составляет величину;(2) Тд 102 - 9 Тем(+1) 30 Из сопоставления выражений (1) и (2) следует, что в предлагаемом устройстве максимальное время выполнения операций деления десятичных чисел меньше в 2,25 раза, чем в известном устройстве. З 5Для среднего времени деления десятичных чисел Т;,"и предлагаемом устройстве имеем ТД 01 = Тд 101 = 4 Тсм 1 лСреднее время деления десятичных операндов в известном устройстве равно вели. 45 чинеСвТ 0 -+ 1 =5,5 Тси(а+1) . (4) На основании сопоставления выраже ний (3) и (4) можно сделать вывод, что предлагаемое устройство обеспечивает соИстинный код тетрады частного равен 1011+1010=0101И блока управления подключен к входу запись регистра делителя, о т л и ч а ющ е е с я тем, что, с цельо повышения быстродействия устройства, оно содержит дополнительный регистр, разрядность которого на один десятичный разряд меньше разрядности регистра делителя, разрядные выходы старших десятичных разрядов которого подключены к информационным входам дополнительного регистра, информационные выходы которого соединены с входами младших десятичных разрядов регистра делителя, управляющий вход с выходом пятого элемента И блока управления, второй управляющий вход регистра частного подключен к выходу седьмого элемента И блока управления.5Источники информации, принятые вовнимание при экспертизе: 1. Авторское свидетельство СССР 10 М 233296 М Кл б 06 Р 7(39 19672. Карцев М. А., Арифметика цифровыхмашин. - М Наука, 1969, с, 525 (прототип),Составитель Л. Глух ва едактор Н, Данилович Техред И, Пенчко Корректор И. Осиновскао к. фил. пред. Патент Заказ 1758/1287 Изд.628 Тнракк 719 ПодннсносНПО сПоискэ Государственного комитета СССР по делам изобретений и открытн113035, Москва, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

2357476, 03.05.1976

ПРЕДПРИЯТИЕ ПЯ М-5339

ПЕШКОВ АНАТОЛИЙ ТИМОФЕЕВИЧ, ГЛУХОВА ЛИЛИЯ АЛЕКСАНДРОВНА

МПК / Метки

МПК: G06F 7/39

Метки: деления, десятичных, п-разрядных, чисел

Опубликовано: 25.06.1980

Код ссылки

<a href="https://patents.su/7-742933-ustrojjstvo-dlya-deleniya-p-razryadnykh-desyatichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для деления п-разрядных десятичных чисел</a>

Предыдущий патент: Устройство выделения первого импульса и вычитания первого импульса из последовательности импульсов

Следующий патент: Устройство для умножения

Случайный патент: Устройство для фрикционно-механиче-ского нанесения покрытий ha внутренниеповерхности