Устройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

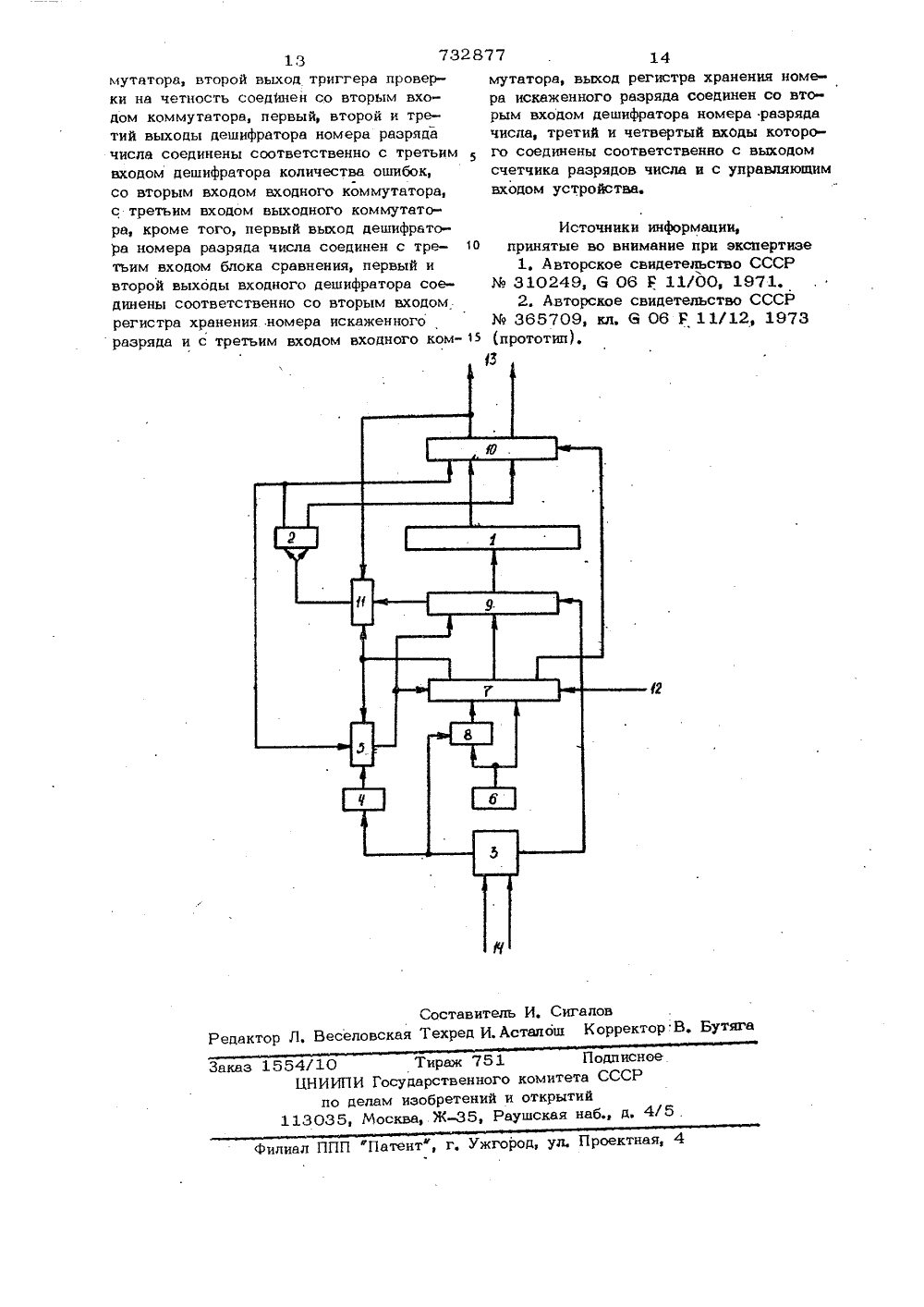

ОПИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскикСоциалкстическикРеспублик(22) Заявлено 30,03.76 (2 ) 2344065/18-24с присоединением заявки реао делам иэебретеииЯ и открытиЯ(54) УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ПОСЛЕДОВАТЕЛЬНОГО КОДА С КОРРЕКЦИЕЙ ОДИНОЧНЫХ ОШИБОК Изобретение относится к вычислительной технике и может быть применено вустройствах обмена цифровых вычислительных машин, в периферийных устройствахцифровых систем, в также в различных устройствах передачи дискретных данных.Известно устройство для кодирования и декодирования и коррекции одиночной ошибки,содержащее сдвигающий регистр, по входуи выходу связанный соответственно с при 0емными и передающими линиями связи 1В указанном устройстве производитсяпреобразование исходного параллельногокода в последовательный при выдаче информации и соответственно обратное прет 5образование последовательного кода в параллельный при приеме информации, причемкаждая из этих операций осуществляетсяза счет сдвиге информации в сдвигающемрегистре,20Использование режима сдвига информации обусловливает недостаточно высокуюдостоверность функционирования этих устройств при прямом и обратном преобразо 2ванин кодов. Например, вследствие того, что в формировании информации последнего разряда передаваемого или принимаемого сообшения участвуют цепи переноса и триггеры практически всех разрядов регистра неисправность, любого из этих элементов приводит к возникновению ошибок, не обнаруживаемых контролем. Использование в этих устройствах сдвигающих уст- ройств не допускает также диагностирование отказов их элементов.Наиболее близким к предлагаемому по технической сущности и достигаемому результату является устройство для кодирования и декодирования последовательного кода с коррекцией одиночной ошибки, содержащее сдвиговой регистр числа, осуществляющий прием и выдачу информации с соответствующим прямым и обратным преобразованием последовательного кода в параллельный, соединенные с двухпроводной линией связи шифратор, кодирующий каждый разряд выдаваемого числа, и. входной дешифратор, преобразующий принктз 73287 маемый код в код "1" или 0, триггер со счетным входом для образования контрольного кода выдаваемой информации и для контроля принимаемой информации, счетчик разрядов числа, счетчик и дешифратор количества ошибок, регистр хранения номера искаженного разряда и дешифратор этого номера 21.Основным недостатком этого устройства является пониженная достоверность 10 преобразования параллельного кода в последовательный при выдаче информации и соответственно последовательного кода в параллельный при приеме информации, обусловленная применением сдвигового ре гистра, надежность функционирования которого в каждом такте связи зависит от исправности срабатывания практически каждого его элемента. Недостаточная достоверность передачи информации в данном 20 устройстве определяется также тем, что при приеме сообщения данные в триггер контроля на четкость ответвляются со входа сдвигового регистра, при этом правильное срабатывание контроля является всего лищь необходимым, но недостаточным условием для безошибочной установки принятого кода на триггерах сдвигового регистра.Недостатки данного устройства, заклю- З 0 чаются также в невозможности диагностирования неисправного узла, "разрушении" информации в регистре после выдачи слова,обусловленное спецификой работы сдви гового регистра, что, в свою очередь, ис ключает возможность оперативного повторения пеоедачи слова, искаженного многократной ошибкой.Наконец, использование для перекоди 40 ровки двоичного кода в корреляционный парафазный код специального шифратора является неоправданным, так как при наличии триг"еров эта процедура может быть выполнена за счет одновременного45 считывания состояния триггера с его единичного и нулевого выходов.Бель изобретения - повышение достоверности.Указанная цель достигается тем, что в устройство для кодирования и декодирования цоследовательного кода с коррекцией одиночных ошибок, содержащее регистр, триггер проверки на четкость,входной дешифратор, счетчик количества ошибок, дешифратор количества ошибок, счетчик разрядов числа, дешифратор номераразряда числа и регистр хранения номера искаженного разряда, причем первый вы 7ход входного дешифратора соединен совходом счетчика количества ошибоквыход которого соединен с первым входомдешифратора количества ошибок, выходсчетчика разрядов числа соединен с первым входом регистра хранения номераискаженного разряда, входы входного дьшифратора являются информационными входами устройства, введены блок сравнения,входной и выходной коммутаторы, причем первь:й х второй выходы выходного коммутатора являются выходами устройства, первь 1 й выход выходного коммутатора соединен с первым входом блока сравнения,выход которого соединен со счетным входом триггера проверки на четность, первый выход триггера проверки на четностьсоединен с первым входом выходного коммутатора и со вторым входом дешифратора количества ошибок, выход которого сое - )дииен с первыми входами входного коммутатора и дешифратора номера разряда числа, первый и второй выходы входного коммутатора соединены соответственно совторым входом блока сравнения и с первым входом регистра, выход которого соединен с информационным входом выходного коммутатора, второй выход триггерапроверки на четность соединен со вторымвходом выходного колмутатора, первый,второй и третий выходы дешифратора номера разряда числа соединены соответственно с третьим входом дешифратора количества ошибок, со вторым входом входного коммутатора, с третьим входом выходного коммутатора, кроме того, первыйвыход дешифратора номера разряда числасоединен с третьим входом блока сравнения, первый и втором выходы входногодешифратора соединены соответственно совторым входом регистра хранения номера.искаженного разряда и с третьим входомвходного коммутатора, выход регистрахранения номера искаженного разряда соединен со вторым входом дешифратора номера разряда числа, третий и четвертыйвходы которого соединены соответственнос выходом счетчика разрядов числа и суправляющим входом устройства,На чертеже приведена структурная схема предлагаемого устройства,Устройство содержит регистр 1, триггер 2 проверки на четность, входной дешифратор. 3, счетчик 4 количества ошибок,дешифратор 5 количества ошибок, счетчикб разрядов числа, дешифратор 7 номераразряда числа, регистр 8 хранения номераискаженного разряда, входной Коммутатор732877 59, .выходной коммутатор 10, блок 11сравнения, шину 12 "Передача и передающую 13 и приемную 14 двухпроводныелинии связи,Входы входного дешифратора 3 соединены с приемной линией связи 14, егопервый выход соединен со вторым входомрегистра 8 хранения номера искаженногоразряда, у которого первый вход соединенс выходом счетчика 6 разрядов числа, ивходом счетчика 4 количества ошибок, выход которого соединен с первым входом дешифратора 5 количества ошибок.Первый вход дешифратора 7 номераразряда числа соединен с выходом дешифратора 5 количества ошибок, к которомутакже подключен первый вход входногокоммутатора 9, его второй вход - с выходом регистра 8 хранения номера искаженного разряда, третий вход - с выходом 2 Осчетчика 6 разрядов числа и четвертыйвход - с управляющим входом шины 12"Передача"Второй вход входного коммутатора 925поразрядно соединен с шинами первого выхода дешифратора 7 номера разряда числа, его третий вход - со вторым выходомвходного дешифратора 3, а второй выходпоразрядно - с единичными входами тригЭОгеров регистра 1,Первый и второй входы выходного коммутатора 10 соединены соответственно с единичным и нулевым выходами триггера 2 проверки на четкость, а первый и. Э 5 второй выходы с передающей линией 13связи.Третий вход выходного коммутатора 10 поразрядно соединен с шинами второ 40 го выхода дешифратора 7 номера разряда числа, его информационный вход также поразрядно соединен единичными выходами триггеров регистра 1. Первый вход блока 11 сравнения сое 45 динен с первым выходом выходного коммутатора 10, второй вход со вторым выходом входного коммутатора 9, третий вход с пер 1 вым выходом дешифратора 7 номера разряда числа, к которому также подключен третий вход дешифратора 5 количества ошибок, Выход блока 1 1 сравнения соединен со счетным входом триггера 2 проверки на четкость, единичный выход которого также соединен со вторым входом дешифратора 5 количества ошибок.Устройство работает следующим обра зом. 6При выдаче информации на регистре 1устанавливается код передаваемого сообщения,При этом поразрядно на информационном входе выходного коммутатора 10 сединичных и нулевых плеч триггеров регистра 1 в соответствии с заданным кодом устанавливаются открывающие и закрывающие потенциалы. Если триггер1 -го разряда в регистре 1 находится вединичном состоянии, то по этому разряду на второй и третий входы выходногокоммутатора 10 поступают соответственно открывающий и закрывающий потенциалы, если триггер находится в нулевомсостоянии, то по этому разряду удерживаются соответственно закрывающий и открывающий потенциалы.Перед началом выдачи информации насчетчике 6 разрядов числа устанавливается код "И ", соответствующий количествуинформационных разрядов в передаваемомсообщении, Далее на.управляющий вход дешифратора 7 номера разряда числа по шине 12 "Передача поступает первый тактирующий сигнал. В соответствии с расшифрованным состоянием счетчика 6 дешифратор 7 вырабатывает на третьем выходе сигнал, который, поступая на третийвход выходного коммутатора 10, опрашивает состояние триггера первого разрядарегистра 1, При этом, еслн этот триггернаходится в нулевом состоянии, то на первый и второй выходы выходного коммутатора 10 выдается код "1, если триггернаходится в состоянии "1", то на этихже выходах появляется код "10". Далеевыработанная кодовая посылка поступаетв передающую линию связи 13,Аналогичным образом срабатывают последующие тактирующие сигналы, поступающие по шине 12 "Передача". Каждый изэтих сигналов вычитает единицу из состояния счетчика 6 разрядов числа (эта цепьна схеме не показана), в результате чегодешифратор 7 на своем втором выходе вырабатывает сигналы, последовательно оп=рашиваюшие состояние триггеров регистра 1 от первого до последнего информационного разряда,Одновременно подается сигнал с первого выхода выходного коммутатора 10 напервый вход блока 11 сравнения, которыйпри отсутствии сигналов на его второми третьем входах (что определяется соответственно режимом выдачи информациии выдачей информационных разрядов) покаждой кодовой посылке "10 пропускает732877 7сигнал на свой выход, переключая триггер2 в противоположное состояние, что, всвою очередь, определяет четность количества.единиц в переданном слове,После выдачи состояния триггеров всехинформационных разрядов на счетчикеколичества разрядов устанавливается кодфО", при котором дешифратор 7 вырабатывает последний выдающий сигнал.Этот сигнал опрашивает состояние тригге Ора 2, который к этому моменту временихранит информацию, полностью соответствующую четности количества единиц в переданном слове, Если число единиц в переданном слове четко, то триггер 2 находится в нулевом состоянии и в последней(контрольной) посылке в передаваемую линию связи 13 передается код 01",Если число единиц в слове нечетно, тотриггер 2 находится в единичном состоянии и в контрольной посылке передаетсякод "10". При коде "0-00" на счетчике6 разрядов числа дешифратор 7 вырабатывает сигнал также на свой первый выход,который, поступая на третий вход блокасравнения 11 (независимо от информации,поступающей на его первый вход с выходавыходного коммутатора 10, т,е, даже присчитывании единичного состояния триггера 2), блокирует прохождение сигналовна счетный вход триггера 2, что сохраняет его состояние, а следовательно, и результат контроля до начала выдачи следующего слова.При приеме слова в устройство в зави- З 5симости от нулевого или единичного значения информации разряда, передаваемойв данной посылке, на вход входного дешифратора 3 из приемной линии 14 связи последовательно поступают кодовые посылки "01" или "10", Дешифратор 3 преобразует эти посылки в двоичный код. Причем,если на вход дешифратора 3 поступаеткод "10", то на его второй выход выдается сигнал, который далее поступает натретий вход входного коммутатора 9, ес-.ли же не посгупает код 01", то на выход дешифратора 3 сигнал не выдается.Управление установкой принимаемойинформации, также как и при выдаче информации, осуществляется дешифратором7 номера разряда, который расшифровывает состояние счетчика 6, ведущего подсчет количества принятых разрядов числа,55Перед началом приема очередного слова регистр 1 и триггер 2 проверки начетность устанавливаются в О", а насчетчике 6 количества разрядов числа 8устанавливается код 0+1", который на единицу превышает код, устанавливаемый на этом счетчике в режиме выдачи информации.При приеме по каждому тактирующему сигналу, поступающему по шине 1 2"Передача", дешифратор 7 в зависимости от состояния счетчика 6 вырабатывает на шины своего первого выхода сигналы, которые поразрядно поступают на первый вход входного коммутатора 9, Этот блок в соответствии с номером разряда числа разрешает прохождение сигнала со второго выхода входного дешифратора 3 на один из своих выходов, Если с выхода входного дешифратора 3 поступил сигнал, что соответствует приему кода 10, то в момент тактирования со второго выхода входного коммутатора 9 на единичный вход регистра 1, соответствующий номеру разряда числа, подается сигнал, который переключает этот триггер в единичное состояние. Если же со второго выхода дешифратора 3 сигнал не выдается, что соответствует приему кода "01, то на выход входного коммутатора 9 сигнал также не выдается, в результате чего триггер регистра 1 в соответствующем разряде остается в нулевом ссстоянии.Одновременно с управлением установкой принимаемой информации дешифратор 7 номера разряда числа вырабатывает сигналы по третьему выходу, что обеспечивает последовательное считывание на контроль состояния триггеров регистра 1, которое осуществляется непосредственно после установки на них принятого кода, При этом возбуждение шин на втором выходе дешифратора 7, ввиду сдвига исходного кода на счетчике разрядов числа 6, происходит с отставанием на единицу относительно возбуждения шин на третьем выходе этого дешифратора. Так при коде " И +1" на счетчике 6 на третьем выходе дешифратора 7 возбуждается первая шина, что обеспечивает соответствующую установку триггера первого разряда регистра 1, а на втором выходе дешифратора 7 вообще не возбуждается ни одна шина,При коде на счетчике 6 на третьем выходе дешифратора 7 возбуждается вторая шина, а на втором выходе первая, что соответственно обеспечивает прием информации во второй разряд регистра 1 и опрос состояния триггера первого разряда регистра 1, в которое он был установлен в предыдущем такте связи, Б случае единичного состояния триггера первого разряда в момент опроса на первый выход10 прохождению сигнала на выход этого блока, сохраняя прежнее состояние триггера 2,Если после просчета состояния триггера ( И)-го разряда триггера 2 находится в единичном состоянии, что свидетельствует о нечетном количестве единиц в( И -1)-ых разрядах, то код контрольнойпосылки должен быть неравнозначен состоянию триггера И -го разряда.Если в й-ом разряде имеет местонулевое состояние, то в контрольной посылке должен поступить код 1, если вИ-ом разряде имеет место единичное состояние, то в контрольной посылке долженпоступить код О", В этих случаях сигналсо входа блока 11 неравнозначности проходит на его выход и далее поступает насчетный вход триггера 2, переключая егов нулевое состояние,После приема контрольной посылки насчетчике разрядов числа 6 устанавливается код 0-00", при котором вырабатывается сигнал коррекции возможной ошибки.Если в процессе приема слова на входной дешифратор 3 из линии 14 связи поступает код 00 или 11, то на егопервык выход выдается сигнал ошибки,который переписывает соответствующееномеру сбившегося разряда числа состояние счетчика 6 количества разрядов в регистр 8 хранения номера искаженного разрядаи одновременно запоминается в счетчике 4 количества ошибок, при этом на второй выход входного дешифратора 3 сигнал не выдается,При опросе дешифратора 7 (код "0-00")на счетчике 6 вырабатывается сигнал наего первый выход, откуда он поступаетна второй вход дешифратора 5 количестваошибок, опрашивая его состояние, Еслив это время на первом входе дешифратора 5 с выхода счетчика 4 удерживаетсякод 1", что соответствует обнаружениюодиночной ошибки,. и на второй вход с едьничного выхода триггера 2 проверки начетность поступает открывающий потенциал, что соответствует нарушению четности количества единиц в принятом слове,то на выход дешифратора 5 с незначительной задержкой выдается сигнал, которыйпоступает на первый вход дешифратора 7номера разряда числа и на первый входвходного коммутатора 9, При этом дешифратор 7 расшифровывает состояние регистра 8 хранения номера искаженного разряда, возбуждая на своем втором выходесоответствующую шину, в результате чеговыходной коммутатор 9 пропускает сигС 732877 выходного коммутатора 10 выдается сигнал, который блоком сравнения 11 пропускается на счетный вход триггера 2, что обеспечивает контроль на четность принимаемой информации.5После приема. последнего ( И-го) информационного разряда на счетчике 6 количества разрядов устанавливается код 1, при этом в регистре 1 принимает код всех И информационных разрядов сло ва, а в триггер 2 контроля на четность передается состояние всех триггеров регистра 1, кроме последнего ( 0 -го). В последней (0+1)-ой посылке в устройство поступает .код контрольного разряда переданного слова, Код "1", находящийся в этот момент на счетчике 6, возбуждает на третьем выходе дешифратора 7 (0+1)-ю шину, а на втором выходе - р -ую шину, Входной коммутатор 9 разрешает прохож дение принимаемого сигнала на свой первый выход, откуда он далее поступает на второй вход блока 1 1 сравнения. Одновременное возбуждение И-ой шины на вто 25 ром выходе дешифратора 7 опрашивает выходной коммутатор 10, считывая на первый вход блока 11 сравнения состояние триггера последнего (И -го) разряда регистра 1, При этом на счетный вход триг 30 гера 2 блок 1 1 сравнения пропускает сигнал только в том случае, если принимае.- мый код контрольного разряда слова и состояние триггера последнего разряда регистра 1 неравнозначны, что не нарушает правильность механизма определения четности количества единиц в переданном слове.Действительно, если после просчета состояния триггера ( п -1)-го разряда.40 триггер 2 находится в нулевом состоянии, то это означает, что в ( Н)-ых разрядах числа было четное количество единиц. При этом, если триггер й-го разряда находится в нулевом состоянии,45 то в последней (контрольной) посылке в устройство должен поступить код О. В этом случае ни на первый, ни на второй входы блока 11 сравнения сигналы не поступают соответственно триггер 2 ос50 тается в прежнем состоянии.Если в Н -ом разряде имеет место единица, то в (И+1)-ой (контрольной) посылке должен поступить код 1. При этом на первый и второй входы блока 11 сравнения одновременно поступают сигналы с первого выхода выходного коммутатора 10 и с первого выхода входного коммутатора 9, что также препятствуетцел со своего второго входа на единичныйвход триггера "сбившегося" разряда, Этотсигнал переключает триггер в единичноесостояние, корректируя ошибку, возникшуюпри приеме. Если нарушения четности незафиксированы или обнаружена более чемодноразовая ошибка, то работа дешифратора 5 количества ошибок полностью блокируется.При коде 0-00 на счетчике 6 одною ю1 Овременно с выработкой сигнала на первыйвыход дешифратор 7 вырабатывает сигнална свой второй выход, который опрашивает состояние триггера 2, однако переключение триггера 2 не происходит в видутого, что сигнал с первого выхода дешифратора 7, опрашиваюший дешифратор 5 количества ошибок, одновременно подаетсяна вход блоке 11 сравнения, запрещая прохождение сигналов на его выход. Это ис-ключает сброс в."0 триггера 2, сохраняя в нем на момент коррекции информацию о нарушении четности,Основным техническим преимушествомпредлагаемого устройства является повышеннея достоверность преобразования параллельного кода в последовательный привыдаче информации и соответственно последовательного кода в параллельный при приеме информации. Повышение достоверностиобеспечивается тем, что прием и выдачаинформации осуществляется без использования режима сдвига информации в резисторе, в результате чего из цепей регистре полностью исключены схемы переносаинформации. Поэтому в предлагаемом устройстве триггеры регистра как при выдаче, так и при приеме информации работают в статическом режиме, т,е, процессвыдачи информации заключается в опросесостояния триггера, беэ каких-либо егопереключений, прием информации состоитвсего лишь в разовой установке триггерав единичное состояние, либо вообще в отсутствии какого-либо оперирования с нимесли передается "0")"Съем" состоянияосуществляется непосредственно с триггера того разряда регистра, информация которого передается, Аналогично установкапринятой информации осуществляется непосредственно на триггер соответствующего разряда регистра,Повышение достоверности обеспечивается в устройстве также тем, что выдачана контроль передаваемой и принимаемойинформации осуществляется тоже непосредственно с триггеров регистра, при этомотсутствие нарушения четности свидетельствует не только о неисправности передачиинформации, но и о верности ее установкина триггерах регистра,Важным преимушеством предлагаемого устройства является возможность глубокого диагностирования неисправностиего элементов, которое обеспечиваетсятем, что отказы триггеров регистра илиобрамляющего регистр оборудования неприводят к размножению ошибок, а вызывают всего лишь возникновение локализованной неперемешаюшейся неисправности,а также сохранение информации на передаюлем конце после выдачи слова, что позволяет оперативно повторить его выдачув случаях, когда передача подвергаетсямногократной ошибке,Формула изобретенияУстройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок, содержащее регистр, триггер проверки не четность,входной дешифратор, счетчик количества ошибок, дешифратор количества ошибок, счетчик разрядов числа, дешифратор номера разряда числа и регистр хранения номера искаженного разряда, причем первый выход входного дешифратора соединен со входом счетчика. количества ошибок, выход которого соединен с первым входом дешифретора количества ошибок, выход счетчика разрядов числа соединен с первым входом регистра хранения номера искаженного разряда, входы входного дешифратора являются информационными входами устройстве, о т л и ч а ю ш е е с я , тем, что, с целью повышения достоверности, в устройство введены блок сравнения, входной и выходной коммутаторы, причем первый и второй выходы выходного коммутатора являются выходами устройства, первый выход выходного коммутатора соединен с первым входом блоке сравнения, выход которого соединен со счетным входом триггера проверки не четность, первый выход триггера проверки начетность соединен с первым входом выходного коммутатора и со вторым входом дешифратора количества ошибок, выход которого соединен с первыми входами входного коммутатора и дешифратора номера разряда числа, первый и второй выходы входного коммутатора соединены соответственно со вторым входом блока сравнения и с первым входом регистра, выход которого соединен с информационным входом выходного ком42 Составитель И, Сигаловловская Техред И. Асталош КорректорВ. Бутяга Редакт 751 Подписноеенного комитета СССР ений и открытий5, Раушская наб., д, 4/5 54/10 Тираж ЦНИИПИ Государств по делам изобре 113035, Москва, ЖЗака филиал ППП Патент", г, Ужгород, ул. Проектная, 4 732877 14 мутатора, второй выход триггера провер- мутатора, выход регистра хранения номки на четность соединен со вторым вхо- ра искаженного разряда соединен со втодом коммутатора, первый, второй и тре- рым входом дешифратора номера разряда тий выходы дешифратора номера разряда числа, третий и четвертый входы которо- числа соединены соответственно с третьим 5 го соединены соответственно с выходом входом дешифратора количества ошибок, счетчика разрядов числа и с управляющим со вторым входом входного коммутатора, входом устройства. с третьим входом выходного коммутатора, кроме того, первый выход дешифрато- Источники информации ра номера разряда числа соединен с тре О принятые во внимание при экспертизе тьим входом блока сравнения, первый и 1. Авторское свидетельство СССР второй выходы входного дешифратора сое-310249, 6 06 Р 11/00, 1971. динены соответственно со вторым входом 2. Авторское свидетельство СССР регистра хранения .номера искаженного365709, кл. б 06 Г 11/12, 1973 разряда и с третьим входом входного ком (прототип),В

СмотретьЗаявка

2344065, 30.03.1976

ПРЕДПРИЯТИЕ ПЯ Г-4677

ВЕРШКОВ ВИТАЛИЙ ЭММАНУИЛОВИЧ, ГРАЧЕВ ВЛАДИМИР НИКОЛАЕВИЧ, ДЮКОВ ВЛАДИМИР КИРИЛЛОВИЧ, КАРАСЕВ ВИКТОР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 11/08, H03M 13/51

Метки: декодирования, кода, кодирования, коррекцией, одиночных, ошибок, последовательного

Опубликовано: 05.05.1980

Код ссылки

<a href="https://patents.su/7-732877-ustrojjstvo-dlya-kodirovaniya-i-dekodirovaniya-posledovatelnogo-koda-s-korrekciejj-odinochnykh-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования и декодирования последовательного кода с коррекцией одиночных ошибок</a>

Предыдущий патент: Устройство для контроля правильности выполнения программ при сбоях

Следующий патент: Устройство для реализации логических функций

Случайный патент: Утюг