Цифровой приемник сигналов многочастотного кода

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1741292

Автор: Охлобыстин

Текст

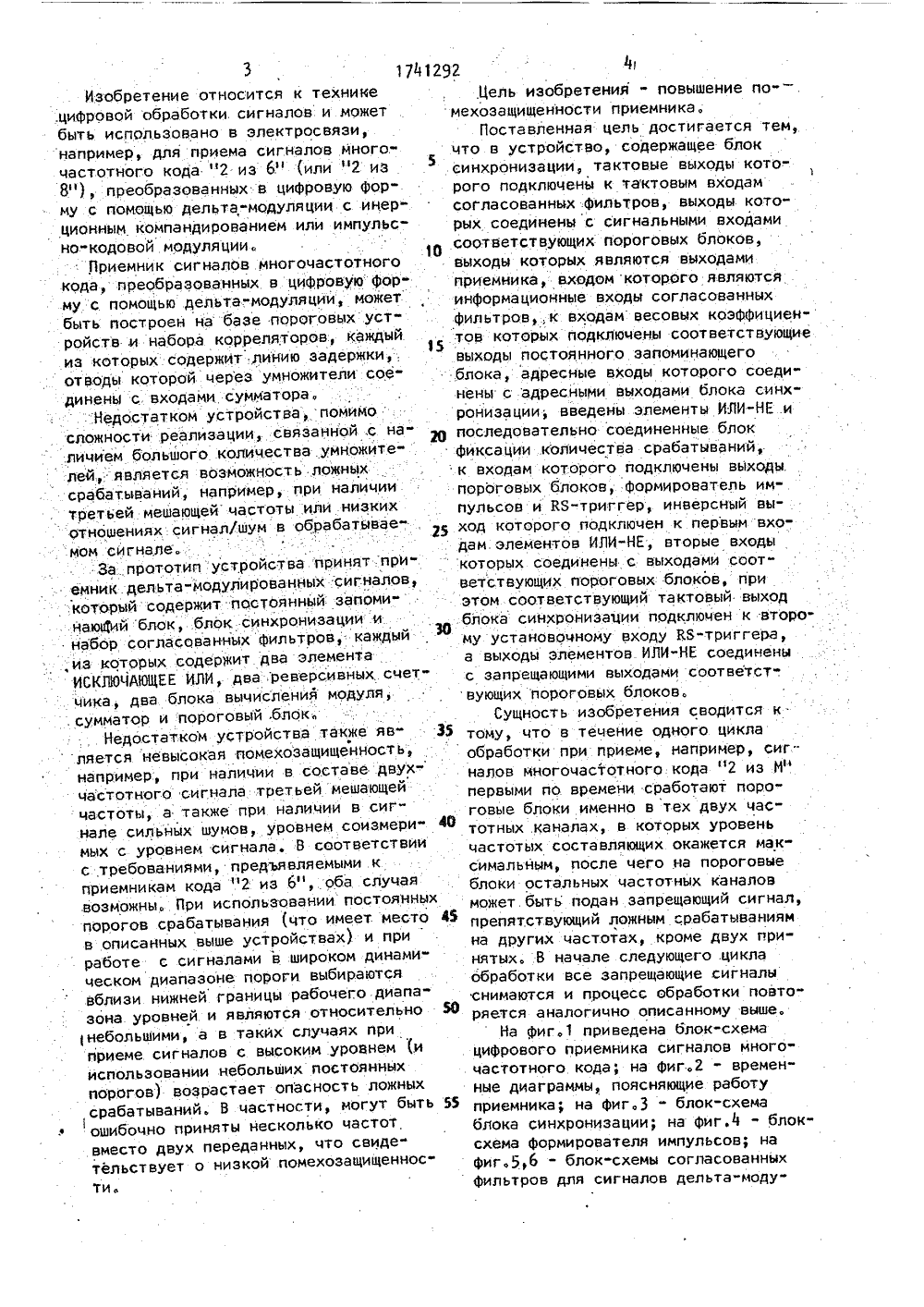

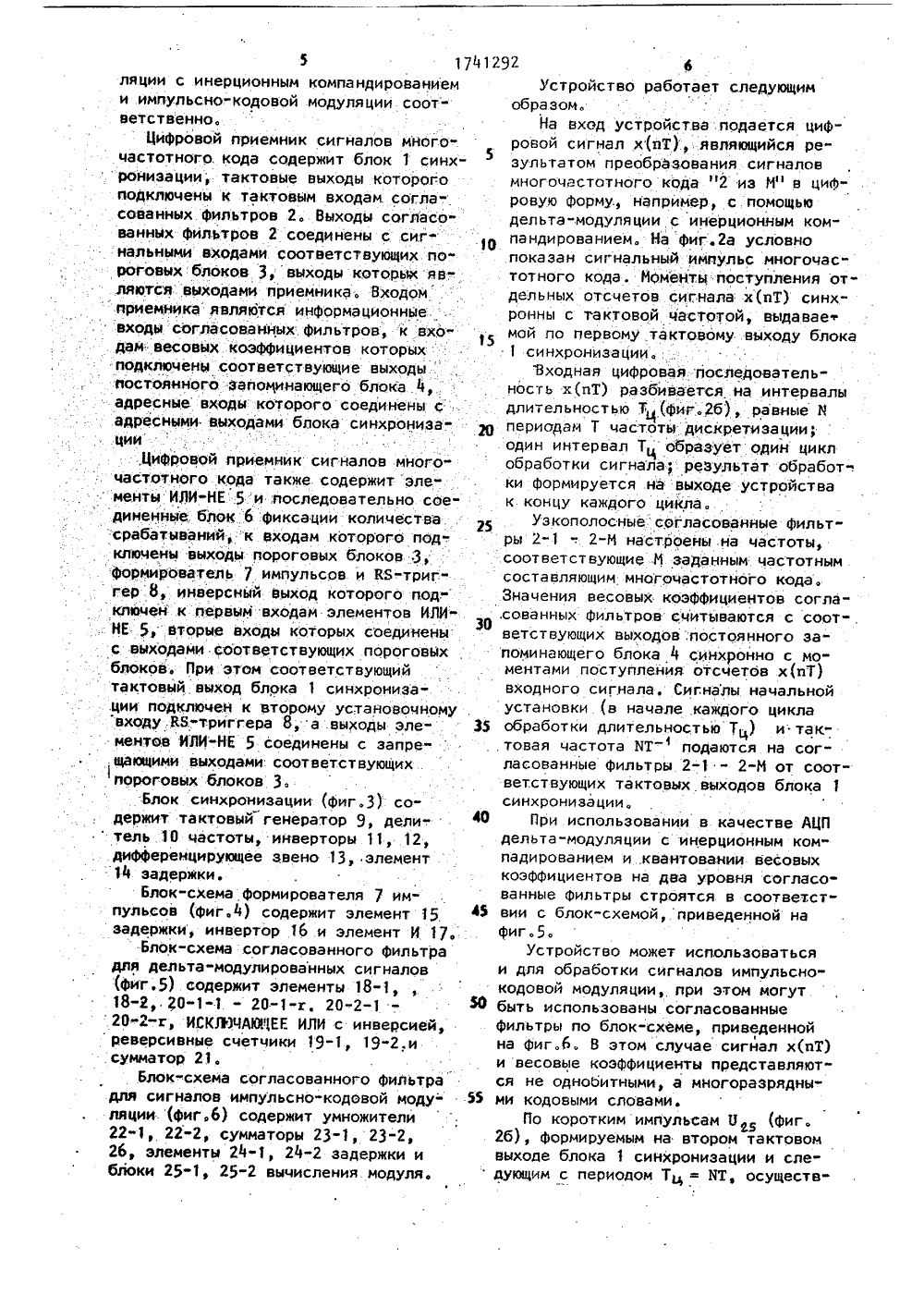

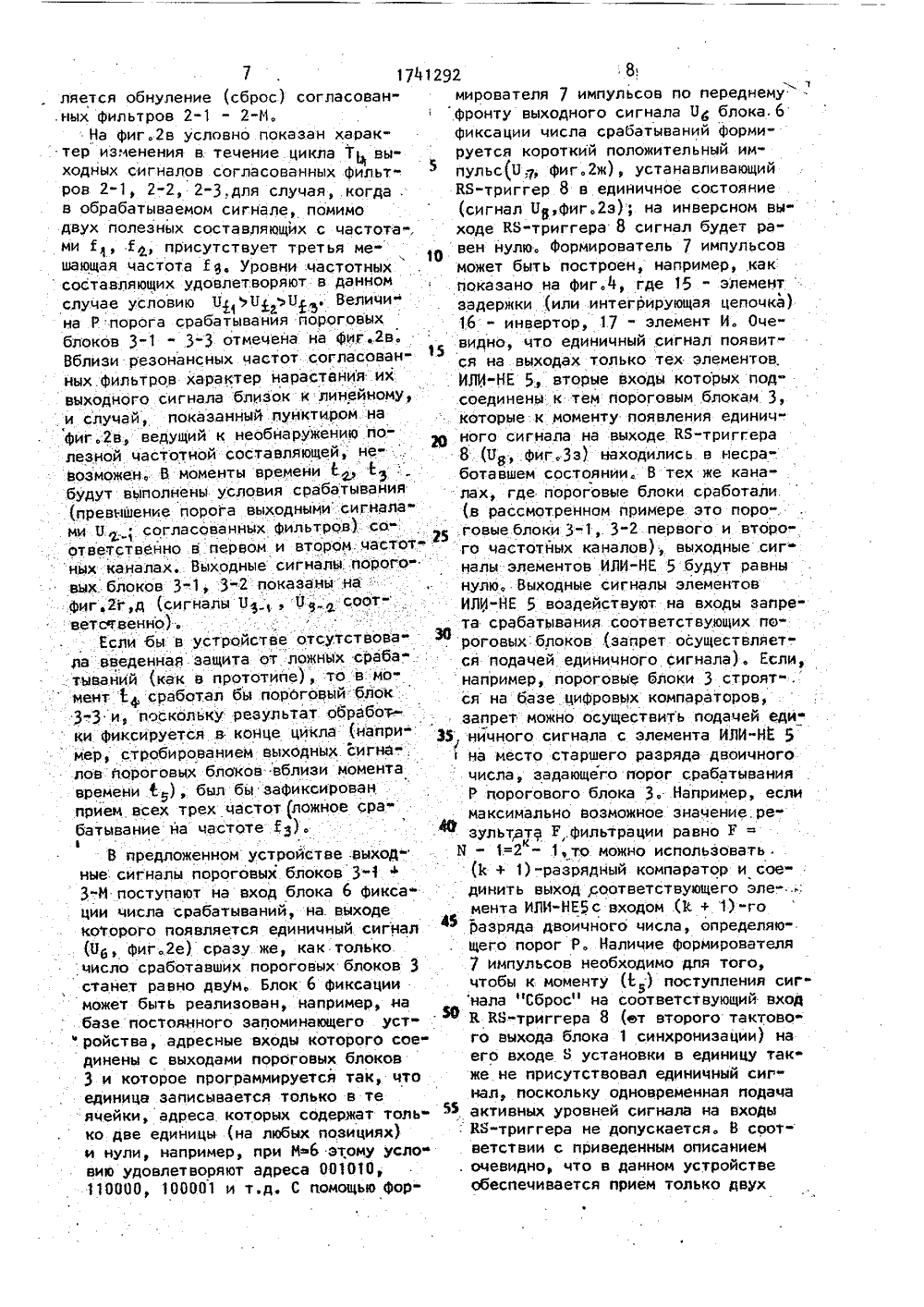

3, 1741292 фИзобретение относится к технике ,Цель изобретения " повышение по. .цифровой обработки. сигналов и может мехозащищенности приемника. быть использовано в электросвязи, Поставленная цель достигается тем, например, для приема сигналов много.- что в устройство, содержащее блок частотного кода "2 из 6" (или "2 из синхронизации, тактовые выходы кото"), преобразованных в цифровую фор- рого подключены к тактовым входам му с помощью дельта"модуляции с инер- согласованных фильтров, выходы кото"ционным компандированием или импульс- рых соединены с сигнальными входами но"кодовой модуляции. соответствующих пороговых блоков,Приемник сигналов многочастотного выходы которых являются выходамикода, преобразованных в цифровую фор" приемника, входом которого являютсяму с. помощью дельта."модуляции, может , информационные входы согласованныхбыть построен на базе пороговых Уст- фильтров, к входам весовых коэффициенройств и набора корреляторов, каждый тов которйх подключены соответствующие15из которых содержит. линию задержки выходы постоянного запоминающегоотводы которой через умножители сое" блока, адресные входы которого соедидинень с входами сумматора. . нены с адресйыми выходами блока синх:Недостатком устройства, помимо ронизации; введены .элементы ИЛИ-НЕ .исложности: реализации,. связанной,с на рО последовательно соединенные блокличием большого .количества умножите" фиксации количества срабатываний,лей является возможность ложных ,к входам которого подключены выходыУсрабатываний, например, при наличии пороговых блоков, формирователь имтретьей мешающей частоты или низких пульсов и КБ-триггер, инверсный выотношениях сигнал/шум в обрабатывае" 2 с ход которого подключен к первым вхо"мом сигнале.. Дам элементов ИЛИ-НЕ, вторые входыЗа .прототип устройства принят "Р" которых соединены с выходами соотемник дельта-модулированных сигналовф ветствующих пороговых блоков, прикоторый содержит постоянньй запоми этом соответствующий тактовый выходор блок .блок синхронизации и . блока синхрониэации подклюцен к второ 30набор согласованныхФильтРов каждый . му установочному входу ВЗ-триггера, ,из которых соде .орых содержит два элемента а выходы элементов ИЛИ"НЕ соединеныИСКЛЮцдвщЕЕ ИЛИ, два .Реверсивных. счет" с запрещающими выходами соответст-.цика, два блока вычисления модУля вующих пороговых блоков. . сумматор и пороговый, блок. :, Сущность изобретения сводится кНедостатком устройства также яв" Э 5 тому, что в тецение одного циклаляется невысокая помехозащищенность, : обработки при приеме, например, сигнапример, при налиции в составе двух" налов многоцастотного кода "2 из И"частотного сигнала третьей мешающей первыми по времени сработают поро"частоты, а также при наличии в сиг" говые блоки именно в тех двух цаснале сильных шумов, уровнем соизмери тотных .каналах, в которых уровень46мых с уровнем сигнала. В соответствии частотых составляющих окажется мак"с требованиями, предъявляемыми к симальным, после цего на пороговыеприемникам кода "2 иэ 6", оба случая блоки остальных частотных каналоввозможны. При использовании постоянных может быть подан запрещающий сигнал,порогов срабатывания (цто имеет место М препятствующий ложным :рабатываниямв описанных выше устройствах) и при на других частотах, кроме двух приработе с сигналами в широком Динами нятых, В начале следующего .циклаческом диапазоне пороги выбираются обработки все запрещающие сигналывблизи нижней границы Рабочего диапа снимаются и процесс обработки повто"зона уровней и являются относительно ф ряется аналогично описанному выше, небольшими, а в таких случаях при На фиг.1 приведена блок-схемаприеме сигналов с высоким уровнем 1 и цифрового приемника сигналов много" использовании небольших постоянных частотного кода; на Фиг.2 - времен"дорогов) возрастает опасность ложных ные диаграммы, поясняющие работусрабатываний, В частности, могут бытьприемника; на фиг.3 " блок-схема .фошибочно приняты несколько цастот. блока синхронизации; на Фиг.4 - блок"вместо двух переданных, что свиде" схема формирователя импульсов; нат льствует о низкой помехозащищеннос фиг.5,6 - блок-схемы согласованных тельствуетти. фильтров для сигналов дельта"моду"17ляции с инерционным компандированиеми импульсно-кодовой модуляций соответственно.Цифровой приемник сигналов много"частотного, кода содержит блок 1 синхронизации, тактовые выходы которогоподключены к тактовым входам согла"сованных фильтров 2. Выходы согласо"ванных фильтров 2 соединены с сигнальными входами соответствующих пороговых блоков 3, выходи которьа яв".ляются выходами приемника. Входомприемника являются информационныевходы согласованйых фильтров, к входаи: весовых коэффициентов которыхподключены соответствующие выходыпостоянного запоминающего блока.4,адресные входы которого соединены садресными выходами блока синхронизации.Цифровой приемник сигналов много"частотного кода также содержит элементы ИЛИ-НЕ 5 и:последовательно соединенные блок 6 фиксации количествасрабатываний, к входам которого под-.ключены выходы пороговых блоков 3,:формирователь 7 импульсов и КЯ-. триг.гер 8, инверсный выход которого под."клюнен к первым входам элементов ИЛИ". НЕ 5, вторые входы которых соединеныс выходами соответствующих пороговыхблоков, При этом соответствующийтактовый. выход блока 1 синхрониза.ции подключен к второму установоцному .входу КБ.-триггера 8,"а .выходы элементов ИЛИ-НЕ 5 соединены с запре" ..сумматор 21.Блок"схема согласованного фильтрадля сигналов импульсно-кодовой моду"ляции.(фиг.6) содержит умножители22"1, 22-2, сумматоры 23-1, 23-2,26, элементы 24-1, 24-2 задержки иблоки 25-1, 25-2 вычисления модуля. 41292 бУстройство работает следующимобразом.На вход устройства .подается цифровой сигнал х(пТ), являющийся ре"зультатом преобразования сигналовмногочастотного кода "2 из И" в цифровую Форму., напрймвр, с помощьюдельта-модуляции с инерционным ком 10 пандированием. На фиг.2 а условнопоказан сигнальный импульс многочас"тотного кода. Моменты постуйления отдельных отсчетов сигнала х(пТ) синх"ронни с тактовой частотой, выдаваемой ло первому тактовому выходу блока1 синхронизации.Входная цифровая последовательность х(пТ) разбивается на интервалыдлительностью Т (фиг.26), равные йпериодам Т частоты дискретизации;один интервал Т образует один циклобработки сигнала;: результат обработ-.ки Формируется .на выходе устройствак концу каждого цикла.Узкополосные согласовайные Фильт. ры 2-1 ". 2-И настроены на частоты,соответствующие И заданным. частотнымсоставляющим многоцастотного кода.Значения весовых коэффициентов согла 30.сованных Фильтров считываются с соот-.ветствующих выходов:постоянного запоминающего блока 4 синхронно с моментами поступлейия отсчетов х(пТ)входного сигнала. Сигналы начальнойустановки (в начале каждого цикла35 обработки длительностью Тц) и тактовая частота ИТ- подаются на согласованные фильтры.2-1 " 2-И от соответствующих тактовых выходов блока 1синхронизации,40 При использовании в качестве АЦПдельта-модуляции с инерционным ком"падированием и,квантовании весовыхкоэффициентов на два уровня согласованные фильтры строятся в соответст 4 вии с блок-схемой, приведенной нафиг.5.Устройство может использоватьсяи для обработки сигналов импульснокодовой модуляции, при этом могут50 быть использованы согласованныефильтры по блок-схеме, приведеннойна фиг.6. В этом случае сигнал х(пТ)и весовые коэффициенты представляют"ся не однобитными, а многоразрядны 5 ми кодовыми словами.По коротким импульсам 0 (Фиг,26), Формируемым на втором тактовомвыходе блока 1 синхронизации и сле дующим с периодом Тц = ИТ, осуществ7 , 1711292 , 81 ляется обнуление (сброс) согласован- мирователя 7 импульсов по переднему .ных фильтров 2-1 - 2-Н. фронту выходного сигнала 0 блока, 6На Фиг.2 в условно показан харак" фиксации числа срабатываний формитер изменения в течение. цикла Тц вы- руется короткий положительный имходных сигналов согласованных фильт.- 5 пульс(0,у, фиг.2 ж), устанавливающий Ров 2"1 2-2, 2-3,для случая,.когда, КБ-триггер 8 в единичное состояние в обрабатываемом сигнале, помимо .(сигнал 08,фиг.2 з); на инверсном выдвух полезных составляющих с частота", ходе КЫ-триггера 8 сигнал будет ра" ми Й, Г, присутствует третья ме- вен нулю. формирователь 7 импульсов шающая частота 1 8, Уровни .частотных . может быть построен, например, каксоставляющих удовлетворяют в данном показано на фиг.М, где 15 - элемент случае условию 010 )11 Велици . задержки (или интегрирующая цепочка) на Р порога срабатыванйя пороговых16 - инвертор, 17 - элемент И. Очеблоков 3-1 - 3-3 отмечена на фиг,2 в. видно, что единичный сигнал появит" Вблизи резонансных частот согласован- ся на выходах только тех элементов.15ных.фильтров характер нарастания их ИЛц-НЕ 5, вторые входы которых подвыходного сигнала близок к:линейному соединены к тем пороговым блокам 3, и случай, показанный пунктиром. на которые к моменту появления единицфиг.2 в, ведущий к необнаружению по" 2 р ного сигнала на выходе КБ-триггера лезной частотной составляющей, не- : 8 (О ,.Фиг,3 з) находились в несра-. возможен,. В моменты времени э- ботавшем состоянии. В тех же кана" будут выполнены условия срабатывания лах, где пороговые блоки сработали.(превышение порога выходными сигнала (в рассмотренном примере это пороми ц . согласованных Фильтров)- са- .говые блоки 3-1 3-2 первого и второФ:.25 ., ф ответственно в первом и ВТОРом:.частотго частотйых каналов), выходные .сиг ных каналах,. Выходнь 1 е сигналы, поРОго" налы элементов ИЛИ-НЕ 5 будут Равнывцх. блоков 3-1, 3-2 показаны на : нулю, Выходные сигналы элементов Фиг.2 г,д (сигналы 11.,0, сооТ ,:. ИЛИ"НЕ 5 воздействуют на входы запреветсфгвенно). : : та срабатывания соответствующих по"Если бы в устройстве отсутствова" , роговых блоков (запрет осуществляетла введенная защита от ложных сраба." ся подачей единичного сигнала). Если, .:тываний (как в прототипе), то в м" ., например, пороговые блоки 3 строят- .мент 1 сработал бы пороговый: блок. ся на базе цифровых компараторов,3-.3 и, поскольку Результат обрэбо- .запрет можно осуществить подачей едики Фиксируется в конце цикла (напРи 35 ничного сигнала с элемента ИЛИ-НЕ 5lмер, стробированием выходных сигна . 1 на место старшего разряда двоичноголов пороговых блоков:вблизи момента . числа, задающего порог срабатываниявремени .1), был бы зафиксировай . Р порогового блока 3. Например, еслиприем всех трех частот (ложное сра максимально возможное значение.ре"батывание на частоте З)4 зультата Р,.фильтрации равно Р =кВ предложенном устройстве .выход" И " 1.=2 - 1, то можно использовать .ные сигналы пороговых блоков 3-1(Е + 1) -разрядный компаратор и сое 3-И поступают на вход блока 6 Фикса- динить выход соответствующего эле-:ции числа срабатываний на. выходе мента ИЛИ-НЕ 5 с входом Ь + 1) "гоюкоторого появляется единичный сигнал разряда двоичного числа, определяю(06, Фиг.2 е) сразу же, как только. . щего порог Р. Наличие формирователячисло сработавших пороговых блоков 3 7 импульсов необходимо для того,станет равно двум. Блок 6 фиксации цтобы к моменту И ) поступления сигможет быть реализован, например, на нала "Сброс" на соответствующий входбазе постоянного запоминающего уст"К КЬ-триггера 8 (ет второго тактово.Щ". Ройства, адресные входы которого сое" го выхода блока 1 синхронизации) надинены с выходами пороговых блоков его входе В установки в единицу так 3 и которое программируется так, что же не присутствовал единичный сир"единице записывается только в те нал, поскольку одновременная подачаячейки, адреса которых содержат толь. активных уровней сигнала на входыко две единицы (на любых позициях) КЬ"триггера не допускается. В сооти нули, например, при и 6 этому усло ветствии с приведенным описаниемвию удовлетворяют адреса 001010, очевидно, что в данном устройстве110000, 100001 и т.д, С помощью Фор- обеспечивается прием только двух5 10 рых соединены с сигнальными входами соответствующих пороговых блоков, выходы которых являются выходами приемника, входом. которого являются25 информационные входы согласованных циентов которых подключены соответствующие адресные выходы постоянного, запоминающего блока, адресные входы ЗО которого соединейы с адресными выходами блока сикхройизации, о т л.и"ч а ю щ и й с я тем, что, с цельюповышения помехозащищенности прием"ника, введены элементы. ИЛИ-НЕ ипоследовательносоединенные блок входам которого подключены выходы . пороговых блоков,Формирователь импульсов и КЪ-триггер, инверсный вы" ход которого подключен к первым вхо" фО дам элементов ИЛИ-НЕ, вторые .входыкоторых соединены с выходами соответствующих пороговых блоков, при этом соответствуюЩий, тактовый вйход блока синхронизации подключен к втоф 5 рому установочному входу КЗ-триггера,а выходы, элементов ИЛИ-НЕ соединены с запрещающими входами соответствую 1,9 - 174частотных составляющих, имеющих максимальный уровень, и устраняютсяложные срабатывания на остальных час"тотах, то есть повышается помехоза"щищенность, устройства.В заключение следует остановитьсяна способе построения блока 1 синхро-.низации, блок-схема котороо приве,дена на фиг,3 и содержит тактовый генератор 9, Формирующий частоту Ьо спериодом Т = 1 , равным периодудискретизации обрабатываемого сигнала, инверторы 11 - 12, 1 с"разрядный(1 с =.1 оЗ Б , гдеа" минимальноецелое, большее а) делитель 10, дифференцирующее.звено 13 и элемент 14задержки. При Н = 2. на адресные входы постоянного запоминающего блока 4подаются выходные сигналы всех 4 сразрядов делителя 10, при этом заодин цикл ВТ обработки перебирается .Я значений адреса, и к началу следующего цикла делитель 1.0 автомати"чески возвращается в исходное .нуле-:вое состояние. При М ф 2 выход де."лителя 10 нужно соединить с его входом установки нуля через дешифратор,фиксирующий появление числа М навыходе делителя 10. С помощью элемен. та 14 .задержки формируется сигнал :У,т (фйг;2 б), слегка задержанный от"носительно переднего Фронта инверсиичастоты йв/2 " с К-го разряда делите.".ля 10 (имеется в виду, что делитель10 последовательно принимает состояния Офф 001 Офф 01 у Оф ф е 10е еОеф 11), благодаря чему в конце циклов,обработки (моменты 1, 1 на фиг.2 г)при необходимости возможно стробирование выходных сигналов пороговых. блоков 5 непосредственно переднимФронтом инверсии частоты Й /2 , напри".кмер, с помощью 0-триггеров (на фиг. 1не доказаны).В соответствии с приведенным вышеописанием технико-экономическая эфФективность предлагаемого устройствапа сравнению с прототипом заключается 1292 10 в повышении защищенности от ложных срабатываний, в частности от сраба" тцваний на и частотах при и ф 2.Положительный эффект достигается тем, что срабатывание фиксируется только в тех двух частотных каналах, в которых уровень профильтрованного сигнала максимален, при этом в каждом цикле обработки формируется специальный сигнал, запрещающий срабатывание во всех остальных частотных каналах. Формула изобретенияЦифровой приемник сигналов многочастотного кода, содержащий блок синхронизации, тактовые выходы ко" торого подключены к тактовым входам согласованных фильтров, выходы кото" фильтров, к входам .весовых коэффификсации количества срабатываний,.к щих пороговых блоков.17 И 292 Х(о Т) и, Й з Рйг.Л к щарсрьойн Ьруам ЖФФасоРа кмью йод)оо Ф сф уесмьило ам lдюжую 1 оФЛрииФОЮРМфсЬока Д1741292 д кадишь Кко от лба иды д Фаюав Зарока 3Щсг. 5от 1 еооога МаьпобомЙгкооа опьк 01 вп пегого Фдкльбою 1 ыхоо Едока 1 офйночо пока фамя

СмотретьЗаявка

4765084, 30.11.1989

ЦЕНТРАЛЬНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ СВЯЗИ

ОХЛОБЫСТИН ЮРИЙ ОЛЕГОВИЧ

МПК / Метки

МПК: H04Q 1/44

Метки: кода, многочастотного, приемник, сигналов, цифровой

Опубликовано: 15.06.1992

Код ссылки

<a href="https://patents.su/7-1741292-cifrovojj-priemnik-signalov-mnogochastotnogo-koda.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой приемник сигналов многочастотного кода</a>

Предыдущий патент: Устройство передачи команд управления по речевому запросу

Следующий патент: Электрический чайник

Случайный патент: Шахтная опора