Устройство для кодирования сигналов изображения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

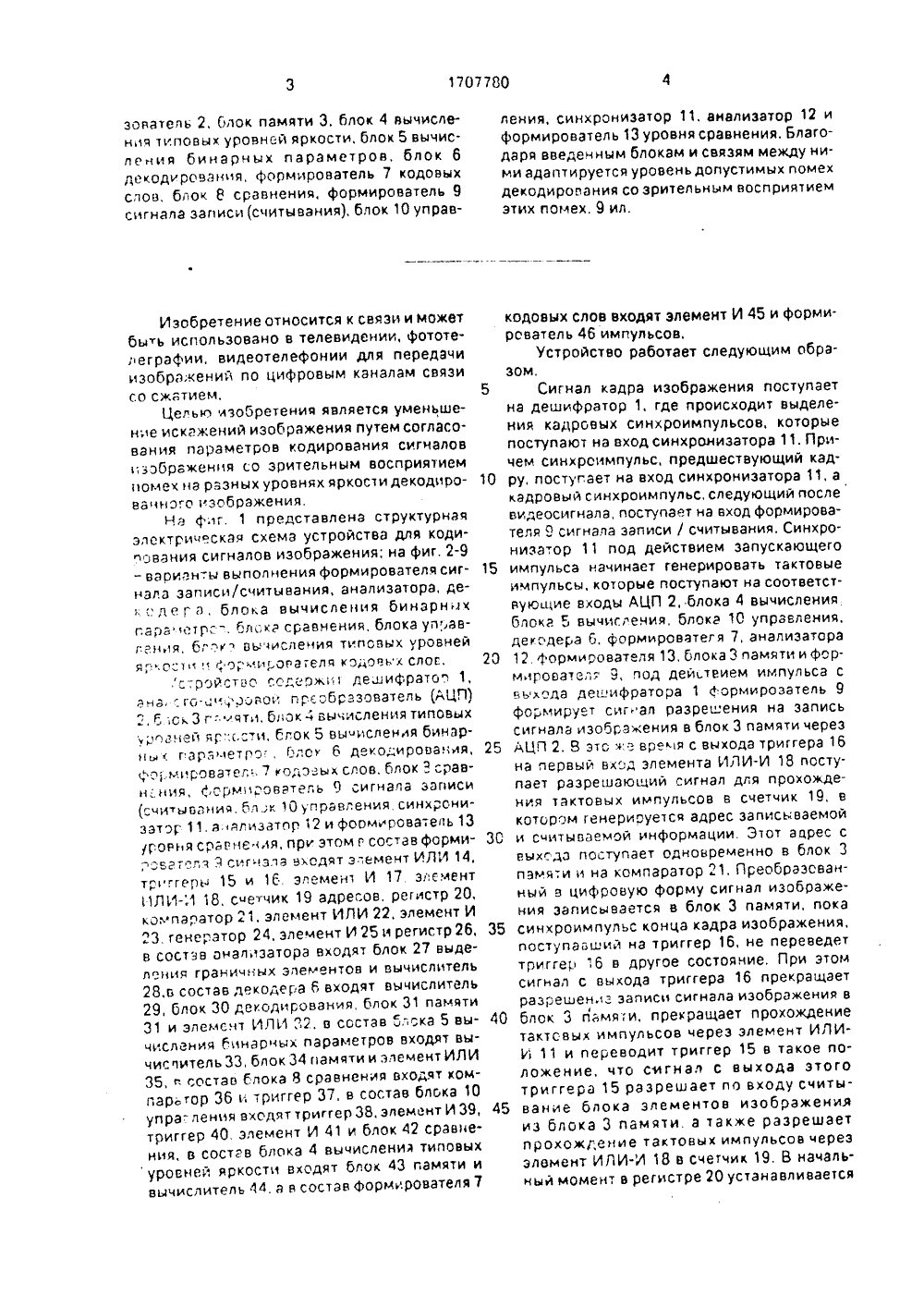

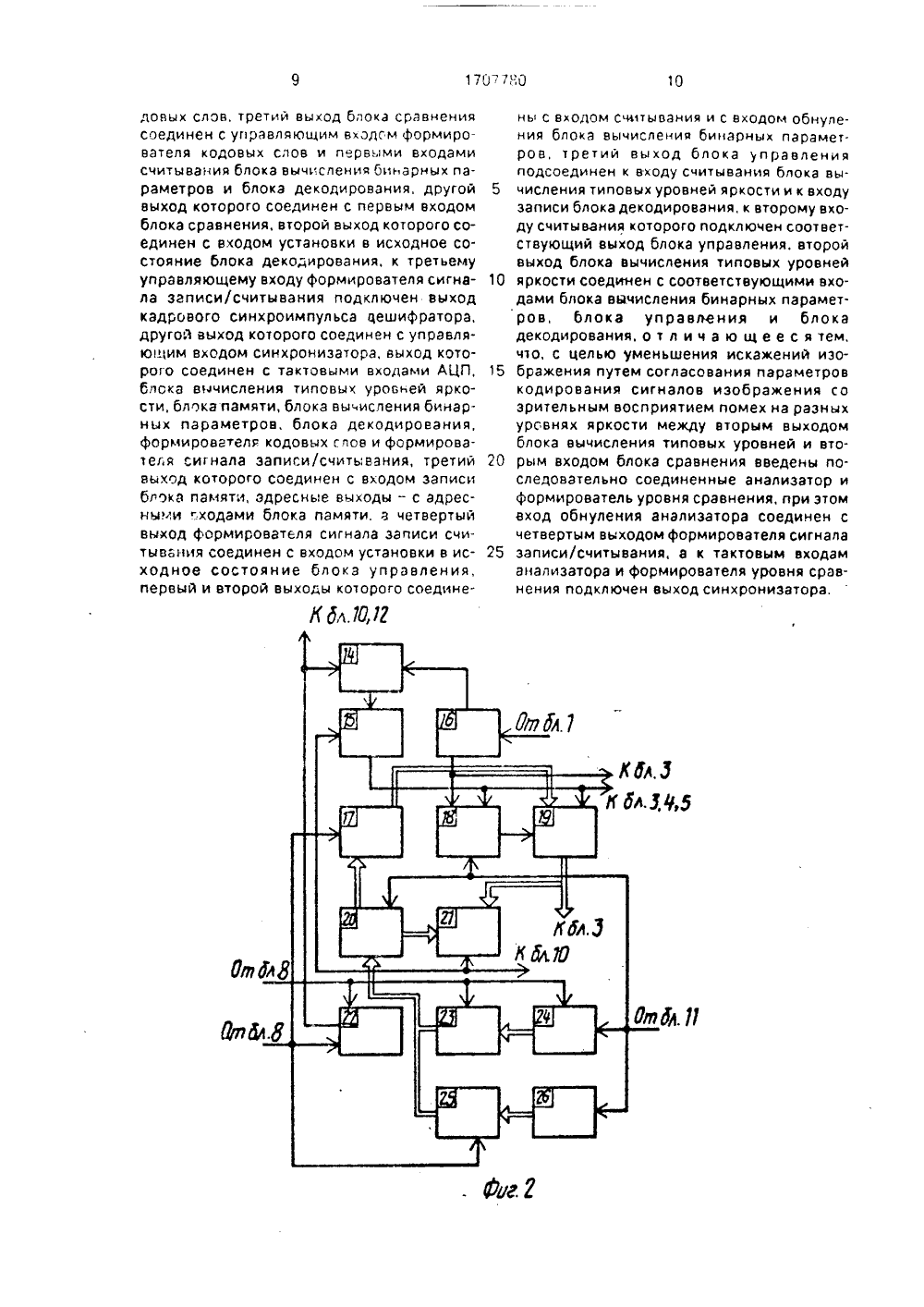

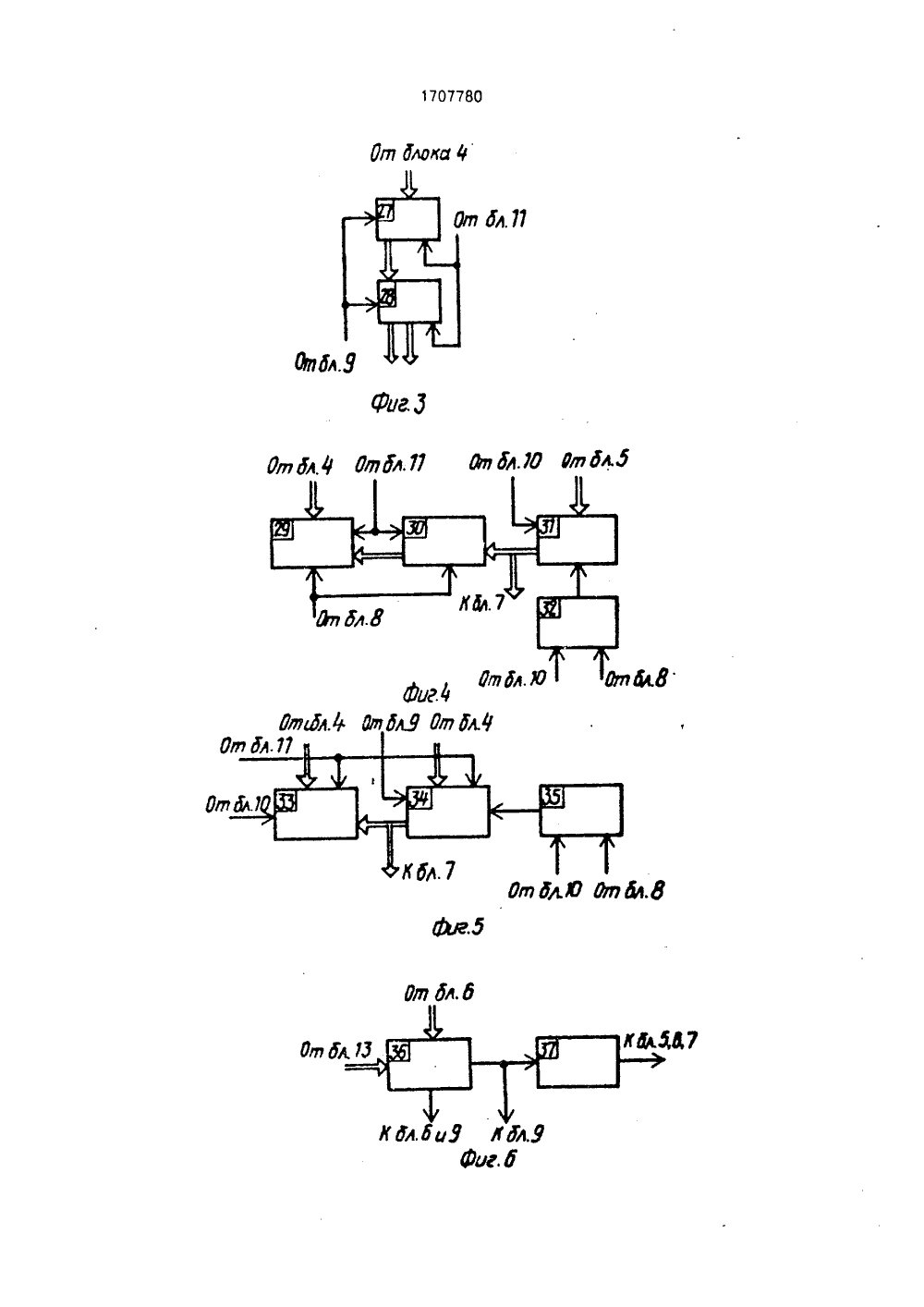

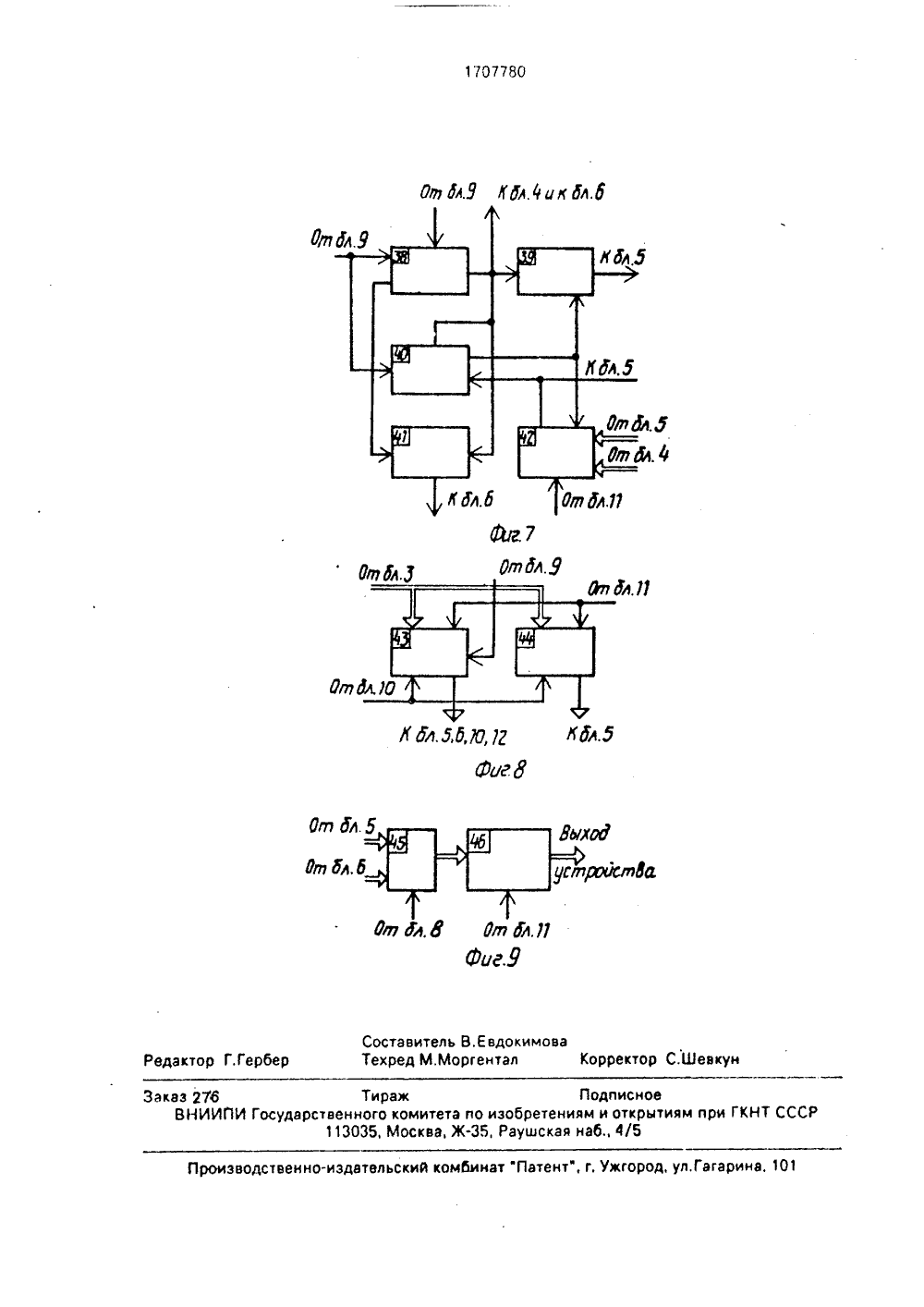

(515 Н 04 й 7/12 ЕНИЯ К А иационного и Г.У.РафиИРОВАНИЯ 4 ГОСУДАгСТБЕ)+4 Ый КОМИТЕТПО ИЗОБфЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР ПИСАНИЕ ИЗОБ СКОМУ СВИДЕТЕЛЪСТВ(54) УСТРОЙСТВО ДЛЯ КОСИГНАЛОВ ИЭОБРАЖБ НИЯ 1707780 А 1(571 Изобретение относится к связи и может быть использовано в телевидении. фотографии, видеотелефонии для передачи изображений по цифровым линиям связи со сжатием. Цель изобретения - уменьшение искажений изображения путем согласования параметров кодирования сигналов иэображения со зрительным восприятием помех на разных уровнях яркости декодированного изображения, Устройство для кодирования сигналов изображения содержит дешифратор 1, аналого-цифровой преобра1707780 зователь 2, блок памяти Э, блок 4 вычисления типовых уровнсй яркости, блок 5 вычисления бинарных параметров, блок 6 декодирования, формирователь 7 кодовых слов, блок 8 сравнения, формирователь 9 сигнала записи (считывания), блок 10 управИзобретение относится к связи и можетбысть использовано в телевидении, фототееграфии, видеотелефонии для передачиизображений по цифровым каналам связисо сжатием,целью изобретения является уменьшение искажений изображения путем согласования параметров кодирования сигналовизображения со зрительным восприятиемпомех на разных уровнях яркости декодированнсгс 1 зсбражения.На фиг. 1 представлена структурнаяэлектрическая схема устройства для кодипсвания сигналов иэображения; на фиг. 2-9- варианты выполнения формирователя сигнала записи/считывания, анализатора, дел. с л е г а, блока вычисления бинарныхгара 1 етр:-, блока сравнения, блока уп авления, баск вычисления типовых уровнейя,сс 11.1с; "и от ателя ксдавь х слос.,с-,рсйствс сод;см 1 дешифратсс 1,ача, . гс-ц;,рсвси преобразователь (АЦП)Г, б;ск 3 г чти, блок 4 вычисления типовыхпаней яр тости, блок 5 выцисленля бинарн с г арак 1 етгс баск 6 декодирования,фс. мирсвдтел 7 кодовых слов, блок срдвн=ния, гсрмп;сватель 9 сигнала записи(считывания, бл.зк 10 управления синхрсниэатср 11. а ллизатср 12 и фссмрсватель 13рорня сраане гия, при этом г состав форми;свгтслч 9 сигнала входят эгемент ИЛИ 14,т,1 ггеры 15 и 16 элемент И 17 элемент11 ЛИ-;1 18, сцетчик 19 адресов, регистр 20,ксмпаратор 21, элемент ИЛИ 22, элемент И23, генератор 24, элемент И 25 и регистр 26,в состав анализатора входят блок 27 выделения граничных элел ентсв и вычислитель28 в состав декодера 6 входят вычислитель29, блок 30 декодирования, блок 31 памяти31 и элемент ИЛИ 32, в состав блока 5 вычисления бинарных парал 1 етров входят вычислительь 33, блок 34 памяти и элемент ИЛИ35,состав блока 8 сравнения входят комгар тор 36 и триггер 37, в состав блока 10упра- ления входят триггер 38, элемент И 39,триггер 40. элемент И 41 и блок 42 сравнения, в состав блока 4 вычисления типовыхуровней яркости входят блок 43 гамяти ивычислитель 14, а в состав формирователя 7 ления, синхронизатор 11, анализатор 12 и формирователь 13 уровня сравнения, Благодаря введенным блокам и связям между ними адаптируется уровень допустимых помех декодирования со зрительным восприятием этих помех. 9 ил. кодовых слов входят элемент И 45 и формирователь 46 импульсов.устройство работает следующим образом,Сигнал кадра изображения поступает на дешифратор 1, где происходит выделения кадровых синхроимпульсов, которые поступают на вход синхронизатора 11. Причем синхрсимпульс, предшествующий кадру, постугает на вход синхронизатора 11, а кадровый синхроимпульс, следующий после видеосигнала, поступает на вход формирователя 9 сигнала записи / считывания, Синхронизатор 11 под действием запускающего импульса начинает генерировать тактовые импульсы, которые поступают на соответствующие входы АЦП 2, блока 4 вычисления блока 5 вычиг,"ения, блока 10 управления. декодера б, фсрмировэтегя 7, анализатора 12 Формирователя 13, блока 3 памяти и фсрм 1 рсвател; 9, под действием импульса с вьлсда дешифратора 1 срмирозатель 9 формирует сиг" ал разрешения на запись сигнала изображения в блок 3 памяти через АЦП 2, В этс явремя с выхода триггера 16 на первый вход элемента ИЛИ-И 18 поступает разрешающий сигнал для прохождения тактовых импульсов в счетчик 19, в котором генерируется адрес записываемой и считываемой информации, Зтст адрес с еыхсдз поступает одновременно в блок 3 памяти и на компаратор 21. Преобразсванный в цифровую форму сигнал изображения записывается в блок 3 памяти, пока синхроимпульс конца кадра иэображения, поступавший на триггер 16, не переведет триггер 16 в другое состояние, При этом сигнал с выхода триггера 16 прекращает разрешен,;:- записи сигнала изображения в блок 3 памяти, прекращает прохождение тактсвых импульсов через элемент ИЛИИ 11 и переводит триггер 15 в такое положение, что сигнал с выхода этого триггера 15 разрешает по входу считывание блока элементов иэображения из блока 3 памяти, а также разрешает прохождение тактовых импульсов через элемент ИЛИ-И 18 в счетчик 19. В начальный момент в регистре 20 устанавливается 5 10 15 2025 30 35 40 45адрес конечного элемента блока элементов иэображения. В результате работы счетчика 19 адреса вырабатываемый адрес подается как в блок 3 памяти, так и на сход первого компаратора 21, на второй вход которого поступает конечный адрес блока элементов сигнала иэображения. При совпадении адресов в первом компараторе 21 на его выходе вырабатывается сигнал, который, поступая на входы триггера 38, блока 10 управления и триггера 15, переводит их другие состояния, Триггер 15 переходит в такое состояние, что запрещается прохождение тактовых импульсов через элемент ИЛИ-И18 в счетч, к 19, а также запрещается описывание элементов блока изображения иэ блока 3 памяти, Одновременно с разрешением считывания блока элементов изображения блока 3 памяти, сигнал разрешения с выхода триггера 15 поступает ча второй вход блока 43 г амяти и на второй вход блока 34 памяти, оазрешая запись сигнала в эти блоки.Считыьаемый блок элементов изображения блока 3 памяти поступает одновременно в блок 43 памяти и блок 4 вычисления, вычислитель 44, в котором рассчитываются параметры блока элементов изображения среднее значение яркости Во и типовые градационные уровни В 1 и Р;, которые записываются во блок 34 памяти. При выработке сигчала на выходе компаратора 21, т.е, в момент совпадения адреса считываемого блока элементов изображения и адреса конечного элемента слака элементов иэображения, тоиггер 38 под действием конечного элемента блока элементов изображения под дейст вием сигнала с выхода компаратораерохе ит в а се состоя чре что си - нал с его выхода обнуляет вычислитель 44 и рэзрешае считывание элементов блока элементов иэображения иэ блока 43 памяти и рассчитанных параметров блока элементов изображения из блока 34 памяти, При этом разрешение на счи 1,вание информации проходит через элемент И 39 с триггера 40 блока 10 управления информация, поступающая на вход вычислителя 33(иэ блока 43 . памяти и блока 34 .памяти), используется для вычисления бинарных параметров блока элементов иэображения, исходя из соотношенийГ, =Г 1 при ХцВо0 при ХК Во,где Хц - начение текущего элемента блока; Ц-чомера строк и столбцов при двумерном блоке элементов.Одновременно с разрешением считывания информации с блоков 43 и 34 памяти этот же сигнал с выхода триггера 38, поступая на второй вход блока 31 памяти, разрешает запись рассчитанных бинарных пара.метров в блок 31 памяти, Одновременно сигнал блока элементов иэображения счи.тывается из блока 43 памяти в блок 42 срае.нения и в блок 27 выделения граничных элементов, Блок 43 сравнения фиксирует момент окончания обработки блока элемен.ов иэображения, выдавая по выходу(блока .- 42 сравнения) сигнал, переводящий триггер40 в другое состояние и обнуляющий вычислитель 33, Сигнал, выработанный триггером 40, поступая с его первого выхода на вход блока 42 сравнения, обнуляет его и одновре менно поступая на элемент И 39, запрещает прохождение управляющего сигнала через этот элемент И 39. В это же время сигнал с второго выхода триггера 40 являетгя;азрешающим для прохождения через -С элемент И 39 сигнала разрешения списывания параметров кодированного сигнала изображения из блока 31 памяти, Этот сигнал считывается в блок 30 декодирования, где производится восстачовление элементов обработанного блока элементов иэображения, Считанная из блока 31 памяти информация используется для декодирования блока элементов изображения согласно алгоритма, задаваемого формулой)0 У 1 = ГВ 2 + Р)В 2где У - значение декодированных элементов. Под действием синхроимпульсов деко.дированные элементы поступают на первый вход вычислителя 29 нг третий вход которо, го поступают элементы исходного блока,сформированного в блоке 43 памяти. Алгоритм работы вычислителя 29, о", ределяющегс ошибку декодирор э,.я имеет вид 40, д = У - Х) Вычисленная ошибка поступает на первый вход компаратора 36 блока Р сравнения. На второй вход компаратора 36 поступает сигнал порога сравнения, который формируется следующим образом.45 Сформированный блок элементов изображения с выхода блока 43 памяти. списывается в блок 27 выделения граничных элементов. Сигнал выделенных элементов, находящихся на границе блока (де в основ ном сосредоточены неправильно декодиро.ванные элементы), поступает на первый вход вычислителя 28, который реализован на процессоре ЭВМ "Электроника 60". В этом вычислителе 28 рассчитывается рас пределение яркости элементов границысформированного блока путем определения числа элементов, попавших в область яркости: белое и черное, серое. Вычисленные значсния элементов, в виде сигналов с выходов вычислителя 28, подаются на входы Формирователя 13 уровня сравнения, в ко 1707780ТОРОМ 1 С 1 рМИруЕТСя СИГНаЛ, ПрОПСгрцИО- ггпьньгй отношению числа;пел 1 ентов, оыделснных а границе, гринадлежащих области "сер г о" относительно области "белое и черное". При л 1 еньшем числе элгементое, принадлежащих области "серое" в коестес уродя сравнения берется отношение значений величин, попавших е областьоое" и область "белое и чгрное", В г;ротг оном случае бг" атся величина с 1 боатная ДСгогОГН 11 ТЕЛЬг 1 СЛ 1 У КОДУ, СфОРМИРОВгННЫй - пап Гироеаггный уровег 1 ь порог) сравнения пс 1 да " второй входкомпгратора Зб, на псьгьгй вход к,., -. ггодается величина оши.1 к:1 декодироогчия сфорл ванного в с оке 43 памяти блока элег 1 ентое изображеНИя, ЕСЛИ ВЕГИЧИНа ОШИбКИ дЕКОдг 1 рОваИя не превышает порога сраеения, учитывают,его зрительное ессприятие искаженных элементов бп ка, тогда с первого выхода компгратор Зб поступает сигнал на вход триггера 37, которьгс 1 вьграбгтьгегет сигнал, разрешаюьц,ли прохождение инф. рл 1 гционногс сигнала через блок элементов И 45, Этот же сигнал с первого выхода компаратора 36 разрешает описывание рассчитанных пар:метрсо из блоксе 34 и 31 памяти, ,1 ти и,",зм.ь кздирг,ьания через блок эле- Л Егт.-е 1 4 З, Срвда ОТСя Е фО"МИргватЛЬ, ПЕ.ЕТЗСГЮЩ;1 й С; ЗИ 1 РЕГИСТ Р ДЕИга, 13 КС СО;ГО Г".Д Дг.гстсгГ 1.1 ТаКТГ 1 р,Гэгцг 1 Х иП у Г Ь С, О Е С ф; ф. г:,1 р О С г Н г 1 Ы г С И 1 г 3 Гг Г С С Т у Г 1 а С. Т Я КгЧгД СГЯЗИ. ОДНОЕРЕГ.: ННО Сг 1 ГНал С ПЕРЗГ, Ег,ХГ :; КОМПгРаТСРг 3.;1 ССТ .гаЕТ На:-О ЗЛЕг: .О- Л ."1, гга Г;,:грг Гар , На .ь.зпел 1 снт.а И 17, Е регул:та е работы "-,;". слог,о рззс сь, сто;, с 11 сд:гчг : Начальгэ гд;,са спе;ующе с а эл:л.:ноа изобр.:жегик Глс а 3 сг 1 ати, Это гг "с 1 зеод;тсь бпагсгрг ра решгюссгему сигнал Г дестоующеп в:.оду блэка эле- М:НТ; В И 17, раэрвгьггц ц Е 1 Х СОКОждЕНИЕ ПРЕДЫДШ ГО ЗаЕНИЯ аДРЕСа ИЗ РЕ ИСТРа 20 г, счетчик 19. Предыдущий конечный адрес, блока элементов изображения становится нацальныгл гдресом нового блока элементов и;:обргжгния, Из генготара 24 чеоеэ ",пог элементов И 23 в регистр 20 Зас Сг.,гоаотса ЛОда й адрЕС НОВОГО бЛОКа элементов 1 з;Ер. жения. Этот же сигнал с первого выхода компарзторг 36, поступающи. чес гэ элементы ИЛИ 22 и 14 перееодлт 1 рг дер 15 о такое состояние, что разрешастся подача тактовых ил 1 пупьсов через злелен 1",ЛИ-И 18 в счетчик 19 и,"азрешается спис гвапне очередного блока элементов иэображения из блска 3 памаи, Сигнал с сыхода элемента ИЛИ 22, поступая на входы триггеров 38 и 40, пгрееодит их в исходное состояние, г сигнал, пос-упающий на 5 10 15 20 25 30 л 40 45 50 55 вход блока 27 выделения граничных элементов и вычислителя 28, обнуляет эти блоки и приводит их в исходное состояние. после чего работа устройства повторяется до тех пор, пока не будут сформированы параметры кодирования последнего блока элементов, В случае же невыполнения условий сравнений в компараторе 36, сигнал с второго выхода компаратора 36 через элемент ИЛИ 22, поступая на вход триггера 15, переводит его в такое состояние, что разрешается прохождение тактовых импульсов через элемент ИЛИ-И 18 в счетчик 19. а поступая на третий вход блока 3 памяти, разрешает считывание иэ этого блока информации. Сигнал же, поступающий на блок элементов И 17, не разрешает считывание начального адреса в счетчик 19, который остается прежним для блока элементов изображения. Конечный адрес этого же блока элементов перестраивается в пределах. регулируемых регистром 26. При невыполнении условий сравнения на блок элементов И 25 поступает разрешающий сигнал и с регистра 26 скорректированный конечный адрес блока алел" ентов иэображения в регистр 20, Поэтому списывание блока начинается с прежнего адреса блока. а окончание формирования б, ока - по конечному скорректировгчному адресу, сформированному в гегистр. 20, Регистр 26 осуществляет корректировку конечного адреса блока по псе вдослучг й ному закону. Период псевдослайости выбран очень большим путем выбора соответствующего числа ячеек регистра 26 сдвига, что обеспечивает многокр "тную пеоестройку конечного адресаблока. Формула изобретения Устройство для кодирования сигналов изображения, содержащее последовательно соединенные дешифратор, аналого-цифровой преобразователь (АЦП), блок памяти, блок вычисления типовых уровней яркости, блок вычисления бинарных параметров, декодер и формирователь кодовых слое, а также блок сравнения, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами формирователя сигнала записи/считывания, первый выход которого соединен с первым упраоляюшим входол блока управления, второй выход формирователя сигнала записи/считывания соединен с входом считывания блока памяти и с входами записи блока вычисления типовых уровней яркости и блока вычисления бинарных параметров, второй выход которого соединен с соответствующим входом формирователя ко 170 7 КО 1 Одовых слов, третий выход блока сравнения соединен с управляющим вхэдсм формирователя кодовых слов и первыми входами считывания блока вычисления бинарных параметров и блока декодирования, другой выход которого соединен с первым входом блока сравнения. второй выход которого соединен с входом установки е исходное состояние блока декодирования. к третьему управляющему входу формирователя сигнала записи/считывания подключен выход кадрового синхроимпульса цешифратора, другой выход которого соединен с управляющим входом синхронизатора, выход которого соединен с тактовыми входал 1 и АцП, блока вычисления типовых уровней яркости, блока памяти, блока вычисления бинарных параметров, блока декодирования, формирователя кодовых слов и формирователя сигнала записи/считывания, третий выход которого соединен с входом записи блока памяти, адресные выходы - с адресными ходами блока памяти, а четвертый выход формирователя сигнала записи считывания соединен с входом установки в исходное состояние блока управления, первый и второй выходы которого соединень с входом считывания и с входол 1 обнуления блока вычисления бинарных параметров, третий выход блока управления подсоединен к входу считывания блока вы числения типовых уровней яркости и к входузаписи блока декодирования, к второму входу считывания которого подключен соответствующий выход блока управления. второй выход блока вычисления типовых уровней 10 яркости соединен с соответствующими входами блока вычисления бинарных параметров, блока управления и блока декодирования, о т л и ч а ю щ е е с я тем.что, с целью уменьшения искажений иэо бражения путем согласования параметровкодирования сигналов изображения со зрительным восприятием помех на разных урсвнях яркости между вторым выходом блока вычисления типовых уровней и вто рым входом блока сравнения введены последовательно соединенные анализатор и формирователь уровня сравнения, при этом вход обнуления анализатора соединен с четвертым выходом формирователя сигнала 25 записи/считывания, а к тактовым входаманализатора и формирователя уровня сравнения подключен выход синхронизатора,1707780 Ркп длока ФОт РлЮ Юл, ЕиЯ РЖФжд.В Составитель В.Е вдокимоваедактор Г.Гербер Техред М,Моргентал Корректор С.Шев аказ 2 гб Тираж Подписное ВНИИЙИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5 л.Гагарина, 10 Производственно-издательский комбинат "Патент", г, Уж

СмотретьЗаявка

4725375, 26.07.1989

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

АРЯМКИН ВЛАДИМИР МАТВЕЕВИЧ, БАБЕНКО ЕКАТЕРИНА АЛЕКСАНДРОВНА, РАФИКОВ ГЕННАДИЙ МУГАЖИРОВИЧ

МПК / Метки

МПК: H04N 7/12

Метки: изображения, кодирования, сигналов

Опубликовано: 23.01.1992

Код ссылки

<a href="https://patents.su/7-1707780-ustrojjstvo-dlya-kodirovaniya-signalov-izobrazheniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования сигналов изображения</a>

Предыдущий патент: Устройство автономной двухабонентной телефонной связи

Следующий патент: Способ изготовления пластинчатого электронагревателя

Случайный патент: 190251