Устройство для программного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1667005

Автор: Омельченко

Текст

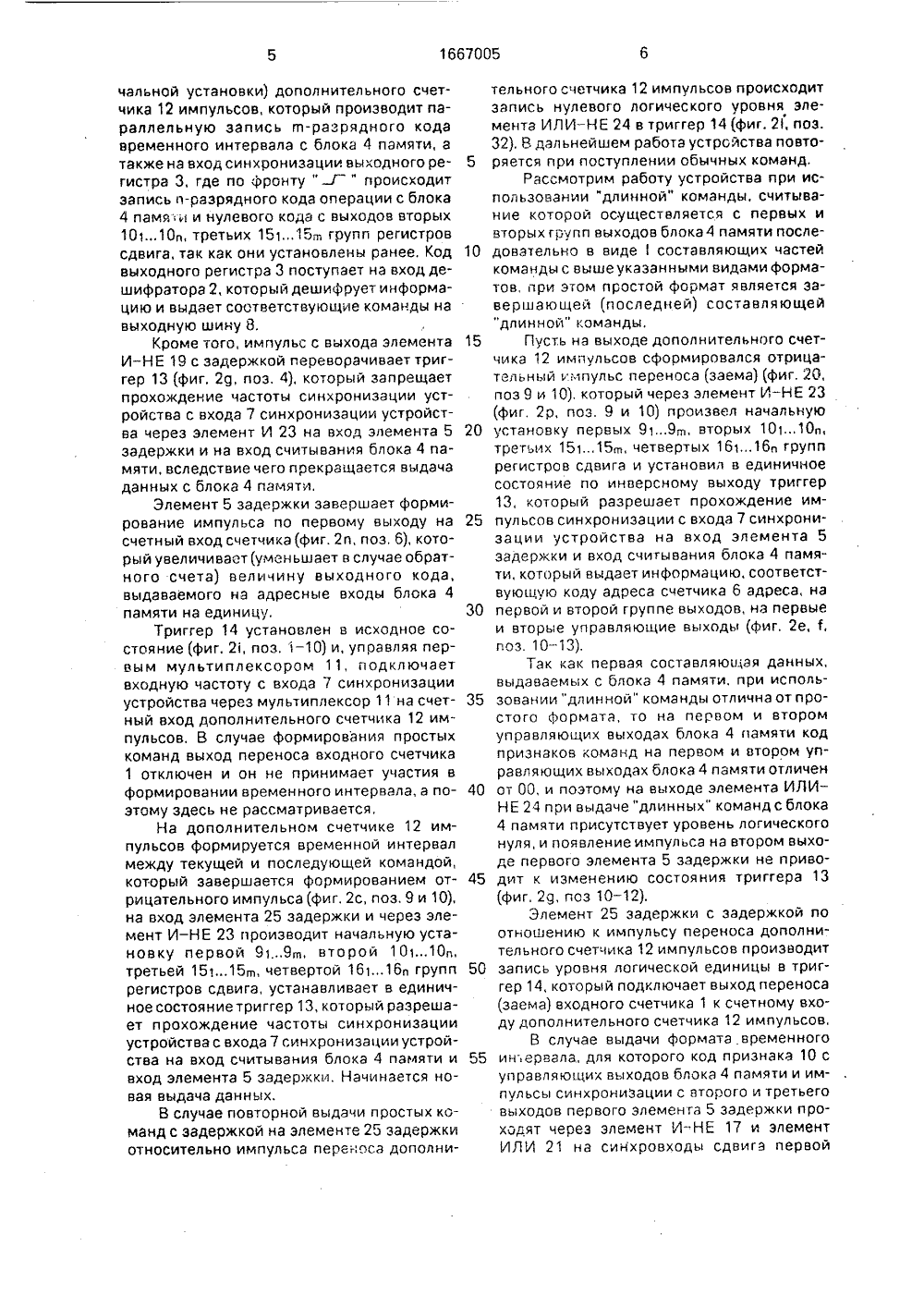

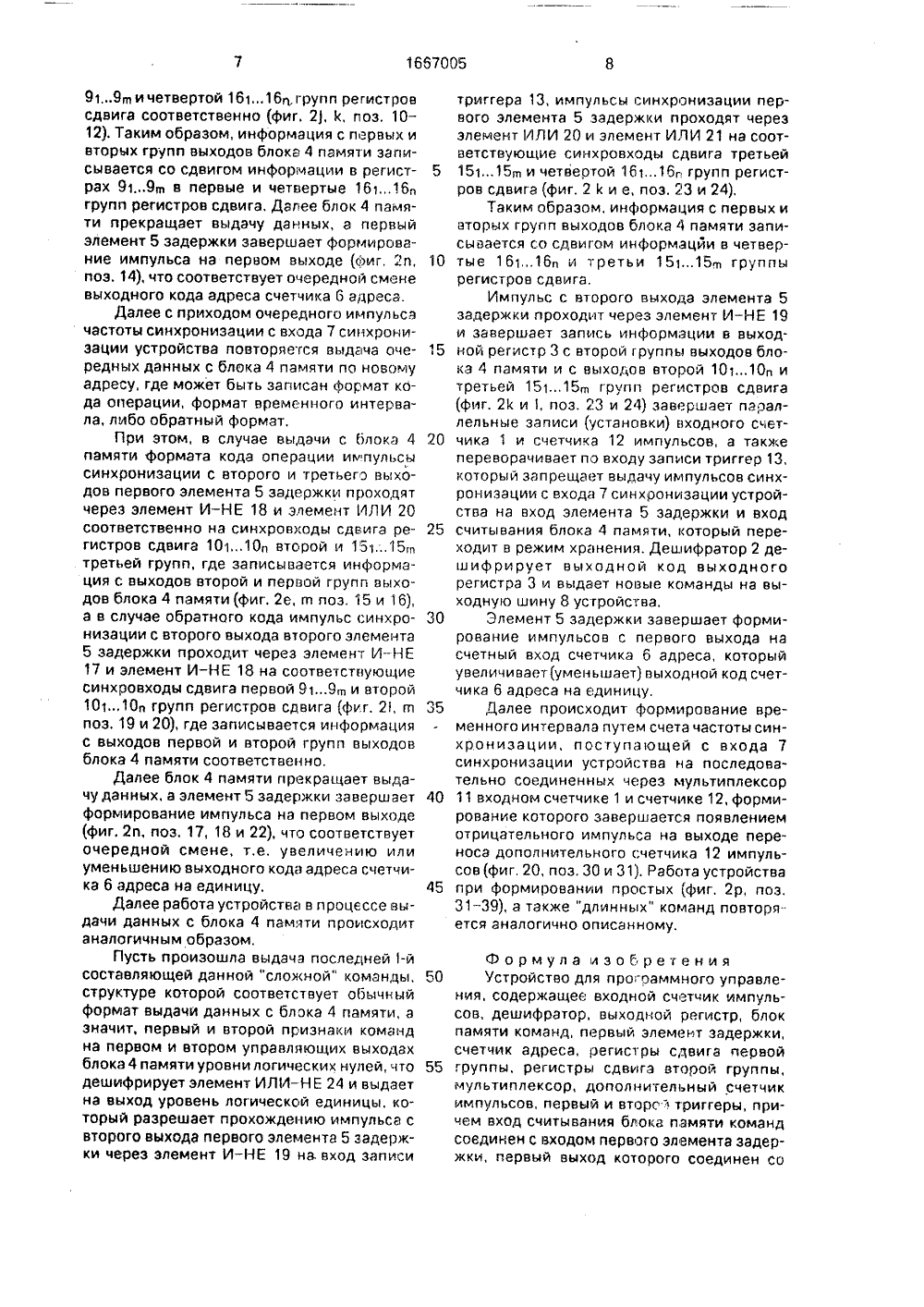

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 667005 А 9 у В 19 1 Й КОМИТЕТМ И ОТКРЫТИЯМ ГОСУДАРСТВЕННПО ИЗОБРЕТЕНПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИ АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(57) Изобретение относитстехнике и может быть испоройствах автоматики и вычиники. Целью изобрете ГРАММНОГО к импульснои ьзовано в устлительной техия является аааЪ(56) Авторское свидетельство СССРМ 1252759, кл. 6 05 В 19/18, 1985.Авторское свидетельство СССРМ 1569804, кл, 6 05 В 19/18, 1988,Устроиство для программного управления относится к автоматике и вычислительной технике и может быть использовано в качестве устройства управления системами в реальном масштабе времени.Целью изобретения является экономия объема памяти устройства за счет уменьшения части объема избыточной информации путем введения дополнительных форматов с независимой выдачей кода временного интервала и кода операции с блока памяти при формировании "длинных" команд.На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы работы.Устройство для программного управления содержит входной счетчик 1 импульсов, дешифратор 2, выходной регистр 3, блок 4 памяти команд, первый элемент 5 задержки, счетчик 6 адреса, вход 7 синхронизации экономия объема памяти устройства за счет уменьшения части объема избыточной информации путем введения дополнительных форматов с независимой выдачей кода временного интервала и кода операции с блока памяти при формировании "длинных" команд. Устройство содержит входной счетчик, дешифратор, выходной регистр, блок памяти, элемент задержки, счетчик адреса, вход синхронизации устройства, щ регистров сдвига первой группы, и регистров сдвига второй группы, мультиплексор, дополнительный счетчик импульсов, два триггера, щ регистров сдвига третьей группы, и регистров сдвига четвертой группы, элементы И - НЕ, ИЛИ; И, ИЛИ - НЕ. 2 ил. устройства, выходная шина 8, в регистров сдвига 989 п 1 первой группы, и регистров сдвига 101".10 П второй группы, мультиплексор 11, дополнительный счетчик 12 импульсов, первый 13 и второй 14 триггеры,. е регистров сдвига 151,15 П третьей группы, и регистров сдвига 16 ъ 16 п четвертой группы, первый 17, второй 18 и третий 19 элементы И - НЕ, первый 20, второй 21 элементы ИЛИ, элемент И 22, четвертый элемент И - НЕ 23, элемент ИЛИ-НЕ 24, второй элемент 25 задержки, вход 26 установки устройства.Устройство для программного управления работает следующим образом,На фиг, 2 показан пример возможных временных диаграмм работы устройства, где а - вход 26 установки устройства; Ь - вход 7 синхронизации устройства; с - второй выход элемента 5 задержки (каскадноесоединениеодновибраторов);О -третий выход элемента 5 задержки (саскадное соединение одновибраторав); е - первый управляющий выход блока 4 памяти команд; 1 - второй управляющий выход блока 4 памяти команд; 9 - выход триггера 13; и - выходэлемента И-НЕ 19;- выходтриТера 14; ) - выход элемента И-НЕ 17; 1 с - выход элемента ИЛИ 21; - выход элемента ИЛИ 20; а - выход элемента И-НЕ 18; и - первый выход первого элемента 5 задержки; о - выход переноса (заема) дополнительного счетчика 12 импульсов; р - выход элемента И - НЕ 23.На временных диаграммах показаны 39 позиций, которым соответствуют изменения режимов работы устройства.На вход 26 установки устройства подается инверсный импульс, показанный на фиг. 2 а, поз. 1, который устанавливает счетчик 6 адреса, второй триггер 14 и через элемент И - НЕ 23 устанавливает в единичное состояние по инверсному выходу триггер 13, сбрасывает первую 919 пь вторую 10110, третью 1515 сп. че-вертую 16116 п группы регистров сдвига.На вход устройства поступает частота синхронизации устройства, показанная на фиг. 2 Ь, поз, 2 и 3, которая, благодаря установке первого триггера 13 (фиг, 2 б, поз, 1 и 2) поступает через элемент И 22 на вход разрешения выдачи данных блока 4 памяти команд и вход элемента 5 задеркки, Происходит выдача данных с блока 4 памяти команд по адресу, задаваемому счетчиком 6 адреса, с активным состоянием на информационных выходах (ранее блок 4 памяти команд находится в режиме хранения информации по первой и второй инфэрмационным группам выходов, а также первому и второму управляющим вцсодам блока 4 памяти мог находиться в высокоимпедансном третьем состоянии, что позволяет экономить энергию, потребляемую устройством в интервалах между выдачами), чему соответствует фиг. 2 е, 1, поз, 2-5, Третье со:тоя ние показано на временных диаграммах нтриховкой вида ХХХ.Выходные (щ + и + 2) - разрядные данные блока 4 памяти разбиты на первьй управляющий выход, второй управляющий выход, первую гп-разрядную группу выходов, вторую и-разрядную группу выходов,В зависимости от кода двухразрядного признака формата на первом и втором управляющих выходах соответственно различают четыре вида формата выдачи данных с блока 4 памяти команд, Формат блока 4 памяти с нулевыми логическими признаками формата на управляющих выходах назы 10 15 20 25 30 35 40 45 50 55 ьается обычным форматом, при этом, во второй и-разрядной группе с выхода блока 4памяти выдается код интервала времени, ав первой гп-разрядной группе с выхода блока 4 памяти выдается код операции.Формат блока 4 памяти с единичнымлогическим первым и нулевым логическимвторым признаками формата на первом ивтором управляющих выходах называетсяформатом временного интервала, при этомв первой гп-разрядной и второй и-разряднойгруппе выходов блока 4 памяти выдается(гп + и)-разрядный код временного интервала,Формат блока 4 памяти с нулевым логическим первым и единичным логическимвторым признаками на пер ом и втором управляющих выходах называется форматом кода операции, при этом, в первойи-разрядной и второй и-разряднойгруппе выходов блока 4 памяти выдается(гп + и)-разрядный код операции. Форматблока 4 памяти с единичным логическимпервым и вторым признаками формата напервом и втором управляющих выходах называется обратным форматом, при этом, вовторой и-разрядной группе с выхода блока4 памяти выдается код операции, а в первойгп-разрядной группе с выхода блока 4 памяти выдается код временного интервала.Под "обьчной" командой называетсякоманда, формируемая выдачей одногообычного формата заданной длины, разрядность которой позволяет производить выдачу наиболее часто встречающихся команд скодом Операции разрядностью гп и кодоминтервалов времени между командами разрядностью и,С целью наиболее эффективного использования блоа 4 памяти "длинные" команды, которые встречаются реже"обычных" команд, выдаОтс 5 с блока памяти последовательно в виде формата операции, формата временного интервала,обратного формата, число каждого из которых может бцть О, 1, 2, 3, 4 и Одной простойкомандой, заверснающей выдачу с блока 4памяти,В случае выдачи (формирования) простой команды с вьхода блока 4 памяти элемент ИЛИ - НЕ 24 формирует на входэлемента И - НЕ 19, а также вход данныхтриггера 14 уровень логической единицы,так как на первом и втором входах элементаИЛИ - НЕ логические нули (фиг. 2 е и , позиции 2 - 4),Импульс, показанный на фиг. 2 с, поз, 2и 3, с второго выхода элемента 5 задержкичерез элемент И-НЕ 19 (фиг. 2 Ь, поз. 2 и 3),поступают на вход записи информации (на 1667005чальной установки) дополнительного счетчика 12 импульсов, который производит параллельную запись гп-разрядного кода временного интервала с блока 4 памяти, а также на вход синхронизации выходного регистра 3, где по фронту "-Г " происходит запись и-разрядного кода операции с блока 4 памя- и и нулевого кода с выходов вторых 10110, третьих 15115 П; групп регистров сдвига, так как они установлены ранее. Код выходного регистра 3 поступает на вход дешифратора 2, который дешифрует информацию и выдает соответствующие команды на выходную шину 8.Кроме того, импульс с выхода элемента И - НЕ 19 с задержкой переворачивает триггер 13 (фиг. 29, поз. 4), который запрещает прохождение частоты синхронизации устройства с входа 7 синхронизации устройства через элемент И 23 на вход элемента 5 задержки и на вход считывания блока 4 памяти, вследствие чего прекращается выдача данных с блока 4 памяти,Элемент 5 задержки завершает формирование импульса по первому выходу на счетный вход счетчика (фиг. 2 п, поз. 6), который увеличивает (уменьшает в случае обратного счета) величину выходного кода, выдаваемого на адресные входы блока 4 памяти на единицу.Триггер 14 установлен в исходное состояние (фиг. 2, поз. 1 - 10) и, управляя первым мультиплексором 11, подключает входную частоту с входа 7 синхронизации устройства через мультиплексор 11 на счетный вход дополнительного счетчика 12 импульсов. В случае формирования простых команд выход переноса входного счетчика 1 отключен и он не принимает участия в формировании временного интервала, а поэтому здесь не рассматривается,На дополнительном счетчике 12 импульсов формируется временной интервал между текущей и последующей командой, который завершается формированием отрицательного импульса (фиг, 2 с, поз. 9 и 10), на вход элемента 25 задержки и через элемент И - НЕ 23 производит начальную установку первой 91.9 п 1, второй 10110 п, третьей 15115 п, четвертой 16 ь 16 п групп регистров сдвига, устанавливает в единичное состояние триггер 13, который разрешает прохождение частоты синхронизации устройства с входа 7 синхронизации устройства на вход считывания блока 4 памяти и вход элемента 5 задержки. Начинается новая выдача данных.В случае повторной выдачи простых команд с задержкой на элементе 25 задержки относительно импульса переноса дополни(фиг, 29, поз 1 О - 12) 50 15 20 25 30 35 40 тельного счетчика 12 импульсов происходит запись нулевого логического уровня элемента ИЛИ - НЕ 24 в триггер 14 (фиг. 21, поз.32). 8 дальнейшем работа устройства повторяется при поступлении обычных команд.Рассмотрим работу устройства при использовании "длинной" команды. считывание которой осуществляется с первых и вторых групп выходов блока 4 памяти последовательно в видесоставляющих частейкоманды с вышеуказанными видами форматов, при этом простой формат является эавершающей (последней) составляющей "длинной" команды,Пусть нэ выходе дополнительного счетчика 12 импульсов сформировался отрицательныймпульс переноса (заема) (фиг. 20, поз 9 и 10), который через элемент И - НЕ 23 (фиг. 2 р, поз. 9 и 10) произвел начальную установку первых 919 п, вторых 10110 п, третьих 151,15 п четвертых 16116, групп регистров сдвига и установил в единичное состояние по инверсному выходу триггер 13, который разрешает прохождение импульсов синхронизации с входа 7 синхронизации устройства на вход элемента 5 задержки и вход считывания блока 4 памяти, который выдает информацию, соответствующую коду адреса счетчика 6 адреса, на первой и второй группе выходов, нэ первые и вторые управляющие выходы (фиг. 2 е, 1, поз. 10 - 13).Так как первая составляющая данных, выдаваемых с блока 4 памяти, при использовании "длинной" команды отлична от простого формата, то на первом и втором управляющих выходах блока 4 памяти код признаков команд на первом и втором управляющих выходах блока 4 памяти отличен от 00, и поэтому на выходе элемента ИЛИ - НЕ 24 при выдаче "длинных" командс блока 4 памяти присутствует уровень логического нуля, и появление импульса на втором выходе первого элемента 5 задержки не приводит к изменению состояния триггера 13 Элемент 25 задержки с задержкой по отношению к импульсу переноса дополнительного счетчика 12 импульсов производит запись уровня логической единицы в триггер 14, который подключает выход переноса (заема) входного счетчика 1 к счетному входу дополнительного счетчика 12 импульсов,В случае выдачи формата временного ин. ервала, для которого код признака 10 с управляющих выходов блока 4 памяти и импульсы синхронизации с второго и третьего выходов первого элеменга 5 задержки проходят через элемент И-НЕ 17 и элемент ИЛИ 21 на синхровходы сдвига первой919 гп и четвертой 161,16 п, групп регистров сдвига соответственно (фиг. 2), 1, поз, 10- 12). Таким образом, информация с первых и вторых групп выходов блока 4 памяти записывается со сдвигом информации в регистрах 919 п 1 в первые и четвертые 161,16 п групп регистров сдвига. Далее блок 4 памяти прекращает выдачу данных, а первый элемент 5 задержки завершает формирование импульса на первом выходе (фиг, 2 п, поэ. 14), что соответствует очередной смене выходного кода адреса счетчика б адреса,Далее с приходом очередного импульса частоты синхронизации с входа 7 синхронизации устройства повторяется выдача очередных данных с блока 4 памяти по новому адресу, где может быть записан формат кода операции, формат временного интервала, либо обратный формат.При этом, в случае выдачи с блока 4 памяти формата кода операции им пульсы синхронизации с второго и третьего выходов первого элемента 5 задержки прохоцят через элемент И - НЕ 18 и элемент ИЛИ 20 соответственно на синхровходы сдвига регистров сдвига 101.10 п второй и 15115 п третьей групп, где записывается информация с выходов второй и первой групп выходов блока 4 памяти (фиг. 2 е, гп поз. 15 и 16), а в случае обратного кода импульс синхронизации с второго выхода второго элемента 5 задержки проходит через элемент И - НЕ 17 и элемент И - НЕ 18 на соответствуюгцие синхровходы сдвига первой 91.9 п и второй 10110 п групп регистров сдвига (фиг. 21, гп поз. 19 и 20), где записывается информация с выходов первой и второй групп выходов блока 4 памяти соответственно.Далее блок 4 памяти прекращает выдачу данных, а элемент 5 задержки завершает формирование импульса на первом выходе (фиг. 2 п, поз, 17, 18 и 22), что соответствует очередной смене, т.е. увеличению или уменьшению выходного кода адреса счетчика 6 адреса на единицу.Далее работа устройства в процессе выдачи данных с блока 4 памяти происходит аналогичным образом,Пусть произошла выдача последней 1-й составляющей данной "сложной" команды, структуре которой соответствует обычный формат выдачи данных с блока 4 памяти, а значит, первый и второй признаки команд на первом и втором управляющих выходах блока 4 памяти уровни логических нулей, что дешифрирует элемент ИЛИ-Н Е 24 и выдает на выход уровень логическсй единицы, который разрешает прохождению импульса с второго выхода первого элемента 5 задержки через элемент И - НЕ 19 на. вход записи 5 10 20 25 30 35 40 45 триггера 13, импульсы синхронизации первого элемента 5 задержки проходят через элемент ИЛИ 20 и элемент ИЛИ 21 на соответствующие синхровходы сдвига третьей 15115 п 1 и четвеотой 16116 п групп регистров сдвига (фиг. 2 1 и е. поз. 23 и 24),Таким образом, информация с первых и вторых групп выходов блока 4 памяти записывается со сдвигом информацйи в четвертые 161,16 п и третьи 15115 п группы регистров сдвига.Импульс с второго выхода элемента 5 задержки проходит через элемент И - НЕ 19 и завершает запись информации в выходной регистр 3 с второй группы выходов блока 4 памяти и с выходов второй 101.10 п и третьей 15115 п 1 групп регистров сдвига (фиг. 21 к и 1, поз. 23 и 24) завершает параллельные записи (установки) входного счетчика 1 и счетчика 12 импульсов, а также переворачивает по входу записи триггер 13, который запрещает выдачу импульсов синхронизации с входа 7 синхронизации устройства на вход элемента 5 задержки и вход считывания блока 4 памяти, который переходит в режим хранения, Дешифратор 2 дешифрирует выходной код выходного регистра 3 и выдает новые команды на выходную шину 8 устройства,Элемент 5 задержки завершает формирование импульсов с первого выхода на счетный вход счетчика б адреса, который увеличивает(уменьшает) выходной код счетчика б адреса на единицу,Далее происходит формирование временного интервала путем счета частоты синхронизации, поступающей с входа 7 синхронизации устройства на последовательно соединенных через мультиплексор 11 входном счетчике 1 и счетчике 12, формирование которого завершается появлением отрицательного импульса на выходе переноса дополнительного счетчика 12 импульсов (фиг, 20, поз. 30 и 31). Работа устройства при формировании простых (фиг, 2 р, поз, 31 - 39), а также "длинных" команд повторяется аналогично описанному. Формула изоб ретения Устройство для прогоаммного управления, содержащее входной счетчик импульсов, дешифратор, выходной регистр, блок памяти команд, первый элемент задержки, счетчик адреса, регистры сдвига первой группы, регистры сдвига второй группы, мультиплексор, дополнительный счетчик импульсов, первый и вторс, триггеры, причем вход считывания блока памяти команд соединен с входом первого элемента задержки, первый выход которого соединен со10 25 30 35 40 45 50 55 счетным входом счетчика адреса, выходная шина которого подключена к группе адресных входов блока памяти команд, первая группа п выходов которого соединена с информационными входами последовательной записи и регистров сдвига первой группы, руппа выходов которых соединена с группой информационных входов входного счетчика импульсов, выход переноса которого соединен с первым информационным входом мультиплексора, выход которого соединен со счетным входом дополнительного счетчика импульсов, вход ввода информации которого соединен с входом записивыходного регистра, а также с входом ввода информации входного счетчика импульсов,:четный вход которого соединен с вторым информационным входом мультиплексора, а также входом синхронизации устройства. вторая группа и выходов блока памяти команд соединена с первой группой информационных входов выходного регистра и с информационными входами последовательной записи и регистров сдвига второй группы, группа входов которых соединена с второй группой информационных входов выходного регистра, разрядные выходы которого подключены к выходам дешифратора, группа выходов которого подключена к выходной шине устройства, кроме того, синхровходы сдвига щ регистров сдвига первой группы и и регистров сдвига второй группы объединены соответственно, о т л и ч а ющ е е с я тем, что, с целью экономии объема памяти, в него введены п регистров сдвига третьей группы и и регистров сдвига четвертой. группы, первый, второй, третий и четвертый элементы И - НЕ, первый, второй элементы ИЛИ, элемент И, элемент ИЛИ - НЕ, второй элемент задержки, при этом первая группа т выходов блока памяти команд соединена с группой информационных входов дополнительного счетчика импульсов, а также с информационными входами последовательной записи и регистров сдвига третьей группы, группа выходов которых соединена с третьей группой информационных входов записи выходного регистра соответственно, вторая группа п выходов блока памяти команд соединена с информационными входами последовательной записи гп регистров сдвига четвертой группы, группа выходов которых соединена с второй группой в информационных входов входного счетчика импульсов, первый управляющий выход блока памяти команд соединен с первым входом элемента ИЛИ - НЕ, первым входом первого элемента ИЛИ, первым входом первого элемента И-НЕ, выход которого соединен с синхровходом сдвига е регистров сдвига первой группы соответственно, второй управляющий выход блока памяти команд соединен с вторым входом элемента ИЛИ - НЕ, первым входом второго элемента И-НЕ и с первым входом второго элемента ИЛИ, выход которого соединен с синхровходами сдвига и регистров сдвига четвертой группы соответственно, вход синхронизации устройства соединен со счетным входом входного счетчика импульсов, втсрым входом мультиплексора, вторым вход м первого элемента И, выход которого соединен с входом считывания блока памяти команд и с входом первого элемента задержки, второй выход которого соединен с первым входом третьего элемента И-НЕ, вторым входом первого элемента И - НЕ, вторым входом второго элемента И-НЕ, выход которого соединен с синхровходами сдвига и регистров сдвига второй группы соответственно, третий выход первого элемента задержки соединен с вторым входом второго элемента ИЛИ и с вторым входом первого элемента ИЛИ, выход которого соединен с синхровходами сдвига п регистров сдвига третьей группы соответственно, выход элемента ИЛИ - НЕ соединен с входом данных второго триггера и вторым входом третьего элемента И - НЕ, выход которого соединен с синхровходом первого триггера, с входом записи выходного регистра, входом ввода информации входного счетчика импульсов, а также входом ввода информации дополнительного счетчика импульсов, выход переноса которого соединен с первым входом четвертого элемента И - НЕ, а также входом второго элемента задержки, выход которого соединен с синхровходом второго триггера, выход которого соединен с управляющим входом мультиплексора, кроме того, в од установки устройства соединен с входом ввода информации счетчика адреса, входом сброса второго триггера, вторым входом четвертого элемента И - НЕ, выход которого соединен с входами сброса регистров сдвига первой, второй, третьей и четвертой групп, а также с входом сброса первого триггера, выход которого подключен к первому входу первого элемента И.а1 В1 ВВт -ВВВюе Ф1 9ФВт-е-Г-ГВВВ 1,г- - г Составитель И,ШвецЮ.Середа Техред М.Моргентал Корр Ре нчаков Заказ 2521 Тираж 477 Подп ВНИИПИ Государственного комитета по изобретениям и о 113035, Москва, Ж, Раушская наб., ноерытиям при ГКНТ С оизводственно-издательский комбинат "Патент", г. У город, ул.Гагарина, 1ВВВ 11 дгт 1" 1В ф аю 1 Веефю иф Ф 1аВ 111 111 ВВ)1111

СмотретьЗаявка

4738244, 14.08.1989

ПРЕДПРИЯТИЕ ПЯ М-5653

ОМЕЛЬЧЕНКО СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G05B 19/408, G05B 19/4155

Метки: программного

Опубликовано: 30.07.1991

Код ссылки

<a href="https://patents.su/7-1667005-ustrojjstvo-dlya-programmnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для программного управления</a>

Предыдущий патент: Система управления

Следующий патент: Устройство адаптивного управления металлорежущим станком

Случайный патент: Электромагнитное захватное устройство