Программно-управляемый генератор синусоидальных колебаний

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

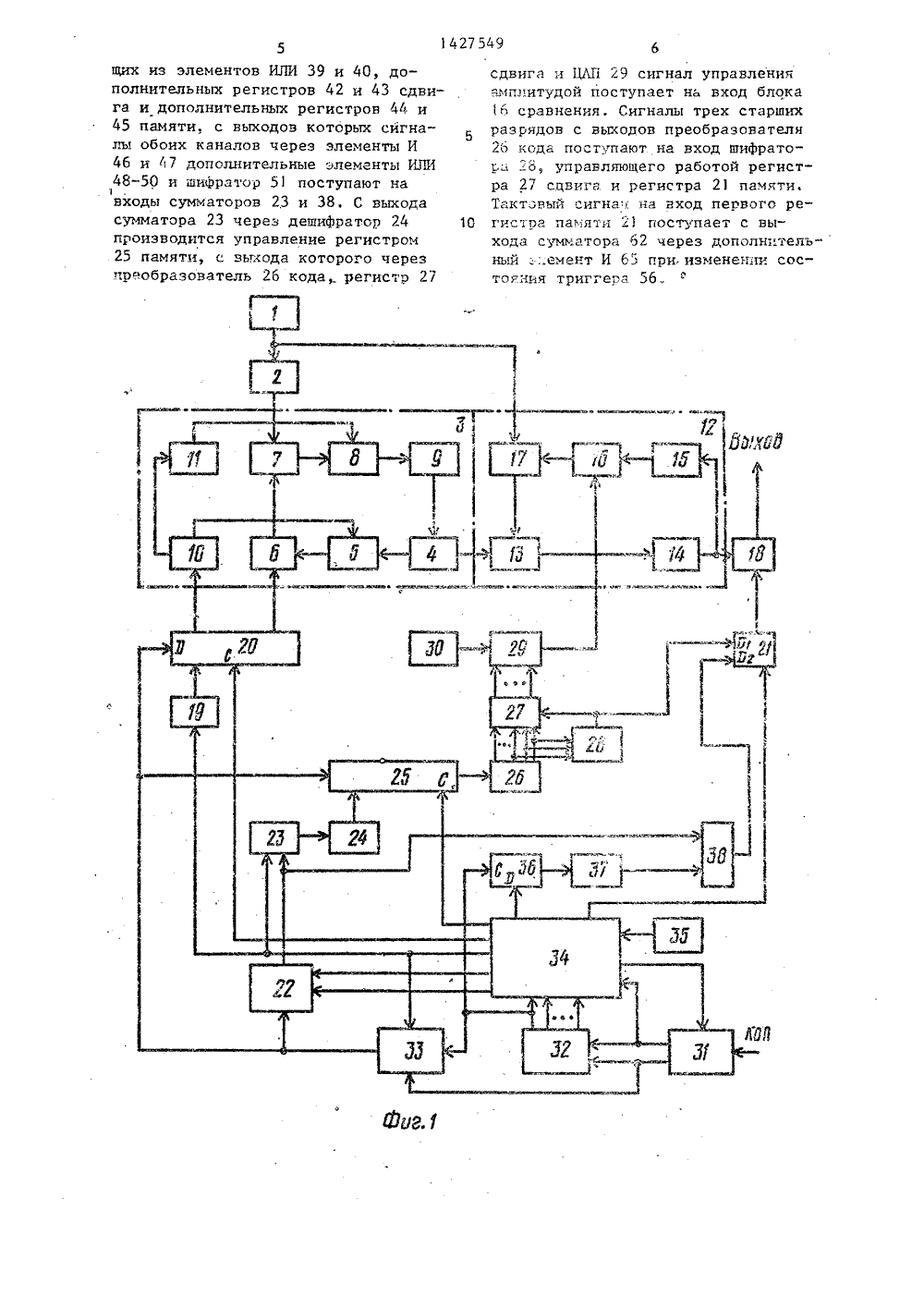

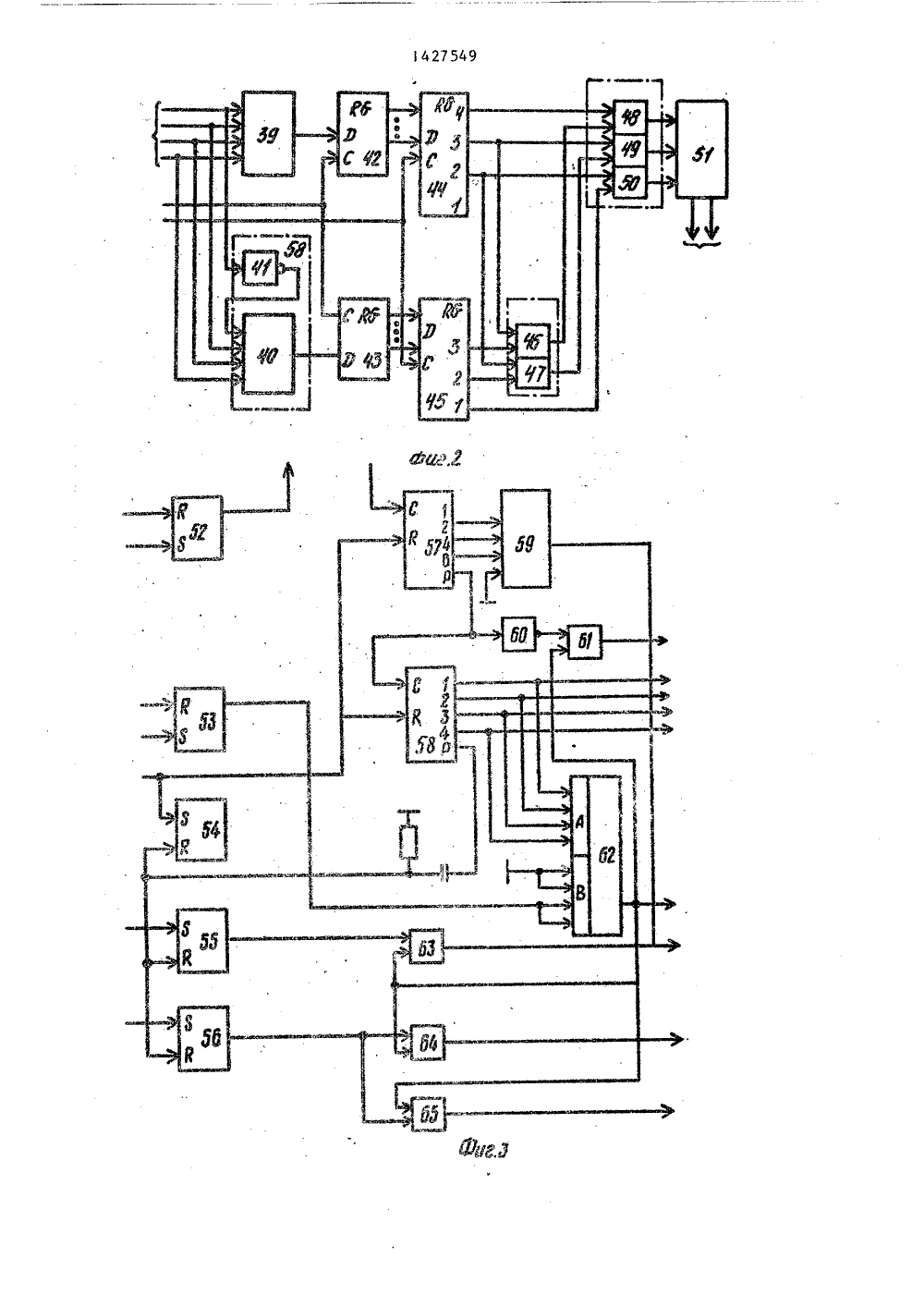

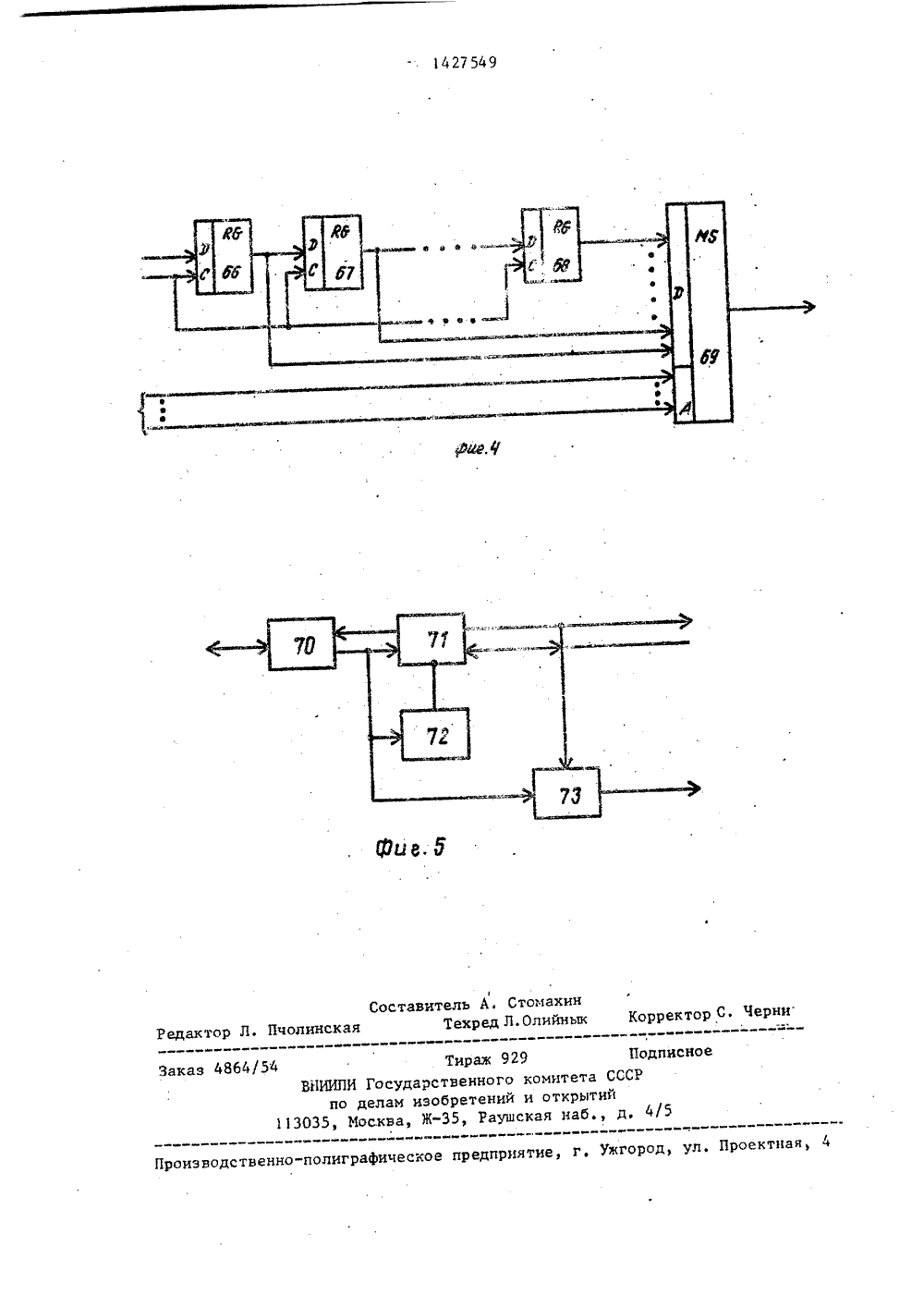

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХ 4275 РЕСПУБЛИН ЯД 11 4 11 03 В ИОАНИ в,инструкци ин о са ГОСУДАРСТВЕННЬ 1 Й НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И СТНРЫТИИ(541)(57) 1. ПРОГРАК 1 НО-УПРАВЛЯЕМЫЙГЕНЕРАТОР СИНУСОИДАЛЬНЫХ КОЛЕБАНИЙ,содержащий последовательно соединенные опорный генератор, делительчастот, датчик сетки частот, блокстабилизации уровня выходного напряжения и аттенюатор, последовательно соединенные блок ввода сигналов программного управления, блокоперативного запоминания и регистрпамяти кода частоты, дешифраторуправляющих сигналов, генератортактовых импульсов, первый регистрпамяти кода амплитуды, первый дешифратор адреса и блок управления,при этом датчик сетки частот выполнен в виде последовательно соединенных накапливающего сумматора,первого цифроаналогового преобразователя, интегрирующего звена,фильтра нижних частот, управляемого напряжением, генератора, блока исключения импульсов, делителя частоты с переменным коэффициентом деления и фазового детектора, опорныйвход которого является опорным входом датчика сетки частот, а второйвыход накапливающего сумматора подключен к управляющему входу блока исключения импульсов, второи выход управляемого напряжением генератора является выходом датчика сетки частот, блок стабилизации уровня выходного напря.,ения выполнен в виде соединенных в кольцо смесителя, усилителя мощности, преобразователя напряжения, блока сравнения и усилителя с регулируемым коэффициентом передачи, сигнальный вход которого подключен к выходу опорного генератора другой вход смесителя является входом блока стабилизации уровня выходного напряжения, выходом которого является выход усилителя мощности, синхрониэирующий выход блока ввода сигналов программного управления соединен с первым входом элемента ИЛИ, выход которого соединен со стробирующим входом дешифратора уп- вею) равляюших сигналов и первым синхронизирующим входом блока управления. первый тактовый вход которого подклю- д, чен к выходу генератора тактовых импульсов, управляющие выходы дешифратора управляющих сигналов соединены с соответствующими управляющими входами блока управления, информационный выход блока ввода сигналов программного управления, соединен также с информационным входом дешифратора управляющих сигналов, синхронизирующий выход дешифратора управляющих сигналов соединен с тактовым входом блока оперативного запоминания. и вторым входом синхронизации блока управления, первыйф рмационный выход которого соединен с входом первого дешифратора адре и управляющим входом блокаоперативного запоминания, тактовыйвход регистра памяти кода частотыподключен к первому тактовому выходублока управления, а управляющий выход первого дешифратора адреса соединен с управляющим входом регистрапамяти кода частсгы, первый и второйинформационные выходы которого соединены с входами соответственнс накапливающего сумматора и делителя частотыс переменным коэффициентом деления,второй тактовый выход блока управления соединен с тактовь.м входом первого регистра памяти кода амппитуды,Выход которого подключен : входу аттенюатора, управляющий выход блокауправления соединен с управляющю:входом блока ввода сигналов програж ного управления, информационный входкоторого является Входом программноуправляемого генератора синусоидальных колебаний, о т л и ч а ю щ и й -с я тем, что, с целью повышения точ-ности установки уровня выходных си"нусоидальных колебаний, в него введены последовательно соединенныеблок Формирования кода амплитуды,.первый .сумматор, второй дешифраторацреса, второй регистр памяти кодаамплитуды, преобразователь кора, первый регистр сдвига и второй циФ- роаналоговый преобразователь, к опор" ному входу которого подкгпочен чвыходис 1 осдцп;а опорного напряжения последовательно соединенные второй регистр сдВига первый шифратор и второй сумматор, а также второй шифратор, группа информационных входов которого подключена к ссответ" ству 1 ощим информационным выходам преобразователя кода, выход которого соединен С управляющим ВхОдОм первого регистра сдвига и 1 ервым инфор " мационньч входом первого регистра памяти хода амплитуды, второй информационный вход которого соединен с выходом второго сумматора,. Выход второго цифроаналогового преобразо-вателя соединен с другим входом бпска сравнения, второй вход второго сум матора подключен к выходу блока Формирования кода амплитуды третий таКтсвыи ВЫХОД блОка управления сОе динен с тактовым входом второго регистра памяти кода ампчитуды, четВертый тактовый выход блока управления соединен с первым тактовым входом блока Формирования. кода амплитуды пятый тактовый. выход блока уп равления соединен с вторым тактовымвходом блока формирования кода амплитуды, тактовый вход второго регистра сдвига соединен с синхронизирующим выходом дешифратора управляющих сигналов, а управляющий входвторого регистра сдвига соединен свторым информационным выходом блокауправления, информационный вход блокаформирова ия кода амплитуды соединенс выходом блока оперативного запоминания, информационный вход второгорегистра памяти кода амплитуды соединен с гыходом блока оперативного запоминания, а второй вход первого сумматора соединен с первым информационным выходом блока управления. 2. Генератор по и. 1 о т л и - ч а ю щ и й .с я тем что блок формирования коца амплитуды содержит последовательно соединенные первый элемент ИЛИ первый дополнительный регистр сдвига и первый дополнительный регистр памяти, первьпл, вто" рой и третий выходы которого соединены с первыми входами первого, второго и третьего дополнитсльных элементов ИЛИ, выходы которых сое" динены с соответствуюшими входами третьего шифратора, выходы которого являются выходами блока Формирования кода амплитуды, последовательно соединенные первый элемент ИЛИ-НЕ, второй элемент ИЛИ, второй дополнительный регистр сдвига и второй дополнительный регистр памяти, первый и з .Орой выходы которого соединены с первыми входами первого и второго:-.лементов Е, выходы которых сседиены с соответствующими вторыми входами первого и второго дополнительных элементов ИЛИ, а второй вход третьего дополнительного элемента ИЛИ соединен с третьим выходом второго дополнителього регистра памяти, вторые входы первого ч второго элементов И соединены соответственно с вторым и третьим выходами перво" г О дополнительного регистра памяти входы первого элемента ИЛИ являются входами блока формирования кода амплитуды, первый вход первого элемента ИЛИ соединен с входом элемента ПЖ-НЕ, а второй, третий и четвертый входы первого элемента ИЛИ соединенысоответственно с вторым, третьим и1427549 четвертым входами второго элементаИЛИ, тактовые входы первого и второго дополнительных регистров сдвигаобъединены и являются первым тактовым входом блока Формирования кода Изобретение относится к радиотехнике н связи, предназначено для по- лучеля синусоидальных колебаний по сигналам программного управления и может быть использовано в автоматизированных системах измерения и контроля,Цель изобретения - повышение точности установки уровня выходных синусоидальных колебаний.На фиг, 1 представлена структурная электрическая схема программноуправляемого генератора синусоидальных колебаний; на фиг. 2 - структурная электрическая схема блока фори- рования кода амплитуды: на Фиг, 3 - структурная электрическая схема блока управления; на Фиг. 4 - структурная электрическая схема блока оперативного запоминания; на фиг. 5 - струк" турная электрическая схема блока вво.да сигналов программного управления: Программно-управляемьй генератор синусоидальных колебаний содержит опорный кварцевый генератор 1, дели-. тель 2 частоты, датчик 3 сетки частот, который состоит из управляемого напряжением генератора 4, блока 5 исключения импульсов, делителя 6 частоты с переменным коэффициентом деления (ДПКД) фазового детектора 7, интегрирующего звена 8, фильтра 9 нижних частот, накапливающего сумматора 10 и первого цифроаналогового преобразователя (ЦАП) 11, блок 12 стабилизации уровня выходного напряжения, смеситель 13, усилитель 14 мощности, преобразователь 15 напряжения, блок сравнения 16, усилитель 17 с регулируемым коэффициентом передачи, аттенюатор 18, первыйдешифратор 19 адреса, регистр 20 памяти кода частоты, первый регистр 21 памяти кода амплитуды, блок форамплитуды, а тактовые входы первогоч второго дополнительных регистровпамяти объединены и являются вторымтактовым входом блока формированияод,". амплитуды. 21 памяти кода амплитуды, блок 22Формированиякода амплитуды, первыйсумматор 23, второй,дешифратор 24адреса, вторсй регистр 25 памятикода амплитуды, преобразователь 26када, первый регистр 27 сдвига, второй шифратор 28, второй ЦАП 29, источник 30 опорного напряжения, блок31 ввода сигналов программного управ 10 пения, дешифратор 32 управляющихсигналов, блок 33 оперативного запоминания, блок 34 управления, генератор 35 тактовых импульсов, второйрегистр сдвига 36, первый шифратор37, второй сумматор 38,Блок 22 Формирования кода амплитудь содержит первый 39 и второй40 элементы ИЛИ, первый элемент ИЛИНЕ 41, первый 42 и второй 43 допол"20нительные регистры сдвига, первый44 и второй 45 дополнительные регист"ры памяти, первый 46 и второй 47элементы И, перьый 48, второй 49 итретий 50 дополнительные элементыИЛИ, а такте шифратор 51,Блок 34 управления образуют триггеры 52-56, первый 57, второй 58 счетчики, дешифратор 59 тактовых импульсов инвертор 60, дополнительно элемент ИЛИ 61, сумматор 62, первый 63, второй 64 и третий 65 дополнитель. ные элементы И. Блок 33 оперативного запоминания, содержит (Фиг,4) первый 66, второй 67, третий 68 дополнительные регистры памяти, а также мультиплексор 69.Блок 31 ввода сигналов программного управления состоит из4 лока 70 приемопередачи, блока 71 формирования сигналов программного управления, блока 72 декодирования сигналов программного управления и буферный регистр 73 памяти.Программно-управляемый генераторсинусоидальных колебаний работаетследующим образом,Сигналы программного управлениячастотой и амплитудой выходного сиг.;яля последовательно поступают наВход блока 31 ввода, состоящий изтактовых интерФейсных ФункциональныхПроходя через блок 70 приемопередачи, блок,72 декодированияИ блок 71 сигналы поступают на управляющий Вход дешиФратора 32 и на перВый синхронизирующии вход блока 34управления. а с выхода буФерного,регистра 73 памяти - ня инФормационвые входы дешиФратора 32 и блока 33перятинного запоминания, состоящего из последовательно соединенныхчетырехразрядных регистров памятиэо 67 и 68, выходы которых коммутиуются с помощью мультиплексора 69 наВходы блока 22 Формирования и регист:,)ов 20 и 25 памяти.На вход регистра 20 памяти посту-пает код частоты выходного сигналя вПоследовательности, определяемой ко 4 ом адреса на выходе перного дешиФ"датора 19, я код амплитуды записы,-,.ФЯ НО ЗТОРой ОЕГИСтР ПЯМЯТИ,,.",Г,.я.о коду адреса с выхода второго дешиФратора 24. Смена данных очас"Оте и амплитуде производится по.;актовым сигналам с выходов блока34: Последовательность команд нажлну даннв поступает с выходовдешнФряторя 32 на триггеры 52-56признака команды, а тактовые сигналы с генератора 35 через первый счет.-:Вгк 57 и дешжоратор 59 поступают чавыходы дополнительных элементов И63 и 64. С изменением состояния триг 1 ера 5"; тактовьй сиГнал с выхОДЯ ДО;-однц,;:.Чьног.", элемента Б 63 поступает на вход регистра 20 памяти,я с изменечием состояния триггера 56тактовый сигнал с выхода дополнительного элемента И 64 поступает на входвторого регистра 25 пямятй С изменением состояния триггера 53 с вы,:;ода.сумматора 62 и дополнительчогоэлемента ИЛИ 6, тактовые сигналы поступают на входы блока 22 Формирования.Изменение частоты выходного сигнала производится по двум входам датчика 3 причем с первого выхода регистдя 20 памяти сигнал управленияпоступяет ня Вход интегрирующеголаИзменение амплитуды выходного сигнала производится одновременно подвум каналам: изменением опорногонапряжения на вьиоде второго ЦАП 29и изменением непичины ослабления аттенюатора 18, При этом на информа"цнонньй ВхОд второГО реГистря пямяти 25 поступает код мантиссы амплитуды, а код порцкя амплитуды децимальная точка, устананлнвается прнподаче сигналя управления с дешиФ ратора 32 через триггер 52 второйрегистр 36 сдвига, первый шнФратор37 и второй сумматор 38 на входпервого ретистра памяти, изменяюДбщего величину козФФициента ослабления аттеиоятора 18,Преобразование кода мантиссыамплитуды заключается з умноженииисходного значения на 10 , где6 ЬОО ш = 0,1,2,3. умножение эквивалентно сдвигу на ш десятичных разрядовчто обеспечивается путем суммирования кода. адреса, поступающего наВходы первого сумматора 23 с нторого счетчика 58 блока 3 ч и кодасдвига амплитуды с выхода блока 22.Формирование кода сдвига амплитудыс вьхода блока 22 произьодится ндвух параллельных каналах состоя 10 15 2 О 2 г звена 8 через накапливающий сумматор 10 и ЦАП 11, а с нторого выхода регистра 20 памяти сигнал управления поступает на вход ДПКД 6, нключенного в петлю Фазоной антоподстройки частоты, которая состоит из Фазовогодетектора 7, интегрирующего звена 8, Фильтра 9 управляемого напряжением генератора 4 и блока 5. При этом датчик 3 вырабатывает сигнал с частотой. значение которой лежит несколько ныше рабочего диапазона частот программ ио-управляемого генератора синусондальных колебаний. Этот сигнал поступает на один вход смесителя 13, на другой вход которого через усили" тель 17 подается сигнал кварцованной частоты с выхода опорного кварцевого,генератора,1 и на опорный вход Фазового детектора 7 через усилитель 2. На выходе смесителя,13 ныделяетс сигнал разностной частоты, для которой блок 12, состоящий из нключенньх в кольцо усилителя 14, преобразователя 15, блока 16 сравнения, усилителя 17 и смесителя 13, обеспечивает постоянство амплитуды выходного сигна 1427549ших из элементов ИЛИ 39 и 40, дополнительных регистров 42 и 43 сдвига и дополнительных регистров 44 и45 памяти, с выходов которых сигналы обоих каналов через элементы И46 и 47 дополнительные элементы ИЛИ48-50 и шифратор 51 поступают навходы сумматоров 23 и 38. С выходасумматора 23 через дешифратор 24производится управление регистром25 памяти, с выхода которого черезпр фобразователь 26 кода,. регистр 27 сдвига и ЦЛП 29 сигнал управления амплитудой поступает на вход блока 16 сравнения, Сигналы трех старших разрядов с выходов преобразователя 26 кода поступают на вход шифрато 28, управляющего работой регистра 27 сдвига и регистра 21 памяти, Тактвый сигна на вход первого ре гистра памяти 21 поступает с выхода сумматора 62 через дополнительный :;,емент И 65 при,изменении состояния триггера 56.1427549 Составитель А, Стомахин Техред Л.Олийнык Корректор С. Черни. Редактор Л. Пчолинска Заказ 4864/54 Производственно-полиграфическое предприятие, г. Ужгород, ул ктная,Тираж ВНИИПИ Государствен по делам изобрет 3035, Москва, Ж, 929 Подписноего комитета СССРий и открытийушская наб., д. 4/5

СмотретьЗаявка

3817383, 26.11.1984

ПРЕДПРИЯТИЕ ПЯ А-3559

ЖУРАВЛЕВ МАРК ИВАНОВИЧ, ГРИНБЕРГ БОРИС ИОСИФОВИЧ, ГЛУСКИНА ВАЛЕНТИНА ИСААКОВНА

МПК / Метки

МПК: H03B 19/00

Метки: генератор, колебаний, программно-управляемый, синусоидальных

Опубликовано: 30.09.1988

Код ссылки

<a href="https://patents.su/7-1427549-programmno-upravlyaemyjj-generator-sinusoidalnykh-kolebanijj.html" target="_blank" rel="follow" title="База патентов СССР">Программно-управляемый генератор синусоидальных колебаний</a>

Предыдущий патент: Генератор электрических колебаний

Следующий патент: Цифровой генератор низкочастотных сигналов

Случайный патент: Полый холодный катод