Микропрограммное устройство управления с самоконтролем

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1427367

Авторы: Балакин, Барашенков, Календарев, Карпова

Текст

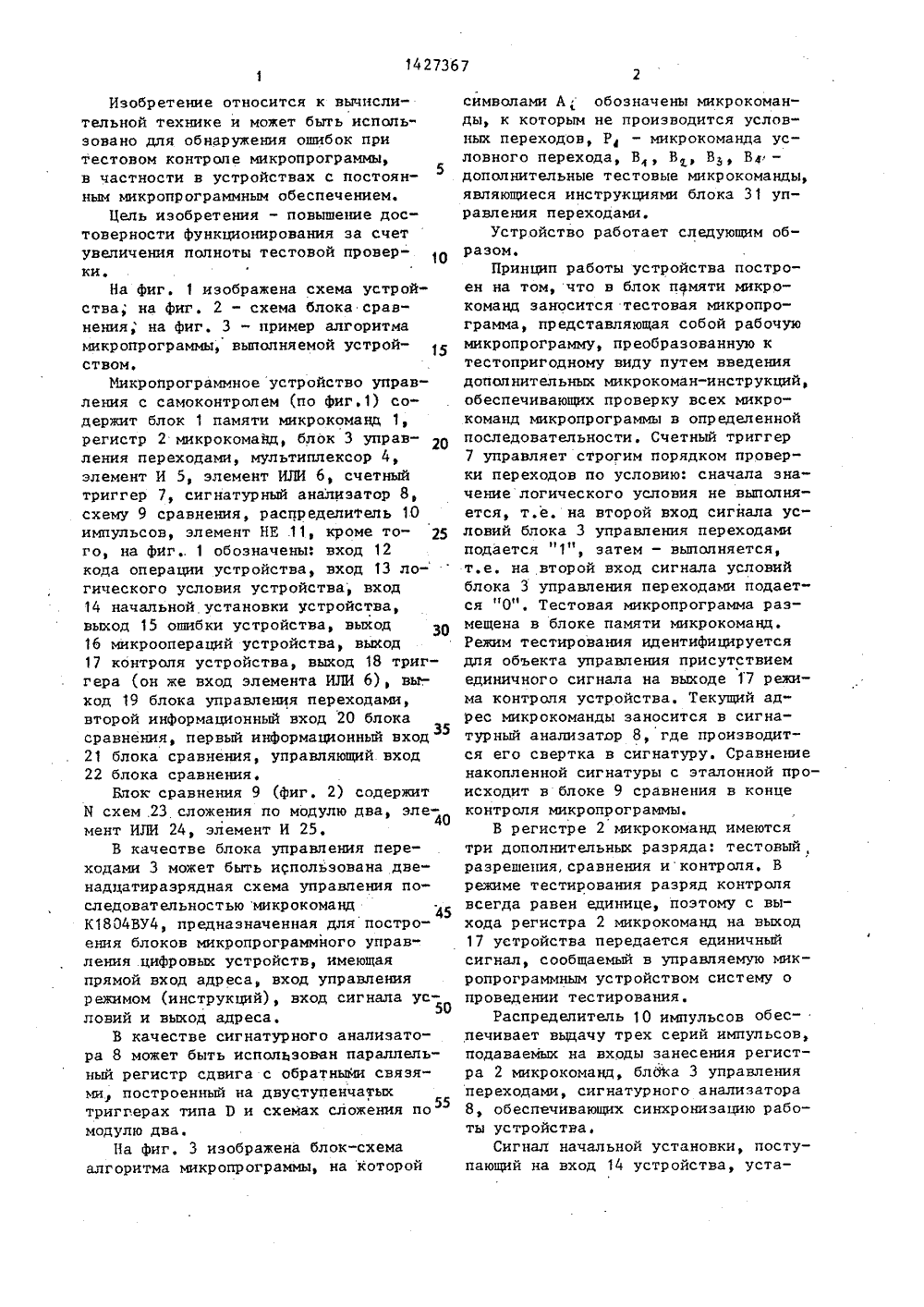

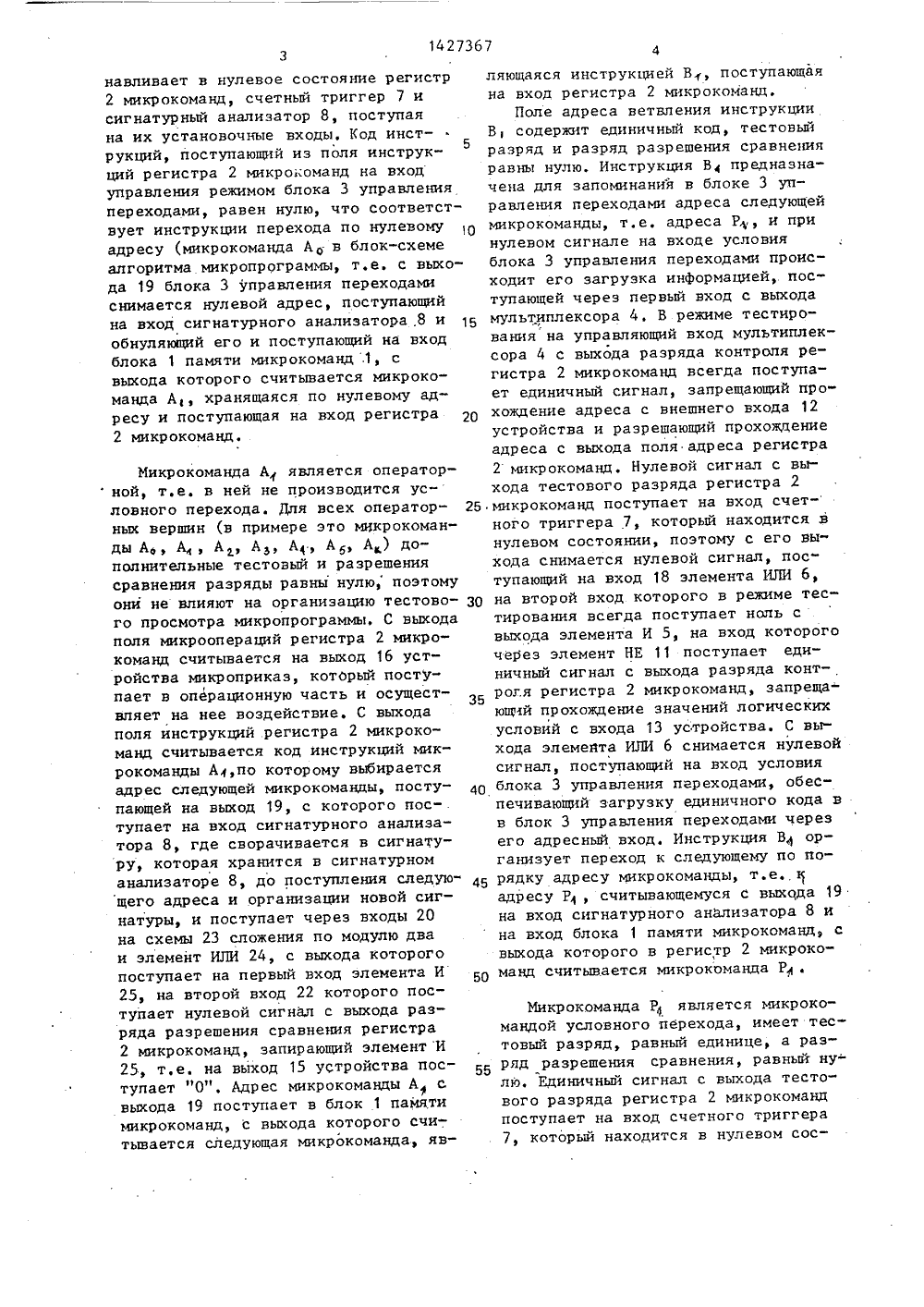

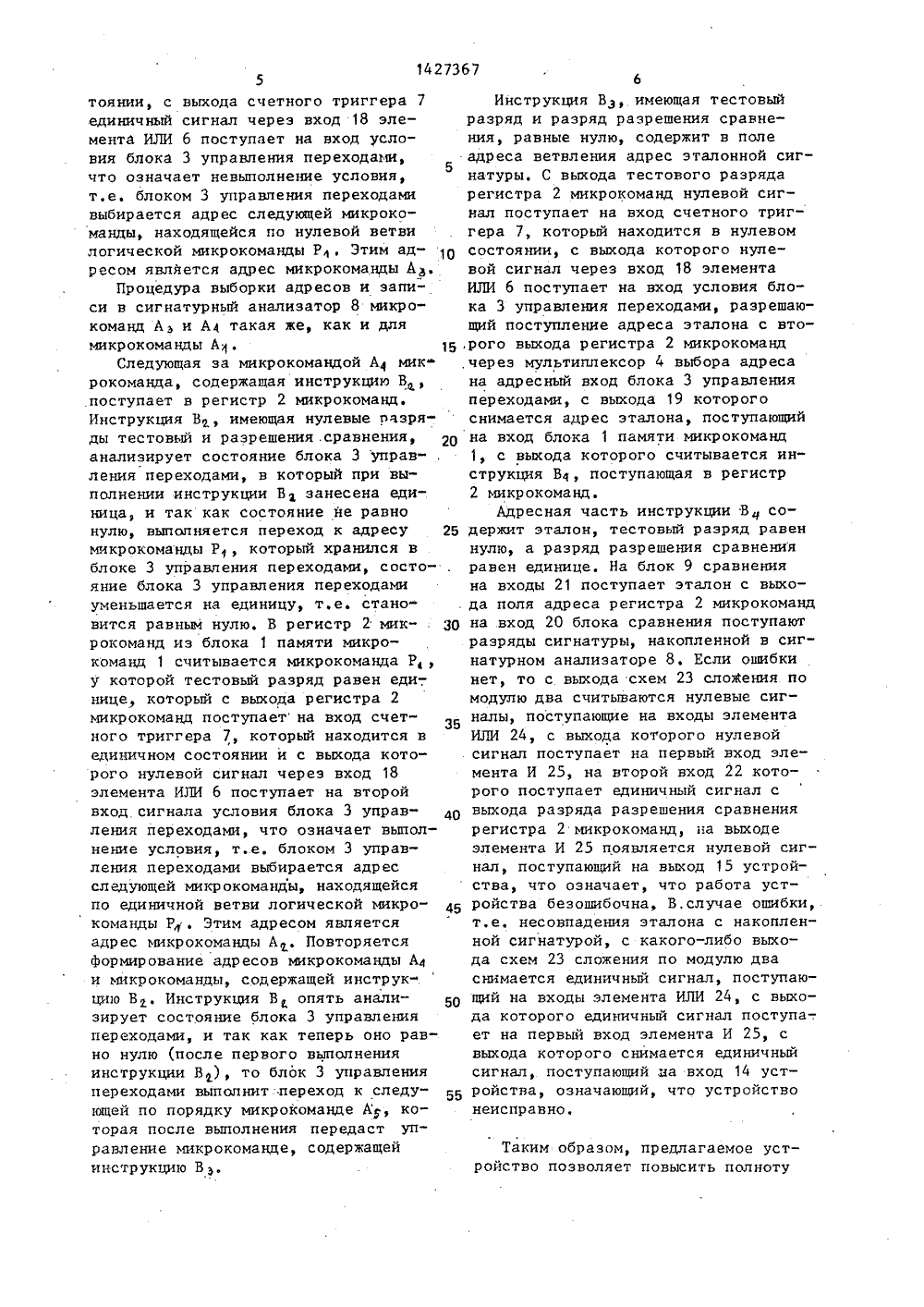

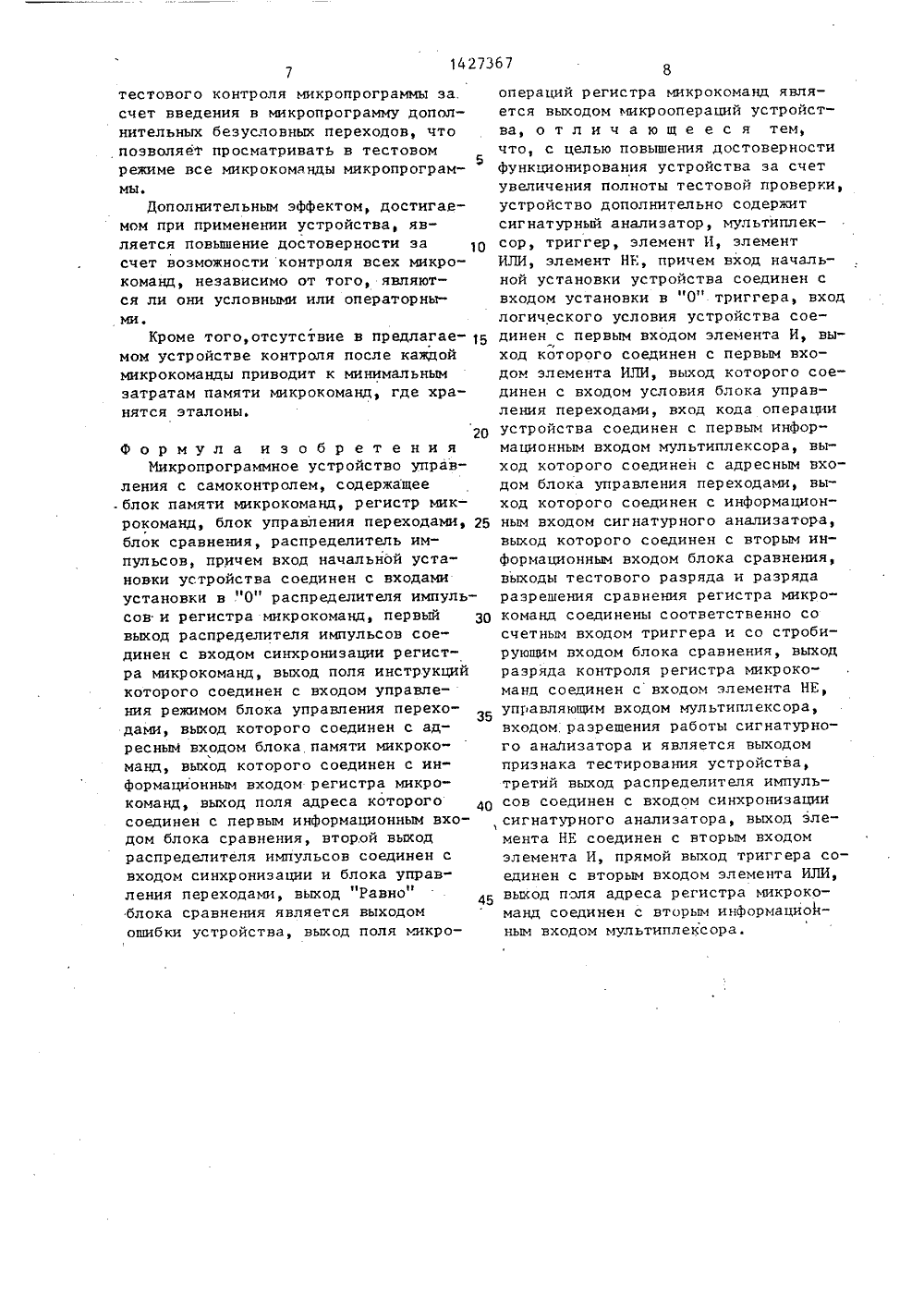

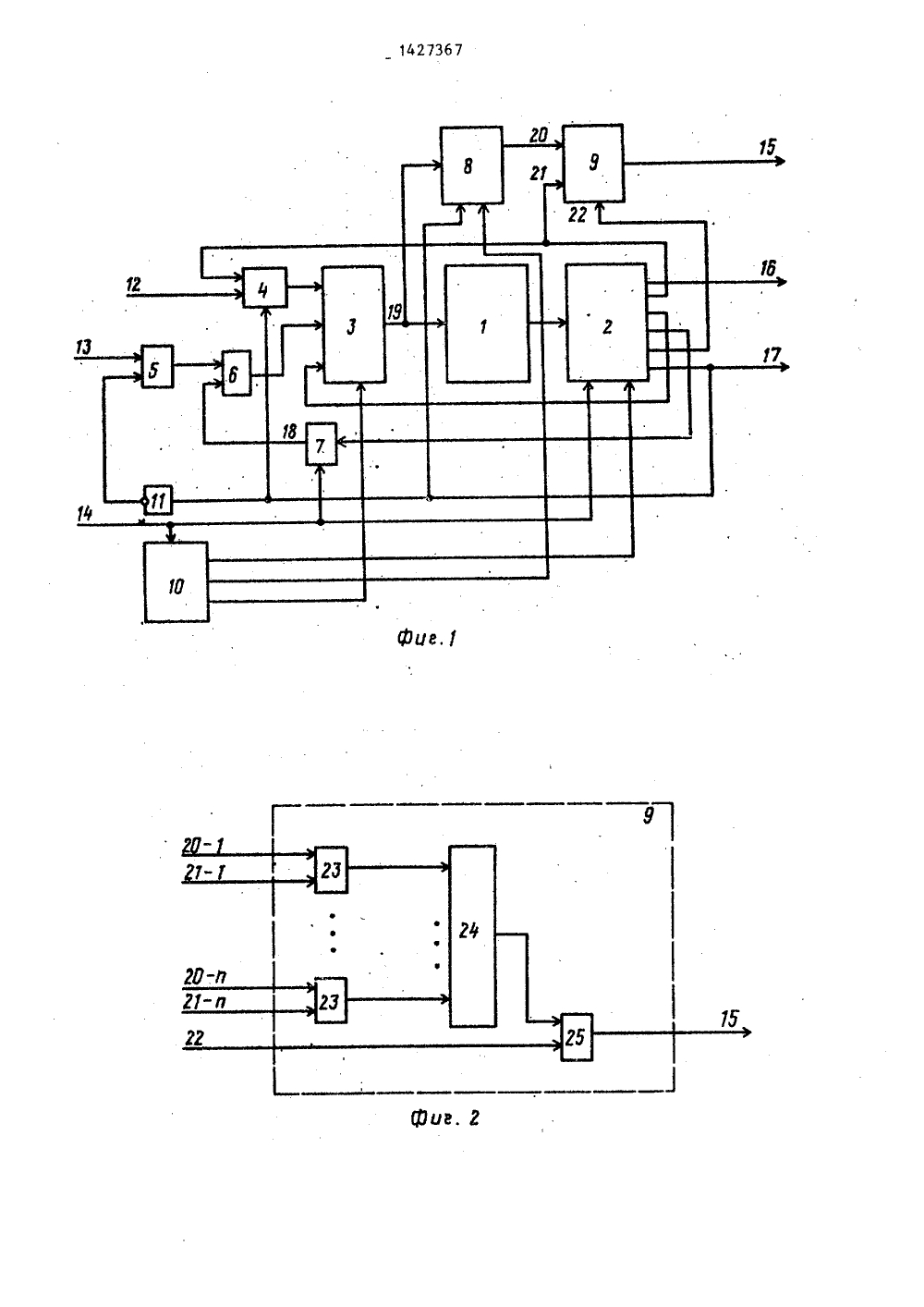

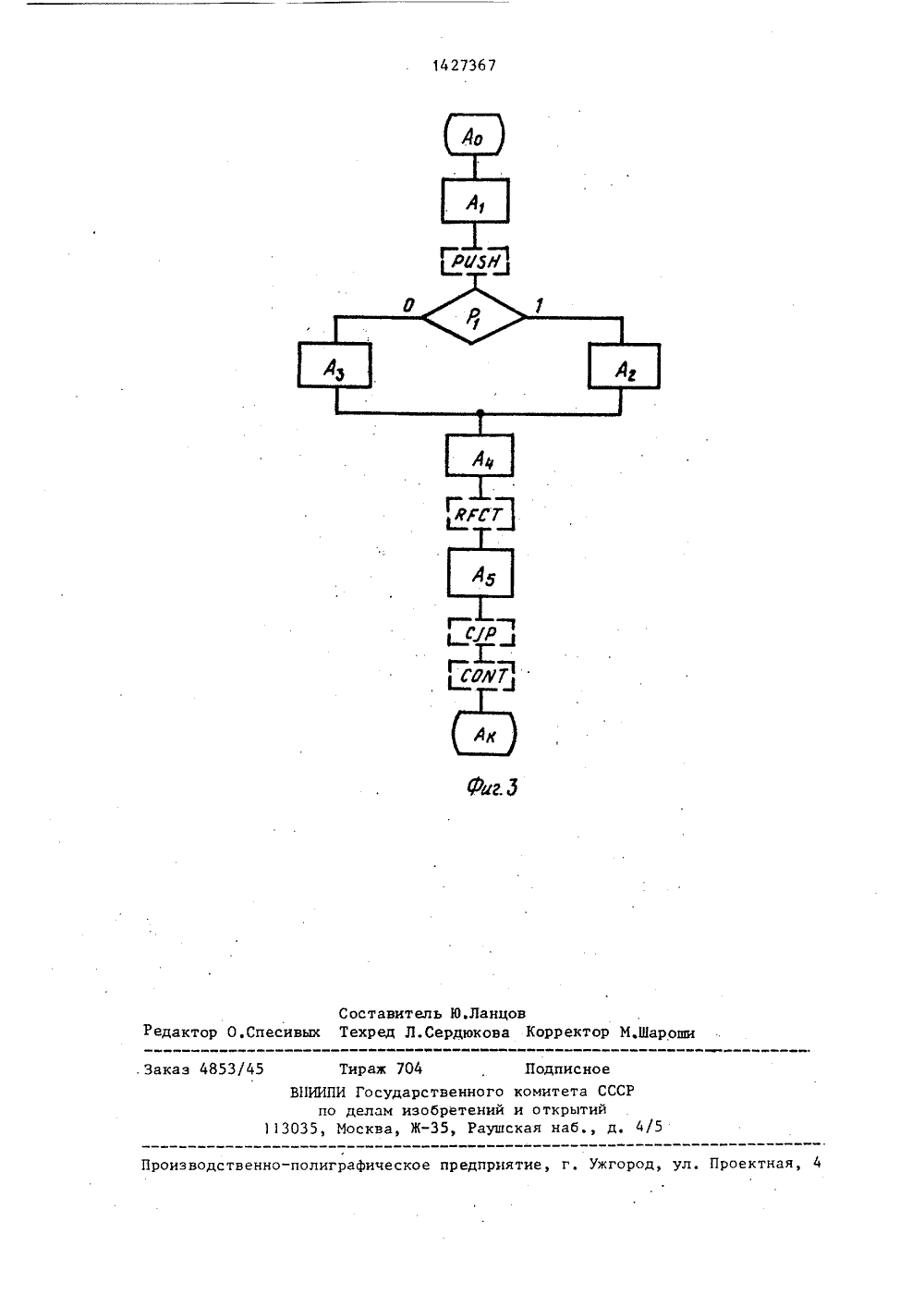

ОЮЗ СОВЕТСНИХ ЦИАЛИСТИЧЕСКИ РЕСПУ 11/Оо ПИСАНИЕ ИЗОБРЕТЕНИВТОРСКОМУ СВИДЕТЕЛЬСТВУ чй ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С САМОКОНТРОЛЕМ(57) Изобретение относится,к,вычислительной технике и может быть использовано для обнаружения ошибок птестовом контроле микропрограммы, Цлью изобретения является повышениедостоверности функционирования засчет увеличения полноты тестовой прверки. Устройство содержит блок памя ти микрокоманд, регистр микрокоманд, блок управления переходами, блок сравнения, распределитель импульсов, эле" менты И, ИЛИ, НЕ, сигнатурный анализатор, мультиплексор и триггер. Новыми являются элементы И, ИЛИ, НЕ, сигнатурный анализатор, мультиплексор и триггер. В предложенном устройстве рабочая микропрограмма преобразуется к тестопригодному виду путем введения дополнительных микрокоманд-инструкций, обеспечивающих проверку всех микрокоманд микропрограммы в определенной последовательности. Тестовая микропрограмма размещается в блоке па" мяти микрокоманд, Режим тестированиязадается присутствием единичного сиг- наг.а на выходе режима контроля устройства. Текущий адрес микрокоманды заносится в, сигнатурный анализатор, где производится его свертка в сигнатуру, Сравнение накопленной сигнатуры с эталонной происходит в схеме сравне- , ния в конце контроля микропрограммы. р Счетный триггер управляет порядком р проверки переходов по условию. В тестовой микропрограмме каждая микро- команда имеет три дополнительных разряда, которые управляют. работой устройства в тестовом режиме. 3 ил, 142736 7Изобретение относится к вычислительной технике и может быть использовано для обнаружения ошибок притестовом контроле микропрограммы,в частности в устройствах с постоян 5ным микропрограммным обеспечением.Цель изобретения - повышение достоверности функционирования за счетувеличения полноты тестовой проверки.На фиг. 1 изображена схема устройства; на фиг. 2 - схема блока сравнения, на фиг. 3 - пример алгоритмамикропрограммы выполняемой устройствомМикропрограммное устройство управления с самоконтролем (по фиг.1) содержит блок 1 памяти микрокоманд 1,регистр 2 микрокомайд блок 3 управления переходами, мультиплексор 4,элемент И 5, элемент ИЛИ б, счетныйтриггер 7, сигнатурный анализатор 8,схему 9 сравнения, распределитель 10импульсов, элемент НЕ .11, кроме того, на фиг 1 обозначены: вход 12кода операции устройства, вход 13 ло-гического условия устройства, вход14 начальной установки устройства,выход 15 ошибки устройства, выход16 микроопераций устройства, выход17 контроля устройства, выход 18 триггера (он же вход элемента ИЛИ 6), вы.ход 19 блока управления переходами,второй информационный вход 20 блокасравнения, первый информационный вход21 блока сравнения, управляющий. вход22 блока сравнения.Елок сравнения 9 (фиг. 2) содержитМ схем .23 сложения по модулю два, элемент ИЛИ 24, элемент И 25,В качестве блока управления переходами 3 может быть использована двенадцатиразрядная схема управления последовательностью микрокомандК 1804 ВУ 4, предназначенная дляпостроения блоков микропрограммного управ"ления цифровых устройств, имеющаяпрямой вход адреса, вход управлениярежимом (инструкций), вход сигнала условий и выход адреса.50В качестве сигнатурного анализатора 8 может быть использован параллельный регистр сдвига с обратныйи связями построенный на двуступенчатыхтриггерах типа Э и схемах сложения помодулю два.На фиг, 3 изображена блок-схемаалгоритма микропрограммы, на которой символами А, обозначены микрокоманды, к которым не производится условных переходов, Р - микрокоманда условного перехода, В В В, В -дополнительные тестовые микрокоманды,являющиеся инструкциями блока 3 1 управления переходами,Устройство работает следующим образом.Принцип работы устройства построен на том, что в блок памяти микрокоманд заносится тестовая микропрограмма, представляющая собой рабочуюмикропрограмму, преобразованную ктестопригодному виду путем введениядополнительных микрокоман-инструкций,обеспечивающих проверку всех микрокоманд микропрограммы в определеннойпоследовательности. Счетный триггер7 управляет строгим порядком проверки переходов по условию: сначала значение логического условия не выполняется, т.е, на второй вход сигнала условий блока 3 управления переходамиподается "1", затем - выполняется,т,е. на второй вход сигнала условийблока 3 управления переходами подается "0". Тестовая микропрограмма размещена в блоке памяти микрокоманд,Режим тестирования идентифицируетсядля объекта управления присутствиемединичного сигнала на выходе 17 режима контроля устройства. Текущий адрес микрокоманды заносится в сигнатурный анализатор 8, где производится его свертка в сигнатуру. Сравнениенакопленной сигнатуры с эталонной происходит в блоке 9 сравнения в концеконтроля микропрограммы.В регистре 2 микрокоманд имеютсятри дополнительных разряда: тестовый,разрешения, сравнения и контроля. Врежиме тестирования разряд контролявсегда равен единице, поэтому с выхода регистра 2 микрокоманд на выход17 устройства передается единичныйсигнал, сообщаемый в управляемую микропрограммным устройством систему опроведении тестирования.Распределитель 10 импульсов обеспечивает выдачу трех серий импульсов,подаваемых на входы занесения регистра 2 микрокоманд, блока 3 управленияпереходами, сигнатурного анализатора8, обеспечивающих синхронизацию работы устройства,Сигнал начальной установки, поступающий на вход 14 устройства, уста1427367 знавливает в нулевое состояние регистр 2 микракоманд, счетный триггер 7 и сигнатурный анализатор 8, поступая на их установочные входы. Код инструкций, поступающий из поля инструкций регистра 2 микрокоманд на вход управления режимом блока 3 управления переходами, равен нулю, что соответствует инструкции перехода по нулевому адресу (микрокоманда Ар.в блок-схеме алгоритма микропрограммы, т.е. с выхода 19 блока 3 управления переходами снимается нулевой адрес, поступающий на вход сигнатурного анализатора,8 и 15 обнуляющий его и поступающий на вход блока 1 памяти микрокоманд .1, с выхода которого считывается микрокоманда А хранящаяся по нулевому адресу и поступающая на вход регистра 2 микрокоманд. Микрокоманда А является оператор ной, т.е. в ней не производится условного перехода. Для всех оператор ных вершин (в примере это мнкрокоманды Аф, А, А, Аз, А, А, А) дополнительные тестовый и разрешения сравнения разряды равны нулю, поэтому они не влияют на организацию тестова- З 0 го просмотра микропрограммы. С выхода поля микроопераций регистра 2 микро- команд считывается на выход 16 устройства микроприказ, который поступает в операционную часть и осуществляет на нее воздействие. С выхода поля инструкций регистра 2 микрокоманд считывается код инструкций микрокоманды А,по которому выбирается адрес следующей микрокоманды, посту пающей на выход 19, с которого поступает на вход сигнатурного анализатора 8, где сворачивается в сигнатуру, которая хранится в сигнатурном анализаторе 8, до поступления следующего адреса и организации новой сигнатуры, и поступает через входы 20 на схемы 23 сложения по модулю два и элемент ИЛИ 24, с выхода которого поступает на первый вход элемента И 25, на второй вход 22 которого поступает нулевой сигнал с выхода разряда разрешения сравнения регистра 2 микракоманд, запирающий элемент И 25, т.е. на Выход 15 уСтройстВа поступает "0". Адрес микрокоманды А с выхода 19 поступает в блок 1 памяти микрокоманд, с выхода которого считывается следующая микрокоманда, являющаяся инструкцией В, поступающая на вход регистра 2 микрокоманд,Поле адреса ветвления инструкции В, содержит единичный код, тестовый разряд и разряд разрешения сравнения равны нулю. Инструкция В предназначена для запоминания в блоке 3 управления переходами адреса следующей микрокоманды, т.е. адреса Р 4 и при нулевом сигнале на входе условия блока 3 управления переходами происходит его загрузка информацией, поступающей через первый вход с выхода мультиплексора 4. В режиме тестирования на управляющий вход мультиплексора 4 с выхода разряда контроля регистра 2 микрокоманд всегда поступает единичный сигнал, запрещающий прохождение адреса с внешнего входа 12 устройства и разрешающий прохождение адреса с выхода поля адреса регистра 2 микрокоманц. Нулевой сигнал с выхода тестового разряда регистра 2 микрокоманд поступает на вход счет- ного триггера 7, который находится В нулевом состоянии, поэтому с его выхода снимается нулевой сигнал, поступающий на вход 18 элемента ИЛИ 6, на второй вход которого в режиме тестирования всегда поступает ноль с выхода элемента И 5, на вход которого через элемент НЕ 11 поступает единичный сигнал с выхода разряда контрог.я регистра 2 микрокаманд, запрещающчй прохождение значений логических условий с входа 13 устройства, С выхода элемейта ИЛИ 6 снимается нулевой сигнал, поступающий на вход условия блока 3 управления переходами, обеС- печивающий загрузку единичного кода в в блок 3 управления переходами через его адресный вход. Инструкция В 4 организует переход к следующему по порядку адресу микрокоманды, т.е.адресу Р, считывающемуся С выхода 19 на вход сигнатурного анализатора 8 и на вход блока 1 памяти микрокоманд, с выхода которого в регистр 2 микрокоманд считывается микракоманца Р . Микрокоманда Р является микрокомандой условного перехода, имеет тестовый разряд, равный единице, а разряд разрешения сравнения, равный ну- лю. Единичный сигнал с выхода тестового разряда регистра 2 микрокоманд поступает на вход счетного триггера 7, который находится в нулевом сосИнструкция Вз, имеющая тестовый разряд и разряд разрешения сравнения, равные нулю, содержит в поле адреса ветвления адрес эталонной сигнатуры. С выхода тестового разряда регистра 2 микрокоманд нулевой сигнал поступает на вход счетного триггера 7, который находится в нулевом состоянии, с выхода которого нулевой сигнал через вход 18 элемента ИЛИ 6 поступает на вход условия блока 3 управления переходами, разрешающий поступление адреса эталона с второго выхода регистра 2 микрокоманд через мультиплексор 4 выбора адреса на адресный вход блока 3 управления переходами, с выхода 19 которого снимается адрес эталона, поступающий на вход блоха 1 памяти микрокоманд 1, с выхода которого считывается инструкция В 4, поступающая в регистр 2 микрокоманд.Адресная часть инструкции В содержит эталон, тестовый разряд равен нулю, а разряд разрешения сравнения равен единице. На блок 9 сравнения на входы 21 поступает эталон с выхода поля адреса регистра 2 микрокоманд на вход 20 блока сравнения поступают разряды сигнатуры, накопленной в сигнатурном анализаторе 8. Если ошибки нет, то с выхода схем 23 сложения по модулю два считываются нулевые сигналы, поступающие на входы элемента ИЛИ 24, с выхода которого нулевой сигнал поступает на первый вход элемента И 25, на второй вход 22 которого поступает единичный сигнал с выхода разряда разрешения сравнения регистра 2 микрокоманд, ла выходе элемента И 25 появляется нулевой сигнал, поступающий на выход 15 устройства, что означает, что работа устройства безошибочна, В.случае ошибки, т.е. несовпадения эталона с накопленной сигнатурой, с какого-либо выхода схем 23 сложения по модулю два снимается единичный сигнал, поступающий на входы элемента ИЛИ 24, с выхода которого единичный сигнал поступа-. ет на первый вход элемента И 25, с выхода которого снимается единичный сигнал, поступающий иа вход 14 устройства, означающий, что устройство неисправно. Таким образом, предлагаемое устройство позволяет повысить полноту 1427367 тоянии, с выхода счетного триггера 7 .единичный сигнал через вход 18 элемента ИЛИ 6 поступает на вход условия блока 3 управления переходами,5 что означает невыполнение условия, т.е. блоком 3 управления переходами выбирается адрес следующей микрокоманды, находящейся по нулевой ветви логической микрокоманды Р. Этим адресом является адрес микрокоманды А.Процедура выборки адресов и записи в сигнатурный анализатор 8 микро- команд А и А 4 такая же, как и для микрокоманды А 4. 15Следующая за микрокомандой А 4 мик" рокоманда, содержащая инструкцию В, поступает в регистр 2 микрокоманд. Инструкция В, имеющая нулевые разряды тестовый и разрешения .сравнения, анализирует состояние блока 3 управления переходами, в который при выполнении инструкции В занесена единица, и так как состояние не равно нулю, выполняется переход к адресу 25 микрокоманды Р, который хранился в блоке 3 управления переходами, состояние блока 3 управления переходами уменьшается на единицу, т.е. становится равным нулю. В регистр 2 мик рокоманд из блока 1 памяти микро- команд 1 считывается микрокоманда Р 4, у которой тестовый разряд равен еди-, нице который с выхода регистра 2 микрокоманд поступает на вход счетного триггера 7, который находится в единичном состоянии и с выхода которого нулевой сигнал через вход 18 элемента ИЛИ б поступает на второй вход. сигнала условия блока 3 управ ления переходами, что означает выполнение условия, те, блоком 3 управления переходами выбирается адрес следующей микрокоманды, находящейся по единичной ветви логической микро команды Р . Этим адресом является адрес микрокоманды А. Повторяется формирование адресов микрокоманды А 4 и микрокоманды, содержащей инструкцию В. Инструкция В опять анали О зирует состояние блока 3 управления переходами, и так как теперь оно равно нулю (после первого выполнения инструкции В), то блок 3 управления переходами выполнит переход к следующей по порядку микрокоманде Ау, которая после выполнения передаст управление микрокоманде, содержащей инструкцию В .тестового контроля микропрограммы за. счет введения в микропрограмму дополнительных безусловных переходов, что позволяет просматривать в тестовом5 режиме все микрокоманды микропрограммы еДополнительным эффектом, достигаемом при применении устройства, является повышение достоверности за счет возможности контроля всех микро- команд, независимо от того, являются ли они условными или операторнымиеКроме того, отсутствие в предлагае мом устройстве контроля после каждой микрокоманды приводит к минимальным затратам памяти микрокоманд, где хранятся эталоны.20Формула изобретенияМикропрограммное устройство управления с самоконтролем, содержащее . блок памяти микрокоманд, регистр микрокоманд, блок управления переходами, 25 блок сравнения, распределитель импульсов, причем вход начальной установки устройства соединен с входами установки в "О" распределителя импульсов и регистра микрокоманд, первый З 0 выход распределителя импульсов соединен с входом синхронизации регистра микрокоманд, выход поля инструкций которого соединен с входом управления режимом блока управления переходами, выход которого соединен с адресньп 4 входом блока памяти микрокоманд, выход которого соединен с информационным входом регистра микро- команд, выход поля адреса которого 40 соединен с первым информационным входом блока сравнения, второй выход распределителя импульсов соединен с входом синхронизации и блока управления переходами, выход "Равно" блока сравнения является выходом ошибки устройства, выход поля жкроопераций регистра микрокоманд является выходом микроопераций устройства, о т л и ч а ю щ е е с я тем,что, с целью повышения достоверностифункционирования устройства за счетувеличения полноты тестовой проверки,устройство дополнительно содержитсигнатурный анализатор, мультиплексор, триггер, элемент И, элементИЛИ, элемент НЕ, причем вход начальной установки устройства соединен свходом установки в "О" триггера, входлогического условия устройства соединен с первым входом элемента И, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с входом условия блока управления переходами, вход кода операцииустройства соединен с первым информационным входом мультиплексора, выход которого соединен с адресным входом блока управления переходами, выход которого соединен с информационным входом сигнатурного анализатора,выход которого соединен с вторым информационным входом блока сравнения,выходы тестового разряда и разрядаразрешения сравнения регистра микрокоманд соединены соответственно сосчетным входом триггера и со стробирующим входом блока сравнения, выходразряда контроля регистра микрокоманд соединен с входом элемента НЕ,управляющим входом мультиплексора,входом. разрешения работы сигнатурного анаЛизатора и является выходомпризнака тестирования устройства,третий выход распределителя импульсов соединен с входом синхронизациисигнатурного анализатора, выход элемента НЕ соединен с вторым входомэлемента И, прямой выход триггера соединен с вторым входом элемента ИЛИ,выход поля адреса регистра микрокоманд соединен с вторым информационным входом мультиплексора.,Заказ 4853/45 Тираж 70 графическое предприятие, г. Ужгород, ул, Проектная роизводственно ВНИИПИ Государстве по делам изобре 035, Москва, Ж, Подписноеного комитета СССРений и открытийРаушская наб., д, 4/5

СмотретьЗаявка

4215605, 27.03.1987

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

БАЛАКИН ВИКТОР НИКОЛАЕВИЧ, БАРАШЕНКОВ ВАЛЕРИЙ ВИКТОРОВИЧ, КАЛЕНДАРЕВ АНДРЕЙ СЕМЕНОВИЧ, КАРПОВА НАТАЛИЯ НИКОЛАЕВНА

МПК / Метки

МПК: G06F 11/36

Метки: микропрограммное, самоконтролем

Опубликовано: 30.09.1988

Код ссылки

<a href="https://patents.su/7-1427367-mikroprogrammnoe-ustrojjstvo-upravleniya-s-samokontrolem.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммное устройство управления с самоконтролем</a>

Предыдущий патент: Микропрограммный модуль

Следующий патент: Многоканальное устройство для распределения заданий процессорам

Случайный патент: Способ штамповки изделий на многопозиционном кузнечно штамповочном автомате